DSP 封装说明

IC专业术语-通信-电子-网络专业术语(中英文对照表)-DSP常用接口中英文对照

封装形式:封装形式是指安装半导体集成电路芯片用的外壳。

它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接。

衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。

封装大致经过了如下发展进程:结构方面:TO->DIP->LCC->QFP->BGA ->CSP;材料方面:金属、陶瓷->陶瓷、塑料->塑料;引脚形状:长引线直插->短引线或无引线贴装->球状凸点;装配方式:通孔插装->表面组装->直接安装。

常见英文缩写解释(按字母顺序排列):模拟滤波器光纤通信高速信号处理和转换无线/射频光线通讯,模拟显示支持电路高频模拟和混合信号ASIC数字转换器,接口,电源管理,电池监控 DC/DC电源电压基准MAXIM前缀是“MAX”。

DALLAS则是以“DS”开头。

MAX×××或MAX××××说明:1后缀CSA、CWA 其中C表示普通级,S表示表贴,W表示宽体表贴。

2 后缀CWI表示宽体表贴,EEWI宽体工业级表贴,后缀MJA或883为军级。

3 CPA、BCPI、BCPP、CPP、CCPP、CPE、CPD、ACPA后缀均为普通双列直插。

举例MAX202CPE、CPE普通ECPE普通带抗静电保护MAX202EEPE 工业级抗静电保护(-45℃-85℃)说明 E指抗静电保护MAXIM数字排列分类1字头模拟器 2字头滤波器 3字头多路开关4字头放大器 5字头数模转换器 6字头电压基准7字头电压转换 8字头复位器 9字头比较器DALLAS命名规则例如DS1210N.S. DS1225Y-100INDN=工业级S=表贴宽体 MCG=DIP封Z=表贴宽体 MNG=DIP工业级IND=工业级 QCG=PLCC封 Q=QFP下面是MAXIM的命名规则:三字母后缀:例如:MAX358CPDC = 温度范围P = 封装类型D = 管脚数温度范围:C = 0℃至 70℃(商业级)I = -20℃至 +85℃(工业级)E = -40℃至 +85℃(扩展工业级)A = -40℃至 +85℃(航空级)M = -55℃至 +125℃(军品级)封装类型:A SSOP(缩小外型封装)B CERQUADC TO-220, TQFP(薄型四方扁平封装)D 陶瓷铜顶封装四字母后缀:例如:MAX1480ACPIA = 指标等级或附带功能C = 温度范围P = 封装类型I = 管脚数管脚数:A: 8 B: 10,64C: 12,192 D: 14E: 16 F: 22,256G: 24 H: 44I: 28 J: 32K: 5,68 L: 40M: 7,48 N: 18O: 42 P: 20Q: 2,100 R: 3,84S: 4,80 T: 6,160U: 60 V: 8(圆形)W: 10(圆形)X: 36Y: 8(圆形)Z: 10(圆形)E 四分之一大的小外型封装F 陶瓷扁平封装H 模块封装, SBGA(超级球式栅格阵列, 5x5 TQFP)J CERDIP (陶瓷双列直插)K TO-3 塑料接脚栅格阵列L LCC (无引线芯片承载封装)M MQFP (公制四方扁平封装)N 窄体塑封双列直插P 塑封双列直插Q PLCC (塑料式引线芯片承载封装)R 窄体陶瓷双列直插封装(300mil)S 小外型封装T TO5,TO-99,TO-100U TSSOP,μMAX,SOTW 宽体小外型封装(300mil)X SC-70(3脚,5脚,6脚)Y 窄体铜顶封装Z TO-92,MQUAD/D 裸片/PR 增强型塑封/W 晶圆DSP信号处理器放大器工业用器件通信电源管理移动通信视频/图像处理器等模拟A/D D/A 转换器传感器模拟器件AD产品以“AD”、“ADV”居多,也有“OP”或者“REF”、“AMP”、“SMP”、“SSM”、“TMP”、“TMS”等开头的。

dspDSP芯片结构介绍2

Digital Signal Processor 数字信号处理器 樊松 讲师

电子与信息工程学院电气工程系

1

第二章 DSP芯片结构介绍

第一节 基本性能 第六节 串行口

第二节 CPU结构

第七节 与外设的接口

第三节 内部总线结构 第八节 复位与省电

第四节 存储器结构 第九节 中断

第五节 在片外围电路 第十节 自举加载

1trn01tcn1m1d1elsen1m2d2d1d2m1尺度1m2尺度22j1n1n2j8d1d216功能exp指数编码器t寄存器如何计算指数171do页存储器18arp1513tc1211ova10ovbbraf15cpl14xf13hm12intm1110ovm19iptr157mpmc如何将40位数据饱和处理成32位数20?程序总线pb?数据总线cbdb和eb?地址总线pabcabdab和eab?在片双向总线2122读写方式地址总线程序总线数据总线pabcabdabeabpbcbdbeb程序读hwlwhwlw单数据写一个周期内如何执行3操作数指令24c54xcpu25cpu26daramsaramrom27存储器型式c541c542c543c545c546c548c549rom28k2k2k48k48k2k16k程序20k2k2k32k32k2k16k程序数据8k16k16kdaram5k10k10k6k6k8k8ksaram24k24k28rom空间交叉的条件mp位ovly位drom位禁止程序数据片内存储器空间29tms320c549存储器空间分配图30?c548和c549页扩展方法?对程序空间扩展31器件rommpmc0daramovly1saramovly1c54128k5kc5422k10kc5432k10kc54548k6kc54648k6kc5482k8k24kc54916k8k24k32片内rom分块的目的333435器件程序数据romdrom1daramsaramc5418k5kc54516k6kc54616k6k8k24kc54916k8k24k363738访问所需周期数39地址cpu寄存器名称地址cpu寄存器名称imr中断屏蔽寄存器12ar2辅助寄存器2ifr中断标志寄存器13ar3辅助寄存器3保留用于测试14ar4辅助寄存器4st0状态寄存器015ar5辅助寄存器5st1状态寄存器116ar6辅助寄存器6al累加器a低字17ar7辅助寄存器7ah累加器a高字18sp堆栈指针ag累加器a保护位19bk循环缓冲长度寄存器bl累加器b低字1abrc块重复计数器bh累加器b高字1brsa块重复起始寄存器bg累加器b保护位1crea块重复结束寄存器t暂存寄存器1dpmst处理器工作方式trn状态转移寄存器1expc程序计数器扩展10ar0辅助寄存器011ar1辅助寄存器11e1f保留4020

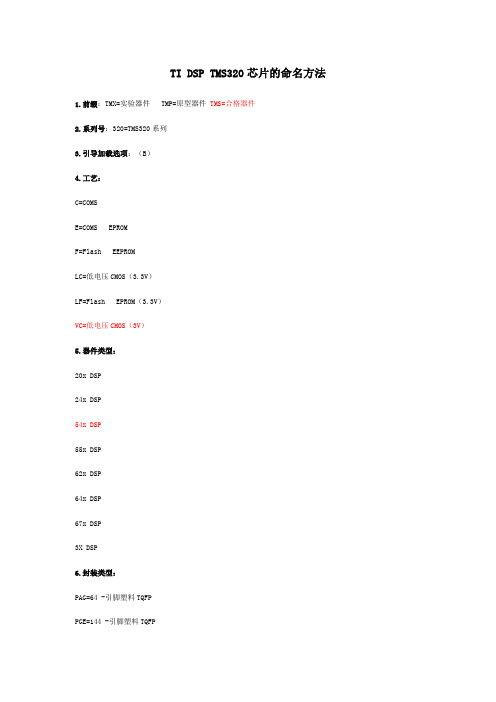

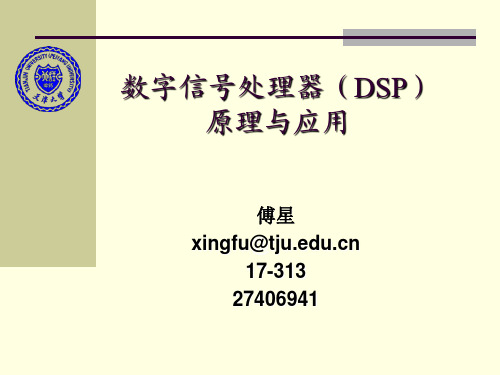

TI DSP TMS320芯片的命名方法

TI DSP TMS320芯片的命名方法1.前缀:TMX=实验器件 TMP=原型器件 TMS=合格器件2.系列号:320=TMS320系列3.引导加载选项:(B)4.工艺:C=COMSE=COMS EPROMF=Flash EEPROMLC=低电压CMOS(3.3V)LF=Flash EPROM(3.3V)VC=低电压CMOS(3V)5.器件类型:20x DSP24x DSP54x DSP55x DSP62x DSP64x DSP67x DSP3X DSP6.封装类型:PAG=64 -引脚塑料TQFPPGE=144 -引脚塑料TQFPPZ=100 -引脚塑料TQFP7.温度范围:(默认0°C-70°C)L=0°C~70°CA=-40°C~85°CS=-40°C~125°CQ=-40°C~85°C,Q100 Fault Grading8.补充说明:PLCC=带J形引线的塑料芯片载体QFP=四方扁平封装TQFP=薄四方扁平封装全系列介绍:C5000 超低功耗DSPTMS320C5000™DSP 平台提供了业界功耗最低的广泛 16 位 DSP 产品系列,性能高达 300MHz (600 MIP)。

这些产品针对强大且经济高效的嵌入式信号处理解决方案进行了优化,其中包括音频、语音、通信、医疗、安保和工业应中的便携式器件。

其待机功率低至 0.15mW,工作功率低于 0.15mW/MHz,是业界功耗最低的 16 位DSP。

即使在执行 75% 双 MAC 和 25% ADD 这样的大活动量操作(无空闲周期)时,包含存储器在内的核心工作功率也仍然低于 0.15mW/MHz。

C5000 的性能高达 300MHz,它能给便携式器件带来复杂的数字信号处理功能,从而支持一流的创新。

该系列中有多款器件针对性能、功耗和连接选项进行了优化。

DSP 第二章 DSP芯片的基本结构和特征

1.存储器分配 TMS320C25具有4K字的片内程序ROM和544字的片内RAM。 RAM分为三块:B0、B1、B2。其中,B0块(256字)既可 配置为数据存储器(用CNFD指令),也可配置为程序存储器 (用CNFP指令)。其余288字(B1和B2块)只能是数据存储器。 544字的片内RAM可使C25能处理512字的数据阵列,如可进行 256点复数FFT运算,且尚有32字用作中间结果的暂存。 TMS320C25提供片外可直接寻址的程序和数据空间各64K字。 寄存器组包含8个辅助寄存器(AR0~AR7),它们可用作数据 存储器的间接寻址和暂存,从而增加芯片的灵活性和效率。这 些寄存器既可用指令直接寻址,也可用3比特的辅助寄存器指针 (ARP)间接寻址。辅助寄存器和ARP既可从数据存储器装数, 也可装入立即数。寄存器的内容也可存入数据存储器中。辅助 寄存器组与辅助寄存器算术单元(ARAU)相连接,用ARAU访 问信息表无需CALU参与地址操作,这样可让CALU进行其他操 作。

在哈佛结构中:由于程序和数据存储器 在两个分开的空间中,因此取指和执行能完全 重叠运行。 TMS320系列DSP芯片在基本哈佛结构的基础 上作了改进: 一是允许数据存放在程序存储器中,并被算 术运算指令直接使用,增强了芯片的灵活性; 二是指令存储在高速缓冲器(Cache)中,当 执行此指令时,不需要再从存储器中读取指令, 节约了一个指令周期的时间。如TMS320C30具 有64个字的Cache。进一步提高了运行速度和灵

2.2.4 特殊的DSP指令DSP芯片的另一个特征:特殊的指令。 指令DMOV:它完成数据移位功能。在数字信号处理中, 延迟操作非常重要,这个延迟就是由DMOV来实现的。 指令LTD:它在一个指令周期内完成LT、DMOV和 APAC(将乘法结果加到ACC中 )三条指令。 指令FIRS:

DSP相关知识及TMS320F2812性能介绍(精)

第一章 DSP 相关知识及TMS320F2812性能介绍数字信号处理(DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

在通常的实时信号处理中,它具有可程控、可预见性、精度高、稳定性好、可靠性和可重复性好、易于实现自适应算法、大规模集成等优点,这都是模拟系统所不及的。

1.1 DSP系统构成数字信号处理器是利用计算机或专用处理设备,在模拟信号变换成数字信号以后,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等高速实时处理的专用处理器,其处理速度比最快的CPU还快10~50倍。

一个典型的DSP系统,输入信号首先进行带限滤波和抽样,然后进行A/D变换将信号变换成数字比特流。

DSP芯片的输入是A/D变换后得到的以抽样形式表示的数字信号,DSP 芯片对输入的数字信号进行某种形式的处理,如进行一系列的乘累加操作(MAC)。

最后,经过处理后的数字样值再经D/A变换转换为模拟样值,之后再进行内插和平滑滤波就可得到连续的模拟波形。

必须指出的是,上面给出的DSP系统模型是一个典型模型,但并不是所有的DSP系统都必须具有模型中的所有部件。

1.2 DSP系统的特点数字信号处理系统是以数字信号处理为基础,因此具有数字处理的全部优点:(1)接口和编程方便。

DSP系统及其他以现代数字技术为基础的系统或设备都是相互兼容的,及这样的系统接口以实现某种功能要比模拟系统及这些系统接口容易得多;另外,DSP系统中的可编程DSP芯片可使设计人员在开发过程中灵活方便地对软件进行修改和升级。

(2)稳定性和可重复性好。

DSP系统以数字处理为基础,受环境温度、湿度、噪声、电磁场的干扰和影响较小,可靠性高;数字系统的性能基本不受元器件参数性能变化的影响,因此数字系统便于测试、调试和大规模生产。

(3)精度高。

16位数字系统可以达到10-5的精度。

(4)特殊应用。

有些应用只有数字系统才能实现,例如信息无失真压缩、V 型滤波器、线性相位滤波器等等。

DSP 相关知识及TMS320F2812性能介绍

第一章 DSP 相关知识及TMS320F2812性能介绍数字信号处理(DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

在通常的实时信号处理中,它具有可程控、可预见性、精度高、稳定性好、可靠性和可重复性好、易于实现自适应算法、大规模集成等优点,这都是模拟系统所不及的。

1.1 DSP系统构成数字信号处理器是利用计算机或专用处理设备,在模拟信号变换成数字信号以后,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等高速实时处理的专用处理器,其处理速度比最快的CPU还快10~50倍。

一个典型的DSP系统,输入信号首先进行带限滤波和抽样,然后进行A/D变换将信号变换成数字比特流。

DSP芯片的输入是A/D变换后得到的以抽样形式表示的数字信号,DSP芯片对输入的数字信号进行某种形式的处理,如进行一系列的乘累加操作(MAC)。

最后,经过处理后的数字样值再经D/A变换转换为模拟样值,之后再进行内插和平滑滤波就可得到连续的模拟波形。

必须指出的是,上面给出的DSP系统模型是一个典型模型,但并不是所有的DSP系统都必须具有模型中的所有部件。

1.2 DSP系统的特点数字信号处理系统是以数字信号处理为基础,因此具有数字处理的全部优点:(1)接口和编程方便。

DSP系统与其他以现代数字技术为基础的系统或设备都是相互兼容的,与这样的系统接口以实现某种功能要比模拟系统与这些系统接口容易得多;另外,DSP系统中的可编程DSP芯片可使设计人员在开发过程中灵活方便地对软件进行修改和升级。

(2)稳定性和可重复性好。

DSP系统以数字处理为基础,受环境温度、湿度、噪声、电磁场的干扰和影响较小,可靠性高;数字系统的性能基本不受元器件参数性能变化的影响,因此数字系统便于测试、调试和大规模生产。

(3)精度高。

16位数字系统可以达到10-5的精度。

(4)特殊应用。

有些应用只有数字系统才能实现,例如信息无失真压缩、V 型滤波器、线性相位滤波器等等。

TMS320C28x系列DSP芯片结构及引脚功能

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28X系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28X系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

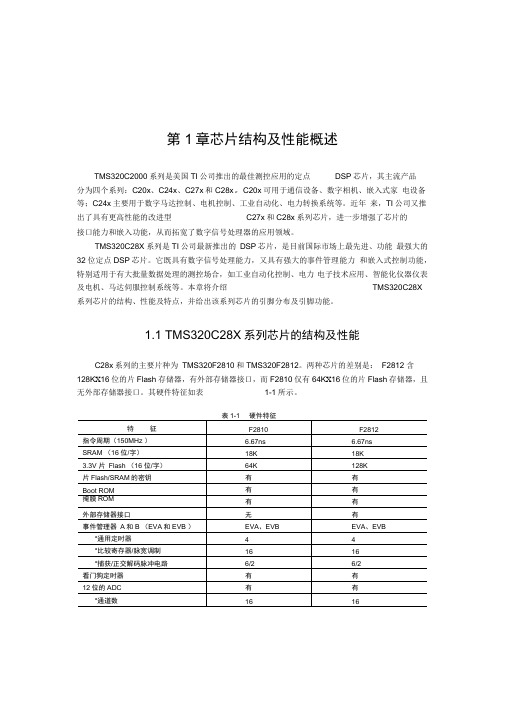

1.1 TMS320C28X系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812 含128K X16位的片Flash存储器,有外部存储器接口,而F2810仅有64K X16位的片Flash 存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

注:?“S”是温度选择(-40C〜+125 C)的特征化数据,仅对TMS是适用的。

??产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI ):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

??? TMP :最终的硅电路小片,它与器件的电气特性相一致,但是没有进行全部的品质和可靠性检测。

第2章TMS320LF240x系列DSP内部资源介绍

2.3.4 乘法器

16×16的硬件乘法器实现无符号数或有符号数(2的补 码数)相乘。

一个乘数来自TREG,另一个来自数据或程序存储器;乘 积放在PREG中。PREG的输出连接到乘积定标移位器PSCALE, 通过PSCALE,乘积结果可从PREG送到CALU或数据存储器。 PSCALE对乘积移位方式有4种(由ST1的乘积移位方式位 PM指定) PM=00:没有移位。 PM=01:左移一位。将二进制补码乘积中多余的1位符号 位去掉。 PM=10:左移4位。将二进制补码乘积中多余的4位符号 位去掉。 PM=11:左移6位。可防止乘积累加溢出。 2.5K字的数据/程序RAM 2.3.5 辅助寄存器和辅助寄存器算术单元

CPU

System module

2.3 中央处理单元(CPU)

LF240x系列芯片的CPU主要包括如下部件: ⑴ 一个32位的中央算术逻辑单元(CALU); ⑵ 一个32位的累加器(ACC); ⑶ CALU的输入数据定标移位器及输出数据定标移位器; ⑷ 一个16x16位的乘法器; ⑸ 一个乘积定标移位器; ⑹ 数据地址发生逻辑,其中包括8个辅助寄存器和1个 辅助寄存器算术单元; ⑺ 程序地址发生逻辑; ⑻ 两个16位的状态寄存器ST0、ST1。 2.5K字的数据/程序RAM LF240x的CPU结构框图如图2.5。

位3:EVB CLKEN。EVB模块时钟使能控制位。同位7。 位2:EVA CLKEN。EVA模块时钟使能控制位。同位7。 位0:ILLADR。无效地址检测位。在检测到一个无效地址时, 该位置1。需软件清0,向该位写1可清0。 ⑵ 系统控制和状态寄存器2(SCSR2)-- 地址7019h

15 保留位 RW_0 7 保留位 RW_0 6 I/P QUAL RW_0 5 WD OVERRIDE RC_1 4 XMIF HI-Z RW_0 3 BOOT EN RW-1 2 MP/MC RW-1 1 DON RW_0 0 PON RW_0 8

dsp器件说明

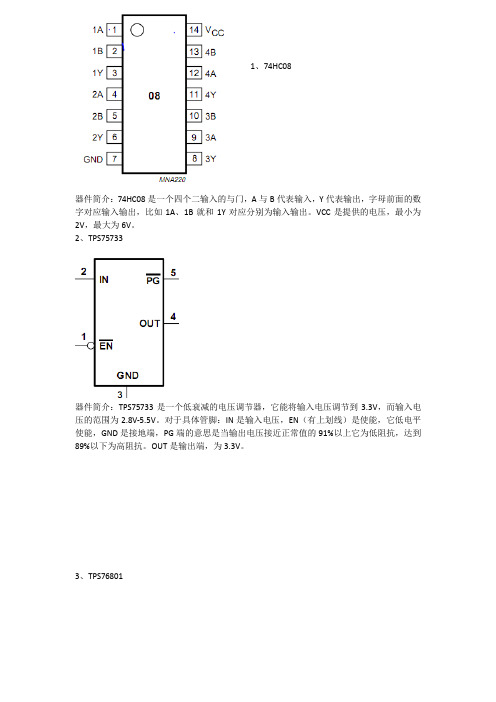

1、74HC08器件简介:74HC08是一个四个二输入的与门,A与B代表输入,Y代表输出,字母前面的数字对应输入输出,比如1A、1B就和1Y对应分别为输入输出。

VCC是提供的电压,最小为2V,最大为6V。

2、TPS75733器件简介:TPS75733是一个低衰减的电压调节器,它能将输入电压调节到3.3V,而输入电压的范围为2.8V-5.5V。

对于具体管脚:IN是输入电压,EN(有上划线)是使能,它低电平使能,GND是接地端,PG端的意思是当输出电压接近正常值的91%以上它为低阻抗,达到89%以下为高阻抗。

OUT是输出端,为3.3V。

3、TPS76801器件简介:TPS76801也是一种低衰减的电压调节器。

它能将输入电压调节到一定的范围(1.2V-5.5V),输出电压的调节是通过借外电路,和R1/R2固定的关系。

它能够实现上电重置和低电量指示;FB/NC端,FB是一个输入端,它通过反馈去感知输出电压的变化,还能防止噪音干扰,NC表示该端也可以不连接。

\、TPS3825器件简介:TPS3825是一个电源监测处理器。

它的作用是监测VDD是否高于门槛电压。

对于该芯片,门槛电压为2.93V。

5、LM1117器件简介:LM1117是一个低衰减的线性调节器。

图片上应该是LM1117-3.3,它能将5V的输入电压转换为3.3V的输出模拟电压量。

6、SN65HVD230器件简介:SN65HVD230是一个can收发器。

D是驱动输入,CANH和CANL分别是高总线输出和低总线输出,R是接收器输出。

Rs是备用控制。

Vref是参考输出,一般为0.5Vcc左右。

Vcc一般为3.3V。

它的功能表为7、PCF8583器件简介:PCF8583是总线接口实时时钟芯片。

它可以作为计数器、警钟或者RAM来使用。

对比较关键的端口说明一下:INT是中断输出端,当alarm寄存器中出现一定的值就发生,它是低有效。

8、MAX3223器件简介:MAX3223是一个多通道的RS232电平转换的器件。

DSP术语

分配:链接器计算输出段的最终存储器地址的过程。 分配节点:将节间消息分配至的处理器节点。 ALU:请参见算术逻辑单元。 ALU 函数:对于并行处理器,是指对到算术逻辑单元 (ALU) 的输入进行的操作, 其中包括三个输入的任何算术或 Boolean 组合,以及混合算术和 Boolean 函 数。(TMS320C8x)

汇编器:从包含汇编语言说明和指令的源文件创建机器语言程序的软件程序。汇 编器将绝对操作代码替换为符号 操作代码,并将绝对或浮动地址替换为符号地 址。

汇编语言:低级的符号编程语言,类似于机器代码语言并由字母组组成 — 每个 字母组代表一个指令;使计算机用 户可以使用助记符(而不是数字指令)来编 写程序。

汇编语言指令:使用计算机操作来表示助记符的语言。

汇编模式:无论当前运行哪种类型的代码,在 DISASSEMBLY 窗口中显示汇编语 言代码但不会显示 FILE 窗口 的调试模式。

汇编程序优化器:可优化线性汇编代码(尚未分配寄存器或预定的汇编代码)的 软件程序。当其中一个输入文件具 有 .sa 扩展名时,汇编程序优化器将会通过 shell 程序 cl6x 自动调用该文件。(TMS320C6x)

异步发送 (TX) 引脚:在该引脚上,来自异步串行端口的数据串行传输;从异步 串行端口移位寄存器 (AXSR) 按一 次一位的速度接收字符。(TMS320C2xx)

属性:指定适用于后续图形信息的部分特性或特点的参数。

音频输出电缆:将软件开发板 (SDB) 连接到音频输入和输出外设的电缆。包含 立体声线路输出、线路输入和辅助 输入的标准 RCA 插孔。(TMS320C8x)

数字信号处理器(DSP)原理与应用.ppt

数字信号处理的实现方法

实现方法 PC机 高级语言 编程 速度 中等 快 慢 应用场合 非嵌入式 非嵌入式 嵌入式 适应性 复杂算法 复杂算法 简单算法

Tianjin University

性价比 较好 中等 较好

PC机+高 速处理

单片机

硬件+ 专用指令

汇编语言 编程

通用DSP

专用DSP

专用指令

硬件+ 专用指令

•机器人视觉

•图像传输/压缩 •同态处理 •模式识别 •工作站

•动画/数字地图

Tianjin University

DSP芯片的主要应用领域

(1)信号处理

•频谱分析

(2)图像处理

•函数发生器

•模式匹配 •地震信号处理 •数字滤波 •锁相环

(3)仪器

(4)声音/语言 (5)控制 (6)军事应用 (7)电信 (8)无线电

MIPS(Million Instruction per second)是 一种评估DSP速度的一个指标。DSP运行频率也 是评估DSP的一个指标,他们二者之间的联系 需要考虑到DSP体系结构(是否多路并行结构、 是执行定点还是浮点运算)。

Tianjin University

价格 商业级 :一般应用;适用于实验室等环境较好 场合; 工业级 :可靠性好;适用于工业现场等环境恶 劣场合; 军品 :可靠性高;适用于各种恶劣场合; 航空级 :可靠性很高;适用于特殊场合;

Tianjin University

血压计

DSP系统基本构成

Tianjin University

输入

抗混叠 滤波 A/D DSP

平滑 滤波 D/A

输出

存储器

Tianjin University

第2章TMS320LF240x系列DSP内部资源介绍

2.1.2 引脚功能

各引脚按功能可分为以下8个部分(表2.1~2.9): ⑴ 事件管理器(EVA和EVB)引脚; ⑵ ADC模数转换器引脚; ⑶ 通信模块(CAN/SPI/SCI)引脚; ⑷ 外部中断与时钟引脚; ⑸ 地址/数据及存储器控制信号引脚; ⑹ 振荡器/PLL/FLASH/BOOT引导程序及其他引脚; ⑺ JTAG仿真测试引脚;2.5K字的数据/程序RAM ⑻ 电源引脚。

2.3.3 输入定标移位器

功能:将来自程序存储器或数据存储器的16位数据调整 为32位数据送到CALU。

移位:左移0-15位 规则:低位填0,高位根据SXM不同。

SSXXMM==01时时::高高位位填进行0 符2号.5K位字扩的展数。据/程序RAM

2.3.4 乘法器

16×16的硬件乘法器实现无符号数或有符号数(2的补 码数)相乘。

System module

2.3 中央处理单元(CPU)

LF240x系列芯片的CPU主要包括如下部件: ⑴ 一个32位的中央算术逻辑单元(CALU); ⑵ 一个32位的累加器(ACC); ⑶ CALU的输入数据定标移位器及输出数据定标移位器; ⑷ 一个16x16位的乘法器; ⑸ 一个乘积定标移位器; ⑹ 数据地址发生逻辑,其中包括8个辅助寄存器和1个

0:至少5个时钟周期长; 1:至少11个时钟周期长。

位5:WD OVERRIDE。WD保护位。复位时为1,向该位写1可

清0。

0:用户不能通过软件来禁止WD。

1:用户可通过软件来禁止WD工作(将WDCR寄存器的

WDDIS位置1)。

位4:XMIF HI-Z。外部存储器接口信号(XMIF)高阻控制

位。

DSP 封装说明

Revision Code Package Type N - Plastic Dip J - Ceramic Dip GB - Ceranuc BGA FZ - Ceramic CC FN - Plastic Leaded CC FD - Ceramic Leadless CC PJ - 100 Pin Plastic QFP PQ - 132 Pin Plastic BQFP PZ - 100 Pin Plastic TQFP PBK - 128 Pin Plastic TQFP GGU - 144 Pin BGA GJC/L - Plastic BGA PGE - Plastic LQFP GHH – 179pin BGA VF – 32pin LQFP PAG - 64pin LQFP PG – 64pin PQFP GJC - 352-pin BGA, 35mm GJL - 352-pin BGA, 27mm GLS - 384-pin BGA, 18mm GNY - 384-pin BGA, 18mm GNZ - 352-pin BGA, 27mm GHK - 288-pin BGA, 16mm GLW - 240-pin BGA, 18mm GFN - 256-pin BGA, 27mm GLZ - 532-pin BGA, 23mm

DSP Nomenclature

TMS

TMX = Experimental Device TMS = Qualified Device SMJ = Mil-Std-883C SM = High Family 320=TI DSP

VC

Technology C = CMOS E = Eprom CMOS F = Flash LC = 3.3 V CMOS LF = 3.3 V Flash VC = 1.8V (Core) CMOS UVC = 1.2V (Core) CMOS

TMS320LF240XDSP内部资源介绍

TMS2

36

2.2 总线结构

总线结构是各种微处理器芯片的总干 道,它的性能(响应速度、位宽、负载 能力等)在很大程度上决定了微处理器 芯片的性能。 LF240x控制器就是采用了多组总线 的结构,LF240x系列芯片具有相同 的总线结构,由6条16位的内部总线 构成 。

其中内部地址总线分为了三条 TDO TMS

135 139 142 144

JTAG扫描输出,测试数据输出引脚。在TCK的下降沿,选中寄存器中的 指令或数据被移出到TDO引脚(↓)

JTAG测试方式选择引脚(↑)。该串行控制输入在TCK的上升沿锁存到TRP 控制器中 JTAG测试时钟方式选择2引脚(↑)。该串行控制输入在TCK的上升沿锁存 到TRP控制器中;仅用于测试和仿真;在用户应用中,该引脚不可接

75

56 54 52

EVB模块的捕获输入#3//通用IO(↑)

EVB模块的比较/PWM输出引脚#1/通用IO(↑) EVB模块的比较/PWM输出引脚#2/通用IO(↑) EVB模块的比较/PWM输出引脚#3/通用IO(↑)

PWM4/IOPB1

PWM5/IOPB2 PWM6/IOPB3 T1PWM/T1CMP/IO PB4 T2PWM/T2CMP/IO PB5 TDIRA/IOPB6 TCLKINA/IOPB7

第2章 内部资源介绍

2.1 基本结构

1、引脚

LF240x系列的DSP芯片中,不同型号芯片 的引脚数是不同的。 如LF2407A有144个引脚,LF2406A有100 个引脚,等等 。 下面是TMS320LF2407A 引脚封装及其结构图

2.1 基本结构

1、引脚

LF240x系列的DSP芯片中,不同型号芯片的 引脚数是不同的。 如LF2407A有144个引脚,LF2406A有100个引 脚,等等

芯片常用封装及尺寸说明

A、常用芯片封装介绍来源:互联网作者:关键字:芯片封装1、BGA 封装(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配 LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚 LSI 用的一种封装。

封装本体也可做得比 QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚 QFP 为40mm 见方。

而且 BGA 不用担心 QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为 1.5mm,引脚数为225。

现在也有一些 LSI 厂家正在开发500 引脚的 BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国 Motorola 公司把用模压树脂密封的封装称为 OMPAC,而把灌封方法密封的封装称为 GPAC(见 OMPAC 和 GPAC)。

2、BQFP 封装(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和 ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见 QFP)。

3、碰焊PGA 封装(butt joint pin grid array)表面贴装型 PGA 的别称(见表面贴装型 PGA)。

4、C-(ceramic) 封装表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷 DIP。

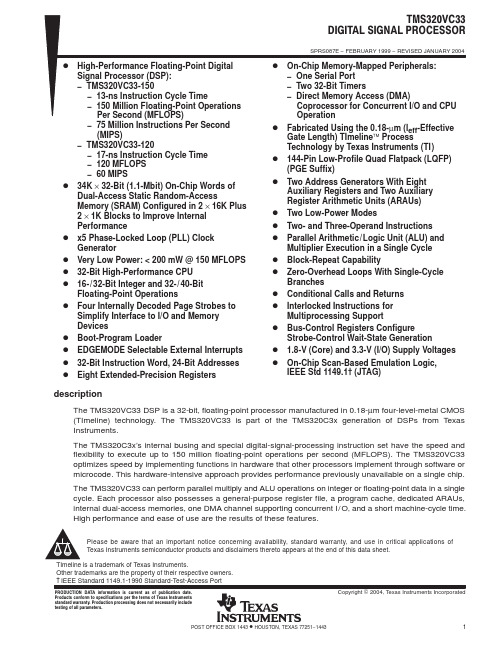

TMS320VC33DSP芯片说明书

D On-Chip Memory-Mapped Peripherals:

− One Serial Port − Two 32-Bit Timers − Direct Memory Access (DMA) Coprocessor for Concurrent I/O and CPU Operation Fabricated Using the 0.18-µm (leff-Effective Gate Length) TImeline Process Technology by Texas Instruments (TI ) 144-Pin Low-Profile Quad Flatpack (LQFP) (PGE Suffix) Two Address Generators With Eight Auxiliary Registers and Two Auxiliary Register Arithmetic Units (ARAUs) Two Low-Power Modes Two- and Three-Operand Instructions Parallel Arithmetic / Logic Unit (ALU) and Multiplier Execution in a Single Cycle Block-Repeat Capability Zero-Overhead Loops With Single-Cycle Branches Conditional Calls and Returns Interlocked Instructions for Multiprocessing Support Bus-Control Registers Configure Strobe-Control Wait-State Generation 1.8-V (Core) and 3.3-V (I/O) Supply Voltages On-Chip Scan-Based Emulation Logic, IEEE Std 1149.1† (JTAG)

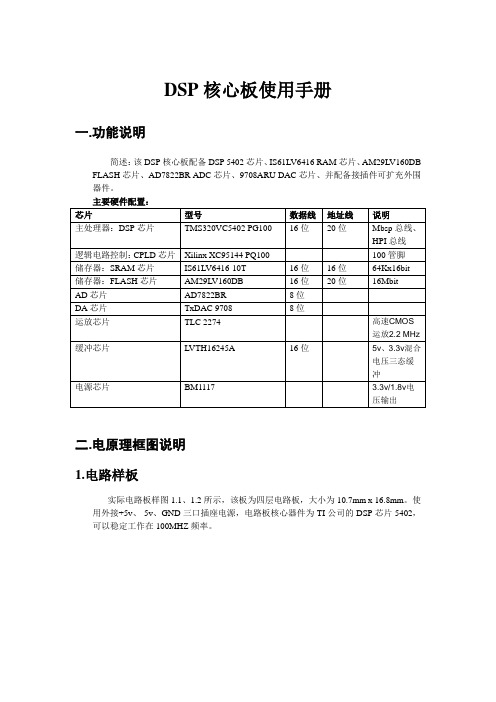

DSP核心板使用手册

DSP核心板使用手册一.功能说明简述:该DSP核心板配备DSP 5402芯片、IS61LV6416 RAM芯片、AM29LV160DB FLASH芯片、AD7822BR ADC芯片、9708ARU DAC芯片、并配备接插件可扩充外围器件。

主要硬件配置:二.电原理框图说明1.电路样板实际电路板样图1.1、1.2所示,该板为四层电路板,大小为10.7mm x 16.8mm。

使用外接+5v、-5v、GND三口插座电源,电路板核心器件为TI公司的DSP芯片5402,可以稳定工作在100MHZ频率。

图1.1 核心板正面照图1.2 核心板侧面照2.电原理框图如图2所示,其中双向箭头线表示的是数据总线,单向箭头线表示的是地址总线或者控制总线(注:AD接口、DA接口处的数据总线例外,这两处数据总线单向传输)图2.电原理框图三.电原理图说明本章节将分别说明各个模块的电原理图原理图使用PROTEL 2004DXP软件绘画(压缩包“DSP核心板.rar”),项目文件中包括:1.system.SchDoc 总体框图2.power.SchDoc 电源部分原理图3.DSP.SchDoc DSP芯片部分原理图4.RamFlash.SchDoc 储存芯片部分原理图5.CPLD.SchDoc CPLD芯片原理图6.boardIO.SchDoc 板载外围器件原理图7.buffer.SchDoc 缓冲器件原理图8.ADDA.SchDoc AD/DA原理图9.interface.SchDoc 核心板接口原理图10.capacitor.SchDoc 板载滤波电容原理图11.PCB1.PcbDoc PCB版图1.电源部分power.SchDoc:图3.10 电源部分A如图3.10所示,核心板的电源部分A由一个4芯插座以及两个LM1117电压转换芯片组成。

可通过外接5V、GND电源供电,通过LM1117转换成3.3V以及1.8V两种直流电压给核心板上的芯片供电。

TMS320系列DSP原理结构及应用

XINTF和并行I/O口; —标准的数学列表。 ◆时钟和系统控制

控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调 节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的 输入时钟频率。

引导模式选择见教材P248中表9.3-1。

第九章 TMS320F2833x系列DSC的硬件结构

9.3 TMS320F2833x 系列DSC的内核

3. F2833x的存储单元

5.存储器映射 F2833x DSC有两个独立的存储空间,即片内存储器和外部

存储器。片内存储器和外部存储器都可以用作数据存储空间和程 序存储空间。片内存储器的空间大小为128K×16,分为高16K 和低16K,包括256K×16位的FLASH,34K×16位的SRAM、 8K×16位的Boot ROM和1K×16位的OTP ROM。

DSC片内存储器与CPU之间数据读写和读取程序执行语句 的操作是通过三条总线(Memory Bus)完成。这三条总线分别 是程序读总线(PrgramRead Bus)、数据读总线(Data Read Bus)和数据写总线(Data Read Bus)。其中,程序读总线由 22根地址线和32位的数据总线组成。数据读和写总线是由32根 地址总线和32位的数据总线组成。32位的数据总线保证了每个周 期内进行32位的操作。

表9.3-2 Flash存储器块的地址分配

地址范围

0x300000-0x307FFF 0x308000-0x30FFFF 0x310000-0x317FFF 0x318000-0x31FFFF 0x320000-0x327FFF 0x328000-0x32FFFF 0x330000-0x337FFF 0x338000-0x337F7F 0x337F80-0x337FF5 0x337FF6-0x337FF7 0x337FF8-0x33FF7F