数字电子技术基础(数字电路)第二章逻辑代数与HDL基础

数字电子技术基础(侯建军)

§1-2 逻辑代数基础

逻辑变量及基本逻辑运算 逻辑函数及其表示方法

逻辑代数的运算公式和规则

逻辑变量及基本逻辑运算

一、逻辑变量

取值:逻辑 0 、逻辑 1 。逻辑 0 和逻辑 1 不代 表数值大小,仅表示相互矛盾、相互对立 的两种逻辑状态

二、基本逻辑运算 与运算 或运算 非运算

返 回

与逻辑

只有决定某一事件的所有条件全部具备, 这一事件才能发生

乘基取整法 :小数乘以目标数制的基数( R=2 ),第 1一次相乘结果的整数部分为目的数的最高位 0 1 K0 0 -1,将其小 数部分再乘基数依次记下整数部分,反复进行下去, 直 K-1 K-2 K-3 K-4 K-5

由此得:(0.65)10=(0.10100)2 综合得:(81.65)10=(1010001.10100)2

逻辑表达式

―-‖非逻辑运算符

F= A

逻辑符号 1 A

F

三、复合逻辑运算 与非逻辑运算 或非逻辑运算 与或非逻辑运算

或逻辑真值表

A 0 0 1 1 B 0 1 0 1 F 0 1 1 1 逻辑符号 A 1 B

F

或逻辑运算符,也有 N个输入: 用“∨”、“∪”表 逻辑表达式 示 F= A + B+ ...+

F= A + B

N

返 回

非逻辑

当决定某一事件的条件满足时,事件不发 返 回 生;反之事件发生,

非逻辑真值表 A F 0 1 1 0

§1-1 数制与编码

进位计数制 数制转换

数值数据的表示

常用的编码

§1-2 逻辑代数基础

逻辑变量及基本逻辑运算 逻辑函数及其表示方法

逻辑代数的运算公式和规则

数字电子技术基础 第二章 数字逻辑基础

A

灯

不通电

亮

通电

灭

10

3. 非运算

非逻辑举例状态表

A

灯

不通电

亮

通电

灭

非逻辑符号

1

A

L

非逻辑真值表

A

L

0

1

1

0

A

L

逻辑表达式

L=A

11

4. 几种常用复合逻辑运算

1)与非运算

两输入变量与非 逻辑真值表

A

B

L

0

0

1

0

1

1

1

0

1

1

1

0

与非逻辑表达式

与非逻辑符号

A&

B

L

A

B

L

L = A ·B

12

2)或非运算

分配律:A ( B + C ) = AB + AC A + BC = ( A + B )( A + C )

19

AA+AC+AB+BC=A+AC+AB+BC=A(1+C+B)+BC=A+BC

重叠律:

A+ A= A

A ·A = A

反演律: A + B = A ·B

吸收律 A A B=A

AB = A + B

互补律: A A 1

A 1 1 A 0 0 A A 0

等幂律: A A A A A A

双重否定律: A A

分别令A=0及A=1代入 这些公式,即可证明 它们的正确性。

17

(3)基本定理

交换律:

《数字电子技术基础》读书笔记02逻辑代数基础

《数字电子技术基础》读书笔记02 逻辑代数基础2.1从布尔代数到逻辑代数1849年英国数学家乔治布尔(George Boole)提出布尔代数,使用数学方法进行逻辑运算。

把布尔代数应用到二值逻辑电路中,即为逻辑代数。

2.2逻辑代数中的运算(想想初等代数中的加减乘除)2.2.1三种基本运算与(AND):逻辑乘,Y=A B或(OR):逻辑加,Y=A+B非(NOT):逻辑求反,Y=Aˊ简单逻辑运算(与、或、非)的两套图形符号,均为IEEE(国际电气与电子工程师协会)和IEC(国际电工协会)认定。

上排为国外教材和EDA软件中普遍使用的特定外形符号;下排为矩形符号。

2.2.2复合逻辑运算(都可以表示为与、或、非的组合)与非(NAND):先与后非,与的反运算,Y=(A B)ˊ或非(NOR):先或后非,非的反运算,Y=(A+B)ˊ与或非(AND-NOR):先与再或再非,Y=(A B+C D)ˊ异或(Exclusive OR):Y=A⊕B=A Bˊ+AˊB A和B不同,Y为1;A和B相同,Y为0。

当A与B相反时,A Bˊ和AˊB,肯定有一个结果为1,则Y为1。

同或(Exclusive NOR):Y=A⊙B=A B+AˊBˊA和B相同,Y为1;A和B不同,Y为0。

当A与B相同时,A B和AˊBˊ,肯定有一个结果为1,则Y为1。

同或与同或互为反运算,即两组运算,只要输入相同,一定结果相反。

A⊕B=(A⊙B)ˊA⊙B=(A⊕B)ˊ复合逻辑运算的图像符号和运算符号。

2.3逻辑代数的基本公式和常用公式2.3.1基本公式(见对偶定理)2.3.2若干常用公式(见逻辑函数化简方法之公式化简法)2.4逻辑代数的基本定理2.4.1代入定理(相当于初等代数中的换元)任何一个包含逻辑变量A的逻辑等式中,若以另外一个逻辑式代入式中所有A的位置,则等式依然成立。

2.4.2反演定理对于任意一个逻辑式Y,若将其中所有的""换成"+","+"换成"","0"换成"1","1"换成"0",原变量换成反变量,反变量换成原变量,则得到的结果就是Yˊ。

数字电子技术基础逻辑代数基础

与普通代数相似的公式

交换律 A B B A

A B B A

结合律 ( A B) C A (B C)

( A B) C A (B C)

分配律 A(B C) AB AC

普通代数

A BC ( A B) ( A C) 不适用!

[例 2. 3. 1] 证明公式 A BC ( A B)( A C)

各种表示方法之间可以相互转换

•真值表

输入变量

输出

A B C····

遍历所有可能的输 入变量的取值组合

Y1 Y2 ···· 输出对应的取值

• 逻辑式

将输入/输出之间的逻辑关系用与/或/非的运算式

表示就得到逻辑式。

• 逻辑图 用逻辑图形符号表示逻辑运算关系,与逻辑电路的 实现相对应。

• 波形图 将输入变量所有取值可能与对应输出按时间顺序排 列起来画成时间波形。

3. 对偶定理:如果两个表达式相等,则它们的对 偶式也一定相等。

将 Y 中“. ”换成“+”,“+”换成“.” “0” 换成“1”,“1”换成“0”

YD

( 对偶式 )

例如Y1 A(B C) CD Y1D (A BC) (C D)

Y2 ((AB C) D) C Y2D ((( A B) C) D)C

2、逻辑函数的建立

例:举重裁判的例子:设有三个裁判,分别用A,B,C表示,

其中A是主裁判。规定至少有两个裁判确认(其中必须包 含主裁判)时,运动员的试举才算成功。

当用Y表示举重结果时,Y与A,B,C的逻辑关系可表示为:

Y=F(A,B,C) =A(B+C)

2.5.2 逻辑函数的表示方法

数字电子技术第2章逻辑代数基础简明教程PPT课件

2.2.2 逻辑函数的最小项表达式

最小项通常用m表示,其下标为最小项的编号。编号的方 法如下:在每一个最小项中,原变量取值为1,反变量取 值为0,则每一个最小项对应一组二进制数,该二进制数 所对应的十进制数就是这个最小项的编号。

三变量的最小项编号表

2.2.3 逻辑函数的代数化简法

代数法化简是指直接利用逻辑代数的基本定律和规则,对 逻辑函数式进行变换,消去多余项和多余变量,以获得最 简函数式的方法。判断与或表达式是否最简的条件是: (1) (2) 每个乘积项中变量最少。 代数法化简没有固定的步骤,常用的化简方法有:并项法、 吸收法、消因子法、消项法和配项法5种。

2.最小项的性质 (1) 任何一个最小项,只有一组与之对应的变量组合使其 取值为1,其他各种变量组合均使其取值为0。 (2) n变量的所有最小项之和恒为1。因为无论输入变量如 何取值,总有某个最小项的值为1,因此其和必定为1。 (3) 任意两个最小项之积为0。 (4) 具有逻辑相邻性的两个最小项相加,可合并为一项, 并消去一个不同因子。

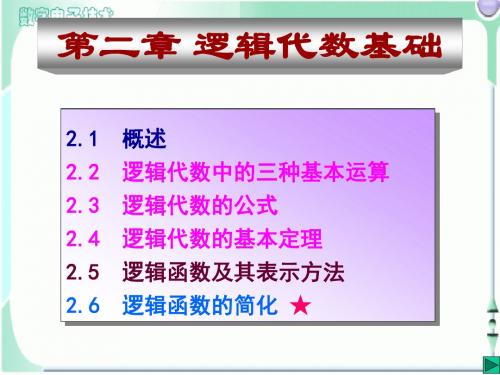

数字电子技术

第2章 逻辑代数基础

本章知识结构图

基本定律

逻 辑 代 数 基 础

基本规则

逻辑函数表示方法

逻辑函数化简

代数法

实例电路分析

卡诺图法

第2章 逻辑代数基础

2.1 逻辑代数

2.2 逻辑函数的化简法 2.3 实例电路分析

2.1 逻辑代数

2.1.1 逻辑代数的基本定律和恒等式

1.基本定律

A B C A B A C

(5) 重叠律 (6) 互补律

《数字电子技术基础》(第五版)教学课件

与(AND)

或(OR)

非(NOT)

以A=1表示开关A合上,A=0表示开关A断开; 以Y=1表示灯亮,Y=0表示灯不亮; 三种电路的因果关系不同:

《数字电子技术基础》(第五版) 教学课件

与

❖ 条件同时具备,结果发生 ❖ Y=A AND B = A&B=A·B=AB

AB Y 0 00 0 10 1 00 1 11

《数字电子技术基础》(第五版) 教学课件

或

❖ 条件之一具备,结果发生 ❖ Y= A OR B = A+B

AB 00 01 10 11

Y 0 1 1 1

《数字电子技术基础》(第五版) 教学课件

非

❖ 条件不具备,结果发生

❖ YANOT A

A

Y

0

1

1

0

《数字电子技术基础》(第五版) 教学课件

几种常用的复合逻辑运算

公式(17)的证明(真值表法):

ABC BC 000 0 001 0 010 0 011 1 100 0 101 0 110 0 111 1

A+BC 0 0 0 1 1 1 1 1

A+B A+C (A+B)(A+C)

0

0

0

0

1

0

1

00

1

1

1

1

1

1

1

11

1

1

1

1

1

1

《数字电子技术基础》(第五版) 教学课件

ACBCADBCD

《数字电子技术基础》(第五版) 教学课件

2.5 逻辑函数及其表示方法

❖ 2.5.1 逻辑函数 ❖ Y=F(A,B,C,······)

数字电子技术基础第二章

• 波形图 将输入变量所有取值可能与对应输出按时间顺序排 列起来画成时间波形。

《数字电子技术基础》第五版

《数字电子技术基础》第五版

• 卡诺图

• EDA中的描述方式 HDL (Hardware Description Language)

VHDL (Very High Speed Integrated Circuit …) Verilog HDL

EDIF DTIF 。。。

《数字电子技术基础》第五版

举例:举重裁判电路

YA(BC)

《数字电子技术基础》第五版

各种表现形式的相互转换:

• 真值表 逻辑式 例:奇偶判别函数的真值表

• A=0,B=1,C=1使 A′BC=1 • A=1,B=0,C=1使 AB′C=1 • A=1,B=1,C=0使 ABC′ =1

ACBCADBCD

《数字电子技术基础》第五版

2.5 逻辑函数及其表示方法

• 2.5.1 逻辑函数 • Y=F(A,B,C,······)

------若以逻辑变量为输入,运算结果为输 出,则输入变量值确定以后,输出的取值 也随之而定。输入/输出之间是一种函数关 系。

注:在二值逻辑中, 输入/输出都只有两种取值0/1。

• 逻辑式 逻辑图

《数字电子技术基础》第五版

1. 用图形符号代替逻辑式中的逻辑运算符。

YA(BC)

• 逻辑式 逻辑图

《数字电子技术基础》第五版

1. 用图形符号代替逻辑式中的逻辑运算符。

2. 从输入到输出逐级写出每个图形符号对应 的逻辑运算式。

(AB)

(( A B) ( A B)) ( A B)( A B)

数字电子技术基础2

二极管开关的转换过程

开通时间ton 当输入电压uI,由UIL跳变到UIH时,二极管D要经过导通延迟时间td、上升

时间tr之后,才能由截止状态转换到导通状态。其原因在于,当uI正跳变时, 只有当PN结中电荷量减少,PN结才由反偏转换到正偏,也即Cj放电,CD充 电

关断时间toff 当输人电压uI。由UIH跳变到UIL时,二极管D经过存储时间ts、下降时间

三极管临界饱和时的基极电流:

IBS Vc R u cc CE S1 1 2 0 0.2 3 0 m A 0.0m 6 A

因为iB>IBS,三极管工作在深度饱和状态。输出电压:

uo=UCES=0.3V 静态开关特性

截止状态

Rb +

+VCC

b c Rc

+

ui=UIL<0.5V

uo=+VCC

-

e

-

饱和状态

iC (mA) 直流负载线

VCC Q2 Rc

Q

80μA 60μA 40μA 20μA

2.3k iB

Q1 iB=0

Ω

0 UCES

VCC uCE(V)

输出特性曲线

①ui=UIL=-2V时,三极管截止,基极电流: ib≈0,ic≈0,uo≈Vcc=12V

②ui=UIH=3V时,三极管导通,基极电流:

iB

30.7mA 1mA 2.3

+VCC Rc iC

Rb b c uo

iB(μA)

iC (mA) 直流负载线

VCC Q2 Rc

Q

80μA 60μA 40μA

ui

iB

20μA

e 0 0.5 uBE(V)

0 UCES

Q1 iB=0

数字电子技术基础第2章

AB

1 1 1 0

A B

1 1 1 0

A B

1 0 0 0

AB

1 0 0 0

第2章 逻辑代数基础

2.2.2 三个重要规则

1. 代入规则

任何一个逻辑等式,如果将等式两边所出现的某一变量都

代之以同一逻辑函数,则等式仍然成立,这个规则称为代入 规则。 由于逻辑函数与逻辑变量一样,只有0、1两种取值, 所以代入规则的正确性不难理解。运用代入规则可以扩大基 本定律的运用范围。

第2章 逻辑代数基础

3

异或和同或运算的常用公式如表2.3.3所示。表中的公

式可以利用真值表或前面的公式证明。 表2.3.3 异或、同或运算的常用公式

名称 变量与 常量的 关系 交换律 结合律 分配律 反演律 调换律 奇偶律 异或公式 A 0=A A 1= A A A =1 A B=B A A B C=A (B C) A(B C)=AB AC 同或公式 A A A A A 1=A 0= A A =0 B=B A (B C)=(A C)=(A+B) B) C (A+C)

公式 1 A+1=1 A+0=A A+A=A A+ A =1 A+B=B+A (A+B)+C=A+(B+C) A+BC=(A+B)(B+C)

公式 2 A 0=0 A 1= A A A=A A A =0 A B=B A (A B) C=A (B C) A (B+C)=AB+AC

B A B L

特点:任1 则1, 全0则0

或逻辑表达式: L = A +B

数字电子技术基础第二章逻辑门电路基础[1]

![数字电子技术基础第二章逻辑门电路基础[1]](https://img.taocdn.com/s3/m/b2cf38a4227916888486d7d1.png)

(3)存储时间ts——从输入信号vi下跳变的瞬间 开始,到集电极电流iC下降到0.9ICS所需的时 间。

(4)下降时间tf——集电极电流从0.9ICS下降 到0.1ICS所需的时间。

数字电子技术基础第二章逻辑门电路 基础[1]

l (一)双极型三极管的静态开关特性

u 判断三极管工作状态的解题思路:

Ø (1)把三极管从电路中拿走,在此电路拓扑结构下求三极管 的发射结电压,若发射结反偏或零偏或小于死区电压值,则三 极管截止。若发射结正偏,则三极管可能处于放大状态或处于 饱和状态,需要进一步判断。进入步骤(2)。

Ø (2)把三极管放入电路中,电路的拓扑结构回到从前。假设 三极管处于临界饱和状态(三极管既可以认为是处于饱和状态 也可以认为是处于放大状态,在放大区和饱和区的交界区域, 此时时的三特极征管IC=既ßI有B)饱,和求状此态时时三的极特管征的VC集ES电=极0.临3V界,饱又和有电放流大I状CS 态, 进极而管求的出集基 电极极临可界能饱流和过电的流最大IBS电。流集。电极临界饱和电流ICS是三

PPT文档演模板

数字电子技术基础第二章逻辑门电路 基础[1]

(二)二极管的动态开关特性

•给二极管电路加入一个方波信号,电流的波形怎样呢?

PPT文档演模板

数字电子技术基础第二章逻辑门电路 基础[1]

PPT文档演模板

•ts为存储时 间 •tt称为渡越时 间 •tre = ts 十 tt 称 为 反 向 恢 复时间

PPT文档演模板

数字电子技术基础第二章逻辑门电路 基础[1]

第一节 二极管、三极管的开关特性

l的动态开关特性

PPT文档演模板

数字电子技术基础 第2章

证明若干常用公式

21、A+A ·B=A 证明:A(1+B)=A 22、A+A’ ·B=A+B 证明:利用分配律,(A+A’).(A+B)=1.(A+B) 23、A ·B+A ·B’=A 证明:A.(B+B’)=A.1 24、A ·(A+B)=A 证明:A.A+A.B=A+A.B=A(1+B)=A.1=A

1.2 逻辑式列出真值表

将输入变量取值的所有组合状态逐一代入逻辑式求出函数值, 就得到真值表。

例 2.5.2 P32-33

五、各种表示方法间的相互转换

2、逻辑函数式与逻辑图 的相互转换

2.1 给定逻辑函数式转换 为相应的逻辑图

用逻辑图形符号代替逻辑 函数式中的逻辑运算符号 并按运算顺序将它们连接 起来。

1、真值表与逻辑函数式的相互转换 1.1 由真值表写出逻辑函数式

1)找出真值表中使逻辑函数Y=1的那些输入变量取值的组合。 2)每组输入变量取值的组合对应一个乘积项,其中取值为1的

写入原变量,取值为0的写入反变量。 3)将这些乘积项相加,即得Y的逻辑函数式。 例 2.5.1 P32

IEC (International Electrotechnical Commission,国 际电工协会)

异或,同或

异或:

输入A,B 不同时,输出Y为1;输入A,B 相同时,输 出Y为0。

Y=A⊕ B=A· B’+A’ · B

或:

输入A,B 不同时,输出Y为0;输入A,B 相同时,输 出Y为1。

证明若干常用公式

25、A ·B+A’ ·C+B ·C=A ·B+A’ ·C 证明:=A.B+A’.C+B.C(A+A’) =A.B+A’.C+A.B.C+A’.B.C =A.B(1+C)+A’.C.(1+B)=A.B+A’.C 同样可证明:A ·B+A’ ·C+B CD=A ·B+A’ ·C 26、A ·(A ·B)’=A ·B’; A’ ·(A·B)’=A’ 证明:A.(A’+B’)=A.A’+A.B’=A.B’

【精品PPT】数字电子技术基础全套课件-2(2024版)

如果以逻辑变量作为输入,以运算结果作为 输出,当输入变量的取值确定之后,输出的取值 便随之而定。输出与输入之间的函数关系称为逻 辑函数。Y=F(A,B,C,…)

二、逻辑函数表示方法 常用逻辑函数的表示方法有:逻辑真值表(真

值表)、逻辑函数式(逻辑式或函数式)、逻辑 图、波形图、卡诺图及硬件描述语言。它们之间 可以相互转换。

( A B)

B A

( A B)

Y (( A B) ( A B)) ( A B)( A B) AB AB

5、波形图→真值表

A

1111

0000

B

11

11

00

00

C 1111

00

Y 11

00 11

0

00 0

ABC Y 00 0 0 t 00 1 1 01 0 1 t 01 1 0 10 0 0 t 10 1 1 11 0 0 t 11 1 1

A断开、B接通,灯不亮。

将开关接通记作1,断开记作0;灯亮记作1,灯 灭记作0。可以作出如下表格来描述与逻辑关系:

功能表

开关 A 开关 B 灯 Y

A

断开 断开

灭

0

断开 闭合

灭

0

1

闭合 断开

灭

1

闭合 闭合 亮

BY

00 真 10 值

00 表

11

两个开关均接通时,灯才会 Y=A•B

亮。逻辑表达式为:

实现与逻辑的电路称为与门。

与门的逻辑符号:

A

&

Y Y=A•B

B

二、或逻辑(或运算)

或逻辑:当决定事件(Y)发生的各种条件A,B,

C,…)中,只要有一个或多个条件具备,事件(Y)

数字电子技术2-PPT精品文档

2.1.3 逻辑函数的代数化简法

1、并项法

同 或 异 或

L A ( BC B C ) A ( B C B C ) 2

AB A B ( D D ) AB A B D A B D

AB A B

2.1.3 逻辑函数的代数化简法

AB A B

AB AB

AB AB

2.1.3 逻辑函数的代数化简法

用或非门实现

L A B C A B C

ABC ABC

L A B C A B C

2.1.3 逻辑函数的代数化简法

A B A B 3、消去法 A

L AB A C B C AB (AB)C

C AB AB C AB

2.1.3 逻辑函数的代数化简法 4、配项法 L AB A C B C AB A C ( A A ) B C AB A C AB C A B C AB AB C A C A C B AB AC

2.1.3 逻辑函数的代数化简法

一、逻辑函数的最简与或表达式

乘积项 乘积项

LAC C D

与或表达式 积之和

最简与或表达式:乘积项最少, 乘积项中变量数最少

2.1.3 逻辑函数的代数化简法

二、逻辑函数的化简方法

基本定律 恒等式 1、并项法 A A 1

B(CC) AB L A B C A B CA 1

A B C A B C

A B CA B C

数字电子技术基础:第二章 逻辑代数基础

8. 同或运算: 其布尔表达式为 Y A⊙B (A B) AB AB

符号“⊙”表示同或运算,即两个输入变量值相同 时Y=1,即相同为“1”不同为“0” 。同或运算用同 或门电路来实现,它等价于异或门输出加非门,

其真值表如表2.2.7所示 其门电路的逻辑符号如图2.2.11 所示

表2.2.7 同或逻辑真值表

☺异或运算的性质

1. 交换律: A B B A

2. 结合律: A (B C) (A B) C

3.分配律: A(B C) AB AC

4. A A 1 A A 0 A1 A A0 A

推论:当n个变量做异或运算时,若有偶数个变量取 “1”时,则函数为“0”;若奇数个变量取1时,则函 数为1.

符号“⊕”表示异或运算,即两个输入逻辑变量取

值不同时Y=1,即不同为“1”相同为“0”,异或运算

用异或门电路来实现 其真值表如表2.2.6所示

表2.2.6 异或逻辑真值表 输入 输出

其门电路的逻辑符号如图2.2.10

A

BY

所示

0

00

A B

=1 Y A B

Y

0

11

1

01

1

10

图2.2.10 异或门逻辑符号

A 0

上式说明:当逻辑变量A、B有

0

一个为1时,逻辑函数输出Y就

1

为1。只有A、B全为0,Y才为0。 1

BY

00 11 01 11

其逻辑门符号如图 2.2.4所示,实现或逻辑

A

运算的门电路称为或门。 B

1

Y

A B

Y

图2.2.4 或门逻辑符号

若有n个逻辑变量做或运算,其逻辑式可表示为

Y A1 A2 An

数字电子技术第二章习题课

解 (1) Y AB BC AC AB BC AC

(2) Y ( A B)(A B )C BC ( AB A B )C B C A B C ABC

(1)

电子与信息工程学院 电子教研室

12

(2)

第2章、逻辑代数基础

题2.15用逻辑代数的基本公式和常用公式将下列逻辑函数化为最简与 或形式 (1) Y AB B A B

解:(1) F1 AD A C (2)F2 B D

电子与信息工程学院 电子教研室

6

第2章、逻辑代数基础

例1.12 用卡诺图化简下列函数为最简与或形式 (1) F1 A BC D A BCD ABC D ABCD AB CD 约束条件: A B C D A B CD A BC D A BCD AB C D 0 (2) F2 A B C D AB C D A BCD AB CD

解:Y A C A B BC A BC BC A BC

例1.11用卡诺图化简下列带有约束项函数为最简与或形式。 (1)F1 ( A, B, C, D) (2,3,6,7,8,10,12,14)

(2)F2 ( A, B, C, D) (0,1,2,3,4,6,8,9,10,1112,14) ,

F (3) 3 A B C D E

解: (1) F1 ( A B)(A B ) A B AB

(2) F2 ( A B C ) ABC ABC ABC ABC (3) F3 A B C D E A B C ( D E ) (4) F4 A B C ABC

4

第2章、逻辑代数基础

数字电子技术 第2章逻辑代数

ABL 000 010 100 111

有0出0 全1出1

(4) 逻辑符号 国标 A

&

B

L

国外 A B

L

推广到n个逻辑变量情况,与运算的布尔代数表达式为: L=A1A2A3┄An

2、或逻辑(逻辑加) (1) 定义—只要有一个条件满足,结果就会发生。

(2) 逻辑式——L= A + B

(3) 真值表

设 开关闭合为 1,断开为 0

2、逻辑赋值问题

数字电路是研究输入、输出变量之间的逻辑关系。 逻辑函数、逻辑运算

逻辑运算遵循自己的定律、规则。 逻辑代数(布尔代数)

分析、设计数字逻辑电路的基本工具

2.1 逻辑代数

研究逻辑运算所遵循的定律、规则。

一、逻辑代数的基本定律

或

与

A+0=A

A·0=0

A+1=1

A·1= A

A+A=A A+A =1

2 173

余 1

低位

2

86

余 0

2

43

余 1

2

21

余 1

2

10

余 0

2

5

余 1

2

2

余 0

2

1

余 1高位ຫໍສະໝຸດ 0(173)10=(10101101)2

❖小数转换采用乘基取整法,直到小数部分为0

例如:将(0.8125)10化为二进制小数可如下进行

0.8125 ×2

整数和小数分别转换

整数:从小数点左第一位开始,每三位一组 小数:从小数点右第一位开始,每三位一组,不足补零 写出每组二进制数对应的八进制数。

例:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

L ( B D )( B D )( A B )

或:

L ( B D )( B D )( A D )

或项; 或项相与。

方法2: 求非函数的最简与或式;反演 由最简或与式可直接变换为最简或非-或非式。

作业

1.5.2 ;1.6.1;1.6.3 2.2.2;2.2.3 (1)、(4);2.2.5;2.2.6 (2) 2.3.1 (3)、(6);2.3.4 ;2.3.5 ;

m3 m6

L = m 3 + m 6 = å m (3, 6)

任意逻辑函数都可以表示成最小项之和的标准 型,简称最小项表达式或“标准与或式”。

注意

自学教材第47页2.2.1和2.2.2代数配项的方法。

3. 最大项与最大项表达式

最大项

Maxterm

三变量(A,B,C) 所有最大项

包含 n 个变量的或项,每个 变量以原变量或反变量的形 式出现且仅出现一次。

L2 CD AB 00 01 11 10 1 1 00 1 BD 1 1 01 BD 11 1 1 1 1 1 1 10 1

L 2 BD B D AB CD

有时最简式不唯一!

L 2 BD B D AB B C

说明:

由最简与或式可直接变换为最简与非-与非式。 最简或与式的获得: L CD AB 00 01 11 10 1 1 B+D 00 1 B+D 01 1 1 11 1 A+B 10 方法1: 合并0方格

L A B AC

2. 最小项与最小项表达式

最小项

Minterm

三变量(A,B,C) 所有最小项

包含 n 个变量的与项,每个 变量以原变量或反变量的形 式出现且仅出现一次。

A × B ×C A × B ×C A × B ×C A × B ×C A × B ×C A × B ×C A × B ×C A × B ×C

(合并后去异存同。)

m0 m1 m2 m3 m4 m5 m6 m7

000 001 010 011 100 101

110

111

最小项表达式 (标准与或式)

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 L 0 0 0 1 0 0 1 0

L = ABC + ABC

任意逻辑函数都可以表示成最大项之积的标准型, 简称最大项表达式或“标准或与式”。

五、逻辑函数的化简

引例:图示电路的逻辑功能?

A B A B L L

A 0 0 1 1

B 0 1 0 1

L 1 1 0 1

(2) (1)

电路更简单。 实现成本低。

化简目的:简化电路结构,降低电路实现成本。

最简式:项数最少;每项的变量数最少。 化简方法:代数法;图表法。

m0 m1 m2 m3 m4 m5 m6 m7

A+B+C A+ B+C A+ B+C A+ B+C A+ B+C A+ B+C A+ B+C A+ B+C

M0 M1 M2 M3 M4 M5 M6 M7

最大项表达式 (标准或与式)

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 L 0 0 0 1 0 0 1 0

合并相邻 1方格

写最简式 注意

优先处理圈法最少的1方格!

【例】 用K图求函数的最简与或式。

L1 BD A BC A B CD AB C D A B C D

L1 CD AB 00 01 11 10 ACD 1 00 1 1 1 01 ABC 11 1 1 1 1 10 ABC ACD

2. 最小项与最小项表达式

最小项性质

输入变量的每一组取值都有一个 值为1的最小项与之对应。

n-1

三变量(A,B,C) 使最小项值为 所有最小项 1的变量取值

A × B ×C A × B ×C 最小项可表示为mi。 A × B ×C 2 A × B ×C å mi = 1 i=0 A × B ×C mi • m j = 0 (ij) A × B ×C A × B ×C n个邻项,相邻最小项可以合并。 A × B × C

L = ABC + ABC

将表达式中的运算符号用逻辑符号 替代,可得到该逻辑函数的逻辑图

A L

B

C

真值表

表达式

波形图

逻辑图

四、逻辑函数表达式的形式

1. 逻辑函数表达式的基本形式

L = AB + AC

L = ( A + B )( A + C )

L = AB × AC L = A+ B+ A+C

与或式(积之和/SOP) 或与式(和之积/POS) 与非-与非式 或非-或非式 与-或-非式

四舍 五入 判别 电路

L

(4-39/26)

3. 具有无关项的逻辑函数及化简

真值表

A B C D

四舍 五入 判别 电路

L

在实际问题中,若有些变量的取值 组合不会出现或变量的取值对函数 值没有影响,则这些变量的取值所 对应的最小项(或最大项)称为无 关项或任意项。

AB C D 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1

最小项对应1方格; 最大项对应0方格。

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

L 0 0 0 1 0 0 1 0

L = ABC + ABC

一般式K图

L = A BCD + A × BC + C × D

【例】 用K图表示逻辑函数

L = A BCD + A × BC + C × D

2.3.1(2)

几点说明:

逻辑函数最简式有时不唯一,但最简程度相同。 或与式的化简及其它最简式 代数法化简特点 方法简单灵活,对变量数无限制 要求对公式的掌握程度高;最简标准不易掌握

2. 逻辑函数的K图(卡诺图)取值的对应关系。 n变量 2n个小方格 用几何位置的相邻反映逻辑上的相邻。 n变量K图中每个方格所对应的最小(大)项的 n个邻项均可在相邻的几何位置上找到。

L = ABC + ABC m 3 m 6

L = m 0 + m1 + m 2 + m 4 + m 5 + m 7

L = m 0 × m1 × m 2 × m 4 × m 5 × m 7 = M 0 × M1 × M 2 × M 4 × M 5 × M 7

= Õ M (0,1, 2, 4, 5, 7)

A+ B+C A+ B+C A+ B+C A+ B+C A+ B+C A+ B+C A+ B+C A+B+C

2. 最大项与最大项表达式

最大项性质

输入变量的每一组取值都有一个 值为0的最大项与之对应。

n -1

三变量(A,B,C) 所有最大项

使最大项值为 0的变量取值

A+ B+C A+ B+C 最大项可表示为Mi。 A+ B+C 2 A+ B+C Õ Mi = 0 A+ B+C i= 0 A+ B+C Mi + Mj = 1 (ij) A+ B+C n个邻项,相邻最大项可以合并。 A + B + C

(4-40/26)

L 0 0 0 0 0 1 1 1 1 1

3. 具有无关项的逻辑函数及化简

无关项及其表示

用×或表示

用约束条件表示

L CD AB 00 01 11 10 00 1 1 1 01 11 × × × × 10 1 1 × ×

M7 M6 M5 M4 M3 M2 M1 M0

111

110

101

100

011 010 001 000

(合并后去异存同。)

2. 最大项与最大项表达式

最大项、最小项的关系

三变量(A,B,C) 所有最小项

三变量(A,B,C) 所有最大项

n变量相同编 号的最小项与 最大项互为非 函数。

A × B ×C A × B ×C A × B ×C A × B ×C A × B ×C A × B ×C A × B ×C A × B ×C

CD AB 00 01 11 10 1 1 00 1 01 1 11 1 1 10 1

A BC

CD

说明 或与式的移植 覆盖

A BCD

合并

相邻最小项(或最大 项)可以合并。

典型合并情况举例:

K图上相邻1方格(或0 方格)可以合并。

CD CD AB 00 01 11 10 AB 00 01 11 10 1 1 00 1 1 1 00 1 1 01 01 1 1 1 1 1 11 1 1 11 1 1 10 1 10 1 两个方格 合并情况例 四个方格 合并情况例

真值表

表达式

L = A×B+ A×B

A B L

波形图

逻辑图

A B L

1 1 1 t1

0 1 0 t2