基于FPGA出租车计费器设计报告(verilog)

基于FPGA编程的出租车计价器报告

课程设计题目学院专业班级姓名指导教师年月日课程设计任务书学生姓名:专业班级:指导教师:工作单位:题目:主要任务:1、课程设计工作量:1周。

2、技术要求:①设计一个符武汉市合现行计价标准的TAXI计价器。

计价方案见附件。

②确定设计方案,按功能模块设计分电路,画出总体电路原理图,阐述基本原理。

③用Quartus软件完成设计,下载至开发板上运行。

④查阅至少5篇参考文献。

⑤按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印。

时间安排:1、年月初作课设具体实施计划与课程设计报告格式的要求说明。

2、年月日至年月日为课程设计时间。

3、年月日完成课程设计报告与答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录1课程设计目的 (4)2设计任务与要求 (4)2.1设计任务 (4)2.2设计要求 (4)3系统组成 (4)4模块设计 (5)4.1秒分频模块 (5)4.2控制模块 (5)4.3计量模块 (6)4.3.1计价部分 (6)4.3.2计时部分 (6)4.3.3计程部分 (6)4.4译码显示模块 (6)5程序调试运行 (9)5.1顶层原理图 (9)5.2仿真结果 (9)6硬件验证 ................................................................ 错误!未定义书签。

6.1引脚锁定............................................................................................. 错误!未定义书签。

6.2硬件验证情况.................................................................................. 错误!未定义书签。

7、课程设计总结 (10)7.1、收获 (10)7.2、心得体会 (10)参考文献 (11)附录 (12)出租车自动计价器的设计1课程设计目的为培养学生树立正确的设计思想和实事求是的工作作风,学习运用所学基础知识理论、专业知识、基本技能去分析和解决工程技术实际问题,提高学生的综合素质,使学生成为工程应用型合格人才,故进行《EDA技术及应用》的课程设计。

基于FPGA的出租车计价器设计

郑州交通职业学院《CPLD/FPGA应用》课程设计报告课程设计题目:基于FPGA的出租车计价器设计所属系别信息工程系专业班级 11大专电子信息工程技术1班姓名 XXXX学号 XXX指导教师 XXX撰写日期 2012 年 6 月一、设计任务与要求1、本课题要求设计车租车自动计价器,能基本实现自动计价的功能2、本出租车计价器的计费系统:行程3公里内,且等待累计时间2分钟内,起步费为10元;3公里外以每公里1.6元计费,等待累计时间2分钟外以每分钟1.5元计费。

并能显示行驶公里数、等待累计时间、总费用。

设计的主要技术指标如下:①、计价范围:0~999.9元 计价分辨率:0.1元 ②、计程范围:0~99公里 计程分辨率:1公里 ③、计时范围:0~59分 计时分辨率:1分二、方案设计与论证出租车的一般计费过程为:出租车载客后,启动计费器,整个系统开始运行,里程计数器从0开始计数,费用计数器从9开始计算;出租车载客中途等待,等待时间计数器从0开始计数。

最后根据行驶里程或停止等待的时间的计费标准计费。

出租车到达目的地停止后,停止计费器,显示总费用。

根据出租车计费器的工作过程,本系统采用分层次、分模块的方式设计,其FPGA 内部具体框图如下所示。

(1) 分频模块:分频模块是其它模块的基础,输入时钟选为32Hz ,分频后的时钟频率为1Hz,为后续模块提供基本时钟。

车费 计数 模块等 待 时 间译 码 模 块输 出 控制 模块里程 计数 模块分 频器 输入信号(2)等待时间模块:该模块针对乘客确认下车前的等待而言,比如堵车、中途下车的情况,通过1Hz脉冲计数,每一分钟计时加一,最大计时时间显示为99分钟。

(3)路程模块:该模块是对车辆行驶路程进行计数,以1Hz时钟为基础,检测行程脉冲,路程模块中有内部变量来判断路程,当大于3公里、20公里时,分别有相应的使能信号对此作出记录,最大路程显示为99公里。

(4)计费模块:该模块是基于等待时间模块和路程模块对费用进行控制的。

基于FPGA的出租车计费器设计.

湖南工程学院课程设计课程名称嵌入式系统课题名称基于CPLD的出租车计费器专业电子信息工程班级电子信息学号201213020113姓名魏震洲指导教师林愿2015年12月20日湖南工程学院课程设计任务书课程名称:嵌入式系统题目:基于CPLD的出租车计费器专业班级:电子信息学生姓名:魏震洲指导老师:林愿审批:任务书下达日期 2015 年12 月 1日设计完成日期 2015 年 12月 15日目录摘要 (1)Abstract ......................... 错误!未定义书签。

引言 (2)1.概述 (2)2.总体设计 (3)2.1设计要求 (3)2.2基本的原理方框图 (4)2.3 开发环境 (4)3.软件设计 (4)3.1总体设计 (4)3.2 各模块设计 (5)4.结果仿真 (11)4.1编译 (11)4.2管脚配置 (11)4.3程序下载 (12)5.硬件电路 (13)6. 系统使用说明 (13)结束语 (14)参考文献 (14)致谢............................. 错误!未定义书签。

附录.. (15)基于CPLD的出租车计费器摘要:本文借助QuartusⅡ9.0软件,基于大规模可编程逻辑器件FPGA,利用Verilog HDL语言,进行出租车计费器设计。

该出租车计费系统包括计数器分频模块、数码管分频模块、计程模块、计时模块、计费模块、控制模块、数码管显示模块和顶层主控模块共八大部分;分起步、里程、等待三个阶段。

该出租车计费器能够自行设定计费标准,借助CycloneⅡ系列EP20C8Q208C8N芯片的FPGA开发板,进行功能仿真,并且利用外围电路和开发板的结合,能够进行相应的硬件测试。

测试结果由2片4个相连的7段共阳极数码管驱动电路来显示。

关键词:出租车计费器;QuartusⅡ9.0软件;Verilog HDL语言;FPGA开发板引言随着出租车行业的发展,对出租车计费器的要求也越来越高,用户不仅要求计费器性能稳定、计费准确;同时还要求其具有计价标准的灵活设定、营运额统计、密码设定等功能。

基于FPGA的出租车计程计费器项目教学设计

基于FPGA的出租车计程计费器项目教学设计一、项目背景出租车计程计费器是出租车行业的重要设备,它可以根据行驶里程和时间自动计算乘客的费用。

传统的计程计费器通常是基于单片机或嵌入式系统来实现的,但是随着FPGA技术的发展,利用FPGA来实现计程计费器也成为一种新的选择。

FPGA具有运算速度快、可编程性强的特点,可以有效地提高计程计费器的性能和灵活性。

本项目将设计基于FPGA的出租车计程计费器,并将其作为教学实践项目,以帮助学生掌握FPGA的应用技术和计程计费器的工作原理。

二、项目目标1. 理解出租车计程计费器的工作原理和需求;2. 掌握FPGA的基本原理和应用方法;3. 设计并实现基于FPGA的出租车计程计费器原型。

三、项目内容1. 出租车计程计费器的工作原理出租车计程计费器通常需要实现以下功能:- 实时采集车辆的行驶里程和行驶时间;- 根据里程和时间计算乘客的费用;- 显示乘客的费用信息。

2. FPGA的基本原理和应用方法FPGA是一种可编程的逻辑器件,它由大量的可编程逻辑单元和存储单元组成,可以根据用户的需要编程实现各种数字逻辑功能。

FPGA的设计通常包括以下几个步骤:- 确定设计功能和性能需求;- 采用硬件描述语言(如Verilog、VHDL)进行逻辑设计;- 进行逻辑综合和布局布线;- 下载到FPGA芯片中进行验证和调试。

基于以上内容,学生将分为以下几个阶段进行项目设计和实现:第一阶段:学习出租车计程计费器的工作原理和需求,了解FPGA的基本原理和应用方法。

第二阶段:进行计程计费器的逻辑设计,包括行驶里程和行驶时间的实时采集、费用的计算和显示。

第三阶段:进行计程计费器的逻辑综合和布局布线,生成FPGA的配置文件。

第四阶段:将配置文件下载到FPGA芯片中进行验证和调试,完成基于FPGA的出租车计程计费器原型的设计和实现。

四、教学方案为了帮助学生顺利完成基于FPGA的出租车计程计费器项目,可以采取以下教学方案:1. 确定项目的实践环境和硬件平台,提供FPGA开发板和相关的软件工具;2. 组织相关理论课程和实验课程,介绍出租车计程计费器的工作原理和需求,讲解FPGA的基本原理和应用方法;3. 指导学生进行项目的逻辑设计、综合布局和验证调试,提供必要的技术支持和指导;4. 完成项目的设计和实现后,组织学生进行成果展示和总结,评选出优秀的作品并给予奖励。

基于FPGA的出租车计费器课程设计程序

设计题目:出租车计费器一、设计实验条件QuartusII7.2二、设计目标1.实现计费功能。

按行驶里程计费,起步价为6.00元,并在车行驶3km后按1.2元/km计费,当计费器达到或超过20元时,每千米加收50%的车费,车停止和暂停时不计费;2.现场模拟汽车的起动、停止、暂停和换挡等状态;3.设计数码管动态扫描电路,将车费和路程显示出来,各有两位小数。

三、设计报告的内容1.前言伴随中国经济的腾飞,城市化的进程也随之加快。

虽然人们出行的选择趋于多样化,但是出租车作为一种重要的交通工具,也为很多人作为出行的选择。

大城市里出租车已经相当普及,但是在中小城市出租车依然处于快速发展的阶段。

出租车的计费方式也在发生变化,由只能显示里程的方式变为现在的自主计费和打印发票及语音提示的智能化方式;根据出租车行业的发展需求,国内许多生产厂商也制造出不同类型的计价器,传统的出租车计费器经过十几年的使用,在稳定性,成本等方面都具有一定的优势。

利用FPGA设计出满足出租车不同计费需求的计费器,去满足当地出租车的计费需求。

这个课题在实现计费功能的同时,也解决了传统出租车计费器系统的不足。

出租车的需求不断的增大,因此,出租车计费器的需求也将不断增大,计程车的服务也显得越来越重要,因此出租车计费器也就应运而生了。

2.设计主体(1)设计原理:假设出租车有启动键、停止键、暂停键和档位键。

启动键为脉冲触发信号,当它为一个脉冲是,表示汽车已启动,并根据车速的选择和基本车速发出相应频率的脉冲(计费脉冲)实现车费和路程的计数,同时车费显示起步价;当停止键为高电平时,表示汽车熄火,同时停止发出脉冲,此时车费和路程计数清零;当暂停键为高电平时,表示汽车暂停并停止发出脉冲,此时车费和路程计数暂停;档位键用来改变车速,不同档位对应着不同的车速,同时路程计数的速度也不同。

出租车计费器可分为两大模块,即控制模块和译码显示模块,系统框图如图1所示,控制模块实现了计费和路程的技术,并且通过不同的档位控制车速。

基于FPGA的出租车计费器

基于FPGA的出租车计费器摘要基于FPGA的出租车计费器设计摘要本文介绍了一种基于FPGA 芯片上实现出租车计价器功能的设计方法,主要阐述如何使用新兴的EDA 器件取代传统的电子设计方法,不仅实现了出租车计价器所需的一些基本功能,同时考虑到出租车行业的一些特殊性,更注重了把一些新的思路加入到设计中。

本设计主要借助了FPGA 芯片,使用Verilog HDL语言灵活编程来实现多方面的计费,这样不仅使其不拘泥于硬件,具有更强的移植性,而且增强了实用价值,更加利于产品升级。

本设计参考成都的出租车计费标准,利用Verilog HDL语言设计出租车计价器,主要具有行驶路程动态显示计费,等待累计时间计费及最后的总费用动态显示功能,突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点。

此程序通过下载到特定的芯片后,可应用于实际的出租车计费系统中。

关键词:出租车计价器; Verilog HDL语言; FPGA; Quartus II; EDAABSTRACTThis article presents a method of how to use FPGA to design a taxi meter, and how to replace traditional electrical design with burgeoning EDA parts. Besides the basic functions of taxi count meter, some new ideas are added concerning about the particularity of this calling. This design has mainly drawn support from the FPGA chip, uses Verilog the HDL language nimble programming to realize various cost, which not only causes it not to rigidly adhere to the hardware with a stronger portability, but also strengthens the use value, even more favors the product promotion.This design acts according to chengdu's rental car cost standard to design rental car fare register with Verilog the HDL language,which includes the travel distance,the waited for the accumulation time cost and the final all-in cost dynamic demonstration function, it, as the hardware description language, has highlighted the advantages of good readability, the probability, and easy to understand and so on. This procedure may apply in the actual rental car cost system through downloads into the specific chip.Key words:Taxi meter;Verilog HDL language;FPGA;Quartus II;EDA目录第一章绪论 (1)1.1 课题背景: (1)1.2 出租车计价器现状及发展趋势: (2)1.3 本设计的主要工作: (3)1.4 现代数字系统的设计方法 : (3)1.4.1 设计步骤: (3)1.4.2 设计优点: (5)1.5 EDA技术: (5)1.5.1 EDA技术的内涵: (5)1.5.2 EDA技术的基本特征: (6)1.5.3 EDA的基本工具: (7)1.6 EDA 技术简介: (8)第二章出租车计价器的设计 (10)2.1 出租车计价器的要求: (10)2.2 系统组成框图: (10)第三章各模块设计 (11)3.1分频模块: (11)3.1.1 计数器的分频模块: (11)3.1.2 计数器的分频模块VerilogHDL源代码: (11)3.1.3 仿真的结果: (12)3.1.4 数码管的分频模块: (12)3.1.5 数码管的分频模块VerilogHDL源代码: (12)3.2 计程模块: (13)3.2.1 计程模块的框图: (13)3.2.2 计程模块的VerilogHDL源代码: (14)3.2.3 计程模块的仿真结果: (15)3.3计时模块: (16)3.3.1 计时模块的框图: (16)3.3.2 计时模块的VerilogHDL源代码: (16)3.3.3 计时模块的仿真结果: (17)3.4控制模块: (18)3.4.1 控制模块的框图: (18)3.4.2 控制模块的VerilogHDL源代码: (18)3.4.3 控制模块的仿真结果: (19)3.5 计费模块: (19)3.5.1 计费模块的框图: (19)3.5.2 计费模块的VerilogHDL源代码如下所示: (20)3.5.3 计费模块的仿真结果: (20)3.6 数码管显示模块: (21)3.6.1 数码管显示模块的框图: (21)3.6.2 数码管显示的VerilogHDL源代码: (21)3.7 顶层模块: (23)第四章验证方案 (26)4.1 验证的流程图: (26)4.2 验证的VerilogHDL源代码: (26)4.3 系统仿真: (28)第五章结论 (30)5.1 Quartus II软件综合的报表: (30)5.2 综合的RTL级电路: (30)5.3 设计总结: (30)5.4 FPGA设计展望: (32)参考文献 (33)致谢 (34)附录 (35)外文资料(原文) (36)外文资料(译文) (44)第一章绪论1.1 课题背景:随着我国经济的迅速发展,人们生活水平的显著提高,城市交通的日趋完善,出租车逐渐成为人们日常生活不可缺少的交通工具。

基于FPGA的出租车计程计费器项目教学设计

基于FPGA的出租车计程计费器项目教学设计1. 引言1.1 项目背景出租车计程计费器在现代城市交通中扮演着至关重要的角色,为乘客提供方便、快捷和准确的计费服务。

随着科技的不断发展,传统的计程计费器已经逐渐无法满足市场的需求。

本课题将基于FPGA技术设计和实现一款高性能的出租车计程计费器,以提升其计费精度和效率。

本项目的目标是利用FPGA技术设计出一款功能强大、性能优越的出租车计程计费器,并将其应用于实际交通场景中。

通过本项目,学生可以深入了解FPGA在嵌入式系统设计中的应用,提升其硬件设计和编程能力,同时也能为出租车行业的智能化发展做出贡献。

1.2 项目目的项目目的是通过基于FPGA的出租车计程计费器项目教学设计,帮助学生深入了解FPGA技术,并掌握计程计费器系统的设计和实现方法。

通过这个项目,学生将学习到FPGA技术的基本原理和应用,培养他们的电路设计能力和问题解决能力。

通过实际操作和项目实践,学生将能够提高他们的团队合作能力和创新意识。

通过对项目的评估和教学效果分析,可以及时发现和解决学生在学习过程中遇到的问题,进一步提高教学质量和学生的学习成果。

最终,希望通过这个项目的教学实践,为学生奠定良好的基础,帮助他们在未来的学习和工作中取得更好的成就。

2. 正文2.1 FPGA技术介绍FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,通过用户编程来配置其内部逻辑电路,从而实现特定的功能。

FPGA具有灵活性高、可重构性强等优点,因此被广泛应用于数字系统的设计和实现中。

在FPGA中最基本的单元是可编程逻辑单元(CLB),它由查找表(LUT)、触发器和多路器等组成,用于实现逻辑电路的功能。

FPGA 还包含了输入输出块(IOB)、时序管理器(CMT)等功能模块,以满足不同应用的需求。

FPGA的编程通常通过硬件描述语言(HDL)来实现,主要使用Verilog和VHDL两种语言。

基于FPGA的出租车计费器设计报告

课程设计报告课程名称:电子技术课程设计学院:自动化专业:自动化自控班级:自控1201B 学号:2012100329055姓名:成绩:前言电子设计自动化(Electronics Design Automation—EDA)技术是现代电子工程领域的一门新技术。

它提供了基于计算机和信息技术的电路系统设计方法。

EDA技术就是依赖功能强大的计算机,对用电路描述语言描述的设计文件,自动地完成编译、化简、分割、综合、布线、优化、仿真等,直至实现既定的电子电路系统的功能。

EDA技术打破了软件设计和硬件设计间的壁垒,是一门综合性学科,一种新的技能技术。

它将设计效率和产品性能合二为一,代表了电子设计技术和电子应用技术的发展方向。

EDA技术是指以计算机为工作平台,融合应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动化设计。

在EDA技术应用中广泛采用自顶向下的设计方法设计电路工程项目的设计流程包括:用自然语言描述功能特性和技术指标,用硬件描述语言建立系统描述→行为描述→结构描述→逻辑描述,用计算机开发软件进行功能仿真→时序仿真→硬件测试。

设计者在整个设计过程中可根据需要,随心所欲的改变器件内部结构乃至期间外部引脚功能,可以将系统电路分解为各个模块,也可以将多个模块集合在一起,而不必顾及各个器件的技术细节。

正是采用了基于可编程器件的,利用计算机完成的自顶向下的设计方法,大大减少了功能芯片的数量,减轻了设计电路板图的工作量,缩小了整体电路的体积,提高了系统的可靠性,加快了验发的速度,降低了产品设计的成本。

VHDL的全名是Very High Speed Integrated Circuit Hardware Description Language,于83年由美国国防部发起创建,由IEEE(The Institute of Electrical and Electronics Engineers 电气与电子工程师学会)进一步发展,在87年作为“IEEE 标准1076”发布,93年被升级为“IEEE1164”。

FPGA出租车计价器设计

EDA课程设计目标1.掌握用Verilog HDL语言的设计方法;2.掌握Verilog HDL语言程序的基本结构,学习编写简单的Verilog HDL设计实用程序;3.了解Quartus II软件的基本使用方法,数字电路系统的设计流程,掌握QuartusII的使用方法;4.在Quartus II环境下,对其设计功能进行编程、仿真、并下载到EDA试验箱的FPGA芯片,验证其设计的正确性。

1 、设计任务及要求设计一个出租车计价器,要求显示里程和金额。

(1)出租车启动和停驶由司机控制;(2)行程小于基本里程时,显示起步价,基本里程设3公里,起步价设5元;(3)行程大于基本里程时,每多行一公里,在起步价上加2元;(4)当出租车等待时,由司机按下等候键,每等待一分钟加1元,不足一分钟的按一分钟计算;(5)此处用脉冲信号模拟轮胎的转数,设每计一个脉冲汽车前进100米,系统中所需脉冲均由50MHz晶振分频提供。

2、设计原理及总体框图(1)设计总体框图图1.总设计框图(2)设计总原理图图2.设计总原理图设计总原理:测控FPGA芯片通过采集速度传感器脉冲信号WCLK进行行驶里程计算,利用外部脉冲信号CLK1产生标准时钟信号,用来计算等待时间,最后根据行驶里程、等待时间来计算计价值。

并用译码电路显示行驶里程、等待时间和计价值。

3、程序设计1.VHDL语言简单介绍VHDL 的英文全名是Very High Speed Integrated Circuit Hardware Description Language,即超高速集成电路硬件描述语言,被认为是标准的硬件描述语言,有专家认为,在新世纪中,VHDL与Verilog HDL语言将承担起几乎全部的数字系统设计任务。

VHDL 主要用于描述数字系统的结构、行为、功能和接口。

除了含有许多具有硬件特征的语句外,VHDL 的语言形式和描述风格与句法十分类似于一般的计算机高级语言。

基于Verilog HDL的出租车计费器设计

李明洪基于Verilog HDL的出租车计费器设计基于Verilog HDL的出租车计费器设计学生姓名:李明洪指导老师:肖红光摘要本次课程设计主要是基于FPGA芯片,使用硬件描述语言Veriloh HDL,采用“自顶向下”的设计方法,编写一个出租车计费器芯片,并使用Max+Plus II软件仿真平台。

本文主要描述了出租车计费器的设计思路与模块划分。

把出租车计费器划分为五大模块,共同实现了出租车计费以及预置和模拟汽车启动、停止、暂停等功能,并动态扫描显示车费数目。

最后,使用Max+Plus II仿真平台对每个模块和主程序分别进行了仿真,并对仿真出来的波形作了分析。

关键词出租车计费;Verilog HDL;Max+Plus II;仿真The design of taxi meter based onVerilog HDLAbstract The course design is mainly based on FPGA chip, the use of hardware description language Veriloh HDL, using "top down " design method, the preparation of a taxi meter chip, and use the Max + Plus II software simulation platform. This paper describes the design idea of the taxi meter and module division. The taxi meter is divided into five modules together to achieve a taxi and analog auto billing and pre-start, stop, pause function, and dynamic scan showed the number of fare. Finally, using Max + Plus II simulation platform and the main program for each module were simulated, and the simulation from an analysis of the waveform.Keywords Taxi charges;Verilog HDL;Max+Plus II;Simulation1 引言随着中国城市化的快速发展,人们出行的选择也会越来越多样化,但是出租车作为一种重要的交通工具,也越来越多的被人们所选择,虽然在大中城市,出租车已经相当普及,但是在一些小的城市,出租车行业也因为城市化进程的加快而快速发展。

基于FPGA的出租车计费系统设计

www�ele169�com | 5电子电路设计与方案0 引言FPGA(Field Programmable Gate Array)是在PAL、GAL 等可编程器件的基础上进一步发展的产物。

FPGA 由可编程逻辑功能块、片内互联线、输入输出块构成,通过修改布线实现可编程。

可使用框图或者Verilog HDL 来设计FPGA,Verilog HDL 推出已经有 20 多年,拥有广泛的设计群体,成熟的资源比 VHDL 丰富,因此本次设计采用 Verilog HDL 语言。

而出租车是日常出行中必不可少的交通工具,基于出租车的附属品市场前景也是十分广阔。

本文基于FPGA 设计模拟了一款出租车计费系统,具有开发周期短,设计灵活等优势[1]。

1 FPGA 片内逻辑总体结构设计■1.1 开发工具本次设计中 FPGA 型号为 Xilinx 公司的 spartan-6 系列的 xc6slx-2ftg256 型号。

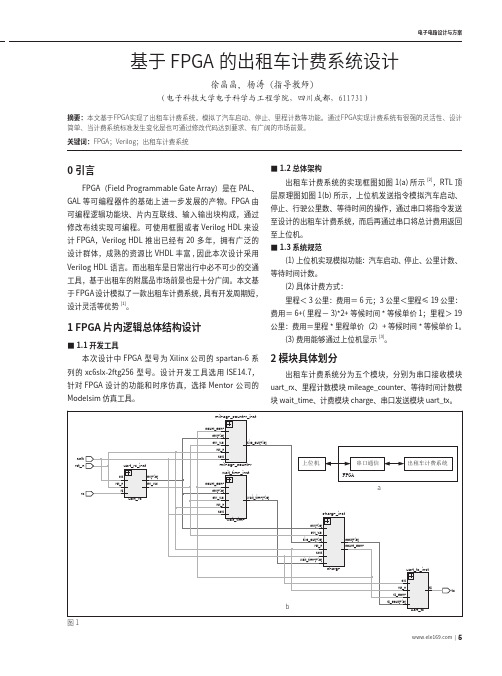

设计开发工具选用 ISE14.7,针对FPGA 设计的功能和时序仿真,选择 Mentor 公司的■1.2 总体架构出租车计费系统的实现框图如图1(a)所示[2],RTL 顶层原理图如图1(b)所示,上位机发送指令模拟汽车启动、停止、行驶公里数、等待时间的操作,通过串口将指令发送至设计的出租车计费系统,而后再通过串口将总计费用返回至上位机。

■1.3 系统规范(1) 上位机实现模拟功能:汽车启动、停止、公里计数、等待时间计数。

(2) 具体计费方式:里程<3公里:费用=6元;3公里<里程≤19公里:费用=6+(里程-3)*2+等候时间*等候单价1;里程>19公里:费用=里程*里程单价(2)+等候时间*等候单价1。

(3) 费用能够通过上位机显示[3]。

2 模块具体划分出租车计费系统分为五个模块,分别为串口接收模块uart_rx、里程计数模块mileage_counter、等待时间计数模基于FPGA 的出租车计费系统设计徐晶晶,杨涛(指导教师)(电子科技大学电子科学与工程学院,四川成都,611731)摘要:本文基于FPGA实现了出租车计费系统,模拟了汽车启动、停止、里程计数等功能。

基于FPGA的出租车计程计费器项目教学设计

基于FPGA的出租车计程计费器项目教学设计一、项目背景计程车是城市交通中广泛存在的一种公共交通工具。

而计程车计价器则是计程车为乘客计价而使用的计量设备。

为了更好地实现计程车计价的准确性,本项目选取FPGA为开发平台,利用FPGA高速计算的特性,开发一个基于FPGA的出租车计程计费器。

二、项目设计1. 系统功能与架构本项目基于FPGA开发,主要由以下模块组成:(1)时钟模块:利用FPGA内置的PLL模块产生稳定的时钟信号。

(2)计时模块:利用时钟信号进行计时并输出当前时间。

(3)里程计算模块:监测车速并根据时间和车速信息计算行驶里程。

(4)费用计算模块:利用里程和起步价、里程单价等信息计算应收费用。

(5)LCD显示模块:将最终计费结果显示在LCD屏幕上。

2. 系统接口设计本项目需要与计费器外部的以下设备进行连接:(1)车速传感器:用于监测车速信息。

(2)计价器外部按钮/旋钮:用于设置起步价、里程单价等信息。

系统的流程主要包括以下步骤:(1)启动计程计费器,并设置起步价、里程单价等参数。

(2)开始计费器计价服务。

(4)根据设定的计价方式计算应收费用。

三、项目实现1. 硬件实现本系统的硬件部分主要包括FPGA芯片、LCD显示屏、车速传感器等。

其中,车速传感器通过FPGA的GPIO接口连接,LCD显示屏通过FPGA的SPI接口连接。

四、教学思路本项目适用于FPGA开发的初学者,重点在于让学生掌握FPGA芯片的使用方法和Verilog HDL语言的应用。

教学流程如下:(1)FPGA基础知识介绍介绍FPGA发展历程、FPGA基础结构、FPGA的编程思想等。

(2)FPGA开发环境构建介绍FPGA开发环境的构建方法,包括开发软件的安装、设备库文件的导入等。

(3)Verilog HDL语言基础介绍Verilog HDL语言的基本语法、数据类型、运算符、语句等。

(4)计程计费器项目开发按照项目设计,在FPGA开发环境中逐步搭建计程计费器系统,并进行相应的调试和优化。

基于FPGA的出租车计价器系统的设计【开题报告】

开题报告电气工程及其自动化基于FPGA的出租车计价器系统的设计一、综述本课题国内外研究动态,说明选题的依据和意义1. 选题的背景和意义我国在70年代开始出现出租车,但那时的计费系统大都是国外进口不但不够准确,价格还十分昂贵。

随着改革开放日益深入,出租车行业的发展势头已十分突出,国内各机械厂家纷纷推出国产计价器。

出租车计价器的功能从刚开始的只显示路程(需要司机自己定价,计算后四舍五入),到能够自主计费,以及现在的能够打发票和语音提示、按时间自主变动单价等功能。

随着城市旅游业的发展,出租车行业已成为城市的窗口,象征着一个城市的文明程度。

现在各大中城市出租车行业都已普及自动计价器,所以计价器技术的发展已成定局。

而部分小城市尚未普及,但随着城市建设日益加快,象征着城市面貌的出租车行业也将加速发展,计价器的普及也是毫无疑问的,所以未来汽车计价器的市场还是十分有潜力的[1]2.国内外研究动态该课题已经是一个相对成熟的课题,此前有过很多人在此方面针对租出车计价器系统做过不同的设计,通过不同的方式,包括用单片机,用ARM,和可编程逻辑器件来设计实现完成过这一课题。

而此次选做的毕业课题是“基于CPLD/FPGA的租出车计价器”,利用现在已经很成熟的可编程逻辑器件来实现这一计费系统,相对用51单片而言,会比较简单,这也同样体现出EDA技术上的优势。

其最突出的地方表现在最具先打电子设计技术特征的功能是日益强大的逻辑设计仿真测试技术。

同时能将所有设计环节纳入统一的自顶向下的设计方案中。

基于EDA技术上的种种优势,他人在选有关此课题时,首先选用的方案是基于EDA技术的CPLD或者FPGA。

这个课题可以有两种解决的方案,一个是基于单片机,另一个是基于FPGA。

对于单片机方案的计费系统是相对传统的计费方式,目前市场上使用的出租车计价器主要采用的都是利用89C51 单片机实现的计价器设计,显示方式上主要采用的是固定显示内容的LED 显示。

基于FPGA的出租车计费器的设计

基于FPGA的出租车计费器的设计目录一、实现功能概述 (2)1、基本功能 (2)2、扩展功能 (2)3、实现功能附图 (2)3.1 下载到DE0 (2)3.2 VGA显示部分 (3)二、模块设计 (4)1、基本功能模块 (4)1.1 模块图 (4)1.2 工作流程图 (5)2、VGA显示模块 (6)2.1 VGA显示原理 (6)2.2 VGA时序分析 (6)三、模块代码解析 (7)1、顶层模块(taxi.bdf) (7)2、里程计数器模块(distans_count.v) (8)3、时间计数模块(time_count.v) (9)4、控制模块(select_clk.v) (10)5、计费器模块(fee_count.v) (10)6、七段译码模块(divided_frequency.v) (11)7、切换模块(choose.v) (12)8、VGA显示模块(DE0_VGA.V、VGA_Ctrl.v、VGA_CLK.v、VGA_Pattern.v) (13)8.1 DE0_VGA.V (13)8.2 VGA_Ctrl.v (15)8.3 VGA_CLK.v (18)8.4 VGA_Pattern.v (20)一、实现功能概述1、基本功能●当行程不超过3km,且等待时间不超过两分钟时,按照出租车起步价(10元)计费。

●当行程超过3km时,按照2元/公里累加计费。

●当等待时间累计超过两分钟,按照1元/公里累加计费。

2、扩展功能●下载到DE0板子上,数码管显示时间、路程和费用。

计费器显示范围为0~999元,分辨率为1元;计程器显示范围为0~99km,分辨率为1km;计时器显示范围为0~59分钟,分辨率为1分钟。

●利用DE0板子上的VGA显示器接口做VGA动态实时显示计费状态及各个使能信号的状态,并且利用小车动画来直观的反映出出租车行驶火车停车等待的状态。

(在模块设计中有相应的附图)3、实现功能附图3.1 下载到DE0数码管计费数码管计里程及时间3.2 VGA显示部分VGA同步显示时间及里程、小车状态及按键状态VGA同步显示费用、小车状态及按键状态二、模块设计1、基本功能模块1.1 模块图等待时间计数模块行驶路程计数模块控制模块计费模块显示模块(数码管部分)时钟1.2 工作流程图基本模块的工作流程概述:出租车载客后,启动计费器,整个系统开始运行,进入初始化状态,即计程和计时从零开始,计费器从起步价10元开始。

基于FPGA出租车计费器设计报告(verilog)

出租车计费器一实验任务及要求1.能实现计费功能,计费标准为:按行驶里程收费,起步费为10.00元,并在车行3公里后再按2元/公里,当计费器计费达到或超过一定收费(如20元)时,每公里加收50%的车费,车停止不计费。

2.实现预置功能:能预置起步费、每公里收费、车行加费里程。

3.实现模拟功能:能模拟汽车启动、停止、暂停、车速等状态。

4.设计动态扫描电路:将车费显示出来,有两位小数。

5.用VHDL语言设计符合上述功能要求的出租车计费器,并用层次化设计方法设计该电路。

6.各计数器的计数状态用功能仿真的方法验证,并通过有关波形确认电路设计是否正确。

7. 完成电路全部设计后,通过系统实验箱下载验证设计的正确性。

计费器按里程收费,每100米开始一次计费。

各模块功能如下:(1) 车速控制模块当起停键为启动状态时(高电平),模块根据车速选择和基本车速发出响应频率的脉冲驱动计费器和里程显示模块进行计数;当处于停止状态时暂停发出脉冲,此时计费器和里程显示模块相应的停止计数。

(2) 里程动态显示模块其包括计数车速控制模块发出的脉冲以及将计数显示动态显示出来,每来一个脉冲里程值加0.1(控制器每发一个脉冲代表运行了0.1公里)。

(3) 计费动态显示模块其初值为10元,当里程超过3公里后才接受计数车速控制模块发出的脉冲的驱动,并且计数显示动态显示出来,每来一个脉冲(代表运行了0.5公里)其数值加1元,当收费超过20时数值加1.5元。

三实验报告要求1.画出顶层原理图;2.用VHDL语言设计各子模块;3.叙述各子模块和顶层原理图的工作原理;4.给出各模块和顶层原理图的仿真波形图;5.给出硬件测试流程和结果。

四:设计说明:实际设计共五个模块,分别为分频模块(每一百米送一个脉冲以方便计数)、计算里程模块、里程取整模块(不足一公里的按一公里算)、计费模块、显示模块。

详细功能如下:1、分频模块:假设车轮每转一圈为2米,送一个脉冲,则需要50分频(共100米),同理,若知道车轮直径,即可算出分频比2、里程模块:每一百米记一次数,最大可以计999.9公里,精确到0.1公里。

FPGA实验报告

大连理工大学城市学院FPGA实验报告学院:电子与自动化学院专业:电子信息工程学生:张凌飞指导教师:王颖完成日期: 2013年4月13日大连理工大学城市学院实验报告基于Verilog语言的出租车计费器第一章引言1.1 出租车计费器介绍随着出租车行业的发展,对出租车计费器的要求也越来越高。

最近几年出租车行业发展迅速,在全国有几千家出租车公司。

因此出租车计费器市场是庞大的。

而出租车计费器成为不可缺少的一部分。

信息社会的现代电子产品,性能越来越高,复杂度越来越大,更新步伐也越来越快。

实现这种进步的主要原因就是微电子技术和电子技术的发展。

而电子技术的发展后者的核心就是电子设计自动化技术。

EDA 是指以计算机为工作平台,融合了应用电子技术、计算机技术、智能化技术的最新成果而开发出的电子CAD通用软件包,它根据硬件描述语言HDL完成的设计文件,自动完成逻辑编译、化简、分割、综合、优化、布局布线及仿真,直至完成对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

没有EDA技术的支持,想要完成超大规模集成电路的设计制造是不可想象的;反过来,生产制造技术的不断进步又必将对EDA技术提出新的要求。

本文采用verilog语言来设计实现出租车计费系统,经过ModelSim和Quartus仿真将其实例化。

如果将该设计再结合到实际应用中,那么,只需改变设计中计费要求,就可以应用到出租车上。

另外,如果再任意输入该出租车计价器的计费标准,那么,它的适用范围可能就更广泛了。

第二章出租车计费器设计原理2.1出租车计费器设计要求(1)行程3公里内(包括3公里),且等待累计时间2分钟内(包括2分钟),起步费为6.0元;(2)3公里外(不包括3公里)以每公里1.0元,等待累计时间2分钟外(不包括2分钟)以每分钟以1.0元计费。

(3)能显示行驶公里数、等待累计时间和最后的总费用。

本计费器的显示范围为0~99元,计价分辨率为1元;计程器显示范围为0~99公里,分辨率为1公里;计时器的显示范围是分钟的显示范围是0—99,辨率为1分钟。

基于FPGA出租车计价器设计

题目:基于FPGA出租车计价器设计装订线基于FPGA出租车计价器的设计摘要本文介绍了一种采用可编程逻辑器件(FPGA/CPLD)进行出租车计价器的设计思想以及实现方法。

FPGA是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

另一方面采用可编程逻辑器件设计,外围电路简单,模块化设计方便,原理清晰,速度快,功能强,可靠性高,灵活性强,并且完成和扩展附加功能性强。

本设计实现了出租车计价器所需的一些基本功能,如计程、计时、计费、动态显示,其中计费金额包括起步价、里程计费、等待计时计费。

该设计采用模块化设计,自顶向下,在Quartus II9.0软件平台下,采用Verilog HDL 硬件描述语言分别设计了分频模块、计程模块、计费模块、计时模块,译码以及动态扫描显示模块的出租车计价器的五大模块,用原理图设计了顶层模块,对每个模块和主程序分别进行了仿真,并对仿真波形作了分析。

经过硬件下载验证,完成了出租车计价器分频模块、计程模块、计费模块、计时模块,译码以及动态扫描显示模块的设计实现。

关键词:FPGA;出租车计价器;Quartus II;Verilog HDLBased on the FPGA Design of Taxi MeterABSTRACTThis article describes the design ideas and methods of the taximeter, through the programmable logic device (FPGA/CPLD). Using programmable logic devices design on the other hand, peripheral circuit is simple, convenient modular design, the principle is clear, fast, strong function, high reliability, strong flexibility, and complete and additional functional extension. This design has realized the taxi meter required some basic functions, such as log, timing, pricing, dynamic display, billing amount fare and mileage charging, waiting for the timing. Through the Quartus II 9.0 Software Platform,using Verilog HDL language completed the description and simulation of frequency module, the meter module, Billing module, timing modules, decoding, dynamic scanning display module,for each module are simulated respectively and top-level module with schematic design , the simulation waveform were analyzed. After download validation hardware, completed the taxi meter divider module, log module, billing module, timing module, decoding and dynamic scanning display modules designed to achieve.Keywords: FPGA;Taximeter;Quartus II;Verilog HDL目录1 前言 (1)1.1 课题的来源及意义 (1)1.2 国内外发展状况 (1)1.3 研究的手段及目标 (2)2 总体方案设计 (3)2.1 方案论证与选择 (3)2.2 设计思想及原理 (4)3 FPGA、Verilog及QuartusⅡ开发环境的介绍 (6)3.1 现场可编程门阵列FPGA (6)3.2 硬件描述语言Verilog HDL (6)3.3 QuartusⅡ开发环境 (7)4 设计与仿真验证 (8)4.1 分频模块 (8)4.1.1 计程分频模块 (8)4.1.2 计时分频模块和计费分频模块 (9)4.1.3 数码管动态显示模块 (9)4.1.4 数码管动态显示模块仿真 (9)4.2 计程模块 (10)4.2.1 计程模块电路 (10)4.2.2 计程模块仿真 (12)4.3 计时模块 (12)4.3.1 计时模块电路 (12)4.3.2 计时模块仿真 (13)4.4 计费模块 (14)4.4.1 计费模块电路 (14)4.4.2 计费模块仿真 (15)4.5 数码管显示模块 (16)4.5.1 数码管显示模块电路 (16)4.5.2 数码管显示仿真 (17)4.6 整体顶层模块设计电路 (17)4.7 下载实现 (20)5 结论 (23)参考文献 (24)致谢 (24)附录 (25)1 前言1.1 课题的来源及意义本课题是在老师指导下,根据学校教学的需求和实际需要而开发的研究项目。

基于FPGA的出租车计费系统设计

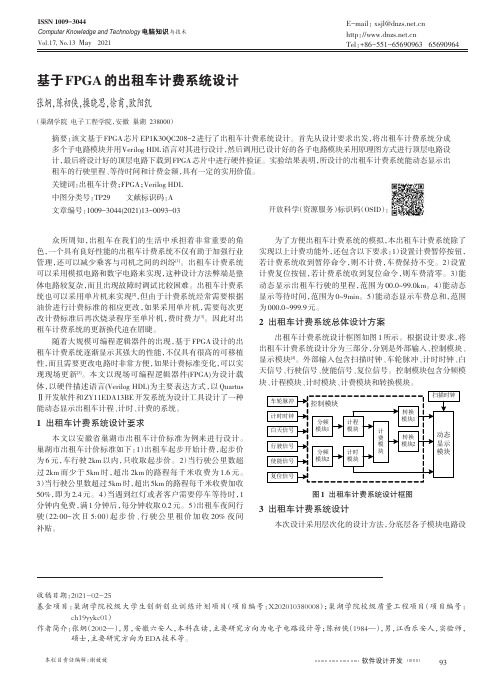

软件设计开发本栏目责任编辑:谢媛媛基于FPGA 的出租车计费系统设计张炯,陈初侠,操晓思,徐甫,欧阳凯(巢湖学院电子工程学院,安徽巢湖238000)摘要:该文基于FPGA 芯片EP1K30QC208-2进行了出租车计费系统设计。

首先从设计要求出发,将出租车计费系统分成多个子电路模块并用Verilog HDL 语言对其进行设计,然后调用已设计好的各子电路模块采用原理图方式进行顶层电路设计,最后将设计好的顶层电路下载到FPGA 芯片中进行硬件验证。

实验结果表明,所设计的出租车计费系统能动态显示出租车的行驶里程、等待时间和计费金额,具有一定的实用价值。

关键词:出租车计费;FPGA ;Verilog HDL 中图分类号:TP29文献标识码:A文章编号:1009-3044(2021)13-0093-03开放科学(资源服务)标识码(OSID ):众所周知,出租车在我们的生活中承担着非常重要的角色,一个具有良好性能的出租车计费系统不仅有助于加强行业管理,还可以减少乘客与司机之间的纠纷[1]。

出租车计费系统可以采用模拟电路和数字电路来实现,这种设计方法弊端是整体电路较复杂,而且出现故障时调试比较困难。

出租车计费系统也可以采用单片机来实现[2],但由于计费系统经常需要根据油价进行计费标准的相应更改,如果采用单片机,需要每次更改计费标准后再次烧录程序至单片机,费时费力[3]。

因此对出租车计费系统的更新换代迫在眉睫。

随着大规模可编程逻辑器件的出现,基于FPGA 设计的出租车计费系统逐渐显示其强大的性能,不仅具有很高的可移植性,而且需要更改电路时非常方便,如果计费标准变化,可以实现现场更新[3]。

本文以现场可编程逻辑器件(FPGA)为设计载体,以硬件描述语言(Verilog HDL)为主要表达方式,以Quartus Ⅱ开发软件和ZY11EDA13BE 开发系统为设计工具设计了一种能动态显示出租车计程、计时、计费的系统。

基于fpga的出租车计费系统设计原理

基于fpga的出租车计费系统设计原理下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!基于FPGA的出租车计费系统设计原理引言在现代城市交通中,出租车作为一种重要的交通工具,其计费系统的设计对于保障乘客权益、提高交通效率具有重要意义。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

出租车计费器一实验任务及要求1.能实现计费功能,计费标准为:按行驶里程收费,起步费为10.00元,并在车行3公里后再按2元/公里,当计费器计费达到或超过一定收费(如20元)时,每公里加收50%的车费,车停止不计费。

2.实现预置功能:能预置起步费、每公里收费、车行加费里程。

3.实现模拟功能:能模拟汽车启动、停止、暂停、车速等状态。

4.设计动态扫描电路:将车费显示出来,有两位小数。

5.用VHDL语言设计符合上述功能要求的出租车计费器,并用层次化设计方法设计该电路。

6.各计数器的计数状态用功能仿真的方法验证,并通过有关波形确认电路设计是否正确。

7. 完成电路全部设计后,通过系统实验箱下载验证设计的正确性。

计费器按里程收费,每100米开始一次计费。

各模块功能如下:(1) 车速控制模块当起停键为启动状态时(高电平),模块根据车速选择和基本车速发出响应频率的脉冲驱动计费器和里程显示模块进行计数;当处于停止状态时暂停发出脉冲,此时计费器和里程显示模块相应的停止计数。

(2) 里程动态显示模块其包括计数车速控制模块发出的脉冲以及将计数显示动态显示出来,每来一个脉冲里程值加0.1(控制器每发一个脉冲代表运行了0.1公里)。

(3) 计费动态显示模块其初值为10元,当里程超过3公里后才接受计数车速控制模块发出的脉冲的驱动,并且计数显示动态显示出来,每来一个脉冲(代表运行了0.5公里)其数值加1元,当收费超过20时数值加1.5元。

三实验报告要求1.画出顶层原理图;2.用VHDL语言设计各子模块;3.叙述各子模块和顶层原理图的工作原理;4.给出各模块和顶层原理图的仿真波形图;5.给出硬件测试流程和结果。

四:设计说明:实际设计共五个模块,分别为分频模块(每一百米送一个脉冲以方便计数)、计算里程模块、里程取整模块(不足一公里的按一公里算)、计费模块、显示模块。

详细功能如下:1、分频模块:假设车轮每转一圈为2米,送一个脉冲,则需要50分频(共100米),同理,若知道车轮直径,即可算出分频比2、里程模块:每一百米记一次数,最大可以计999.9公里,精确到0.1公里。

3、取整模块:现实中出租车的精确度为0.1公里,计算价格的时候不足一公里的按一公里算,所以加了这一个模块,输出的是计算价格时的里程数。

4、计费模块:按行驶里程收费,起步费为11.00元(包括1元得燃油附加费),并在车行3公里后再按2元/公里,当计费器计费达到或超过一定收费(20元)时,每公里加收50%的车费,车停止不计费。

5、显示模块:通过动态扫描显示车费和里程数,将十进制数转化为四位十进制数(如将9999转化为四个9)以方便显示设计流程图如下流程说明:车轮每转一圈送一个脉冲波,假设每转一圈为2米,则经过50分频器后是每100米送一个脉冲到里程计算模块,里程计算模块可以精确到0.1公里,将计算的里程数送至取整模块进行判断,若小数部分不为零则整数部分加1,即不足一公里的部分按一公里计算,取整后的里程送至计费模块计费,同时和计算的费用用过显示模块进行转化和显示顶层原理图如下:五、实验结果:通过maxplusII将sof文件下载到试验箱上,运行正常,与实验目的一致,可以通过调整输入的脉冲频率来调整计费的速度。

初始价格为11元,超过3公里每公里加收2元,价格超过20每公里3元。

六、一些问题和改进:总的来说本次试验是顺利的,过程中主要遇到了这几点问题:1、刚开始没有完全想好要用几个模块做,没画好流程图,所以模块数量显得有点多,许多模块显得有些不必要,如取整模块完全可以合并到计费模块中。

2、对其中的管脚定义太过于随意,造成很大空间的浪费,而且在使用较早的芯片时出现管脚不足的现象,这和模块过多也有很大关系。

一些改进的想法:1、在本次设计中,假设车轮每转一圈为2米,刚好50分频,但是显然现实中不会刚好每圈2米,极可能出现有小数的分频,所以分频器需要改进,或者使用其他模块使得没100送一个脉冲。

2、将里程数送到显示模块时,已经是经过取整,所以没有小数部分,但是里程模块的小数部分又不能和整数部分一起送到显示模块进行转化,所以需要想办法将小数和整数部分合并且不影响取整。

3、可以再加上按时间收费的模块以便出租车在较长时间等待的过程中也能计费附:程序清单1、module FDIV ( CLK, K); //分频器设计input CLK ;output K ;reg[12:0] count ; reg M1 ;parameter ratio=50 ; //定义分频比为50,若是不同规格的轮胎,调整此参数always @(posedge CLK)beginif (count==ratio-1) count<=0 ; else count<= count+1 ;if (count==0) M1 <= ~M1; e lse if (count==ratio/2) M1 <= ~M1 ;endassign K=M1 ;endmodule2、module Mileage ( CLK,RST,Mile_int,Mile_dec ) ; //里程模块input CLK,RST ;output [12:0] Mile_int ;output[3:0] Mile_dec ; //定义小数和整数的里程以便取整reg [3:0] count1 ; reg [12:0] count2 ;always @(posedge CLK or posedge RST)beginif(RST) begin count1<=0 ; count2<=0 ; end //里程清零else if (count1==9) begin count1<=0 ;count2<=count2+1 ; end else count1 <= count1+1 ; //每一个脉冲小数里程加1,满十后整数部分加1endassign Mile_dec=count1 ; assign Mile_int=count2 ;endmodule3、module quzheng ( M_int,M_dec,Mile ) ; //取整模块input [12:0] M_int ; //输入的里程整数input [3:0] M_dec ; //输入的里程小数output [12:0] Mile ;reg [12:0] Mile ;always @ ( M_int,M_dec )beginif (M_dec !=0) Mile <= M_int+1 ; //不满一公里的,按一公里计算,即整数部分加一else Mile <= M_int ; //为零则整数不变endendmodule4、module Fare ( CLK,RST,Mile,T_fare ) ; //计费模块parameter S_price=10 , Fuel=1; //起步价10元,燃油附加费1元input CLK,RST ;input [12:0]Mile ; //取整后的里程输入output [12:0] T_fare ; //总的车费reg [12:0] Q1 ;always @ (posedge CLK or posedge RST)beginif(RST) Q1<=0 ;else if(Mile<=3) Q1 <= S_price+Fuel ; //小于3公里,起步价11元else if(Q1<20) Q1 <= S_price+Fuel+2*(Mile-3) ; //大于11小于20元每公里加收2元else Q1 <= S_price+Fuel+3*(Mile-3) ;//大于20元每公里加收3元endassign T_fare = Q1 ;endmodule5、显示模块module deceder (scan,seg7,dp,clk20mhz,money_in,distance_in);output[7:0] scan; //数码管地址选择信号output[6:0] seg7; //7段显示控制信号output dp; //小数点input clk20mhz; //系统时钟20MHZinput [12:0] money_in; //车费input [12:0] distance_in; //路程reg[7:0]scan;reg[6:0]seg7;reg dp;reg clk1khz; //1KHZ分频时钟,用于扫描数码管地址reg[3:0] data;reg[3:0] m_one,m_ten,m_hun,m_tho; //车费钱数的4位十进制表示reg[3:0] d_one,d_ten,d_hun,d_tho; //路程的4位十进制表示reg[15:0] count ;reg[15:0]comb1;reg[3:0]comb1_a,comb1_b,comb1_c,comb1_d;reg[15:0] comb2;reg[3:0]comb2_a,comb2_b,comb2_c,comb2_d;reg[2:0] cnt;//1khz分频,用于扫描数码管地址always@(posedge clk20mhz)beginif(count==1'd10000)begin clk1khz<=~clk1khz;count<='d0;end elsebegin count<=count+1;end//将车费转化为4位十进制数if(comb1<money_in)beginif (comb1_a=='d9&&comb1_b=='d9&&comb1_c=='d9) begincomb1_a<='b0000;comb1_b<='b0000;comb1_c<='b0000;comb1_d<=comb1_d+1;comb1<=comb1+1;endelse if(comb1_a=='d9&&comb1_b=='d9)begincomb1_a<='b0000;comb1_b<='b0000;comb1_c<=comb1_c+1;comb1<=comb1+1;endelse if(comb1_a=='d9)begincomb1_a<='b0000;comb1_b<=comb1_b+1;comb1<=comb1+1;endelsebegincomb1_a<=comb1_a+1;comb1<=comb1+1;endendelse if (comb1==money_in)beginm_one<=comb1_a;m_ten<=comb1_b;m_tho<=comb1_d;endelse if (comb1>money_in)begincomb1_a<='b0000;comb1_b<='b0000;comb1_c<='b0000;comb1_d<='b0000;comb1<='d0;end//将路程转化为4位十进制数if(comb2<distance_in)beginif (comb2_a=='d9&&comb2_b=='d9&&comb2_c=='d9)begincomb2_a<='b0000;comb2_b<='b0000;comb2_c<='b0000;comb2_d<=comb2_d+1;comb2<=comb2+1;endelse if(comb2_a=='d9&&comb2_b=='d9)begincomb2_a<='b0000;comb2_b<='b0000;comb2_c<=comb2_c+1;comb2<=comb2+1;endelse if(comb2_a=='d9)begincomb2_a<='b0000;comb2_b<=comb2_b+1;comb2<=comb2+1;endelsebegincomb2_a<=comb2_a+1;comb2<=comb2+1;endendelse if (comb2==distance_in)begind_ten<=comb2_b;d_hun<=comb2_c;d_tho<=comb2_d;endelse if (comb2>distance_in)begincomb2_a<='b0000;comb2_b<='b0000;comb2_c<='b0000;comb2_d<='b0000;comb2<='d0;endend// 数码管动态扫描always@(posedge clk1khz)begincnt=cnt+1;endalways@(cnt)begincase(cnt)'b000:begin data<=m_one;dp<='d0;scan<='b00000001;end 'b001:begin data<=m_ten;dp<='d0;scan<='b00000010;end 'b010:begin data<=m_hun;dp<='d1;scan<='b00000100;end 'b011:begin data<=m_tho;dp<='d0;scan<='b00001000;end 'b100:begin data<=d_one;dp<='d0;scan<='b00010000;end 'b101:begin data<=d_ten;dp<='d0;scan<='b00100000;end 'b110:begin data<=d_hun;dp<='d1;scan<='b01000000;end 'b111:begin data<=d_tho;dp<='d0;scan<='b10000000;end default:begin data<='bx;dp<='bx;scan<='bx;endendcaseend//7段译码always@(data)begincase(data[3:0])4'b0000:seg7[6:0]=7'b1111110;4'b0001:seg7[6:0]=7'b0110000;4'b0010:seg7[6:0]=7'b1101101;4'b0011:seg7[6:0]=7'b1111001;4'b0100:seg7[6:0]=7'b0110011;4'b0101:seg7[6:0]=7'b1011011;4'b0110:seg7[6:0]=7'b1011111;4'b0111:seg7[6:0]=7'b1110000;4'b1000:seg7[6:0]=7'b1111111;4'b1001:seg7[6:0]=7'b1111011;default:seg7[6:0]=7'b0000000;endcaseendendmodule。