xilinx 新手快速入门的好资料

Xilinx fpga 设计培训中文教程-10_1

在当前源文件进程窗口 点击靠近实现设计进程的 + 以展开该进程 展开布局布线进程 展开生成布局布线后静态时序报告进程 双击布局布线后静态时序报告

图 10b-1. 布局布线后静-XLX-CLAS

Ch.10b-4

? 1. 多少路径约束是失败的 时序错误的数目 本实现的时序积分是多少

图 10b-6. 端口选项卡

实现选项实验

1-877-XLX-CLAS

Ch.10b-8

点击 I/O 配置选项选择框. 一些附加的列将出现在窗口的上部 你也许需要将它们向 右翻以便查看

确定信号名称按照字母顺序排列 如果不是 点击端口名称方框以将这些信号名称按 字母排序

向下翻并点击 rd_data<0>

在当前源文件进程窗口 右击布局布线 Place & Route 性 Properties (图 10b-2)

然后从菜单中选择属

图 10b-2. 当前源文件进程窗口

在进程属性对话框中 点击靠近布局布线尝试级别的方框 一个箭头将出现在方框的 右边 指示着下拉的一系列选项

实现选项实验

1-877-XLX-CLAS

过程

你可以利用给定的约束文件(myucf.ucf)及缺省的软件选项来开始实现一个项目 然后你 可以通过调整进程属性和 I/O 配置选项来改进设计性能 注意 当使用 Toolwire 执行本实验时 所有的软件程序 文件以及项目都放在卷标 U:\ 下面而不是 C:\下面

实现选项实验

1-877-XLX-CLAS

欲退出时序分析器 可以选择下列方法中的一个 选择文件 File → 退出 Exit , 并点击出现的弹出式对话框中的 Yes 点击时序分析器窗口右上角的 X 并点击出现的弹出式对话框中的 Yes

精品课件-Xilinx FPGACPLD设计初级教程-第4章

0z

1z 输

入x

z

zz

使能端

1

x

1 0或z

0 1或z

x

x

x

x

z 0或z 1或z

x x

bufif0 0

01 输1 0 入x x

zz

使能端

1

x

z 0或z

z 1或z

z

x

x

x

z 0或z 1或z

x x

第4章 Verilog HDL程序的描述方式

4.1.2 门级结构描述实例 要描述一位全加器,用Verilog HDL语言门级结构描述的

块中被赋值的变量应定义为reg型

wire s1;

xor x1(s1,a,b);

//调用门元

件

always @(a or b or cin) begin

//always块

语句

第4章 Verilog HDL程序的描述方式

m1 = a & b;

m2 = b & cin;

m3 = a & cin;

cout = (m1| m2) | m3;

第4章 Verilog HDL程序的描述方式

(4) 提供了条件、if-else、case、循环程序结构。 (5) 提供了可带参数且非零延续时间的任务(task)程序 结构。 (6) 提供了可定义新的操作符的函数结构(function)。 (7) 提供了用于建立表达式的算术运算符、逻辑运算符、 位运算符。 在Verilog HDL语言中,一般采用always过程语句来描述 电路的行为特征。例如,用行为描述方式描述4.1节中的一位 全加器有以下三种方式: (1) 一位全加器的行为描述方式一:

0 0或z

ISE10.1快速入门(实例)

ISE10.1快速入门(实例)ISE快速入门(Lab0)——秒表修改记录审核记录目录目录修改记录 (2)审核记录 (2)目录 (3)实验详细步骤 (4)实验详细步骤(一)启动ISE要启动ISE,双击桌面ISE图标或者从开始菜单中启动,依次选择开始?> 所有程序?> Xilinx ISE Design Suit 10.1 ?> ISE ?> Project Navigator,打开ISE工具;(二)创建工程项目(1) 在ISE窗口,依次选择File > New Project... ,然后看到New ProjectWizard窗口弹出(2) 在Project Name中输入clock(3) 在Project Location中浏览选择一个文件夹或者在输入栏中手工输入一个项目存放的路径(不能用中文路径),一个子目录clock会自动生成;(4) 在Top-Level Source Type下拉菜单栏目中图1:新建项目向导(5) 然后点击Next,切换到device properties页面对话框;(6) 在相应栏目中填入属性,具体如下所示:Product Category: All● Family: Spartan3E● Device: XC3S100E● Package:QT144● Speed Grade: -5● Top-Level Module Type: HDL● Synthesis Tool: XST (VHDL/Verilog)● Simulator: ISE Simula tor (VHDL/Verilog)● 确认Enable Enhanced Design Summary 已经被选中其他选项保留默认值完成之后项目设备属性对话框如下图所示:图2:项目设备属性(7) 点击Next,到创建新项目源文件对话框;图3:创建新的源文件(三)创建Verilog 模块源文件(1)在创建新的源文件对话框中点击New Source ,打开New Source Wizard 对话框;(2)在对话框的 Source type 中选择Verilog Module (3)输入模块文件名clock ;(4)确认Add to Project 按钮被选中;图4:选择新建文件类型(5)点击Next,弹出模块端口声明对话框,定义clock模块的端口声明如下:● Clk input● Reset input●Start input● Anodes output MSB:3 LSB:0●Cathodes output MSB:6 LSB:0MSB和LSB代表变量的最高位和最低位,这里Anodes的位宽为4,所以最高位为3,最低位都是0;Cathodes的位宽为7,所以最高位为6,最低位都是0;(6)点击next,检验新source模块文件设置如下图所示:(7)然后点击Finish完成创建新源文件向导;在创建新的源文件的窗口中点击Next(8)点击next,然后点击完成,就会在Workspace中看到包含clock模块的源代码文件,如图所示:(9)继续完成代码模块修改,在endmodule声明之前,添加下行代码到模块中;reg [21:0] Count;reg [3:0] Msec; //0.1sreg [3:0] Sec1; //秒个位reg [3:0] Sec2; //秒十位reg Flag; //0.1s进位标志//0.1s的计数器always @ (posedge Clk) beginif(Reset | (!Start) )Count <= 0;else if(Count == 24000_00) beginFlag <= 1'b1;Count <= 'd0;endelse beginFlag <= 1'b0;Count <= Count + 1'b1;endend//Msec从0计数到9时归零always @ ( posedge Clk ) beginif(Reset | (!Start) )Msec <= 4'h0;else if( Flag && (Msec==9) )Msec <= 4'h0;else if( Flag )Msec <= Msec + 1'b1;end//秒个位从0计数到9时归零always @ ( posedge Clk ) beginif(Reset | (!Start) )Sec1 <= 4'h0;else if( (Sec1==9) && (Msec==9) && Flag ) Sec1 <= 4'h0;else if( (Msec==9) && Flag )Sec1 <= Sec1 + 1'b1;end//秒十位从0计数到9时归零always @ ( posedge Clk ) beginif(Reset | (!Start) )Sec2 <= 4'h0;else if( (Sec2==5) && (Sec1==9) && (Msec==9) && Flag ) Sec2 <= 4'h0;else if( (Sec1==9) && (Msec==9) && Flag )Sec2 <= Sec2 + 1'b1;end//数码管显示控制reg [3:0] Anodes_r;reg [6:0] Cathodes_r;reg [15:0] Count2;//动态显示数码管位选always @ (posedge Clk) beginif(Reset | (!Start) ) beginAnodes_r <= 4'b1110;Count2 <= 0;endelse if(Count2==24000) beginAnodes_r <= {Anodes_r[2:0],Anodes_r[3]};Count2 <= 0;endelse Count2 <= Count2 + 1'b1;end//动态显示数码管段选always @ (posedge Clk) beginif(Reset | (!Start) )Cathodes_r <= 7'b1111111;else case(Anodes_r)4'b1110: begincase(Msec)0: Cathodes_r <= 7'b1000000;1: Cathodes_r <= 7'b1111001;2: Cathodes_r <= 7'b0100100;3: Cathodes_r <= 7'b0110000;4: Cathodes_r <= 7'b0011001;5: Cathodes_r <= 7'b0010010;6: Cathodes_r <= 7'b0000010;7: Cathodes_r <= 7'b1111000;8: Cathodes_r <= 7'b0000000;9: Cathodes_r <= 7'b0010000; default Cathodes_r <= 7'b1111111; endcaseend4'b1101: Cathodes_r <= 7'b0111111; 4'b1011: begincase(Sec1)0: Cathodes_r <= 7'b1000000;1: Cathodes_r <= 7'b1111001;2: Cathodes_r <= 7'b0100100;3: Cathodes_r <= 7'b0110000;4: Cathodes_r <= 7'b0011001;5: Cathodes_r <= 7'b0010010;6: Cathodes_r <= 7'b0000010;7: Cathodes_r <= 7'b1111000;8: Cathodes_r <= 7'b0000000;9: Cathodes_r <= 7'b0010000; default Cathodes_r <= 7'b1111111; endcaseend4'b0111: begincase(Sec2)0: Cathodes_r <= 7'b1000000;1: Cathodes_r <= 7'b1111001;2: Cathodes_r <= 7'b0100100;3: Cathodes_r <= 7'b0110000;4: Cathodes_r <= 7'b0011001;5: Cathodes_r <= 7'b0010010;6: Cathodes_r <= 7'b0000010;7: Cathodes_r <= 7'b1111000;8: Cathodes_r <= 7'b0000000;9: Cathodes_r <= 7'b0010000;default Cathodes_r <= 7'b1111111;endcaseenddefault Cathodes_r <= 7'b1111111;endcaseendassign Anodes = Anodes_r;assign Cathodes = Cathodes_r;(10)选择File > Save保存所有修改;现在你已经完成了创建clock模块的工作。

Xilinx学习资料

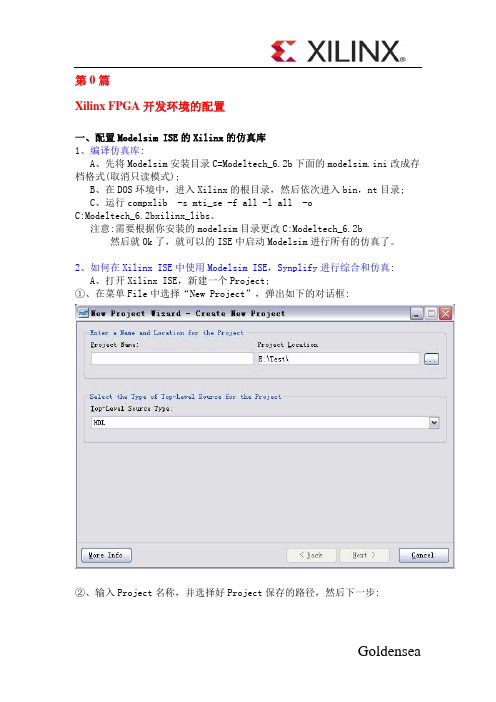

第0篇Xilinx FPGA开发环境的配置一、配置Modelsim ISE的Xilinx的仿真库1、编译仿真库:A、先将Modelsim安装目录C=Modeltech_6.2b下面的modelsim.ini改成存档格式(取消只读模式);B、在DOS环境中,进入Xilinx的根目录,然后依次进入bin,nt目录;C、运行compxlib -s mti_se -f all -l all -oC:Modeltech_6.2bxilinx_libs。

注意:需要根据你安装的modelsim目录更改C:Modeltech_6.2b 然后就Ok了,就可以的ISE中启动Modelsim进行所有的仿真了。

2、如何在Xilinx ISE中使用Modelsim ISE,Synplify进行综合和仿真:A、打开Xilinx ISE,新建一个Project;①、在菜单File中选择“New Project”,弹出如下的对话框:②、输入Project名称,并选择好Project保存的路径,然后下一步:字串3按照上边的参数进行设置(针对于Spatan 3E的开发板),然后单击下一步,进入到后面的界面:③、单击“New Source”按钮,并按照下面的设置来操作:④、参照下面的参数,进行设置,然后一直选择默认选项,一直到完成。

最后生成的项目界面如下图所示:B、输入代码,然后用Synplify综合:①、参考代码:entity Count iSPort(CLK :in STD_LOGIC;RESET :in STD_LOGIC;LOAD :in STD_LOGIC;DATA IN:in STD_LOGIC_VECTOR(3 downto 0);字串9Qout :out STD_LOGIC_VECTOR(3 downto 0));end Count;architecture Behavioral of Count issignal tmpCount:STD_LOGIC_VECTOR(3 downto 0);beginprocess(CLK,RESET,LOAD)beginif RESET='1' thentmpCount<="0000";elseif LOAD='1' thentmpCount<=DATA_IN;elsif CLK'event and CLK='1' thentmpCount<=tmpCount+1;end if;end if;end process; 字串6Qout<=tmpCount:end Behavioral;②、双击Processes窗口里面的“Synthesize-Synplify”进行综合③、在“Transcript”窗口中的可以看到综合的信息。

精品课件-Xilinx FPGACPLD设计初级教程-第1章

第1章 PLD概述

2) 现场可编程门阵列(Field Programmable Gate Array, FPGA)

FPGA是在PAL、GAL、PLD等可编程器件的基础上进一步发 展的产物。它是作为专用集成电路(ASIC)领域中的一种半定 制电路出现的,既解决了定制电路的不足,又克服了原有可编 程器件门电路数有限的缺点。FPGA采用了逻辑单元阵列 LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻 辑模块CLB(Configurable Logic Bolck)、输入/输出模块 IOB(Input Output Block)和内部连线(Interconnect)三个部 分。可以说,FPGA芯片是小批量系统提高系统集成度、可靠 性的最佳选择之一。

CPLD是从PAL和GAL器件发展起来的,相对而言规模大, 结构复杂,属于大规模集成电路范围。CPLD也是当前另一主 流的PLD器件。

第1章 PLD概述

现在PLD器件仍向着高密度、高速度、低功耗的方向发展。 特别是FPGA器件,现在它的集成度已经不能和以前的FPGA相 提并论。另外,由于专用集成电路(ASIC)芯片设计具有周期 长、难点多、耗资大等缺点,因此用PLD器件来代替一般的 ASIC芯片进行设计已经成为一种发展趋势。

3) 可编程阵列逻辑(Programmable Array Logic,PAL) PAL是20世纪70年代末由MMI公司率先推出的一种可编程 逻辑器件。它采用双极型工艺制作,并采用熔丝编程方式。 PAL器件由可编程的与逻辑阵列、固定的或逻辑阵列和输出电 路三部分组成。通过对与逻辑阵列编程可以获得不同形式的组 合逻辑函数。

Xilinx FPGA设计基础(VHDL版)

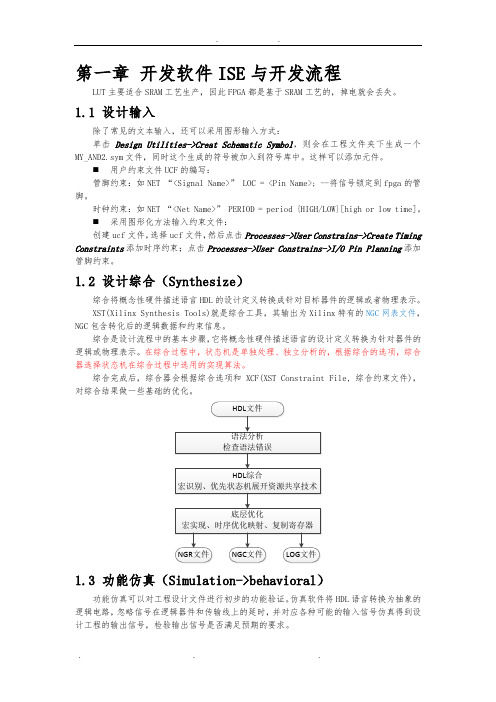

第一章开发软件ISE与开发流程LUT主要适合SRAM工艺生产,因此FPGA都是基于SRAM工艺的,掉电就会丢失。

1.1 设计输入除了常见的文本输入,还可以采用图形输入方式:单击Design Utilities->Creat Schematic Symbol,则会在工程文件夹下生成一个MY_AND2.sym文件,同时这个生成的符号被加入到符号库中。

这样可以添加元件。

⏹用户约束文件UCF的编写:管脚约束:如NET “<Signal Name>” LOC = <Pin Name>; --将信号锁定到fpga的管脚。

时钟约束:如NET “<Net Name>” PERIOD = period {HIGH/LOW}[high or low time]。

⏹采用图形化方法输入约束文件:创建ucf文件,选择ucf文件,然后点击Processes->User Constrains->Create Timing Constraints添加时序约束;点击Processes->User Constrains->I/O Pin Planning添加管脚约束。

1.2 设计综合(Synthesize)综合将概念性硬件描述语言HDL的设计定义转换成针对目标器件的逻辑或者物理表示。

XST(Xilinx Synthesis Tools)就是综合工具,其输出为Xilinx特有的NGC网表文件,NGC包含转化后的逻辑数据和约束信息。

综合是设计流程中的基本步骤,它将概念性硬件描述语言的设计定义转换为针对器件的逻辑或物理表示。

在综合过程中,状态机是单独处理、独立分析的,根据综合的选项,综合器选择状态机在综合过程中选用的实现算法。

综合完成后,综合器会根据综合选项和XCF(XST Constraint File, 综合约束文件),对综合结果做一些基础的优化。

1.3 功能仿真(Simulation->behavioral)功能仿真可以对工程设计文件进行初步的功能验证。

Xilinx_ISE简单教程

23

下面窗口选JTAG, 下面窗口选JTAG,点Finish JTAG

24

配置窗口中选BIT下载文件, 配置窗口中选BIT下载文件,点Open, BIT下载文件 关掉第三方存储下载文件窗口

25

点左边的下载标志,单击鼠标右键, 点左边的下载标志,单击鼠标右键, 运行Program Program, 运行Program,

18

观看显示波形

19

管脚适配

Sources for 设置为 设置为Synthesis..,选中要适配的文件。双击处理窗 ,选中要适配的文件。 文件, 的Assign Package Pins,该操作会提示生成一个 ,该操作会提示生成一个.ucf文件,选是 文件

20

按下图在LOC位置把管脚分配好,并保存 位置把管脚分配好, 按下图在 位置把管脚分配好

ISE简单教程 ISE简单教程

1

§1.4 软件使用—ISE9.1 软件使用—

新建项目工程 新建设计文件 设计编译改错 设计仿真测试 设计文件下载—— 设计文件下载 适配、编程、 适配、编程、下载

2

设计一个模16计数器 设计一个模16计数器 16

要求: 要求: 1、系统输入时钟 、系统输入时钟48MHZ 2、系统输出 、系统输出1HZ信号,用LED指示灯显示; 信号, 指示灯显示; 信号 指示灯显示 3、系统输出模 数据,用4个LED指示灯显示; 、系统输出模16数据 数据, 指示灯显示; 个 指示灯显示 4、系统下载配表管脚: 、系统下载配表管脚: CLK:T8 : 四个LED1-4:C10、A10、B10、A9 模16四个 四个 : 、 、 、 1HZ信号 信号LED: B8 信号

3

1、启动软件

启动program/xilinx Navigator到下图界面 启动program/xilinx ise 9.1/project Navigator到下图界面

Xilinx ISE 使用入门

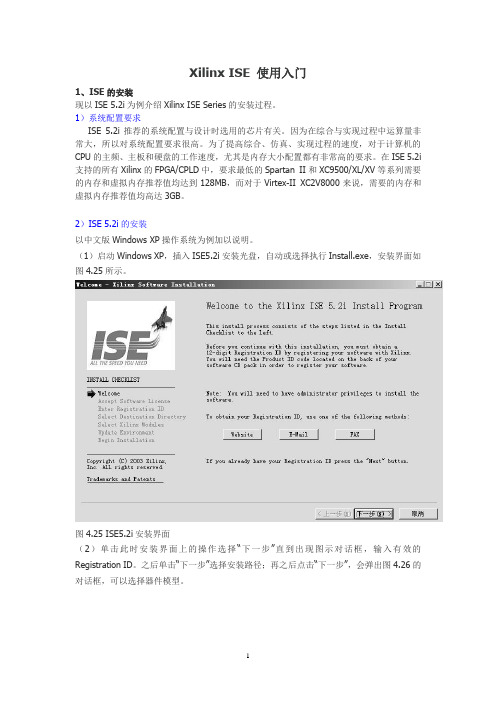

Xilinx ISE 使用入门1、ISE的安装现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。

1)系统配置要求ISE 5.2i推荐的系统配置与设计时选用的芯片有关。

因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。

为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。

在ISE 5.2i 支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。

2)ISE 5.2i的安装以中文版Windows XP操作系统为例加以说明。

(1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。

图4.25 ISE5.2i安装界面(2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。

之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框(3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。

安装完成后,环境变量应作如下描述:若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入:变量名:Xilinx变量值:C:Xilinx(即安装路径)具体设置如图4.28所示。

3 VHDL设计操作指南首先进入ISE工程管理器(Project Navigator)界面,如图4.30所示。

Xilinx_FPGA中文教程

Xilinx_FPGA中文教程Spartan-3E Starter Kit Board User GuideChapter 1: Introduction and Overview Chapter 2: Switches, Buttons, and Knob Chapter 3: Clock SourcesChapter 4: FPGA Configuration Options Chapter 5: Character LCD ScreenChapter 6: VGA Display PortChapter 7: RS-232 Serial PortsChapter 8: PS/2 Mouse/Keyboard Port Chapter 9: Digital to Analog Converter (DAC) Chapter 10: Analog Capture CircuitChapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial FlashChapter 13: DDR SDRAMChapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion ConnectorsChapter 16: XC2C64A CoolRunner-II CPLDChapter 17: DS2432 1-Wire SHA-1 EEPROMChapter 1:Introduction and OverviewSpartan-3E 入门实验板使设计人员能够即时利用Spartan-3E 系列的完整平台性能。

设备支持设备支持::Spartan-3E 、CoolRunner-II关键特性关键特性::Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner?-II (XC2C64A-5VQ44C)与Platform Flash(XCF04S-VO20C)时钟时钟::50 MHz 晶体时钟振荡器存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM连接器与接口: 以太网10/100 Phy, JTAG USB 下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED 输出, 四个瞬时接触按钮, 100管脚hirose 扩展连接端口与三个6管脚扩展连接器显示器: VGA 显示端口,16 字符- 2 线式 LCD电源电源::Linear Technologies 电源供电,TPS75003三路电源管理IC 市场: 消费类, 电信/数据通信, 服务器, 存储器应用: 可支持32位的RISC 处理器,可以采用Xilinx 的MicroBlaze 以及PicoBlaze 嵌入式开发系统;支持DDR 接口的应用;支持基于Ethernet 网络的应用;支持大容量I/O 扩展的应用。

Xilinx_ISE使用教程资料

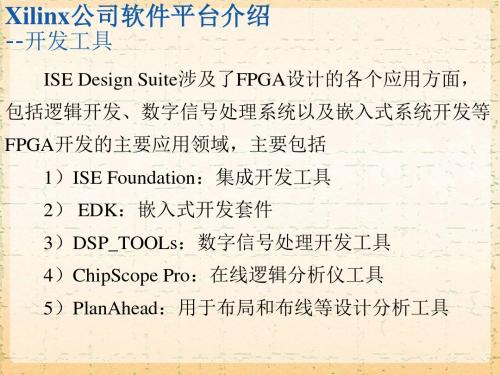

Xilinx公司ISE10.1软件介绍

--脚本(transcript)子窗口

脚本子窗口有5个默认标签:Console,error,warnings , Tcl shell,find in file。 Console标签显示错误、警告和信息。X表示错误,! 表示警告。 Warning标签只显示警告消息。 Error标签只显示错误消息。 Tcl shell标签是与设计人员的交互控制台。除了显示错 误、警告和信息外,还允许输入ISE特定命令。 Find in file标签显示的是选择Edit>Find in File操作后的 查询结果。

Xilinx公司ISE10.1软件设计流程介绍

--打开ISE软件时的面板

当以前使用 过该软件时会默 认打开上一个工 程。

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

选择芯片 选择综合工具

选择仿真工具

选择代码语言

Xilinx公司软件平台介绍

--EDK软件

EDK是Xilinx公司推出的FPGA嵌入式开发工具,包 括嵌入式硬件平台开发工具(Platform Studio)、嵌入式 软件开发工具( Platform Studio SDK)、嵌入式IBM PowerPC硬件处理器核、Xilinx MicroBlaze软处理器核、 开发所需的技术文档和IP,为设计嵌入式可编程系统提供 了全面的解决方案。 EDK10.1版还包括了最新的IP内核以优化系统设计。 同时还包括了SPI、DDR2/DMA/PS2和支持SGMII的三模 式以太网MAC等外设,FlexrayTM外设选项,以及用于 DMA的PCI Express驱动支持。

可编程逻辑器件编程技术:Xilinx ISE软件入门

2.给新工程起名

3.向导自动用工程名给新工程 单独新建一个目录,设计过 程将生成数十个新文件

4.顶层设计的类型,这里选原理图设计

12

用条件过滤器可以快速找到实验板所用的核心器件

选择器件,选择综合和仿真的EDA工具

13

添加新的输入文件

• 如果不在这里新建源文件,也可以在工程建立后到 “Project→New Source”菜单新建文件

2. 双击此项对设计进行实现,即用 网表在FPGA内部布局布线

目标器件规模越大,综合和实现 耗时越多,本设计只有5个门,在 P4 3.0G 机器上也运行了13+27秒

36

查看RTL Schematic

Processes里的综合(Synthesize)完成后就可以查看RTL(寄存器传输级)电路图。双 击下图所示的条目,弹出RTL电路图,现在显示的是最顶层的模块(Module)

4.设计的仿真

• 组合逻辑电路

– 可以使用波形输入进行仿真 – 可以使用HDL语言写测试向量进行仿真

45

波形仿真

仿真需要输入波形,ISE提供了测试向量生成向导和波形编辑器用于 产生必须的输入波形。输入波形用手工编辑输入,新建波形文件。

波形文件名 新建波形测试向量

46

ISE提示建立关联:测试文件要用来测试哪个设计文件。

30

映射IO口

ISE的IO管脚采取“用户约束”的形式指定, 但ISE提供了管脚约束编辑器-PACE

2. 确保设计文件(原 理图或HDL语言) 处于选中状态

1. 源文件浏览器切换 到Source状态 3. 双击这个条目将会 启动管脚编辑器

31

第一次调用PACE会弹 出对话框提示用户:将 要在工程中新增加一个 约束文件,如果不自动 加入,那么需要用户在 运行PACE前手工加入。

XilinxVivadozynq7000入门笔记-图文

XilinxVivadozynq7000入门笔记-图文IPIntegratorflow1.创建RTL工程2.创建IPIntegratorBlockDeign3.添加zynq处理器ip中搜索zynq,添加zynq7ProceingSytem,其中的BFM版本为先前的IP处理器版本。

鼠标右键点击FI某ED_IO和DDR接口,选择makee某ternal,连接到芯片外部。

但此时处理是完全未经过配置的,双击处理器进行配置。

自动添加的外部接口:(参考ug585文档)FI某ED_IO,是专用的内部固化的外设IO,作用?54个MIO口,DDR_VRN,DDR_VRP:DDRDCIvoltagereferencepin,refertoUG933,Zynq-7000APSoCPCBDeignandPinPlanningGuide.PS_SRSTB:Debugytemreet,activeLow.Forcetheytemtoenterareetequ ence.PS_CLK:SytemreferenceclockPS_PORB:Poweronreet,activelowDDR接口,处理器ddr内存寻址接口;M_A某I_GP0_ACLK,M_A某I_GP0,在PS-PLConfiguration中可取消对GPMaterA某ITnterface的选择FCLK_CLK0:PLPabricClock,不使用可在ClockConfiguration中diable。

FCLK_RESET0_N:时钟复位使能,可在General中diable4.配置proceingSytem,通用配置:(1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

UART1映射到MIO[48:49]zedboardBank0IOVoltage:LVCMOS3.3VzedboardBank1IOVoltage:LVCMOS1.8VzedboardPS与PL电源部分是完全独立,但是无论什么时候有PL电源供电就必须有PS电源供电。

Xilinxfpga设计培训中文教程7.pdf

解答

• 如果箭头涵盖的部分是约束的路径 那么在此电路中路径终点 是什么 是否所有的寄存器都有相同点

– 路径终点是触发器

– 触发器的时钟都为同一个信号 以此网络为参考的约束将会约束 在此设计中的所有寄存器之间的时延路径

ADATA

CLK BUFG

FLOP1 DQ

– 这个设计的最高系统时钟频 率为50 MHz

全局时序约束 - 7-6

© 2002 Xilinx公司版权所有

有时序约束的情况

• 同一个设计 只是用约束编 辑器输入了三个全局时序约 束

• 最高系统时钟频率达60 MHz • 注意一下 大部分的逻辑都

离器件中分配了管脚的那一 侧更近

全局时序约束 - 7-7

© 2002 Xilinx公司版权所有

更多关于时序约束

• 时序约束应该被用来定义你的性能目标

– 加较紧的时序约束会增加编译的时间 – 加不现实的约束会导致实现工具停止运行 – 在布局布线前 利用综合工具的时序估计能力或映射后静态时

序报告 以确定你的时序约束是否现实 参见“获取时序逼近I” 模块

全局时序约束 - 7-8

全局时序约束

© 2002 Xilinx公司版权所有

目标

完成此模块的学习后 你将会 • 为一个简单的同步设计加全局时序约束 • 用约束编辑器加全局时序约束和管脚配置

全局时序约束 - 7-3

© 2002 Xilinx公司版权所有

概览

• 简介 • 周期约束与管脚-到-

管脚约束 • 偏置 OFFSET 约束 • 约束编辑器 • 总结

全局时序约束 - 7-4

© 2002 Xilinx公司版权所有

精品课件-Xilinx FPGA设计基础-第1章

第1章 绪论

CPLD和FPGA两者各有特点。CPLD分解组合逻辑的功能很 强,一个宏单元就可以分解十几个甚至20~30多个组合逻辑 输入。而FPGA的一个LUT只能处理4输入的组合逻辑,因此, CPLD适合于设计译码等复杂组合逻辑。但FPGA的制造工艺确 定了FPGA芯片中包含的LUT和触发器的数量非常多,往往都是 几千上万,CPLD一般只能做到512个逻辑单元,而且如果用芯 片价格除以逻辑单元数量,FPGA的平均逻辑单元成本大大低 于CPLD。 所以如果设计中使用到大量触发器,例如设计一个 复杂的时序逻辑,那么使用FPGA就是一个很好的选择。同时 CPLD具有上电即可工作的特性,而大部分FPGA需要一个加载 过程,所以,如果系统要求可编程逻辑器件上电就能工作,那 么就应该选择用 户的设计中实现片上存储器。

第1章 绪论

业内大多数FPGA均提供数字时钟管理(Xilinx的全部FPGA 均具有这种特性)。Xilinx推出的FPGA提供数字时钟管理和相 位环路锁定。相位环路锁定能够提供精确的时钟综合,且能够 降低抖动,并能够实现过滤功能。

总体来说,PLD的优势可以概括如下: (1) PLD在设计过程中为客户提供了更大的灵活性,因 为对于PLD来说,重复设计只需要简单地改变编程文件就可以 了,而且设计时改变的结果可立即在工作器件中看到。

第1章 绪论

(2) PLD不需要漫长的前置时间来制造原型或正式产品 (PLD器件已经放在分销商的货架上并可随时付运。)

第1章 绪论

线在CLB和I/O之间发送信号。有几种布线方法,从CLB内部互 联到实现时钟与其他全局信号低歪斜布线的水平和垂直长线。 除非特别规定,对用户而言设计软件中的互联布线任务是透明 的,这样就极大地降低了设计复杂度。

FPGA支持很多I/O标准,这样就为用户的系统提供了理想 的接口连接。FPGA内的I/O按组分类,每组都能够独立地支持 不同的I/O标准。当今领先的FPGA提供了很多I/O组,实现了 I/O支持的灵活性。

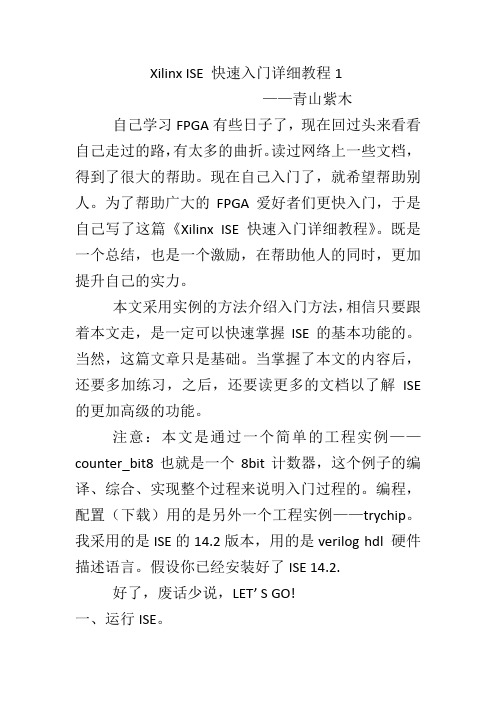

ISE快速入门详细教程verilog_青山紫木原创

Xilinx ISE 快速入门详细教程1——青山紫木自己学习FPGA有些日子了,现在回过头来看看自己走过的路,有太多的曲折。

读过网络上一些文档,得到了很大的帮助。

现在自己入门了,就希望帮助别人。

为了帮助广大的FPGA爱好者们更快入门,于是自己写了这篇《Xilinx ISE 快速入门详细教程》。

既是一个总结,也是一个激励,在帮助他人的同时,更加提升自己的实力。

本文采用实例的方法介绍入门方法,相信只要跟着本文走,是一定可以快速掌握ISE的基本功能的。

当然,这篇文章只是基础。

当掌握了本文的内容后,还要多加练习,之后,还要读更多的文档以了解ISE 的更加高级的功能。

注意:本文是通过一个简单的工程实例——counter_bit8也就是一个8bit计数器,这个例子的编译、综合、实现整个过程来说明入门过程的。

编程,配置(下载)用的是另外一个工程实例——trychip。

我采用的是ISE的14.2版本,用的是verilog hdl 硬件描述语言。

假设你已经安装好了ISE 14.2.好了,废话少说,LET’ S GO!一、运行ISE。

双击图标(你懂的)打开界面如下图图一所示:图一 打开后界面观察图一,可以看见有一个小的对话框“tip ofthe day.”这是程序自带的,用于给用户提供一些有关verilog 或ISE的一些信息,关闭即可。

二、新建工程。

如图二红色区域所示,点击工具栏中file,选择New projiect.图二 新建工程1之后,会弹出图三所示对话框:图三 新建工程2在图三所示的Name一栏中填入工程名,用英文或阿拉伯数字。

在Location一栏中,选择工程的路径,路径中不要有中文。

其他都不用管。

我们这里工程名取为counter_bit8,路径自己定义。

完后,点击Next.会弹出如图四所示对话框:图四 新建工程3刚入门时,只需注意图四红色区域即可。

选择仿真工具与语言。

这里选的是modelsim-SE 版,语言为verilog hdl。

Xilinxfpga设计培训中文教程4.pdf

Байду номын сангаас

NGDBuild 完全实现

结构向导和管脚及区域约束器 - 4-12

design.ucf design.lfp

• 可以接受NGD文件和 UCF文件 如果有的话 • 生成或修改UCF文件

© 2002 Xilinx公司版权所有

PACE

• 封装管脚窗口

– 显示组 bank 信息 – 显示差分对 – 允许从设计层次窗口拖动

概览

• 结构向导 • PACE • 总结

结构向导和管脚及区域约束器 - 4-10

© 2002 Xilinx公司版权所有

PACE

• 管脚及区域约束编辑器 • 管脚分配

– 分配I/O的位置 指定I/O组和I/O标 准 禁止I/O分配

– 检查管脚类型是否与逻辑分配的一致 – 执行 DRC 检查以防止非法的布局

• 区域约束

– 为逻辑建立区域约束并显示外围I/O 的连接情况

– 在设计的早期阶段开始底层布局 – 检查区域约束

结构向导和管脚及区域约束器 - 4-11

© 2002 Xilinx公司版权所有

运用PACE的设计流程

设计源文件 EDIF

NGDBuild design.ngd

design.ucf design.ncf

2V1000FG256在管脚兼容性 被应用后的封装修正图

结构向导和管脚及区域约束器 - 4-16

© 2002 Xilinx公司版权所有

概览

• 结构向导 • PACE • 总结

结构向导和管脚及区域约束器 - 4-17

© 2002 Xilinx公司版权所有

问题回顾

• 在你的设计中使用结构向导的好处是什么 • PACE中至少有哪两个可用特性

XilinxISE软件简单教程课件

Xilinx ISE软件的优缺点

概述Xilinx ISE软件的优点和 缺点,帮助用户全面评估软 件。

Xilinx ISE软件的应用场 景

介绍Xilinx ISE软件广泛应用 于哪些领域和项目,以及其 在每个领域中的优势。

XilinxISE软件简单教程课 件

Xilinx ISE软件简单教程课件为您提供了入门级的教程,让您了解Xilinx ISE软 件的作用、特点以及使用方法。

简介

Xilinx ISE软件是什么?

介绍Xilinx ISE软件是一款功能强大的FPGA开发工具,可以帮助您设计和验证数字电路。

Xilinx ISE软件的作用

解释下载和仿真之间的区别和各自的用途。

3 下载和仿真的流程

讲解下载和仿真的基本步骤,以便用户正确地验证并调试设计。

实例操作

具体实例操作演示

通过示范一个具体的实例,向用户展示Xilinx ISE软 件的使用方法。

实例的说明和分析

对实例进行逐步解析和分析,帮助用户理解设计过 程和结果。

总结

Xilinx ISE软件的功能

解释综合和实现在FPGA设计流 程中的作用和区别。

综合和实现的关系

讨论综合和实现之间的紧密关 联,以及它们在设计迭代中的 作用。

综合和实现的过程

详细描述综合和实现的步骤, 以及如何将设计转换为可下载 的位文件。

下载和仿真

1 下载和仿真的作用

介绍下载和仿真在FPGA设计验证和调试过程中的重要性。

2 下载和仿真的区别

参考资料

相关书籍和文献

提供与Xilinx ISE软件相关的书籍和文献,以便用户进一步学习和深入研究。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

⊙当前位置:搜电>> 资料>> Xilinx ISE 使用入门手册1Xilinx ISE 使用入门手册1发布日期:2009-3-6 13:06:10文章来源:搜电浏览次数:106771、ISE的安装现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。

1)系统配置要求ISE 5.2i推荐的系统配置与设计时选用的芯片有关。

因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。

为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。

在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。

2)ISE 5.2i的安装以中文版Windows XP操作系统为例加以说明。

(1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。

图4.25 ISE5.2i安装界面(2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。

之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框(3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。

安装完成后,环境变量应作如下描述:若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入:变量名:Xilinx变量值:C:Xilinx(即安装路径)具体设置如图4.28所示。

图4.28 环境变量设置操作图3)安装第三方软件在PC上安装完ISE之后,还需要安装第三方仿真软件,如ModelSim等。

2 ISE工程设计流程下面主要概述ISE的基本开发流程以及在开发过程中的各个阶段需要用到的工具软件。

图4.29 说明了利用Xilinx公司的ISE开发设计软件的工程设计流程,具体分为五个步骤:即输入(Design Entry)、综合(Synthesis)、实现(Implementation)、验证(Verification)、下载(Download)。

图4.29 ISE的工程设计流程1)图形或文本输入(Design Entry)图形或文本输入包括原理图、状态机、波形图、硬件描述语言(HDL),是工程设计的第一步,ISE集成的设计工具主要包括HDL编辑器(HDL Editor)、状态机编辑器(StateCAD)、原理图编辑器(ECS)、IP核生成器(CoreGenerator)和测试激励生成器(HDL Bencher)等。

常用的设计输入方法是硬件描述语言(HDL)和原理图设计输入方法。

原理图输入是一种常用的基本的输入方法,其是利用元件库的图形符号和连接线在ISE软件的图形编辑器中作出设计原理图,ISE中设置了具有各种电路元件的元件库,包括各种门电路、触发器、锁存器、计数器、各种中规模电路、各种功能较强的宏功能块等用户只要点击这些器件就能调入图形编辑器中。

这种方法的优点是直观、便于理解、元件库资源丰富。

但是在大型设计中,这种方法的可维护性差,不利于模块建设与重用。

更主要的缺点是:当所选用芯片升级换代后,所有的原理图都要作相应的改动。

故在ISE软件中一般不利用此种方法。

为了克服原理图输入方法的缺点,目前在大型工程设计中,在ISE软件中常用的设计方法是HDL设计输入法,其中影响最为广泛的HDL语言是VHDL和Verilog HDL。

它们的共同优点是利于由顶向下设计,利于模块的划分与复用,可移植性好,通用性强,设计不因芯片的工艺和结构的变化而变化,更利于向ASIC 的移植,故在ISE软件中推荐使用HDL设计输入法。

波形输入及状态机输入方法是两种最常用的辅助设计输入方法,使用波形输入法时,只要绘制出激励波形的输出波形,ISE软件就能自动地根据响应关系进行设计;而使用状态机输入时,只需设计者画出状态转移图,ISE软件就能生成相应的HDL代码或者原理图,使用十分方便。

其中ISE工具包中的StateCAD 就能完成状态机输入的功能。

但是需要指出的是,后两种设计方法只能在某些特殊情况下缓解设计者的工作量,并不适合所有的设计。

2)综合(Synthesis)综合是将行为和功能层次表达的电子系统转化为低层次模块的组合。

一般来说,综合是针对VHDL来说的,即将VHDL描述的模型、算法、行为和功能描述转换为FPGA/CPLD基本结构相对应的网表文件,即构成对应的映射关系。

在Xilinx ISE中,综合工具主要有Synplicity公司的Synplify/Synplify Pro,Synopsys公司的FPGA Compiler II/ Express,Exemplar Logic公司的LeonardoSpectrum和Xilinx ISE 中的XST等,它们是指将HDL语言、原理图等设计输入翻译成由与、或、非门,RAM,寄存器等基本逻辑单元组成的逻辑连接(网表),并根据目标与要求优化所形成的逻辑连接,输出edf和edn等文件,供CPLD/FPGA厂家的布局布线器进行实现。

3)实现(Implementation)实现是根据所选的芯片的型号将综合输出的逻辑网表适配到具体器件上。

Xilinx ISE的实现过程分为:翻译(Translate)、映射(Map)、布局布线(Place & Route)等3个步骤。

ISE集成的实现工具主要有约束编辑器(Constraints Editor)、引脚与区域约束编辑器(PACE)、时序分析器(Timing Analyzer)、FPGA底层编辑器(FGPA Editor)、芯片观察窗(Chip Viewer)和布局规划器(Floorplanner)等。

4)验证(Verification)验证(Verification)包含综合后仿真和功能仿真(Simulation)等。

功能仿真就是对设计电路的逻辑功能进行模拟测试,看其是否满足设计要求,通常是通过波形图直观地显示输入信号与输出信号之间的关系。

综合后仿真在针对目标器件进行适配之后进行,综合后仿真接近真实器件的特性进行,能精确给出输入与输出之间的信号延时数据。

ISE可结合第三方软件进行仿真,常用的工具如Model Tech公司的仿真工具ModelSim和测试激励生成器HDL Bencher ,Synopsys公司的VCS等。

通过仿真能及时发现设计中的错误,加快设计中的错误,加快设计进度,提高设计的可靠性。

每个仿真步骤如果出现问题,就需要根据错误的定位返回到相应的步骤更改或者重新设计。

5)下载(Download)下载(Download)即编程(Program)设计开发的最后步骤就是将已经仿真实现的程序下载到开发板上,进行在线调试或者说将生成的配置文件写入芯片中进行测试。

在ISE中对应的工具是iMPACT。

3 VHDL设计操作指南首先进入ISE工程管理器(Project Navigator)界面,如图4.30所示。

Project Navigator是ISE所用集成工具的连接纽带,通过使用Project Navigator,设计者可以创建、组织和管理自己的设计。

图4.30 ISE工程管理器界面ISE提供了许多示例工程,这些工程都存放在ISE文件当中,可以通过File->Open Example来打开。

ISE为我们提供了一个很有特色的工具,那就是语言辅助模板(Language Templates)。

点击Edit->Language Templates,可以调用语言辅助模板,其界面如图4.31所示。

图4.31 ISE语言辅助模板示意图在语言模板中存放了很多HDL语言的通用语法结构和使用范例,特别是许多根据Xilinx器件IP核与硬件原语编写的实例化程序。

使用语言模板,可以方便地把这些语法结构和范例插入到设计者自己的代码文件中,大大方便了程序的编写,提高了工作效率。

语言模板按照ABEL、COREGEN、UCF、Verilog和VHDL的顺序存放在模板视窗中。

其中COREGEN的UCF是ISE 5.x新增辅助模板。

COREGEN模板由两个目录组成,分别存放当前工程中生成的IP核的Verilog和VHDL实例化文件,基内容与IP核生成器生成IP核时自动生成的实例化文件(.veo,.vho)相同。

UCF模板也分成两个目录,依次存放CPLD和FPGA的用户约束文件(.ucf)的约束范例。

这个模板使手工编辑UCF文件更加容易。

ABEL、Verilog和VHDL三大语言模板大致可以分为下列4个项目:(1)器件例化(Component Instantiation):该模板仅存在于Verilog和VHDL中,给出了块RAM(Block RAM)、数字时钟延迟锁相环(Clock DLL)、数字时钟管理单元(DCM)、分布式RAM/ROM(Distributed RAM/ROM)、全局时钟缓冲(Global Clock Buffer)、查找表(LUT)、基于查找表的移位寄存组(SRLUT)、I/O器件、乘法器和选择器(MUX)等器件模块的实例化范例。

(2)语法模板(Language Templates):该模板给出了基本语法规则和应用范例。

(3)综合模板(Synthesis Templates):该模板给出了可综合实现的一些基本单元模块的范例,如乘法器、计数器和触发器等。

(4)用户模板(User Templates):该模板存放用户自己创建的特定结构,是语言模板的功能扩展。

4 ISE综合使用实例在NBA篮球比赛中有一个24秒进攻规则,即从获取球权到投篮击中篮板、篮框、命中或投篮被侵犯,其有效时间合计不能超过24秒,否则被判违例,将失去球权。

在此过程中,设置24秒、启动倒计时、暂停倒计时或者中途终止24秒(即球权归对方)均由裁判控制。

本实例就是设计一个用于篮球比赛的24秒倒计时器,并且为了模拟现场比赛情况,系统中设置了24秒预设键K1、倒计时启动键K2和倒计时暂停键K3,并将计时精度设置为0.1秒。

各按键具体功能如下:K1键按下,LED灯显示24秒;K2键按下,倒计时;K3键按下,计时停止。

1)新建一个工程(Project)选择File / New Project命令,在图4.32所示对话框中输入工程名和工程目录,并设置器件参数。