版图经验总结

版图经验总结

1查看捕捉点设置是否正确.08工艺为0.1,06工艺为0.05,05工艺为0.025.2Cell名称不能以数字开头.否则无法做DRACULA检查.3布局前考虑好出PIN的方向和位置4布局前分析电路,完成同一功能的MOS管画在一起5对两层金属走向预先订好。

一个图中栅的走向尽量一致,不要有横有竖。

6对pin分类,vdd,vddx注意不要混淆,不同电位(衬底接不同电压)的n井分开.混合信号的电路尤其注意这点.7在正确的路径下(一般是进到~/opus)打开icfb.8更改cell时查看路径,一定要在正确的library下更改,以防copy过来的cell是在其他的library下,被改错.9将不同电位的N井找出来.10 更改原理图后一定记得check and save11 完成每个cell后要归原点12 DEVICE的个数是否和原理图一至(有并联的管子时注意);各DEVICE的尺寸是否和原理图一至。

一般在拿到原理图之后,会对布局有大概的规划,先画DEVICE,(DIVECE之间不必用最小间距,根据经验考虑连线空间留出空隙)再连线。

画DEVICE后从EXTRACTED中看参数检验对错。

对每个device器件的各端从什么方向,什么位置与其他物体连线必须先有考虑(与经验及floorplan的水平有关).13 如果一个cell调用其它cell,被调用的cell的vssx,vddx,vssb,vddb如果没有和外层cell连起来,要打上PIN,否则通不过diva检查.尽量在布局低层cell时就连起来。

14 尽量用最上层金属接出PIN。

15 接出去的线拉到cell边缘,布局时记得留出走线空间.16 金属连线不宜过长;17 电容一般最后画,在空档处拼凑。

18 小尺寸的mos管孔可以少打一点.19 LABEL标识元件时不要用y0层,mapfile不认。

20 管子的沟道上尽量不要走线;M2的影响比M1小.21 电容上下级板的电压注意要均匀分布;电容的长宽不宜相差过大。

版图工程师试用期工作总结

版图工程师试用期工作总结

在试用期的工作中,我深刻地体会到了做一名版图工程师的责任和使命。

这段

时间里,我不断学习、不断进步,也积累了一些宝贵的经验和体会。

首先,我意识到作为一名版图工程师,要具备扎实的专业知识和技能。

在工作中,我不断学习并熟练掌握了各种版图设计软件的使用方法,提高了自己的设计水平和效率。

同时,我也加强了对于版图设计原理和规范的学习,努力做到每一份设计都符合标准和要求。

其次,我深刻体会到了团队合作的重要性。

在试用期的工作中,我和同事们紧

密合作,共同解决了许多设计上的难题,也一起完成了一些重要的项目。

团队合作不仅让工作更加高效,也让我学会了倾听和沟通,更加融入了团队,感受到了团队的力量和温暖。

最后,我明白了责任和使命。

做一名版图工程师,不仅仅是为了完成任务,更

是要为客户提供优质的设计和服务。

在试用期的工作中,我努力做到细致、认真、负责,用心对待每一个项目,用心对待每一个客户,用心对待每一份设计。

我深信,只有这样,才能赢得客户的信任和赞誉,也才能让自己的设计更具有意义和价值。

总的来说,在试用期的工作中,我不断学习、不断进步,也不断感受到了版图

工程师这个职业的魅力和挑战。

我会继续努力,不断提升自己的专业能力和团队协作能力,做一名更加优秀的版图工程师。

感谢公司给我这次宝贵的机会,我会珍惜并努力回报。

版图LAYOUT布局经验总结94条

layout布局经验总结布局前的准备:1 查看捕捉点设置是否正确.08工艺为0.1,06工艺为0.05,05工艺为0.025.2 Cell名称不能以数字开头.否则无法做DRACULA检查.3 布局前考虑好出PIN的方向和位置4 布局前分析电路,完成同一功能的MOS管画在一起5 对两层金属走向预先订好。

一个图中栅的走向尽量一致,不要有横有竖。

6 对pin分类,vdd,vddx注意不要混淆,不同电位(衬底接不同电压)的n井分开.混合信号的电路尤其注意这点.7 在正确的路径下(一般是进到~/opus)打开icfb.8 更改cell时查看路径,一定要在正确的library下更改,以防copy过来的cell是在其他的library下,被改错.9 将不同电位的N井找出来.布局时注意:10 更改原理图后一定记得check and save11 完成每个cell后要归原点12 DEVICE的个数是否和原理图一至(有并联的管子时注意);各DEVICE的尺寸是否和原理图一至。

一般在拿到原理图之后,会对布局有大概的规划,先画DEVICE,(DIVECE 之间不必用最小间距,根据经验考虑连线空间留出空隙)再连线。

画DEVICE后从EXTRACTED中看参数检验对错。

对每个device器件的各端从什么方向,什么位置与其他物体连线必须先有考虑(与经验及floorplan的水平有关).13 如果一个cell调用其它cell,被调用的cell的vssx,vddx,vssb,vddb如果没有和外层cell连起来,要打上PIN,否则通不过diva检查.尽量在布局低层cell时就连起来。

14 尽量用最上层金属接出PIN。

15 接出去的线拉到cell边缘,布局时记得留出走线空间.16 金属连线不宜过长;17 电容一般最后画,在空档处拼凑。

18 小尺寸的mos管孔可以少打一点.19 LABEL标识元件时不要用y0层,mapfile不认。

版图设计小结

2

3 BJT管的设计,如下图设计:

8:1的PNP BJT 管 对称设计

三) 布局设计 拿到原理图之后,对布局有大概的规划,先画DEVICE,(DIVECE 之间不必用最小间距,根据经验考虑 连线空间留出空隙再连线。对每个device器件的各端从什么方向,什 么位置与其他物体连线 必须先有考虑 布局前分析电路,将完成同一功能的MOS管画在一起 对两层金属走向预先订好。一个图中栅的走向尽量一致,不要有横 有竖。 将不同电位的N阱找出来,不同电位(衬底接不同电压)的n井分开.混 合信号的电路尤其注意这点 一般的电容可以最后考虑布局,在空档处拼凑也可以用来做隔离用, 电容的长宽不宜相差过大 ,一般选择接近方形的比较好。且边缘要 加dummy电容 但是并不是说电容设计很随意,在电容要求匹配精度的电路中电容要 有很好的匹配设计 ,以下是电容的几种设计方案:

电容阵列物理设计方案

图I 此电容阵列的优点是对称性 比较好,缺点:连线复杂

dummy

C5

C4

C3

C2

C1

C0

C=155f C0= 16C C1= 8C C2= 4C C3= 2C C4= C

C0 C1 C2 C3 C4 C5

C5=C

图II 此电容阵列的排布适合多位的电 容阵列,而且连线简单

优点是C0、C1、的电容比较对称,连线也简单独立。缺点: 整体上看对称性不是很满意

4.LVS验证: (1) 做LVS前首先要做完DRC,有些简单的错误在DRC中会修改掉 (2) 要确认LVS规则,及其里面需要修改的版图文件的路径及其名称是否正 确 (3) 做LVS第一步很大的可能会出现PIN 名不匹配,尤其是在大的版图设计 完后会出现电源地短接,这个需要仔细地检查是否有地PIN名悬空造成短接, 或者多标注了相同名字地PIN,要注意LVS规则里地电源,地如何识别地如上 面地LVS模板 GROUND-NODE = VS*, Vs*, vS*, vs* POWER-NODE = VC*, Vc*, vC*, vc* 所以除电源,地外不要起VS,VC等开头地名字,以免造成混乱.此外如果是版 图上确实把电源地短接了,这个找起来就麻烦一些了,所以在设计地时候一 定要小心,做到心中有数. (4) 上步完成后要检查MOS管,电容,电阻等是否匹配上.EG:noms 在版图和 电路两旁地个数是否一致,具体匹配关系先不看,这样会比较好地把握错误. (5) 找错误要提高分析问题地能力,从LVS结果中分析问题,找匹配对应关系, 有个小窍门,刚开始找错地时候可以先找版图上打”?”的线的地方,很有 可能是悬空,如果没有悬空可能是逻辑上产生的错误,这个就可以先放一放 这个错误,先解决简单的错误,因为有些复杂的错误有可能是假错,要一步一 步的做.做LVS只能在实践中多分析来提高

版图设计学习总结知识分享

版图设计学习总结版图设计是一个上乘电路设计,下接集成电路芯片制造的中间桥梁;版图设计将电路图中虚拟的晶体管转换成现实中实际存在器件的必不可少的过程,版图就是为集成电路制造所用的集成电路掩膜上的几何图形;利用一层一层的掩膜版,通过工艺线的工作就可以制造出相应的集成电路;MOS器件是四端器件,一种载流子导电,是电压控制器件;电阻一般有栅电阻、阱电阻、注入电阻等,起到一个限流的作用;电容存储电荷的能力称为容性,在集成电路中,电容是无处不在的,只要有一块导电材料跨过另外一块导电材料就会形成一个电容。

电容又称为去耦电容或者隔直电容。

为什么?由两个背靠背PN结构成的具有电流放大作用的晶体三极管称为双极性晶体管,双极型晶体管是一种电流控制器件,电子和空穴同时参与导电。

同场效应晶体管相比,双极型晶体管开关速度慢,输入阻抗小,功耗大;什么是输入阻抗?双极型晶体管工作原理:发射结正偏,集电结反偏时,为放大工作状态;发射结正偏,集电结也正偏,为饱和工作状态;发射结反偏,集电结反偏时,为截止工作状态;发射结发片,集电结正偏时,为反向工作状态;各个状态下的特性是什么?电感在电路中的基本作用是通直流,阻交流;模拟电路的匹配原则:1.把需要匹配的器件相互靠近,使器件保持同一个方向,需要用虚设器件把需要匹配的包围起来,使导线上的集成参数匹配,同时每一样东西都对称,使差分逻辑布线一致,使器件宽度一致、采用尺寸较大的器件,设计时总是与你的电路设计者交流,注意临近的器件;寄生效应:电容、电阻、电感两种材料之间会有寄生电容,电流流过之处会有寄生电阻,高频电路导线具有寄生电感,器件本身也有寄生效应,影响电路的速度、改变频率响应特性电路的寄生;项目启动前对工艺进行一个全面了解,对所有器件结构进行剖析。

工艺完全掌握后,结合工艺对电路进行一个评估,分析电路中的所有应用有没有与工艺相冲突。

根据封装要求,以及电路工程师的要求对版图的初步大模块进行定位。

layout版图经验

一.版图设计感受现在,你了解了一点版图设计了,如果你再了解得更多一点的话,你就会发现你满怀热情的希望学会的版图设计,其实只是一种大人玩的七巧板而已,只是没有小孩玩的七巧板好玩,也没有那么复杂和变化多端。

现在,人各有志,你想把这块七巧板玩出点花样来的话,可以,在这里有大把朋友愿意陪你一起玩;或者你想起了你到这里来的初衷,想要把你的那个电路做成集成电路,那你暂时就别玩七巧板了,想办法尽快的完成你的芯片设计吧。

假如你原来用分立元件设计的电路里用到了许多标准的集成电路,有反相器,与非门、D触发器,计数器、甚至包含了一个液晶显示驱动模块等等,按理说你要设计这些单元的版图,这可不是件轻松的活,日复一日,月复一月,非把你画得痴痴傻傻,呆若木鸡不可,你原来设计一个高性能电路的满腔热情在这里没有用处,你火花般迸发的电路设计灵感对版图设计也一样没有帮助,画版图要的是拼七巧板的技巧。

当你累死累活的干了三个月之后,才发现已经开始种第二季稻的农民伯伯也没有这么辛苦。

由此推算,做一个版图库的工作量约等于种两季稻的工作量。

做一个芯片设计师不如种田实在。

不过即使让你干画版图的活你也不用害怕,电脑上高科技的最奇妙的特点在于它的劳动竟然可以重复使用,第一次做单元图库要用两个月的时间,到了第二次做图库时,你可以把第一次图库拷贝过来,修修改改,有两个星期的时间也就可以了,这就是电脑里COPY 的绝妙之处。

真奇怪为什么不把这种电脑科技推广到农业科技上去,要是农民伯伯也采用这些技术的话,他只要专心种好一亩田就可以了,然后跨嗒跨嗒地拷贝它个十万八千亩,于是站在一望无际金黄色田头,看着晨曦下巍巍壮观的麦浪翻滚,就很难控制住“身在田头,胸怀世界”的感觉了。

幸好农民伯伯还没有还没有掌握这门技术,不然实在要叫我们这些搞芯片设计的家伙无地自容了,但我们还十应该抓紧时间,在目前芯片比种田暂时领先的优势下,做出比农民伯伯更多的贡献来。

但现在情况不一样了,在这里,有现成的单元版图供你使用,这些单元版图放在一个库里,里面品种繁多,差不多包含的你可能用到的全部品种,不要以为这是什么“演示版”,这是很多芯片设计师正在使用的工作库,你现在要干的活已经不是什么版图设计,而是要干一些类似于你以前经常干的活:给双面线路板布线。

版图技巧总结

版图技巧总结1. 介绍版图设计在电子工程和芯片设计过程中扮演着至关重要的角色。

合理和高效的版图设计是确保芯片性能和可靠性的关键。

本文将介绍几个重要的版图技巧,帮助读者在版图设计中取得更好的效果。

2. 封装选择封装是芯片设计中的一个重要环节。

首先,我们需要选择适合芯片设计的封装。

封装的选择可以根据芯片的特性、应用需求和工艺制程进行合理的评估和选择。

常见的封装类型包括QFN、BGA和CSP等。

在选择封装时,需要考虑以下几个因素:•芯片面积和引脚数目•热管理和散热需求•电气特性和信号完整性•成本和制造可行性3. 布局设计布局设计是版图设计中的另一个关键环节。

合理的布局设计可以最大程度地减小电路之间的干扰,并提高芯片的可靠性。

以下是一些布局设计的重要技巧:3.1 分割区域将芯片分割为不同的区域,可以有效地划分不同功能模块并减小相互之间的干扰。

在不同的区域之间使用合适的引脚和电源线分离,有助于减少功耗和噪声。

3.2 引脚位置规划合理的引脚位置规划可以提高芯片的信号完整性和热管理效果。

将高速信号引脚和敏感引脚远离噪声源和电源引脚,可以降低信号干扰和互损。

3.3 电源分布良好的电源分布是保持芯片稳定工作的重要因素之一。

在布局设计过程中,需要合理规划电源线路的分布和接地方式。

避免电源线过长和过窄,尽量减小电源线的电阻和电感。

同时,有效的接地方案也需要考虑,确保电路的稳定性和减小噪声干扰。

4. 金属规则版图设计中的金属规则是确保电路可制造性的重要指标之一。

在进行版图设计时,需要遵守金属规则以减少制造工艺上的限制和成本。

以下是一些常见的金属规则:4.1 金属间距和开孔规则金属之间的间距和开孔大小需要符合制造工艺的要求。

适当的间距和开孔规则可以减少金属层之间的短路和开路问题,并提高芯片的可靠性。

4.2 金属填充在芯片设计中,经常会遇到空洞或空白区域。

为了提高制造工艺的容错性和减少金属层的不均匀性,需要进行金属填充。

金属填充可以提高芯片的平面度和减小应力问题。

版图工程师试用期工作总结

版图工程师试用期工作总结在过去的试用期里,我作为一名版图工程师,经历了许多挑战和收获。

这段时间里,我学到了很多新的知识和技能,也遇到了许多新的问题和困难。

在这篇文章中,我将总结一下我的试用期工作经历,分享我所学到的东西,以及我对未来工作的期望。

首先,我想说我在这段时间里学到了很多新的知识和技能。

作为一名版图工程师,我需要不断地学习和更新自己的知识,以跟上行业的发展。

在这段时间里,我学会了如何使用各种版图设计软件,掌握了版图设计的基本原理和技巧。

我还学习了如何与团队合作,如何与客户沟通,以及如何解决问题和应对挑战。

这些知识和技能对我未来的工作将会非常有帮助。

其次,我也遇到了许多新的问题和困难。

在工作中,我常常会遇到一些疑难问题,需要花费大量的时间和精力去解决。

有时候,我也会遇到一些困难的客户,需要我耐心地与他们沟通,找到解决问题的方法。

但是,通过不断地努力和学习,我成功地克服了这些困难,取得了一些成绩。

最后,我对未来的工作充满了期待。

在试用期的工作经历中,我深深地感受到了版图工程师这个职业的魅力和挑战。

我希望在未来的工作中,能够继续学习和进步,不断地提升自己的专业技能和团队合作能力。

我也希望能够在未来的工作中,为公司做出更大的贡献,成为一名优秀的版图工程师。

总的来说,我的试用期工作经历是充实而有意义的。

我学到了很多新的知识和技能,也遇到了许多新的问题和困难。

我对未来的工作充满了期待,我相信我会在未来的工作中取得更大的成就。

感谢公司给我这次机会,让我有机会在这个领域里不断学习和成长。

希望未来的工作会更加精彩!。

图版工作总结

图版工作总结

图版工作是印刷行业中至关重要的一环,它直接影响着印刷品的质量和效果。

在过去的一段时间里,我一直在图版工作岗位上工作,通过不断的学习和实践,我对这个工作岗位有了更深刻的认识和理解。

首先,图版工作需要高度的专业技能和经验。

在处理图版制作过程中,需要掌

握各种图像处理软件和印刷设备的操作技巧,同时还需要对印刷品的质量要求有清晰的认识。

通过不断的学习和实践,我逐渐熟练掌握了这些技能,并且在实际工作中取得了一定的成绩。

其次,图版工作需要细心和耐心。

在处理图版制作过程中,需要对每一个细节

都进行精益求精的处理,确保印刷品的质量和效果。

同时,由于图版工作需要反复的试验和修改,因此需要有耐心和毅力,不断地进行尝试和改进,直到达到最佳的效果。

最后,图版工作需要团队合作和沟通能力。

在图版制作过程中,需要与设计师、印刷工人等多个岗位进行紧密的合作,确保整个印刷流程的顺利进行。

因此,良好的团队合作和沟通能力对于图版工作来说至关重要。

总的来说,图版工作是一项需要高度专业技能、细心耐心和团队合作的工作。

通过不断的学习和实践,我对图版工作有了更深刻的认识和理解,同时也意识到自己在这个岗位上还有很多需要提升和改进的地方。

希望在未来的工作中,能够不断提升自己的专业技能,更好地完成图版工作,为印刷品的质量和效果做出更大的贡献。

版图工作总结

版图工作总结

在过去的一段时间里,我一直在版图工作中努力工作。

这项工作需要我不断地与客户沟通,制定设计方案,并确保最终的产品符合客户的要求。

在这个过程中,我学到了很多东西,也积累了宝贵的经验。

首先,我学会了与客户进行有效的沟通。

在版图工作中,客户的需求是最重要的。

我学会了倾听客户的意见和建议,以确保我的设计方案能够满足他们的要求。

我也学会了向客户解释我的设计理念,并接受他们的反馈和建议。

通过和客户的紧密沟通,我能够更好地理解他们的需求,从而提供更好的设计方案。

其次,我学会了制定有效的设计方案。

在版图工作中,设计方案的质量直接关系到最终产品的效果。

我学会了通过调研和分析,制定符合客户需求的设计方案。

我也学会了在设计过程中不断地改进和完善方案,以确保最终的产品能够达到客户的期望。

最后,我学会了团队合作。

在版图工作中,团队合作是非常重要的。

我学会了和同事们紧密合作,共同解决问题,提高工作效率。

我也学会了向同事学习和借鉴他们的经验和技巧,以提升自己的设计水平。

通过这段时间的版图工作,我不仅学到了很多专业知识和技能,也积累了宝贵的工作经验。

我相信这些经验和技能将会对我的未来工作产生积极的影响。

我会继续努力学习和提升自己,为客户提供更好的设计方案,为公司创造更大的价值。

版图设计工程师工作总结

版图设计工程师工作总结一、工作内容作为一名版图设计工程师,我的主要工作是负责版图设计和相关文件的编制。

具体来说,我的工作内容包括以下几个方面:1、理解项目需求:首先需要充分理解项目需求,包括产品功能、性能、外观等方面的要求,以便能够设计出符合项目需求的版图。

2、设计版图:根据项目需求,利用相关软件进行版图设计,包括电路图、布线图、装配图等。

同时需要考虑可制造性、可测试性和可维护性等因素。

3、文件编制:完成版图设计后,需要编制相关的技术文件,包括设计说明书、装配说明书、测试说明书等,以便生产部门和使用部门能够正确理解和使用版图。

4、沟通协调:在工作中需要与项目经理、硬件工程师、结构工程师等各个部门进行沟通协调,确保版图设计和相关文件的编制符合项目整体要求。

二、工作成果通过一段时间的工作,我取得了一些工作成果。

具体来说,我在以下几个方面取得了一些进展:1、提高了版图设计能力:通过不断学习和实践,我逐渐提高了自己的版图设计能力,能够更加熟练地运用相关软件进行版图设计。

2、优化了版图设计方案:通过对多个版图设计方案进行比较和优化,我能够设计出更加合理、高效的版图方案,提高了产品的性能和可靠性。

3、编制了完整的版图文件:我编制了完整的版图文件,包括设计说明书、装配说明书、测试说明书等,为生产部门和使用部门提供了便利。

4、沟通协调能力得到提高:通过与各个部门的沟通协调,我逐渐提高了自己的沟通协调能力,能够更好地与他人合作完成项目工作。

三、经验教训在工作中我也遇到了一些问题和困难,通过反思和总结,我认为有以下几点经验教训值得分享:1、充分理解项目需求:在开始版图设计之前,一定要充分理解项目需求,包括产品功能、性能、外观等方面的要求,以便能够设计出符合项目需求的版图。

2、注意细节问题:版图设计需要注重细节问题,一个小小的疏忽可能导致整个项目的失败。

因此,在设计过程中一定要细心、认真。

3、与其他部门保持良好沟通:在工作中需要与其他部门保持良好沟通,了解其他部门的需求和反馈意见,以便能够及时调整自己的工作方向和方法。

图版工作总结

图版工作总结

在过去的一段时间里,我有幸参与了图版工作,并且取得了一些成就。

在这篇文章中,我将对我的工作进行总结,分享一些经验和教训。

首先,我要感谢我的团队成员们,他们在整个过程中给予了我很大的支持和帮助。

我们一起克服了许多困难,共同努力完成了各项任务。

团队合作是图版工作中非常重要的一部分,没有团队的支持和合作,我是无法取得如此好的成绩的。

其次,我要提到的是技术的提升。

在图版工作中,技术是至关重要的。

我不断学习和提升自己的技术水平,不断尝试新的技术和工具。

这些努力让我在图版工作中更加得心应手,也让我的作品更加出色。

另外,我也学会了如何更好地与客户沟通。

客户的需求和反馈对于图版工作来说非常重要,而良好的沟通能够帮助我更好地理解客户的需求,并且更好地满足他们的要求。

通过与客户的沟通,我也学会了更好地把握设计的方向和风格。

最后,我要总结一下我在图版工作中的收获。

通过这段时间的工作,我不仅提升了自己的技术水平,还学会了更好地与团队合作和与客户沟通。

这些都是我在未来工作中会继续努力提升的方面。

总的来说,图版工作是一项需要不断学习和提升的工作,我会继续努力,不断提升自己的技术水平和团队合作能力,为客户提供更好的服务。

感谢这段时间的工作经历,也期待未来的挑战和成长。

版图工作总结

版图工作总结

在过去的一段时间里,我们团队经历了许多挑战和机遇,通过努力工作和团队合作取得了许多成绩。

在这篇文章中,我将对我们的版图工作进行总结,分享我们的成就和经验。

首先,我们团队在版图工作中取得了一些重要的进展。

我们成功地完成了一系列复杂的版图设计任务,包括芯片布局、电路板设计等。

我们的工作不仅满足了客户的需求,还得到了客户的高度赞扬。

这些成就得益于我们团队成员的专业知识和团队合作精神。

其次,我们在版图工作中遇到了一些挑战,但我们成功地克服了这些困难。

在一些项目中,我们面临了时间紧迫和资源有限的情况,但我们团队通过合理安排工作流程和有效沟通,成功地完成了任务。

这些挑战不仅锻炼了我们的能力,也让我们更加团结和成熟。

最后,我们在版图工作中积累了一些宝贵的经验。

我们意识到,版图工作需要高度的专业技能和耐心,需要团队成员之间的密切合作和良好的沟通。

我们也意识到,版图工作是一个不断学习和提高的过程,我们需要不断更新知识和技能,适应行业的发展和变化。

总的来说,我们团队在版图工作中取得了一些重要的成就,也积累了一些宝贵的经验。

我们将继续努力,不断提高自己的专业水平,为客户提供更好的服务。

希望在未来的工作中,我们能够取得更大的成就,为公司的发展做出更大的贡献。

版图技巧总结

盛年不重来,一日难再晨。

及时宜自勉,岁月不待人。

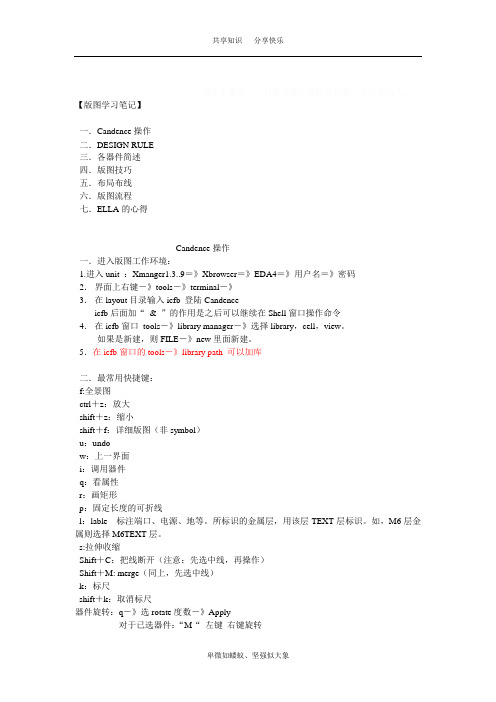

【版图学习笔记】一.Candence操作二.DESIGN RULE三.各器件简述四.版图技巧五.布局布线六.版图流程七.ELLA的心得Candence操作一.进入版图工作环境:1.进入unit :Xmanger1.3..9=》Xbrowser=》EDA4=》用户名=》密码2.界面上右键-》tools-》terminal-》3.在layout目录输入icfb 登陆Candenceicfb后面加“& ”的作用是之后可以继续在Shell窗口操作命令4.在icfb窗口tools-》library manager-》选择library,cell,view。

如果是新建,则FILE-》new里面新建。

5.在icfb窗口的tools-》library path 可以加库二.最常用快捷键:f:全景图ctrl+z:放大shift+z:缩小shift+f:详细版图(非symbol)u:undow:上一界面i:调用器件q:看属性r:画矩形p:固定长度的可折线l:lable 标注端口、电源、地等。

所标识的金属层,用该层TEXT层标识。

如,M6层金属则选择M6TEXT层。

s:拉伸收缩Shift+C:把线断开(注意:先选中线,再操作)Shift+M: merge(同上,先选中线)k:标尺shift+k:取消标尺器件旋转:q-》选rotate度数-》Apply对于已选器件:“M“左键右键旋转g:格点鼠标在各格点移动一般不用如果取消,则再按一次“g”shift+x: 进入调用器件的下层shift+b:返回上层F3:在选择了操作命令后,按F3可以显示旋转,宽度调整等被操作器件特性。

该键很有用。

Undo默认为一步。

若要增加次数,在ICFB窗口的OPTIONS里选择USER PREFERENCES,改变undo次数。

三.Layout环境界面常用操作左边的窗口为“LSW”窗口。

A V:all view NV:no view AS:all select NS:none select(在连线时,可以先选NV,所有层次都看不见,再选中需要连线的层次,则版图上只显示该层,方便连线。

版图公司年末个人工作总结

版图公司年末个人工作总结尊敬的领导:转眼间,又到了一年的年末,我写此封信向您总结今年的工作。

在过去的一年里,我在版图公司工作中取得了一些成绩。

首先,我在工作中遇到的各种问题和挑战都能够迎刃而解,通过不断学习和提升自己的工作能力,我成功地完成了多项工作任务,并且得到了客户和同事的肯定和赞扬。

同时,我也积极参与公司的团队合作和项目推进,为公司的业务发展做出了一定的贡献。

此外,我也意识到了自己在工作中的不足之处,比如沟通能力和团队合作能力还有待提高,这也让我更加明确了未来的工作方向和提升重点。

在新的一年里,我会继续努力学习,不断提升自己的专业能力和技能,在工作中更加注重团队合作,积极主动地承担更多的责任和挑战,努力做到更好。

同时,我也会不断总结经验和教训,不断调整工作态度和方法,以更加有效地提高工作效率和质量。

最后,我要感谢公司和领导对我的信任和支持,也感谢同事们在工作中的帮助和合作。

希望在新的一年里,我们能够一起携手共进,共同实现更好的工作业绩。

谢谢!此致敬礼XXX尊敬的领导:在这一年的工作中,我不断努力,完成了许多任务。

首先,我负责的项目取得了非常好的成果,顺利交付给客户,并且得到了客户的一致好评。

同时,在与同事和上级的良好协作下,我所负责的工作任务能够顺利完成,对公司的整体工作成果也做出了贡献。

我在工作中也遇到了不少挑战,比如某个项目进展不顺利,需要加班加点才能完成,还有与同事的沟通出现了矛盾。

但是,通过不断地学习和努力,我成功地克服了这些困难,取得了圆满的成绩。

在工作中,我也意识到了自己的不足之处。

比如,有时候工作中的紧张情绪容易影响到我的工作效率和质量,还有在团队合作中需要更加主动和耐心。

因此,我会在新的一年里更加努力地克服这些问题,不断提高自己的工作能力和素质,为公司的发展做出更大的贡献。

在新的一年里,我将积极学习公司业务知识和行业动态,不断提高自己的专业能力,为公司的发展和壮大做出更多的贡献。

芯片版图个人工作总结

芯片版图个人工作总结在过去的一年中,我主要负责设计和优化芯片版图的工作。

在这个岗位上,我学到了很多新的知识和技能,并且取得了一些成就。

以下是我个人在这方面的工作总结:首先,我熟练掌握了芯片版图设计软件,能够独立完成芯片版图的设计和优化工作。

我熟练掌握了版图设计的基本原理和流程,并且能够根据项目的需求,合理地布局和连接芯片内部的器件和线路。

此外,我还能够根据设计规范和标准,进行版图设计的验证和优化。

其次,在项目中,我遇到了一些挑战和困难,但我能够靠着自己的努力和坚持克服了这些困难。

例如,在一个项目中,由于器件数量较多,版图设计的面积较大,我面临了布局和布线的瓶颈问题。

但是我通过不断的思考和尝试,采用了一些创新的方案,最终成功地解决了这个问题。

最后,我能够良好地和团队成员合作,并且能够根据团队的需求和项目进度,合理地安排我的工作。

在团队中,我能够积极地分享我的经验和知识,帮助团队解决问题,并且能够接受其他团队成员的建议和意见,不断改进和完善我的工作。

总的来说,在过去的一年中,我在芯片版图设计方面取得了一些成绩,并且在团队中取得了良好的合作和交流。

我会继续努力学习和提高自己的专业能力,为公司未来的发展贡献我的力量。

除了以上提到的成绩和经验外,在过去一年的工作中,我还有一些其他的收获和体会。

首先,我深刻了解了芯片版图设计对于整个芯片设计流程的重要性。

芯片版图是整个芯片设计工程中的最后一道关卡,它直接影响到芯片的性能、功耗和成本。

因此,在版图设计过程中,我深入学习了各种版图设计原理和优化方法,以确保芯片达到设计要求和性能指标。

其次,我在与其他部门和团队的合作中,学会了更好地理解整个产品开发的流程和各个环节之间的关联。

与布局设计师、验证工程师、工艺工程师等工作密切合作,加深了我对整个芯片设计流程的理解,也让我意识到一款芯片的成功离不开各个环节的有机协作。

在实际的项目中,我也遇到了一些挑战。

一次,在版图设计的过程中,遇到了信号完整性和功耗分析方面的问题。

版图技巧总结

【版图学习笔记】一.Candence操作二.DESIGN RULE三.各器件简述四.版图技巧五.布局布线六.版图流程七.ELLA的心得Candence操作一.进入版图工作环境:1.进入unit :Xmanger1.3..9=》Xbrowser=》EDA4=》用户名=》密码2.界面上右键-》tools-》terminal-》3.在layout目录输入icfb 登陆Candenceicfb后面加“& ”的作用是之后可以继续在Shell窗口操作命令4.在icfb窗口tools-》library manager-》选择library,cell,view。

如果是新建,则FILE-》new里面新建。

5.在icfb窗口的tools-》library path 可以加库二.最常用快捷键:f:全景图ctrl+z:放大shift+z:缩小shift+f:详细版图(非symbol)u:undow:上一界面i:调用器件q:看属性r:画矩形p:固定长度的可折线l:lable 标注端口、电源、地等。

所标识的金属层,用该层TEXT层标识。

如,M6层金属则选择M6TEXT层。

s:拉伸收缩Shift+C:把线断开(注意:先选中线,再操作)Shift+M: merge(同上,先选中线)k:标尺shift+k:取消标尺器件旋转:q-》选rotate度数-》Apply对于已选器件:“M“左键右键旋转g:格点鼠标在各格点移动一般不用如果取消,则再按一次“g”shift+x: 进入调用器件的下层shift+b:返回上层F3:在选择了操作命令后,按F3可以显示旋转,宽度调整等被操作器件特性。

该键很有用。

Undo默认为一步。

若要增加次数,在ICFB窗口的OPTIONS里选择USER PREFERENCES,改变undo次数。

三.Layout环境界面常用操作左边的窗口为“LSW”窗口。

A V:all view NV:no view AS:all select NS:none select(在连线时,可以先选NV,所有层次都看不见,再选中需要连线的层次,则版图上只显示该层,方便连线。

版图工作总结

版图工作总结

在过去的一段时间里,我有幸参与了公司的版图工作,并且在这个过程中积累了不少经验和收获。

在这篇文章中,我想分享一下我的工作总结,希望能够对大家有所帮助。

首先,版图工作需要细心和耐心。

在进行版图设计的过程中,我们需要仔细地考虑每一个细节,确保版图的布局和设计符合公司的形象和要求。

同时,也需要花费大量的时间和精力来进行反复的修改和调整,以确保最终的效果能够达到预期的目标。

其次,版图工作需要团队合作和沟通。

在这个过程中,我和我的同事们需要密切合作,共同商讨和决定版图的设计方案。

在这个过程中,沟通是非常重要的,只有通过有效的沟通,我们才能够达成共识,确保版图的设计能够符合公司的整体要求。

另外,版图工作也需要不断的学习和提升。

在这个过程中,我不断地学习新的设计技巧和方法,以提升自己的设计水平和能力。

同时,也需要不断地关注市场的变化和趋势,以确保我们的版图设计能够跟上时代的步伐。

最后,版图工作也需要对细节的把控和质量的把关。

在这个过程中,我们需要对每一个细节都进行严格的把控,确保版图的设计能够达到最高的质量标准。

只有通过不断地追求卓越,我们才能够在激烈的市场竞争中脱颖而出。

总的来说,版图工作是一项需要细心、耐心、团队合作和不断学习的工作。

通过这段时间的工作,我深刻体会到了版图工作的重要性和复杂性,也收获了很多宝贵的经验和教训。

希望在未来的工作中,我能够继续努力,不断提升自己的设计能力,为公司的发展贡献自己的力量。

图版工作总结

图版工作总结

在过去的一段时间里,我有幸能够参与图版工作,并且取得了一些成绩。

在这

段时间里,我学到了很多东西,也遇到了不少挑战。

现在,我想通过这篇文章来总结一下我的图版工作经历。

首先,我想谈谈我在图版工作中取得的成绩。

在这段时间里,我完成了许多设

计项目,包括海报、名片、宣传单等。

我不仅仅是完成了任务,更重要的是我能够通过自己的创意和设计技巧,为客户提供了满意的作品。

我还参与了一些团队合作的项目,通过和团队成员的密切合作,我们成功地完成了一些复杂的设计任务。

这些成绩让我感到非常自豪,也让我对自己的设计能力更有信心。

其次,我也遇到了一些挑战。

在图版工作中,有时候客户的要求可能会非常苛刻,或者设计的灵感不够充分,这就需要我付出更多的努力和时间来克服这些困难。

我还遇到了一些技术上的问题,比如软件的使用和设计工具的选择等。

但是,通过不断地学习和实践,我逐渐克服了这些困难,也提高了自己的设计水平。

最后,我想说的是,图版工作是一项需要不断学习和提高的工作。

在这段时间里,我学到了很多设计知识和技巧,也不断地提高了自己的审美能力和设计水平。

我相信,只要我坚持不懈地努力,我一定能够在图版设计领域取得更大的成就。

总的来说,通过这段时间的图版工作,我不仅仅积累了丰富的设计经验,也提

高了自己的设计能力。

我相信,这段经历将会成为我未来设计生涯中宝贵的财富,也会让我在未来的工作中更加游刃有余。

感谢这段宝贵的经历,也期待未来更多的设计挑战和成就。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 查看捕捉点设置是否正确.08 工艺为0.1,06工艺为0.05,05 工艺为0.025.2Cell名称不能以数字开头.否则无法做DRACULA佥查.3 布局前考虑好出PIN 的方向和位置4布局前分析电路,完成同一功能的MOS管画在一起5 对两层金属走向预先订好。

一个图中栅的走向尽量一致,不要有横有竖。

6对pin分类,vdd,vddx注意不要混淆,不同电位(衬底接不同电压)的n井分开.混合信号的电路尤其注意这点.7在正确的路径下(一般是进到~/opus)打开icfb.8 更改cell 时查看路径,一定要在正确的library 下更改,以防copy 过来的cell 是在其他的library 下,被改错.9将不同电位的N井找出来.10 更改原理图后一定记得check and save11 完成每个cell 后要归原点12 DEVICE勺个数是否和原理图一至(有并联的管子时注意);各DEVICE勺尺寸是否和原理图一至。

一般在拿到原理图之后,会对布局有大概的规划,先画DEVICE (DIVECE 之间不必用最小间距,根据经验考虑连线空间留出空隙)再连线。

画DEVICE后从EXTRACTE中看参数检验对错。

对每个device器件的各端从什么方向,什么位置与其他物体连线必须先有考虑(与经验及floorplan 的水平有关).13如果一个cell 调用其它cell,被调用的cell的vssx,vddx,vssb,vddb如果没有和外层cell连起来,要打上PIN,否则通不过diva检查.尽量在布局低层cell时就连起来。

14 尽量用最上层金属接出PIN。

15 接出去的线拉到cell 边缘,布局时记得留出走线空间.16 金属连线不宜过长;17 电容一般最后画,在空档处拼凑。

18小尺寸的mos管孔可以少打一点.19 LABEL标识元件时不要用yO层,mapfile不认。

20管子的沟道上尽量不要走线;M2的影响比M1小.21 电容上下级板的电压注意要均匀分布;电容的长宽不宜相差过大。

可以多个电阻并联.22 多晶硅栅不能两端都打孔连接金属。

23 栅上的孔最好打在栅的中间位置.24 U形的mos管用整片方形的栅覆盖diff层,不要用layer gen eration的方法生成U 形栅.25 一般打孔最少打两个26 Con tact面积允许的情况下,能打越多越好,尤其是inpu t/out put部分,因为电流较大.但如果contact 阻值远大于diffusion 则不适用.传导线越宽越好,因为可以减少电阻值,但也增加了电容值.27 薄氧化层是否有对应的植入层28金属连接孔可以嵌在diffusion 的孔中间.29 两段金属连接处重叠的地方注意金属线最小宽度30 连线接头处一定要重叠,画的时候将该区域放大可避免此错误。

31摆放各个小CELL时注意不要挤得太近,没有留出走线空间。

最后线只能从DEVICE上跨过去。

32 Text2,y0 层只是用来做检查或标志用,不用于光刻制造.33芯片内部的电源线/地线和ESD上的电源线/地线分开接;数模信号的电源线/地线分开。

34 Pad的pass窗口的尺寸画成整数90um.35连接Esd电路的线不能断,如果改变走向不要换金属层36 Esd电路中无VDDX,VSS是VDDB,VSSB.37 PAD和ESD最好使用M1连接,宽度不小于20um;使用M2连接时,pad 上不用打VIA孔,在ESD电路上打。

38 PAD与芯片内部cell的连线要从ESD电路上接过去。

39 Esd电路的SOURCES两边,DRAIN放中间。

40 ESD的D端的孔到poly的间距为4,S端到poly的间距为八+0.2.防止大电流从D端进来时影响Poly.41 ESD的pmos管与其他ESD或POWER的nmos管至少相距70um 以上。

42大尺寸的pm os/ nmos与其他nm os/pm os(非po wermos和ESD的间距不够70um时,但最好不要小于50um,中间加NWELL打上NTAP.43 NWELL和PTAP的隔离效果有什么不同?NWELL较深,效果较好.44只有esd电路中的管子才可以用2*2um的孔.怎么判断ESD电路?上拉P 管的D/G均接VDD,S接PAD下拉N管的G/S接VSS,□接PAD.P/N管起二极管的作用.45摆放ESD时nmos摆在最外缘,pmos在内.46 关于匹配电路,放大电路不需要和下面的电流源匹配。

什么是匹配?使需要匹配的管子所处的光刻环境一样。

匹配分为横向,纵向,和中心匹配。

1221 为纵向匹配,12 为中心匹配(把上方1 转到下方1 时,上方2 也达到下方 2 位置)21中心匹配最佳。

47 尺寸非常小的匹配管子对匹配画法要求不严格.4个以上的匹配管子,局部和整体都匹配的匹配方式最佳.48在匹配电路的mos管左右画上dummy,用poly,poly的尺寸与管子尺寸一样,dummy与相邻的第一个poly gate的间距等于poly gate之间的间距.49电阻的匹配,例如1,2两电阻需要匹配,仍是1221等方法。

电阻dummy 两头接地vssx。

50 Via不要打在电阻体,电容(Poly)边缘上面.51 05工艺中resistor 层只是做检查用52电阻连线处孔越多,各个VIA孔的电阻是并联关系,孔形成的电阻变小.53 电阻的dummy 是保证处于边缘的电阻与其他电阻蚀刻环境一样54 电容的匹配,值,接线,位置的匹配。

55电阻连接fuse的pad的连线要稍宽,因为通过的电流较大.fuse的容丝用最上层金属.56 关于powermos①powermos 一般接pin,要用足够宽的金属线接,②几种缩小面积的画法。

③栅的间距?无要求。

栅的长度不能超过100um57 Po wer mos要考虑瞬时大电流通过的情况,保证电流到达各处的路径的电阻相差不大.(适应所有存在大电流通过的情况).58 金属层dummy 要和金属走向一致,即如果M2 横走,M2 的dummy 也是横走向59 低层cell 的Pin,label 等要整齐,and 不要删掉以备后用.60 匹配电路的栅如果横走,之间连接用的金属线会是竖走,用金属一层, 和规定的金属走向一致。

61 不同宽度金属连接的影响?整个layout 面积较大时影响可忽略.62输出端节电容要小.多个管子并联,有一端是输出时注意做到这点.63做DRACULA佥查时,如果先运行drc,drc检查没有完毕时做了Ivs检查,那么drc检查的每一步会比lvs检查的每一步快反之,lvs会比drc快.64最终DRACULA通过之后在layout图中空隙处加上ptap,先用thin-oxid将空隙处填满,再打上孔,金属宽度不要超过10,即一行最多8个孔(06工艺)65为防止信号串扰,在两电路间加上PTAP此PTAP单独连接VSS PAD.66金属上走过的电压很大时,为避免尖角放电,拐角处用斜角,不能走90度度的直角.67如果w=20,可画成两个w=10mos管并联68 并联的管子共用端为S 端, 或D 端;串联的管子共用端为s/d 端.出错检查:69 DEVICE勺各端是否都有连线;连线是否正确;70 完成布局检查时要查看每个接线的地方是否都有连线,特别注意VSSX, VDDX71查线时用SHOTS各线高亮显示,便于找出可以合并或是缩短距离的金属线。

72多个电阻(大于两根)打上DUMMY。

保证每根电阻在光刻时所处的环境一样,最外面的电阻的NPIM层要超出EPOLY2 0.55 um,即两根电阻间距的一半。

73无关的MOS管的THIN要断开,不要连在一起74 并联的管子注意漏源合并,不要连错线。

一个管子的源端也是另一个管子的源端75做DRAC检查时最上层的pin的名称用text2标识。

Text2的名称要和该pin 的名称一样.76大CELL不要做DIVA检查,用DRACULE.77 Text2层要打在最顶层cell里.如果打在pad上,于最顶层调用此PADQracula无法认出此pin.78消除电阻dummy的lvs报错,把nimp和RPdummy层移出最边缘的电阻,不要覆盖dummy79 06工艺中M1最小宽度0.8,如果用0.8的M1拐线,虽然diva的drc不报错,但DRACUL啲drc会在拐角处报错.要在拐角处加宽金属线.80最后DRACULA勺lvs通过,但是drc没有过,每次改正drc错误前可把layout图存成layouts再改正.以免改错影响lvs不通过,旧版图也被保存下来了.81 Cell中间的连线尽量在低层cell中连完,不要放在高层cell中连,特别不要在最高层cell 中连,因为最高层cell 的布局经常会改动,走线容易因为cell 的移动变得混乱.82 DRACULA勺drc无法检查出pad必须满足pad到与pad无关的物体间距为10这一规则.83做DRACULA佥查时开两个窗口,一个用于lvs,一个用于drc.可同时进行,节省时间.容易犯的错误84 电阻忘记加dummy85使用NS功能后没有复原(选取AS)之后又进行整图移动操作,结果被NS 的元件没有移动,图形被破坏.86使用strech功能时错选•每次操作时注意看图左下角提示.87 Op 电路中输入放大端的管子的衬底不接vddb/vddx.88 是否按下capslock 键后没有还原就操作节省面积的途径89 电源线下面可以画有器件.节省面积.90 电阻上面可以走线,画电阻的区域可以充分利用。

91 电阻的长度画越长越省面积。

92走线时金属线宽走最小可以节省面积.并不需要走孔的宽度.93 做新版本的layout 图时,旧图保存,不要改动或删除。

减小面积时如果低层CELL的线有与外层CELL!连,可以从更改连线入手,减小走线面积。

94 版图中面积被device,device 的间隔和走线空间分割。

减小面积一般从走线空间入手,更改FLOOR PLAN。