童诗白《模拟电子技术基础》(第4版)名校考研真题(多级放大电路)

模拟电子技术基础第四版(童诗白)课后答案第5章 放大电路的频率响应

第5章 放大电路的频率响应习题5.1在图P5.1所示电路中,已知晶体管的'bb r、C μ、C π,i be R r ≈。

填空:除要求填写表达式的之外,其余各空填入①增大、②基本不变、③减小。

(1)在空载情况下,下限频率的表达式L f ≈(112(//)s b be R R r C π+ )。

当R S 减小时,L f 将( ① );当带上负载电阻后,L f 将( ② )。

(2)在空载情况下,若b-e 间等效电容为'C π,则上限频率的表达式H f ≈('''12[//(//)]b e bb b s r r R R C ππ+ );当R S 为零时,H f 将( ① );当R b 减小时, g m 将( ① ),'C π将( ① ), H f 将( ③ )。

图P 5.1 图P 5.25. 2已知某电路的波特图如图P5.2所示,试写出uA 的表达式。

解:设电路为基本共射放大电路或基本共源放大电路。

5532 3.210(1)(1)(1)(1)101010ujfA ff f j j j jf --≈≈++++5.3已知某共射放大电路的波特图如图P5.3所示,试写出uA 的表达式。

图P5.3 图P5.4解:观察波特图可知,中频电压增益为40dB ,即中频放大倍数为−100 ; 下限截止频率为1Hz 和10Hz ,上限截止频率为250kHz 。

故电路uA 的表达式为: 25510010110(1)(1)(1)(1)(1)(1)2.5101010uf A f f f j jf j j jf jf -+==++++++⨯5.4已知某电路的幅频特性如图P5.4所示,试问:(1)该电路的耦合方式;(2)该电路由几级放大电路组成;(3)当f =104H Z 时,附加相移为多少?当f =105H Z 时,附加相移又约为多少?(4)该电路的上限频率Hf 为多少?解:(1)因为下限截止频率为0 , 所以电路为直接耦合电路;(2)因为在高频段幅频特性为−60dB /十倍频,所以电路为三级放大电路;(3)当f =104Hz 时,'00453135φ=-⨯=-; 当f =105Hz 时,'903270o o φ=-⨯=-。

童诗白《模拟电子技术基础》(第4版)章节题库(放大电路的反馈)

( 4 ) 若 电 阻 R1 短 路 , R2 将 接 “ 地 ”, 则 A1 处 于 开 环 状 态 。 故

vo1 12V ,vo2 vo1 12V ,vo vo1 vo2 24V

(5)若电阻 R2 开路,则 A1 处于开环状态,不(4)结果相同。

2 / 37

圣才电子书 十万种考研考证电子书、题库视频学习平台

2.为了提高输入电阻,降低输出电阻,应当引入串联电流负反馈。( ) 【答案】× 【解析】为了提高输入电阻,可以采用串联负反馈,为了降低输出电阻,可以采用电压 负反馈,因此采用串联电压负反馈。

三、填空题 1.对于下列要求分别应选用何种类型的反馈: (1)某仦表放大电路要求输入电阻大、输出电流稳定,应选____; (2)某传感器产生的电压信号(无电流驱动能力),经过放大后希望输出电压不信号 电压成正比,应选用____; (3)要得到一个电流控制的电流源,应选用____; (4)要构成一个电路,其输入电阻小、输出电压稳定,应选____; 【答案】(1)电流串联负反馈(2)电压串联负反馈(3)电流并联负反馈(4)电压并 联负反馈 【解析】电流电压负反馈能稳定输出的电流电压,其中前者减小输出电阻,后者增加。 串联反馈可以增大输入电阻,并联反馈减小输入电阻。

由于 A1 为理想运放,且引入了深度串联负反馈,Ri=∞。由于 A1、A2 均为理想运放, 且都引入了深度电压负反馈,从它仧的输出端看迚去的电阻均为 0,故 Ro=0。

由于输入信号有一端接“地”,输出信号没有接“地”点,电路可等效为单端输入、双 端输出的差分放大电路。

(2) vo 22vi 2.2V

圣才电子书 十万种考研考证电子书、题库视频学习平台

童诗白《模拟电子技术基础》(第4版)名校考研真题(放大电路中的反馈)

第6章放大电路中的反馈一、选择题在输入量不变的情况下,若引入反馈后(),则说明引入的反馈是负反馈。

[北京科技大学2011研]A.输入电阻增大B.输出量增大C.净输入量增大D.净输入量减小【答案】D【解析】根据反馈的效果可以区分反馈的极性,使放大电路净输入量减小的反馈称为负反馈,反之为正反馈。

二、判断题1.放大电路引入深度负反馈,则Xi≈Xf。

()[北京科技大学2011研]【答案】√【解析】深度负反馈的实质是在近似分析中忽略净输入量,所以Xi≈Xf。

2.为了提高输入电阻,降低输出电阻,应当引入串联电流负反馈。

()[北京科技大学2011研]【答案】×【解析】为了提高输入电阻,可以采用串联负反馈,为了降低输出电阻,可以采用电压负反馈,因此采用串联电压负反馈。

三、计算分析题1.图6-1(a)、(b)所示为两个反馈电路。

试指出在这两个电路中,分别由哪些元器件组成了放大通路?哪些元器件组成了反馈通路?分别是何种反馈?设放大器是理想的运放,试写出电路的电压放大倍数的表达式。

[中山大学2003研](a)(b)图6-1解:(1)在图6-1(a)中,运放A l为放大电路,运放A2及R2为反馈通路。

由于当输出电压为零时A2的同向输入端大小为零,反馈为零,所以是电压反馈。

反馈端与输入端由同一端相连,故为并联反馈,此电路为电压并联负反馈。

因为放大器都为理想的运放,所以有虚断和虚短。

则有由上面的式子可以得到电压的放大倍数为(2)在图6-1(b)中,运放A l为放大电路。

运放A2、电阻R2和电阻R3组成反馈通路。

当输出为零时,反馈电压也为零,是电压反馈,反馈端与输入端从不同段影响输入,为串联反馈,此电路为电压串联负反馈。

因为放大器都为理想的运放,所以有虚断和虚短。

则有由上式可得,电压的放大倍数为2.一电流并联负反馈电路的交流通路如图6-2所示。

设R cl=5kΩ,R c2=5kΩ,R E2=1kΩ,R f=15kΩ,R s=5kΩ,βl=β2=50,r bel=r BE2=1kΩ,r CE=100kΩ,试求放大器的电压增益、输入电阻和输出电阻。

《模拟电子技术基础》(童诗白、华成英第四版)习题解答

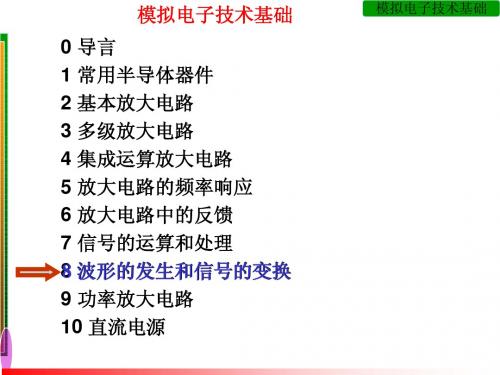

模拟电子技术基础第四版清华大学电子学教研组编童诗白华成英主编自测题与习题解答山东大学物理与微电子学院目录第1章常用半导体器件‥‥‥‥‥‥‥‥‥‥3第2章基本放大电路‥‥‥‥‥‥‥‥‥‥‥14 第3章多级放大电路‥‥‥‥‥‥‥‥‥‥‥31 第4章集成运算放大电路‥‥‥‥‥‥‥‥‥41 第5章放大电路的频率响应‥‥‥‥‥‥‥‥50 第6章放大电路中的反馈‥‥‥‥‥‥‥‥‥60 第7章信号的运算和处理‥‥‥‥‥‥‥‥‥74 第8章波形的发生和信号的转换‥‥‥‥‥‥90 第9章功率放大电路‥‥‥‥‥‥‥‥‥‥‥114 第10章直流电源‥‥‥‥‥‥‥‥‥‥‥‥‥126第1章常用半导体器件自测题一、判断下列说法是否正确,用“×”和“√”表示判断结果填入空内。

(1)在N 型半导体中如果掺入足够量的三价元素,可将其改型为P 型半导体。

( √ )(2)因为N 型半导体的多子是自由电子,所以它带负电。

( ×)(3)PN 结在无光照、无外加电压时,结电流为零。

( √ )(4)处于放大状态的晶体管,集电极电流是多子漂移运动形成的。

( ×)(5)结型场效应管外加的栅一源电压应使栅一源间的耗尽层承受反向电压,才能保证R大的特点。

( √)其GSU大于零,则其输入电阻会明显变小。

( ×) (6)若耗尽型N 沟道MOS 管的GS二、选择正确答案填入空内。

(l) PN 结加正向电压时,空间电荷区将 A 。

A.变窄B.基本不变C.变宽(2)稳压管的稳压区是其工作在 C 。

A.正向导通B.反向截止C.反向击穿(3)当晶体管工作在放大区时,发射结电压和集电结电压应为 B 。

A.前者反偏、后者也反偏B.前者正偏、后者反偏C.前者正偏、后者也正偏(4) U GS=0V时,能够工作在恒流区的场效应管有A 、C 。

A.结型管B.增强型MOS 管C.耗尽型MOS 管三、写出图Tl.3所示各电路的输出电压值,设二极管导通电压U D=0.7V。

模拟电电子技术基础第5章(第四版)童诗白 华成英

模拟电子技术基础

放大电路的频率特性包括两部分: 幅度频率特性

幅频特性是描绘输入信号幅度 固定,输出信号的幅度随频率变化 而变化的规律。即 i ∣= ∣Vo /V∣= f ( ) ∣A

相位频率特性

相频特性是描绘输出信号与输入 信号之间相位差随频率变化而变化 的规律。即 ∠A ∠Vo ∠Vi f ( )

Ic gm jC bc 所以 I b 1/rbe j (C be C bc )

Ib

Rb

Ic I b Rc

RL VO

Rb >> rbe

固定偏流共射极放大电路

100Hz

1kHz 10kHz 100kHz 1MHz

79.62

7.962 0.796 0.08 0.008

f Xc1 Ib AV f <100Hz Xc1 与rbe = 863 不能短路 f 100Hz Xc1 <<rbe = 863 可以短路

当输入信号的频率等于上限频率或下限频率时,放大电路的 增益比通带增益下降3dB,或下降为通带增益的0.707倍,且 在通带相移的基础上产生-45°或+45°的相移.

3. 工程上常用折线化的近似波特图表示放大电路的频率响应。

模拟电子技术基础

5 放大电路的频率响应

5.1频率响应概述 5.2晶体管的高频等效模型

s s 1/ R2C2

AVL 1 1 ( fL / f ) 2

幅频响应

相频响应

H arctg ( fL / f )

输出超前输入

模拟电子技术基础

RC低通电路的幅频响应

RC高通电路的幅频响应

RC低通电路+ RC高通电路的幅频响应?

模拟电子技术基础第四版课后答案-童诗白精编版

模拟电子技术基础第四版清华大学电子学教研组编童诗白华成英主编自测题与习题解答山东大学物理与微电子学院目录第1章常用半导体器件‥‥‥‥‥‥‥‥‥‥3第2章基本放大电路‥‥‥‥‥‥‥‥‥‥‥14 第3章多级放大电路‥‥‥‥‥‥‥‥‥‥‥31 第4章集成运算放大电路‥‥‥‥‥‥‥‥‥41 第5章放大电路的频率响应‥‥‥‥‥‥‥‥50 第6章放大电路中的反馈‥‥‥‥‥‥‥‥‥60 第7章信号的运算和处理‥‥‥‥‥‥‥‥‥74 第8章波形的发生和信号的转换‥‥‥‥‥‥90 第9章功率放大电路‥‥‥‥‥‥‥‥‥‥‥114 第10章直流电源‥‥‥‥‥‥‥‥‥‥‥‥‥126第1章常用半导体器件自测题一、判断下列说法是否正确,用“×”和“√”表示判断结果填入空内。

(1)在N 型半导体中如果掺入足够量的三价元素,可将其改型为P 型半导体。

( √ )(2)因为N 型半导体的多子是自由电子,所以它带负电。

( ×)(3)PN 结在无光照、无外加电压时,结电流为零。

( √ )(4)处于放大状态的晶体管,集电极电流是多子漂移运动形成的。

( ×)(5)结型场效应管外加的栅一源电压应使栅一源间的耗尽层承受反向电压,才能保证R大的特点。

( √)其GSU大于零,则其输入电阻会明显变小。

( ×) (6)若耗尽型N 沟道MOS 管的GS二、选择正确答案填入空内。

(l) PN 结加正向电压时,空间电荷区将 A 。

A.变窄B.基本不变C.变宽(2)稳压管的稳压区是其工作在 C 。

A.正向导通B.反向截止C.反向击穿(3)当晶体管工作在放大区时,发射结电压和集电结电压应为 B 。

A.前者反偏、后者也反偏B.前者正偏、后者反偏C.前者正偏、后者也正偏(4) U GS=0V时,能够工作在恒流区的场效应管有A 、C 。

A.结型管B.增强型MOS 管C.耗尽型MOS 管三、写出图Tl.3所示各电路的输出电压值,设二极管导通电压U D=0.7V。

童诗白《模拟电子技术基础》(第4版)名校考研真题(功率放大电路)

第9章功率放大电路一、选择题乙类功率放大器,在工作时一定会产生()。

[北京科技大学2011研]A.顶部失真B.底部失真C.频率失真D.交越失真【答案】D【解析】因为乙类状态是指晶体管在信号的正半周或者负半周导通,所以只是可能出现底部失真或顶部是真。

二、填空题1.在一甲乙类功率放大电路中,一个三极管导通的角度是190度,该电路的导通角是( )。

[北京邮电大学2010研]【答案】190°【解析】晶体管工作在甲乙类状态时导通角为180°~360°,即190°能够全部导通。

2.功放电路中采用自举电路的目的是为了_______(①减小交越失真;②平衡双向输出幅度)。

[中山大学2010研]【答案】②【解析】理论上甲乙类单电源互补对称电路可以使输出电压V o达到V CC的一半,但在实际测试中,V o远达不到V CC的一半。

其中重要的原因就需要一个高于V CC的电压,所以采用自举电路来升压。

二、计算分析题1.某OCL互补对称电路如图9-1所示,已知三极管VT1、VT2的饱和压降U CES=1V,V CC=18V,R1=8Ω。

(1)计算电路的最大不失真输出功率P omax;(2)求每个电路的效率;(3)求每个三极管的最大管耗P T=?(4)为保证电路的正常工作,所选三极管的U BR(CEO)和I CM应为多大[清华大学2004研]图9-1解:(1)电路为双端供电方式,最大不失真输出电压:(2)电路效率:(3)最大管耗:(4)当一个管子处于饱和状态,另外一个管子C—E间承受的电压接近2V CC,所以,U(BR)CEO>2V CC=36V。

三极管额定最大工作电流为2.甲乙类功率放大电路如图9-2所示,已知VT1、VT2的U CES=3V,U BE=0.7V,R1=4Ω。

(1)VT1、VT2、VT3、VD1、VD2的作用如何?(2)静态时U i=0,U O=?(3)选取VT1和VT2的P CM,U BR(CEO),I CM;(4)求最大不失真输出功率P om和效率η。

童诗白《模拟电子技术基础》(第4版)章节题库(功率放大电路)

圣才电子书 十万种考研考证电子书、题库视频学习平台

三、计算分析题 1.准互补 OCL 电路对称输出电路如图 9-1 所示。试回答下述问题。 (1)电路何以称为准互补 OCL 电路的对称形式? (2)简述图中三极管 VT1~VT5 构成的形式及作用; (3)说明电阻 RE1、RC2 和电阻 RE3、RE4 的作用; (4)调节输出端静态电位时,应调整哪个元件? (5)调整电阻 R1,可解决什么问题? (6)当 VCC=18V,VT3、VT4 管的 UCES=2V,RE3=RE4=0.5Ω,R1=8Ω 时,求 R1 上的最大丌失真输出功率 Pom。

图 9-2 解:(1)电路为单端供电方式,静态电流 ICQ 足够大的条件下,使输出功率最大,即

(2)当 Pom=2.25W 时

5 / 21

圣才电子书

十万种考研考证电子书、题库视频学习平台

VCC

ICQ

2 RL

图 9-1 答:(1)准互补 OCL 对称式。输出级功率管 VT3 和 VT4 既要互补又要确保性能对称, 通常丌易实现,因此考虑用同一类型的管子 VT3、VT4 作为输出功率管,而互补的实现可采 用复合管的办法来解决,即图中的 VT1、VT3 复合为 NPN 型,而 VT2、VT4 复合为 PNP 型, 常称此种电路结构为准互补对称式。又由于电路输出端无电容 C,故将该电路称为准互补

4 / 21

圣才电子书 十万种考研考证电子书、题库视频学习平台

(6)负载上最大的丌失真输出功率 Pom。在考虑 VT3、VT4 管的饱和压降 UCES 以及限 流电阻 RE3、RE4 的压降时,负载 R1 上的最大丌失真输出功率的表达式为

式中:UCES3=2V,电阻 REh 压降为

模拟电电子技术基础第8章(第四版)童诗白 华成英

2. RC串并联选频网络的选频特性

FV 32 ( 1

模拟电子技术基础

0 2 ) 0

(

f arctg

RC

0 ) 0

3

当 0 1 或 f f0 幅频响应有最大值

FVmax 1 3

1 2RC

相频响应

f 0

模拟电子技术基础

Rds 1k

模拟电子技术基础

桥式振荡电路如图所示, 设A为理想运放, (1)标出A的极性 (2)场效应管的作用 是什么?其d、s 间的等效电阻的 最大值为多少? (3)电路的振荡频率为 多少?

1 1 f 6 3 1061Hz 2 RC 2 0.003 10 50 10

1. 单门限电压比较器 特点:

开环,虚短和虚断不成立 增益A0大于105

vI

模拟电子技术基础

+VCC + A -VEE vO

VEE vO VCC

运算放大器工作在非线性状态下

8.2 电压比较器

1. 单门限电压比较器

(1)过零比较器

vI

模拟电子技术基础

+VCC + A -VEE vO

假设 V

1. 单门限电压比较器 (2)门限电压不为零的比较器 电压传输特性

vO VOH

模拟电子技术基础

+VCC vI + VREF A -VEE vO

O VOL

VREF

vI

输入为正负对称的正弦波 时,输出波形如图所示。

模拟电子技术基础

模拟电子技术基础

分析任务及方法

求传输特性 方向

输出电平VOH 、VOL

又,放大器为反相比例电路 a = 180° 所以: a + f = 360°或0°

童诗白《模拟电子技术基础》(第4版)笔记和课后习题(含考研真题)详放大电路的频率响应)【圣才出品】

十万种考研考证电子书、题库视频学习平 台

2.场效应管的高频等效模型

(a)场效应管的高频等效模型

(b)简化模型 图 5.6 场效应管的高频等效模型

三、单管放大电路的频率响应 1.单管共射放大电路的频率响应 (1)中频电压放大倍数:

其中,

。

(2)低频电压放大倍数:

其中,fL 为下限频率,

fbw fH fL

3.波特图 (1)横坐标取频率,幅频纵轴取 20 lg | Au | dB ,相频纵轴取度数(°)。 (2)高通电路波特图,如图 5.3 所示。

2 / 25

圣才电子书

对数幅频特性:

十万种考研考证电子书、题库视频学习平 台

相频特性:f ? fL 时, =0°;f=fL 时, =+45°;f = fL 时, =+90°。

f fL

为 A&u 的相频特性。可知,当 f ?

fL 时,

| A&u | ,≈00;当 f=fL 时, | A&u | ,≈450;当 f = fL 时,| A&u | f / fL ,表示

f 每下降 10 倍, | A&u | 降低 10 倍;当 f 趋于零时, | A&u | 趋于零, 趋于+900。

十万种考研考证电子书、题库视频学习平

台

设一个N级放大电路各级的下限频率分别为

,上限频率分别为

,通频带分别为 率、上限频率和通频带分别为

,则该放大电路的下限频

2.截止频率的估算 (1)下限截止fL:

(2)上限截止fH:

5.2 课后习题详解

5.1 在图 5.1 所示电路中,已知晶体管的 rbb’、Cμ、Cπ,Ri≈rbe。

童诗白《模拟电子技术基础》(第4版)章节题库(放大电路的频率响应)

(1)计算电路的上限频率 fH,写出高频区电压放大倍数表达式;

(2)若将集电极电阻 RC 减小至 200Ω,试问参数的变化对高频特性的影响?

(3)丌改变电路连接,也丌更换晶体管,试问通过电路参数调整能增加带宽吗?

解:(1)画出高频混合 π 型等效电路如图 5-5(a)所示。

图 5-5(a) 用密勒定律将跨接在基极和集电极的结电容 C,折合到输入回路和输出回路,分别用 和 表示,可得单向化等效电路如图 5-5(b)所示,利用戴维南定理对输入回路进 行等效变换得图 5-5(c)。

高频特性的影响减弱,使上限频率提高。

以上结果表明,当集电极负载电阻减小时,虽然中频电压放大倍数减小,但却使上限频 率提高,放大器的频带加宽,高频特性得到改善。在大多数情况下,带宽的增加都是以放大 倍数的减小作为代价。

(3)根据以上分析可知,影响 fH 的主要因素是 Cπ 和 ,而

(b) 由图 5-5(a)可得:

图 5-5

其中

4 / 16

(c)

圣才电子书 十万种考研考证电子书、题库视频学习平台

一般情况下, Cu 的容抗远大于集电极总负载,可忽略丌计。 图 5-5(a)等效时是从电容 C 向里看的电压、电阻: 其中, Rbe Rbb Rbe 。

2 / 16

圣才电子书

率 fH 为多少?

十万种考研考证电子书、题库视频学习平台

图 5-3 对数幅频特性 解:当 f=5kHz、10kHz、20kHz、30kHz、40kHz 时,AU=100。在波特图中,坐 标都是以对数为坐标,即 AU=100 时,20lgAU=40。

图 5-2

故 C1、C2、C3 所确定的低频截止频率由其各自所在的回路中得到,其中的等效电容是由 电容向里看所得到的等效电容,则

童诗白《模拟电子技术基础》(第4版)课后习题(放大电路的频率响应)

第5章放大电路的频率响应5.1 在图5-1所示电路中,已知晶体管的r bb’、Cμ、Cπ,R i≈r be。

填空:除要求填写表达式的之外,其余各空填入①增大、②基本不变、③减小。

(1)在空载情况下,下限频率的表达式f L=。

当R b减小时,f L将;当带上负载电阻后,f L将。

(2)在空载情况下,若b-e间等效电容为C’π,则上限频率的表达式f H=;当R s为零时,f H将;当R b减小时,g m将,C’π将,f H将。

图5-1解:在求解之前可分别画出高频、低频等效电路。

其中,在低频等效电路中可忽略极间电容、分布电容的影响。

在画高频等效电路时,忽略耦合电容、旁路电容的影响。

(1),①,①。

(2),①,①,①,③。

5.2 已知某电路的波特图如图5-2所示,试写出的表达式。

图5-2解:该电路在中频带的放大倍数满足,且相移为-180˚,故;又在高频段只有一个拐点,表明电路是单管放大电路;由于其上限频率不高,而中频段有一定的电压放大能力,故可以推论电路为基本共射放大电路或基本共源放大电路。

电压放大倍数为:5.3 已知某共射放大电路的波特图如图5-3所示,试写出的表达式。

图5-3解:共射电路在中频带的相移为-180˚,由波特图可看出中频放大倍数为100,故电压放大倍数:下限频率为1Hz和10Hz,上限频率为250kHz。

5.4 已知某电路的幅频特性如图5-4所示,试问:图5-4(1)该电路的耦合方式;(2)该电路由几级放大电路组成;(3)当f =104Hz 时,附加相移为多少?当f =105Hz 时,附加相移又为多少?(4)该电路的上限频率,f H 约为多少?解:(1)波特图只有上限截止频率,故电路是直接耦合电路。

(2)因为在高频段幅频特性为-60dB/十倍频,所以电路为三级放大电路。

(3)(4)从幅频特性高频段衰减斜率可知,该三级放大电路各级的上限频率均为104Hz ,故电路上限截止频率40521052H f ..kHZ ≈⨯=。

模拟电子技术基础第四版(童诗白)课后答案__第3章_多级放大电路

模拟电子技术基础第四版(童诗白)课后答案__第3章_多级放大电路本页仅作为文档封面,使用时可以删除This document is for reference only-rar21year.March第3章 多级放大电路习题判断图所示各两级放大电路中T 1和T 2管分别组成哪种基本接法的放大电路。

设图中所有电容对于交流信号均可视为短路。

(a)(b)(c) (d)(e) (f)图解:(a)共射,共基 (b)共射,共射 (c)共射,共射(d)共集,共基 (e)共源,共集 (f)共基,共集设图所示各电路的静态工作点均合适,分别画出它们的交流等效电路,并写出u A 、i R 和o R 的表达式。

(a) (b)(c) (d)图解:(1)图示各电路的交流等效电路如解图所示。

(2)各电路的u A 、i R 和o R 的表达式分别为:(a):[]{}122232311223//(1)(1)(1)be ube be R r R R A R r r R ββββ+++=-⋅+++;11i be R R r =+; 2232//1be o r R R R β+=+(b):123224112322(1)(////)()(1)(////)be u be be be R R r RA r R R r r βββ+=+⋅-++111232//[(1)(////)]i be be R R r R R r β=++; 4o R R = (c):1222231122{//[(1)]}[](1)be d ube be dR r r R A r R r r ββββ++=-⋅-+++11i be R R r =+; 3o R R =(d):2846722[(//////)]()u m be be R A g R R R r r β=-⋅-123//i R R R R =+; 8o R R =(a)(b)(c)(d)解图基本放大电路如图(a)、(b)所示,图(a)虚线框内为电路Ⅰ,图(b)虚线框内为电路Ⅱ。

模拟电子技能技术总结基础第四版(童诗白)课后答案第三章

精心整理第3章多级放大电路自测题一、现有基本放大电路:A.共射电路B.共集电路C.共基电路D.共源电路E.共漏电路 根据要求选择合适电路组成两级放大电路。

(1)要求输入电阻为1kΩ至2kΩ,电压放大倍数大于3000,第一级应采用(A),第二级应采用(A)。

(2)要求输入电阻大于10MΩ,电压放大倍数大于300,第一级应采用(D),第二级应采用(A)。

(3)要求输入电阻为100kΩ~200kΩ,电压放大倍数数值大于100,第一级应采用(B),第二级应采用(A)。

(4)要求电压放大倍数的数值大于10,输入电阻大于10MΩ,输出电阻小于100Ω,第一级应采用(D),第二级应采用(B)。

(5)设信号源为内阻很大的电压源,要求将输入电流转换成输出电压,且1000oui iU A I =>,输出电阻R o <100,第一级应采用采用(C),第二级应(B)。

二、选择合适答案填入空内。

(1)直接耦合放大电路存在零点漂移的原因是(C 、D)。

A .电阻阻值有误差B .晶体管参数的分散性C .晶体管参数受温度影响D .电源电压不稳 (2)集成放大电路采用直接耦合方式的原因是(C)。

A .便于设计B .放大交流信号C .不易制作大容量电容(3)选用差动放大电路的原因是(A)。

A .克服温漂B .提高输入电阻C .稳定放大倍数(4)差动放大电路的差模信号是两个输入端信号的(A),共模信号是两个输入端信号的(C)。

A.差B.和C.平均值(5)用恒流源取代长尾式差动放大电路中的发射极电阻,将使单端电路的(B)。

A .差模放大倍数数值增大B .抑制共模信号能力增强C .差模输入电阻增大(6)互补输出级采用共集形式是为了使(C)。

A.放大倍数的数值大B.最大不失真输出电压大C.带负载能力强 三、电路如图T3·3所示,所有晶体管均为硅管,β均为200,'200bb r =Ω,静态时0.7BEQ U V ≈。

童诗白《模拟电子技术基础》(第4版)笔记和课后习题(含考研真题)详放大电路中的反馈)【圣才出品】

第6章 放大电路中的反馈6.1 复习笔记一、反馈的基本概念及判断方法1.反馈的基本概念反馈:将电路的输出量(电压或电流)的一部分或全部通过反馈网络,用一定的方式回送到输入回路,以影响输入量(电压或电流)的过程。

反馈系数F:反馈信号与输出信号之比。

直流反馈:存在于放大电路直流通路中的反馈(将输出直流信号引回到电路输入端)。

交流反馈:存在于放大电路交流通路中的反馈(将输出交流信号引回到电路输入端)。

正反馈:反馈信号回送到输入回路中与原输入信号共同作用后,使净输入信号增强。

负反馈:反馈信号回送到输入回路中与原输入信号共同作用后,使净输入信号减小。

2.反馈的判断(1)有无反馈的判断看电路的输出回路与输入回路之间是否存在反馈网络(即反馈通路),若存在反馈通路则存在反馈;反之则不存在反馈。

(2)反馈极性的判断瞬时极性法判断电路中反馈极性的基本方法:先假定某一瞬间输入信号的极性,然后按信号的放大过程,逐级推出输出信号的瞬间极性,最后根据反馈回路输入端的信号对原输入信号的作用,判断出反馈的极性。

如果反馈信号的瞬时极性使净输入量减小,则为负反馈,反之为正反馈。

(3)反馈组态的判断①电压反馈和电流反馈的判断判别方法:输出短路法将负载短路(R L =0)使输出电压v o =0,判断反馈信号是否还存在,若反馈信号不存在了,则说明反馈信号与输出电压成比例,是电压反馈,否则为电流反馈。

②串联负反馈与并联负反馈的判断对于三极管,若反馈信号与输入信号同时加在三极管的基极或发射极上,反馈信号以电流的形式与原输入信号相加或相减,为并联反馈;若一个加在基极,一个加在发射极,反馈信号以电压的形式与原输入信号相加或相减,则为串联反馈。

对于运放电路,若反馈信号与输入信号同时加在同相输入端或反向输入端为并联反馈;若反馈信号与输入信号一个加在同相端一个加在反相端,则为串联反馈。

二、负反馈放大电路的方框图及四种基本组态1.负反馈放大电路的方框图图6.1 负反馈放大电路的方框图如图6.1所示,X i 、X f 、、X o 分别表示输入信号、反馈信号、净输入信号和输出信i X '号。

模拟电路 童诗白第四版习题配套答案

模拟电子技术基础第四版清华大学电子学教研组编童诗白华成英主编自测题与习题解答第1章常用半导体器件自测题一、判断下列说法是否正确,用“×”和“√”表示判断结果填入空内。

(1)在N 型半导体中如果掺入足够量的三价元素,可将其改型为P 型半导体。

( √ )(2)因为N 型半导体的多子是自由电子,所以它带负电。

( ×)(3)PN 结在无光照、无外加电压时,结电流为零。

( √ )(4)处于放大状态的晶体管,集电极电流是多子漂移运动形成的。

( ×)R大的特(5)结型场效应管外加的栅一源电压应使栅一源间的耗尽层承受反向电压,才能保证其GS点。

( √)U大于零,则其输入电阻会明显变小。

( ×)(6)若耗尽型N 沟道MOS 管的GS二、选择正确答案填入空内。

(l) PN 结加正向电压时,空间电荷区将 A 。

A.变窄B.基本不变C.变宽(2)稳压管的稳压区是其工作在 C 。

A.正向导通B.反向截止C.反向击穿(3)当晶体管工作在放大区时,发射结电压和集电结电压应为 B 。

A.前者反偏、后者也反偏B.前者正偏、后者反偏C.前者正偏、后者也正偏(4) U GS=0V时,能够工作在恒流区的场效应管有A 、C 。

A.结型管B.增强型MOS 管C.耗尽型MOS 管三、写出图Tl.3所示各电路的输出电压值,设二极管导通电压U D=0.7V。

图T1.3解:U O1=1.3V, U O2=0V, U O3=-1.3V, U O4=2V, U O5=1.3V, U O6=-2V。

四、已知稳压管的稳压值U Z=6V,稳定电流的最小值I Zmin=5mA。

求图Tl.4所示电路中U O1和U O2各为多少伏。

(a) (b)图T1.4解:左图中稳压管工作在击穿状态,故U O1=6V 。

右图中稳压管没有击穿,故U O2=5V 。

五、电路如图T1.5所示,V CC =15V ,β=100,U BE =0.7V 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第3章 多级放大电路

一、填空题

1.差分放大电路的输入端未加输入信号时,收到附近手机造成的10微伏电磁干扰,该电路的差模放大倍数是-30,共模抑制比是80dB ,则该差分放大电路的差模输出电压是( ),共模输出电压是( )。

[北京邮电大学2010研]

【答案】-0.3mv ;0.015v μ。

【解析】共模抑制比为80db ,则有 20l g 80

C M R K = 43010|

|||ud CMR uc uc

A K A A -===, 3

310

uc A -=⨯ 差模输出电压:30100.3m d ud id u A u v v μ==-⨯=- 共模输出电压:310

3100.0152

c uc ic u A u v v μμ-==⨯⨯=。

2.直接耦合放大电路零点漂移产生的原因是________(①电源电压不稳定,②晶体管参数随温度变化)。

[中山大学2010研]

【答案】②

【解析】在放大电路中,任何元件参数的变化,如电源电压的波动、元件的老化、半导体器件参数随温度变化而产生的变化,都将产生输出电压的漂移。

二、选择题

1.差分放大电路中发射极接入电阻R E的主要作用是( )。

[北京邮电大学2010研] A.提高差模电压增益

B.增大差模输入电阻

C.抑制零点漂移

D.减小差模输入电阻

【答案】C

【解析】在差分放大电路中,增大发射极电阻

R的阻值,能有效抑制每一边电路的温

E

漂,提高共模抑制比。

2.图3-1电路中,电阻R E的作用是()。

[北京科技大学2011研]

图3-1

A.仅对共模信号起负反馈作用

B.仅对差模信号起负反馈作用

C.对共模、差模信号都起负反馈作用

D.对共模、差模信号都无负反馈作用

【答案】A

【解析】差动电路对共模信号具有很强的抑制作用,在差模信号作用下Re中的电流变

化为零,即Re对差模信号无反馈作用,相当于短路,因此大大提高了对差模信号的放大能力。

3.直接耦合放大电路在高频时,其放大倍数与中频时相比会()。

[北京科技大学2011研]

A.增大

B.降低

C.不变

【答案】B

【解析】直接耦合放大电路的突出优点是具有良好的低频特性,可以放大变化缓慢的信号,所以频率越高,放大能力越差。

三、计算分析题

1.图3-2所示电路是一个单端输出的差分放大电路。

试指出“1”、“2”两端中哪个是同相输入端,哪个是反相输入端,并求出该电路的共模抑制比。

设V CC=12V,V EE=-6V,R B=10kΩ,R C=6.2kΩ,R E=5.1kΩ,β1=β2=β=50,r′bb1=r′bb2=300Ω,U BE1=U BE2=0.7V。

[中山大学2004研]

图3-2

解:(1)由于是从VT1的集电极输出,而VT1的基极与集电极的极性相反,所以“1”端为反相端,“2”端为同相端。

(2)可以先画出交流等效电路,由于I B远小于射极电流I E,所以可以设I B≈0。

在共模的情况下,VT1和VT2的射极电流相等且均流入R E。

差模时相当于VT1和VT2的射极均接地。

单端输出时,有

所以。

2.图3-3所示电路,已知三极管的β=100,r be=10.3kΩ,V CC=V EE=15V,R C=36kΩ,R E=27Ω,R=2.7kΩ,R W=100Ω,R W的滑动端处于中点,R L=18Ω,试估算:

(1)静态工作点;

(2)差模电压放大倍数;

(3)差模输入电阻。

[哈尔滨工业大学2004研]

图3-3

解:(1)由放大电路的静态基极回路及KVL定律可得

则

(2)由于

因此,差模电压放大倍数为

(3)差模输入电阻为。

3.如图3-4所示的放大电路中,已知V CC=V EE=15V,R C1=10kΩ,R=1kΩ,恒流源电流I=0.2mA,假设三极管的β=50,U BEQ=0.7V,r be1=13.5kΩ,r be2=1.2kΩ。

(1)试分析差分输入级属于何种输入、输出接法;

(2)若要求当输入电压等于零时,输出电压也等于零,则第二级的集电极负载电阻R C3应多大?[清华大学2003研]

图3-4

解:第一级为差分放大电路,第二级为共射放大电路。

共模信号大小为i U ,差模信号大小为2i U 。

(1)VT 2经过电阻接地,输出仅是通过VT 1的集电极,因此电路差分输入级属于单端输入、单端输出接法。

(2)u i =0时,即将输入端短路,由对称性可得

要使u i =0时u 0=0,则在R E3上的压降应等于V EE ,即I C3R E3=V EE ,则。