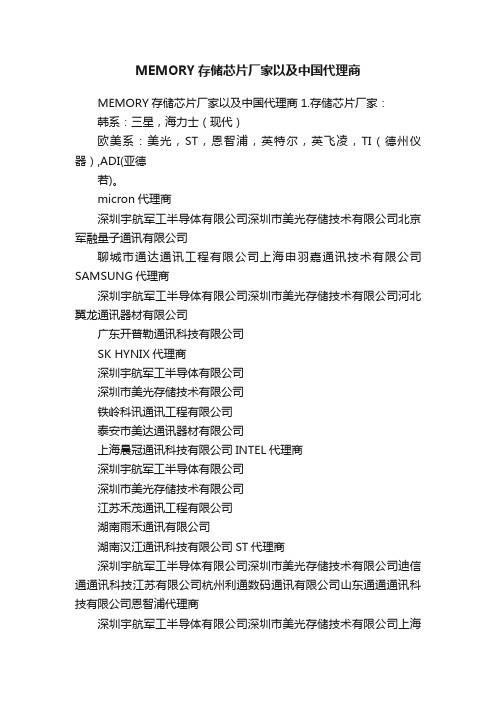

MEMORY存储芯片厂家以及中国代理商

MEMORY存储芯片MT25QU128ABA1ESE-0SIT中文规格书

Features•SPI-compatible serial bus interface•Single and double transfer rate (STR/DTR)•Clock frequency–166 MHz (MAX) for all protocols in STR –90 MHz (MAX) for all protocols in DTR•Dual/quad I/O commands for increased through-put up to 90 MB/s•Supported protocols in both STR and DTR –Extended I/O protocol –Dual I/O protocol –Quad I/O protocol •Execute-in-place (XIP)•PROGRAM/ERASE SUSPEND operations•Volatile and nonvolatile configuration settings •Software reset•Additional reset pin for selected part numbers•Dedicated 64-byte OTP area outside main memory –Readable and user-lockable–Permanent lock with PROGRAM OTP command •Erase capability –Bulk erase–Sector erase 64KB uniform granularity –Subsector erase 4KB, 32KB granularity •Security and write protection–Volatile and nonvolatile locking and software write protection for each 64KB sector –Nonvolatile configuration locking –Password protection–Hardware write protection: nonvolatile bits (BP[3:0] and TB) define protected area size –Program/erase protection during power-up –CRC detects accidental changes to raw data •Electronic signature–JEDEC-standard 3-byte signature (BB18h)–Extended device ID: two additional bytes identify device factory options •JESD47H-compliant–Minimum 100,000 ERASE cycles per sector –Data retention: 20 years (TYP)OptionsMarking•Voltage – 1.7–2.0V U •Density –128Mb128•Device stacking –MonolithicA •Device generationB •Die revisionA •Pin configuration–RESET# and HOLD#8•Sector Size –64KBE •Packages – JEDEC-standard, RoHS-compliant–24-ball T-PBGA, 05/6mm x 8mm (5 x 5 array)12–24-ball T-PBGA 05/6mm x 8mm (4 x 6 array)14–Wafer level chip-scale package,15balls , 9 active balls (XFWLBGA 0.5P)54–8-pin SOP2, 208 mils body width (SO8W)SE –16-pin SOP2, 300 mils body width (SO16W)SF –W-PDFN-8 6mm x 5mm (MLP8 6mm x 5mm)W7–W-PDFN-8 8mm x 6mm (MLP8 8mm x 6mm)W9•Standard security 0•Special options –Standard S –AutomotiveA •Operating temperature range –From –40°C to +85°C IT –From –40°C to +105°CAT找Memory 、FPGA 、二三极管、连接器、模块、光耦、电容电阻、单片机、处理器、晶振、传感器、 滤波器,上深圳市美光存储技术有限公司Signal Assignments – Package Code: SE, W7, W9Figure 7: 8-Pin, SOP2 or W-PDFN (Top View)12348765S#DQ1W#/DQ2V SS1MT25QXXXXXXX 3EXX-XXXXS#DQ1W#/DQ2V SSV CC DQ3/HOLD#C DQ0V CC DQ3/RESET#C DQ0Notes:1.RESET# or HOLD# signals can share pin 7 with DQ3, depending on the selected device(see Part Numbering Ordering Information). When using single and dual I/O commands on these parts, DQ3 must be driven HIGH by the host, or an external pull-up resistor must be placed on the PCB, in order to avoid allowing the HOLD# or RESET# input to float.2.On the underside of the W-PDFN package, there is an exposed central pad that is pulledinternally to V SS . It can be left floating or can be connected to V SS . It must not be con-nected to any other voltage or signal line on the PCB.3.MT25QXXXXXXX8EXX-XXXX not available in 8-pin package.Signal Assignments – Package Code: SFFigure 8: 16-Pin, Plastic Small Outline – SO16 (Top View)12345678161514131211109C DQ0V SS W#/DQ2DQ3/HOLD#V CC RESET#DNU DNU DNU DNU DNU DNU DNU C DQ0V SS W#/DQ2DNU DNU DNU DNU C DQ0V SS W#/DQ2DNU DNU DNU DNU S#DQ1DQ3/HOLD#V CC DNUDNU DNUDNU S#DQ1DQ3/RESET#V CC DNU DNUDNU DNU S#DQ18MT25QXXXXXXX 3EXX-XXXXMT25QXXXXXXX 1EXX-XXXX Notes:1.RESET# or HOLD# signals can share pin 1 with DQ3, depending on the selected device(see Part Numbering Ordering Information). When using single and dual I/O commands on these parts, DQ3 must be driven HIGH by the host, or an external pull-up resistor must be placed on the PCB, in order to avoid allowing the HOLD# or RESET# input to float.128Mb, 1.8V Multiple I/O Serial Flash Memory Signal Assignments – Package Code: SE, W7, W9128Mb, 1.8V Multiple I/O Serial Flash Memory Signal Assignments – Package Code: SF128Mb, 1.8V Multiple I/O Serial Flash MemorySignal Descriptions128Mb, 1.8V Multiple I/O Serial Flash Memory Package Dimensions – Package Code: 12Notes: 1.All dimensions are in millimeters.。

中国存储芯片上市公司

中国存储芯片上市公司中国存储芯片上市公司是指在中国股票市场上市交易的从事存储芯片设计、制造和销售的企业。

存储芯片是计算机、通信设备、消费电子等领域的重要组成部分,对于信息技术的发展起着关键性的作用。

以下是一些具有代表性的中国存储芯片上市公司。

1. 长江存储(600584.SS):成立于2001年,是中国大陆最早的DRAM芯片制造商之一。

公司主要从事DRAM芯片的研发、设计、制造和销售,产品广泛应用于计算机、手机、网络设备等领域。

2. 启明星辰(601360.SS):是中国领先的存储器制造企业之一,主要产品包括闪存芯片、eMMC芯片和SSD等。

公司致力于提供高性能、高可靠性的存储解决方案,产品广泛应用于手机、平板电脑、汽车电子等领域。

3. 南芯科技(600567.SS):是中国最大的SRAM芯片制造商之一,产品主要用于通信设备、工控设备、计算机等高端领域。

公司还积极扩展新兴市场,如物联网、人工智能等。

4. 邦讯技术(002564.SZ):成立于2000年,是中国领先的Flash控制芯片设计企业之一。

公司主要从事闪存控制器的研发、设计和销售,产品广泛应用于手机、数码相机、汽车导航等领域。

5. 中芯国际(688981.SS):成立于2000年,是中国最大的芯片制造企业之一。

公司主要从事整合电路的设计、制造和销售,产品涵盖存储芯片、通信芯片、功放芯片等。

中芯国际在全球范围内享有较高的声誉和市场份额。

6. 兆易创新(603986.SS):成立于2006年,是中国领先的存储芯片设计企业之一。

公司主要从事NOR Flash和EEPROM等产品的研发、设计和销售,广泛应用于电视机、手机、家电等领域。

7. 紫光国微(688012.SS):成立于2004年,是中国领先的专业存储器制造商之一。

公司主要产品包括DDR3、DDR4内存条、UDIMM和SODIMM等,广泛应用于计算机、服务器、通信设备等高端市场。

以上是中国存储芯片上市公司中的一部分,这些企业在技术研发、市场销售等方面取得了显著的成就,对于中国存储芯片产业的发展起到了重要的推动作用。

MEMORY存储芯片N25Q256A13EF840E中文规格书

READ MEMORY OperationsThe device supports default reading and writing to an A[MAX:MIN] of A[23:0] (3-byteaddress).Reading and writing to an A[MAX:MIN] of A[31:0] (4-byte address) is also supported. Se-lection of the 3-byte or 4-byte address range can be enabled in two ways: setting thenonvolatile configuration register or entering the ENABLE 4-BYTE ADDRESS MODE orEXIT 4-BYTE ADDRESS MODE commands. Further details for these settings and com-mands are in the respective register and command sections of the data sheet.Note: When the device is set to the default address range of A[23:0], another method forenabling 4-byte addressing is through the extended address register. Details can befound in Nonvolatile and Volatile Registers.3-Byte AddressTo execute READ MEMORY commands, S# is driven LOW. The command code is inputon DQ n, followed by input on DQ n of three address bytes. Each address bit is latched induring the rising edge of the clock. The addressed byte can be at any location, and theaddress automatically increments to the next address after each byte of data is shiftedout; therefore, the entire memory can be read with a single command. The operation isterminated by driving S# HIGH at any time during data output.Don’t CareDQ[0]C ExtendedDQ1Note: 1.C x = 7 + (A[MAX] + 1).READ MEMORY Operations Timing – Single Transfer RateFigure 32: SUBSECTOR and SECTOR ERASE CommandCDQ0CDQ0[1:0]CDQ0[3:0]Extended Dual QuadNote: 1.For extended SPI protocol, C x = 7 + (A[MAX] + 1).For dual SPI protocol, C x = 3 + (A[MAX] + 1)/2.For quad SPI protocol, C x = 1 + (A[MAX] + 1)/4.BULK ERASE Command质量等级领域:宇航级IC 、特军级IC 、超军级IC 、普军级IC 、禁运IC 、工业级IC ,军级二三极管,功率管等;应用领域:航空航天、船舶、汽车电子、军用计算机、铁路、医疗电子、通信网络、电力工业以及大型工业设备祝您:工作顺利,生活愉快!以深圳市美光存储技术有限公司提供的参数为例,以下为N25Q256A13EF840E的详细参数,仅供参考Figure 33: BULK ERASE CommandC DQ0C DQ[1:0]C DQ[3:0]ExtendedDualQuadPROGRAM/ERASE SUSPEND CommandTo initiate the PROGRAM/ERASE SUSPEND command, S# is driven LOW. The com-mand code is input on DQ0. The operation is terminated by the PROGRAM/ERASE RE-SUME command.PROGRAM/ERASE SUSPEND command enables the memory controller to interrupt and suspend an array PROGRAM or ERASE operation within the program/erase latency.If a SUSPEND command is issued during a PROGRAM operation, then the flag status register bit 2 is set to 1. After erase/program latency time, the flag status register bit 7 is also set to 1, showing the device to be in a suspended state, waiting for any operation (see the Operations Allowed/Disallowed During Device States table).If a SUSPEND command is issued during an ERASE operation, then the flag status regis-ter bit 6 is set to 1. After erase/program latency time, the flag status register bit 7 is also set to 1, showing that device to be in a suspended state, waiting for any operation (see the Operations Allowed/Disallowed During Device States table).If the time remaining to complete the operation is less than the suspend latency, the de-vice completes the operation and clears the flag status register bits 2 or 6, as applicable.Because the suspend state is volatile, if there is a power cycle, the suspend state infor-mation is lost and the flag status register powers up as 80h.During an ERASE SUSPEND operation, a PROGRAM or READ operation is possible in any sector except the one in a suspended state. Reading from a sector that is in a sus-pended state will output indeterminate data. The device ignores a PROGRAM com-mand to a sector that is in an ERASE SUSPEND state; it also sets to 1 the flag status reg-ister bit 4: program failure/protection error, and leaves the write enable latch bit un-changed. The WRITE LOCK REGISTER, WRITE VOLATILE CONFIGURATION REGIS-TER, and WRITE ENHANCED VOLATILE CONFIGURATION REGISTER commands are。

芯片代理商排名

芯片代理商排名芯片代理商排名的评比可以从多个方面来考量,如市场份额、销售业绩、产品质量和技术支持等因素。

以下是一些在全球范围内排名较高的芯片代理商。

1. 英飞凌(Infineon Technologies):总部位于德国,在汽车电子、安全、工业和通信等领域有着广泛的应用。

英飞凌是全球领先的半导体制造商之一,拥有强大的研发实力和丰富的产品线。

2. NXP半导体(NXP Semiconductors):总部位于荷兰,是一家专注于安全和连接解决方案的芯片制造商。

该公司在中央处理器(CPU)和射频技术(RF)方面具有突出的技术实力。

3. 德州仪器(Texas Instruments):该公司总部位于美国,是一家全球领先的半导体公司,主要在模拟和嵌入式处理器领域开展业务。

德州仪器产品广泛应用于消费电子、汽车和工业设备等领域。

4. 美光科技(Micron Technology):总部位于美国,是一家全球领先的存储芯片制造商。

美光科技生产的产品包括动态随机存取存储器(DRAM)和闪存产品,广泛应用于计算机、手机、数据中心等领域。

5. 联发科技(MediaTek):总部位于台湾,是一家全球知名的芯片设计公司。

联发科技专注于移动通信和多媒体技术,其处理器在智能手机和其他移动设备中得到广泛应用。

6. 博通(Broadcom):总部位于美国,是一家在通信和半导体行业拥有广泛影响力的公司。

博通以其在无线通信、网络和视听等领域的产品而闻名。

7. 高通(Qualcomm):总部位于美国,是一家全球领先的无线通信技术公司。

高通专注于移动芯片和通信技术的研发,其骁龙系列处理器在智能手机和移动设备市场上占据重要地位。

8. 恩智浦(NXP):总部位于荷兰,是一家全球领先的汽车电子和可靠性解决方案供应商。

恩智浦的产品广泛应用于汽车电子、工业以及个人消费电子等领域。

9. 立锜科技(ON Semiconductor):总部位于美国,是一家专注于能源效率和便携式电力管理的半导体企业。

中国三大芯片公司

中国三大芯片公司中国三大芯片公司 1三家公司如下:1、华为海思。

尤其是对于华为麒麟处理器,更是作为目前最强国产手机处理器,但事实上对于华为手机芯片、5G芯片的表现,虽然处于全球顶尖水准,但事实上在安防芯片领域,主要用于视频监控等,目前市面上很多行车记录仪,监控等设备均采用了华为海思芯片,所以华为的安防芯片在全球安防芯片市场,更是能够高达70%。

2、汇顶科技相信大家都知道,汇顶科技作为国内一家非常出色芯片企业,目前在指纹识别芯片领域,同样也占到了全球高达50%的市场份额,可以说目前几乎所有智能手机厂商都与汇顶科技有着合作关系,绝大部分手机都采用了汇顶科技的指纹识别芯片,其中也包括屏下指纹识别芯片。

3、比特大陆。

比特大陆,矿友们也是再熟悉不过,作为一家专注于算力芯片的企业,简单点说就是做“矿机芯片”,从目前全球市场份额数据来看,比特大陆同样能够占到全球70%左右的市场份额,事实上在这一领域,中国芯片企业更是一加独大,中国所有厂商更是能够占到全球矿机芯片市场90%+的市场份额。

芯片:集成电路英语:integrated circuit,缩写作 IC;或称微电路(microcircuit)、微芯片(microchip)、晶片/芯片(chip)在电子学中是一种将电路(主要包括半导体设备,也包括被动组件等)小型化的方式,并时常制造在半导体晶圆表面上。

中国三大芯片公司 1摘要中国三大芯片公司: TOP1、紫光集团紫光集团是由清华紫光总公司成立的,主要聚焦于IT服务领域,主要打造从“云-网-端”的产业链,是目前我国最大的综合性集成电路企业,IT服务领域在世界排行第二,也是中国十大芯片企业的第一名,能够为大型客户的信息化需求提供非常完整的IT服务。

TOP2、华为海思海思半导体是一家半导体公司,成立于2004年,公司总部在深圳。

海思产品包括无线网络、数字媒体、固定网络等领域的芯片以及及解决方案,目前面对美国的打压,海思总裁称早就做出过生存极限的假设,目前公司打造存储的芯片可以全部转正。

内存 五大生产厂家

内存五大生产厂家金士顿(Kingston)作为世界第一大内存生产厂商的Kingston,其金士顿内存产品在进入中国市场以来,就凭借优秀的产品质量和一流的售后服务,赢得了众多中国消费者的心。

不过Kingston虽然作为世界第一大内存生产厂商,然而Kingston品牌的内存产品,其使用的内存颗粒确是五花八门,既有Kingston自己颗粒的产品,更多的则是现代(Hynix)、三星(Samsung)、南亚(Nanya)、华邦(Winbond)、英飞凌(Infinoen)、美光(Micron)等等众多厂商的内存颗粒。

利屏利屏是进来新近崛起的一个内存新秀。

利屏科技(深圳)有限公司总部设在美国西部风景如画的世界高科技重镇旧金山。

公司致力于研发、生产和销售利屏LPT 极限高端内存条产品。

公司拥有一支技术过硬的产品研发团队和足迹遍及中、外的专业销售队伍。

产品深受广大游戏玩家和超频爱好者的喜爱。

同时被冠以”超频之神”的美誉。

胜创(Kingmax)成立于1989年的胜创科技有限公司是一家名列中国台湾省前200强的生产企业(Commonwealth Magazine,May 2000),同时也是内存模组的引领生产厂商。

通过严格的质量控制和完善的研发实力,胜创科技获得了ISO-9001证书,同时和IT行业中最优秀的企业建立了合作伙伴关系。

公司以不断创新的设计工艺和追求完美的信念生产出了高性能的尖端科技产品,不断向移动计算领域提供价廉物美的最出色的内存模组。

在SDRAM时期,Kingmax就曾成功的建造了PC150帝国,开启了内存产品的高速时代,也奠定了Kingmax在内存领域领先的地位。

Kingmax始终保持着领先的位置,继续引领着内存发展的方向。

说到KingMax 内存,就不能不说到它独特的”TinyBGA”封装技术专利--作为全球领先的DRAM生产厂商,胜创科技在1997年宣布了第一款基于TinyBGA封装技术的内存模组,这项屡获殊荣的封装技术能以同样的体积大小封装3倍于普通技术所达到的内存容量。

MEMORY存储芯片NUC029LAN中文规格书

1 GENERAL DESCRIPTIONThe NuMicro® NUC029 series 32-bit microcontroller is embedded with ARM® Cortex®-M0 core for industrial control and applications which need rich communication interfaces or require high performance, high integration, and low cost. The Cortex®-M0 is the newest ARM®embedded processor with 32-bit performance at a cost equivalent to the traditional 8-bit microcontroller. The NuMicro® NUC029 series includes four part numbers: NUC029LAN, NUC029NAN, NUC029ZAN, NUC029TAN and NUC029FAE.The NUC029LAN/NUC029NAN/NUC029ZAN/NUC029TAN can run up to 50MHz and operate at2.5V ~ 5.5V, -40℃ ~ 85℃, and the NUC029FAE can run up to 24 MHz and operate at 2.5V ~5.5V, -40℃ ~ 105℃. Therefore, the NUC029 series can afford to support a variety of industrialcontrol and applications which need high CPU performance.The NUC029LAN/NUC029NAN/NUC029ZAN/NUC029TAN offers 64K/64K/32K bytes flash, 4 Kbytes Data Flash, 4 Kbytes flash for the ISP, and 4 Kbytes SRAM. The NUC029FAE offers 16 Kbytes flash, size configurable Data Flash (shared with program flash), 2 Kbytes flash for the ISP, and 2K-bytes SRAM.Many system level peripheral functions, such as I/O Port, EBI (External Bus Interface), Timer, UART, SPI, I2C, PWM, ADC, WDT (Watchdog Timer), WWDT (Window Watchdog Timer), Analog Comparator and Brown-out Detector, have been incorporated into the NUC029 series in order to reduce component count, board space and system cost. These useful functions make the NUC029 series powerful for a wide range of applications.Additionally, the NuMicro®NUC029 series is equipped with ISP (In-System Programming) and ICP (In-Circuit Programming) functions, and IAP (In-Application Programming), which allow the user to update the program memory without removing the chip from the actual end product.Table 1-1 NuMicro® NUC029 Series Difference List2 FEATURES∙ARM® Cortex®-M0 core–Runs up to 50 MHz–One 24-bit system timer–Supports Low Power Sleep mode– A single-cycle 32-bit hardware multiplier–NVIC for the 32 interrupt inputs, each with 4-levels of priority–Supports Serial Wire Debug (SWD) interface and two watchpoints/four breakpoints–Provides hardware divider and supports signed 32-bit dividend, 16-bit divisor operation(NUC029xAN only)∙Operating voltage ranges from 2.5 V to 5.5 V∙Memory–16/32/64 KB Flash for program memory (APROM)–Up to 4 KB Flash for loader (LDROM)–Up to 4 KB SRAM for internal scratch-pad RAM (SRAM)– 4 KB Flash for data memory (Data Flash) (NUC029xAN only)–Configurable Data Flash (NUC029FAE only)∙Clock Control–Programmable system clock source–22.1184 MHz internal oscillator◆Dynamically calibrating the HIRC OSC to 22.1184 MHz ±3% from -40℃ to 105℃by external 32.768 kHz crystal oscillator (LXT) (NUC029FAE only)–4~24 MHz external crystal input–10 kHz low-power oscillator for Watchdog Timer and wake-up in Sleep mode–PLL allows CPU operation up to the maximum 50 MHz (NUC029xAN only)–32.768 kHz external crystal input (LXT) for Power-down wake-up and system operation clock (NUC029FAE only)∙GPIO–Up to 40 general-purpose I/O (GPIO) pins for LQFP/QFN 48-pin package–Four I/O modes:◆Quasi-bidirectional◆Push-pull output◆Open-drain output◆Input only with high impendence–TTL/Schmitt trigger input selectable–I/O pin can be configured as interrupt source with edge/level setting–Supports high driver and high sink I/O mode–Configurable I/O mode after POR∙Timer–Up to four sets of 32-bit timers with 24-bit up counter and one 8-bit prescale counter–Independent clock source for each timer–Provides up to four timer counting modes: one-shot, periodic, toggle and continuous counting–24-bit up counter value is readable through TDR (Timer Data Register)–Supports event counting function to count the input event from external counter pin–24-bit capture value is readable through TCAP (Timer Capture Data Register)–Supports external capture pin for interval measurement◆Supports external capture pin to reset 24-bit up counter◆Supports chip wake-up from Idle/Power-down mode if a timer interrupt signal isgenerated–Supports internal capture triggered while internal ACMP output signal transition(NUC029xAN only)–Supports Inter-Timer trigger mode (NUC029xAN only)–Supports internal signal (CPO0, CPO1) for interval measurement (NUC029FAE only)∙WDT (Watchdog Timer)–Multiple clock sources–Supports wake-up from Power-down or Sleep mode–Interrupt or reset selectable on watchdog time-out–Time-out reset delay period can be selected to 3/18/130/1026 * WDT_CLK (NUC029xAN only)∙WWDT (Window Watchdog Timer) (NUC029xAN only)–6-bit down counter with 11-bit pre-scale for wide range window selected∙PWM Generator and Capture Timer (NUC029xAN only)–Up to four built-in 16-bit PWM generators, providing eight PWM outputs or four complementary paired PWM outputs–Individual clock source, clock divider, 8-bit pre-scalar and dead-zone generator for each PWM generator–PWM interrupt synchronized to PWM period–16-bit digital Capture timers with rising/falling capture inputs–Supports capture interrupt–Internal 10 kHz to PWM clock source–Polar inverse function–Center-aligned type function–Timer duty interrupt enable function–Two kinds of PWM interrupt period type selection–Two kinds of PWM interrupt duty type selection–Period/duty trigger ADC function–PWM Timer synchronous start function∙Enhanced PWM Generator (NUC029FAE only)–Independent 16-bit PWM duty control units with maximum three outputs–Supports group/synchronous/independent/ complementary modes–Supports One-shot or Auto-reload mode–Supports Edge-aligned and Center-aligned type–Programmable dead-zone insertion between complementary channels–Each output has independent polarity setting control–Hardware fault brake protections–Supports duty, period, and fault break interrupts–Supports duty/period trigger ADC conversion–Timer comparing matching event trigger PWM to do phase change–Supports comparator event trigger PWM to force PWM output low for current period –Provides interrupt accumulation function∙UART–Up to two sets of UART devices–Programmable baud-rate generator–Buffered receiver and transmitter, each with 16 bytes FIFO–Optional flow control function (CTS and RTS)–Supports IrDA(SIR) function–Supports RS-485 function–Supports LIN function (NUC029xAN only)∙SPI–Up to two sets of SPI devices–Supports Master/Slave mode–Full-duplex synchronous serial data transfer–Provides 3 wire function–Variable length of transfer data from 8 to 32 bits–MSB or LSB first data transfer–Rx latching data can be either at rising edge or at falling edge of serial clock–Tx sending data can be either at rising edge or at falling edge of serial clock–Supports Byte Suspend mode in 32-bit transmission–4-level depth FIFO buffer–PLL clock source (NUC029xAN only)∙I2C–Up to two sets of I2C modules–Supports Master/Slave mode–Bi-directional data transfer between masters and slaves–Multi-master bus (no central master)–Arbitration between simultaneously transmitting masters without corruption of serial data on the bus–Serial clock synchronization allows devices with different bit rates to communicate via one serial bus–Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer–Programmable clocks allow versatile rate control–Supports 7-bit addressing mode–Supports multiple address recognition (four slave addresses with mask option)–Supports Power-down wake-up function–Supports FIFO function (NUC029FAE only)∙ADC–12-bit SAR ADC with 760 kSPS for NUC029xAN, and 10-bit SAR ADC with 300 kSPS for NUC029FAE–Up to eight single-end analog input channels◆Or four differential analog input channels (NUC029xAN only)–Four operation modes (NUC029FAE only support Single mode)◆Single mode: A/D conversion is performed one time on a specified channel◆Burst mode: A/D converter samples and converts the specified single channeland sequentially stores the result in FIFO◆Single-cycle Scan mode: A/D conversion is performed only one cycle on allspecified channels with the sequence from the smallest numbered channel tothe largest numbered channel◆Continuous Scan mode: A/D converter continuously performs Single-cycle Scanmode until software stops A/D conversion–An A/D conversion can be started by:◆Software Write 1 to ADST bit◆External pin (STADC)◆PWM trigger with optional start delay period–Each conversion result is held in data register with valid and overrun indicators–Each channel has individual data register (NUC029xAN only)–Conversion result can be compared with specified value and user can select whether to generate an interrupt when conversion result matches the compare register setting –Internal temperature sensor output (NUC029xAN only)∙Analog Comparator–Up to four sets of Comparator analog modules–External input or internal band-gap voltage selectable at negative node–Interrupt when compared results change–Power-down wake-up∙EBI (External Bus Interface) for external memory-mapped device access (NUC029LAN/ NUC029NAN only)–Accessible space: 64 KB in 8-bit mode or 128 KB in 16-bit mode–Supports 8-bit or 16-bit data width–Supports byte-write in 16-bit data width∙ISP (In-System Programming) and ICP (In-Circuit Programming)∙IAP (In-Application Programming)∙One built-in temperature sensor with 1℃ resolution (NUC029xAN only)∙BOD (Brown-out Detector)–With 4 levels: 4.4V/3.7V/2.7V/2.2V–Supports Brown-out interrupt and reset option∙96-bit unique ID (UID)∙LVR (Low Voltage Reset)–Threshold voltage level: 2.0V∙Operating Temperature:–NUC029LAN/NUC029NAN/NUC029ZAN/NUC029TAN: -40℃~85℃–NUC029FAE:-40℃~105℃∙Reliability: EFT > ± 4 KV, ESD HBM pass 4 KV∙Packages:–All Green package (RoHS)–48-pin LQFP, 48-pin QFN, 33-pin QFN, 20-pin TSSOP。

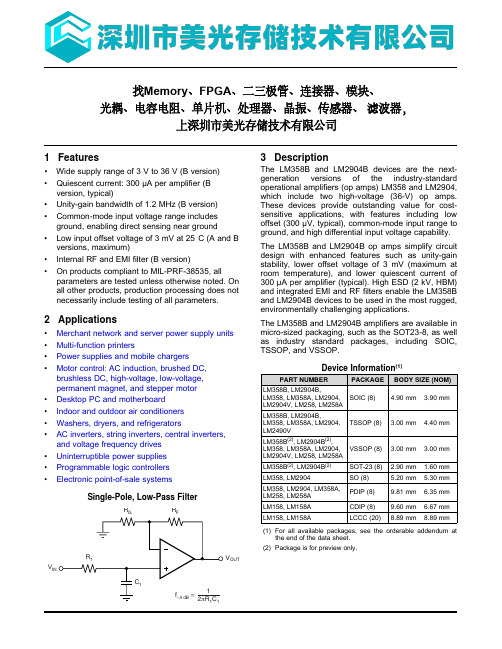

中国存储芯片三巨头

中国存储芯片三巨头

中国存储芯片三巨头:兆易创新、江丰电子、北方华创。

1、兆易创新

兆易创新位列全球Nor flash市场前三位,且随着日美公司的退出,市场份额不断提高;存储价格不断高涨,公司的盈利能力亮眼。

公司打造IDM存储产业链。

2017年10月,公司和合肥市产业投资控股(集团)有限公司签署了存储器研发相关合作协议,合作开展工艺制程19nm存储器的12英寸晶圆存储器研发项目,即合肥长鑫,研发进展顺利。

2、江丰电子

超高纯金属及溅射靶材是生产超大规模集成电路的关键材料之一,公司的超高纯金属溅射靶材产品已应用于世界著名半导体厂商的最先端制造工艺,在16 纳米技术节点实现批量供货,成功打破美、日跨国公司的垄断格局,同时还满足了国内厂商28 纳米技术节点的量产需求,填补了我国电子材料行业的空白。

3、北方华创

北方华创作为设备龙头,深度受益本轮晶圆厂扩建大潮,公司业务涵盖集成电路、LED、光伏等多个领域,多项设备进入14纳米制程。

公司产品线覆盖刻蚀机、PVD、CVD、氧化炉、清洗机、扩散炉、MFC等七大核心品类,下游客户以

中芯国际、长江存储、华力微电子等国内一线晶圆厂为主。

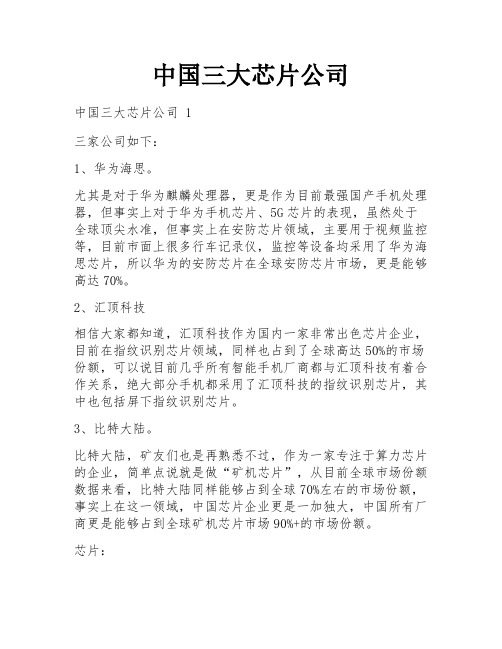

MEMORY存储芯片LM358DR中文规格书

R GR FV INV OUT1Features•Wide supply range of 3V to 36V (B version)•Quiescent current:300µA per amplifier (B version,typical)•Unity-gain bandwidth of 1.2MHz (B version)•Common-mode input voltage range includes ground,enabling direct sensing near ground•Low input offset voltage of 3mV at 25°C (A and B versions,maximum)•Internal RF and EMI filter (B version)•On products compliant to MIL-PRF-38535,allparameters are tested unless otherwise noted.On all other products,production processing does not necessarily include testing of all parameters.2Applications•Merchant network and server power supply units •Multi-function printers•Power supplies and mobile chargers•Motor control:AC induction,brushed DC,brushless DC,high-voltage,low-voltage,permanent magnet,and stepper motor •Desktop PC and motherboard•Indoor and outdoor air conditioners •Washers,dryers,and refrigerators•AC inverters,string inverters,central inverters,and voltage frequency drives •Uninterruptible power supplies •Programmable logic controllers •Electronic point-of-sale systemsSingle-Pole,Low-Pass Filter3DescriptionThe LM358B and LM2904B devices are the next-generation versions of the industry-standard operational amplifiers (op amps)LM358and LM2904,which include two high-voltage (36-V)op amps.These devices provide outstanding value for cost-sensitive applications,with features including low offset (300µV,typical),common-mode input range to ground,and high differential input voltage capability.The LM358B and LM2904B op amps simplify circuit design with enhanced features such as unity-gain stability,lower offset voltage of 3mV (maximum at room temperature),and lower quiescent current of 300µA per amplifier (typical).High ESD (2kV,HBM)and integrated EMI and RF filters enable the LM358B and LM2904B devices to be used in the most rugged,environmentally challenging applications.The LM358B and LM2904B amplifiers are available in micro-sized packaging,such as the SOT23-8,as well as industry standard packages,including SOIC,TSSOP,and VSSOP.Device Information (1)PART NUMBERPACKAGEBODY SIZE (NOM)LM358B,LM2904B,LM358,LM358A,LM2904,LM2904V,LM258,LM258A SOIC (8) 4.90mm ×3.90mmLM358B,LM2904B,LM358,LM358A,LM2904,LM2490VTSSOP (8)3.00mm ×4.40mmLM358B (2),LM2904B (2),LM358,LM358A,LM2904,LM2904V,LM258,LM258A VSSOP (8) 3.00mm ×3.00mm LM358B (2),LM2904B (2)SOT-23(8) 2.90mm ×1.60mm LM358,LM2904SO (8) 5.20mm ×5.30mm LM358,LM2904,LM358A,LM258,LM258A PDIP (8)9.81mm ×6.35mm LM158,LM158A CDIP (8)9.60mm ×6.67mm LM158,LM158ALCCC (20)8.89mm ×8.89mm(1)For all available packages,see the orderableaddendum atthe end of the data sheet.(2)Package is for preview only.找Memory 、FPGA 、二三极管、连接器、模块、光耦、电容电阻、单片机、处理器、晶振、传感器、 滤波器,上深圳市美光存储技术有限公司LM158,LM158A,LM258,LM258ALM358,LM358A,LM358B,LM358BA,LM2904,LM2904B,LM2904BA,LM2904VSLOS068X–JUNE1976–REVISED JUNE2020MIN MAX UNITSupply voltage,V S=([V+]–[V–])LM358B,LM358BA,LM2904B,LM2904BA±20or40V LM158,LM258,LM358,LM158A,LM258A,LM358A,LM2904V±16or32LM2904±13or26Differential input voltage,V ID(2)LM358B,LM358BA,LM2904B,LM2904BA,LM158,LM258,LM358,LM158A,LM258A,LM358A,LM2904V–3232V LM2904–2626Input voltage,V I Either input LM358B,LM358BA,LM2904B,LM2904BA–0.340V LM158,LM258,LM358,LM158A,LM258A,LM358A,LM2904V–0.332LM2904–0.326Duration of output short circuit(one amplifier)to ground at(or below)T A=25°C,V S≤15V(3)Unlimited sOperating ambient temperature,T A LM158,LM158A–55125°C LM258,LM258A–2585LM358B,LM358BA–4085LM358,LM358A070LM2904B,LM2904BA,LM2904,LM2904V–40125Operating virtual-junction temperature,T J150°C Storage temperature,T stg–65150°CLM158,LM158A,LM258,LM258ALM358,LM358A,LM358B,LM358BA,LM2904,LM2904B,LM2904BA,LM2904VSLOS068X–JUNE1976–REVISED JUNE2020 7.3Recommended Operating Conditionsover operating ambient temperature range(unless otherwise noted)MIN MAX UNITV S Supply voltage,V S=([V+]–[V–])LM358B,LM358BA,LM2904B,LM2904BA336V LM158,LM258,LM358,LM158A,LM258A,LM358A,LM2904V330LM2904326V CM Common-mode voltage V–V+–2VT A Operating ambient temperature LM358B,LM358BA–4085°C LM2904B,LM2904BA,LM2904,LM2904V–40125LM358,LM358A070LM258,LM258A–2085LM158,LM158A–55125LM158,LM158A,LM258,LM258ALM358,LM358A,LM358B,LM358BA,LM2904,LM2904B,LM2904BA,LM2904V SLOS068X–JUNE1976–REVISED JUNE2020Typical Characteristics(continued)LM158,LM158A,LM258,LM258A LM358,LM358A,LM358B,LM358BA,LM2904,LM2904B,LM2904BA,LM2904VSLOS068X–JUNE1976–REVISED JUNE2020PARTS PRODUCT FOLDER ORDER NOWTECHNICALDOCUMENTSTOOLS&SOFTWARESUPPORT&COMMUNITYLM158Click here Click here Click here Click here Click here LM158A Click here Click here Click here Click here Click here LM258Click here Click here Click here Click here Click here LM258A Click here Click here Click here Click here Click here LM358Click here Click here Click here Click here Click here LM358A Click here Click here Click here Click here Click here LM358B Click here Click here Click here Click here Click here LM2904Click here Click here Click here Click here Click here LM2904B Click here Click here Click here Click here Click here LM2904V Click here Click here Click here Click here Click here。

存储芯片三巨头

存储芯片三巨头存储芯片产业是信息社会中不可或缺的一环,它直接影响着计算机、手机、智能家居等产品的性能和运行速度。

在全球存储芯片市场中,几家行业巨头占据着主导地位,它们分别是三星电子、美光科技和SK海力士。

本文将介绍这三家公司的背景和业务情况。

首先,三星电子是全球领先的集成电路制造商之一,成立于1969年。

它总部位于韩国首尔,并在全球范围内设有分支机构和研发中心。

三星电子在存储芯片领域处于领先地位,旗下拥有世界上最大的NAND闪存生产线。

该公司还涉足DRAM芯片和SSD(固态硬盘)领域,这使得其成为综合实力最强的存储芯片生产商之一。

同时,三星电子还拥有领先的技术研发能力,不断推出新一代的存储芯片产品,提高性能和降低成本。

由于其领先地位和强大的技术实力,三星电子在全球存储芯片市场占有很大份额。

其次,美光科技是美国一家知名的集成电路制造商,成立于1978年,总部位于加利福尼亚州。

美光科技是全球领先的DRAM芯片和闪存产品制造商之一。

该公司拥有先进的制造工艺和技术实力,能够生产高性能、高质量的存储芯片产品。

此外,美光科技还在新一代存储技术的研发上取得了重要突破,如3D NAND闪存和XPoint存储技术,这些技术将推动存储芯片行业的发展。

美光科技积极投资研发,并与其他公司合作,共同推动存储芯片技术的进步。

最后,SK海力士是韩国第二大半导体公司,成立于1983年。

该公司是全球最大的DRAM制造商之一,也是2D和3D NAND闪存领域的一家重要参与者。

SK海力士致力于提供高品质、高性能的存储芯片产品,并不断创新和研发,推动存储芯片技术的发展。

目前,SK海力士积极推进3D NAND技术的发展,这一技术可以提高存储芯片的容量和性能。

此外,该公司还积极开展与其他公司的合作,拓展市场份额并加强技术竞争力。

综上所述,三星电子、美光科技和SK海力士是全球存储芯片市场的三巨头。

它们在制造工艺、技术实力和产品品质方面都有一定优势,竞争激烈。

MEMORY存储芯片N25Q128A13EF840F中文规格书

Device DescriptionThe N25Q is the first high-performance multiple input/output serial Flash memory de-vice manufactured on 65nm NOR technology. It features execute-in-place (XIP) func-tionality, advanced write protection mechanisms, and a high-speed SPI-compatible businterface. The innovative, high-performance, dual and quad input/output instructionsenable double or quadruple the transfer bandwidth for READ and PROGRAM opera-tions.FeaturesThe memory is organized as 256 (64KB) main sectors that are further divided into 16subsectors each (4096 subsectors in total). The memory can be erased one 4KB subsec-tor at a time, 64KB sectors at a time, or as a whole.The memory can be write protected by software through volatile and nonvolatile pro-tection features, depending on the application needs. The protection granularity is of64KB (sector granularity) for volatile protectionsThe device has 64 one-time programmable (OTP) bytes that can be read and program-med with the READ OTP and PROGRAM OTP commands. These 64 bytes can also bepermanently locked with a PROGRAM OTP command.The device also has the ability to pause and resume PROGRAM and ERASE cycles by us-ing dedicated PROGRAM/ERASE SUSPEND and RESUME instructions.Operating ProtocolsThe memory can be operated with three different protocols:•Extended SPI (standard SPI protocol upgraded with dual and quad operations)•Dual I/O SPI•Quad I/O SPIThe standard SPI protocol is extended and enhanced by dual and quad operations. Inaddition, the dual SPI and quad SPI protocols improve the data access time andthroughput of a single I/O device by transmitting commands, addresses, and dataacross two or four data lines.XIP ModeXIP mode requires only an address (no instruction) to output data, improving randomaccess time and eliminating the need to shadow code onto RAM for fast execution.All protocols support XIP operation. For flexibility, multiple XIP entry and exit methodsare available. For applications that must enter XIP mode immediately after poweringup, XIP mode can be set as the default mode through the nonvolatile configuration reg-ister bits.质量等级领域:宇航级IC、特军级IC、超军级IC、普军级IC、禁运IC、工业级IC,军级二三极管,功率管等;应用领域:航空航天、船舶、汽车电子、军用计算机、铁路、医疗电子、通信网络、电力工业以及大型工业设备祝您:工作顺利,生活愉快!以深圳市美光存储技术有限公司提供的参数为例,以下为N25Q128A13EF840F的详细参数,仅供参考Table 15: Flag Status Register Bit Definitions (Continued)Notes: 1.Register bits are read by READ FLAG STATUS REGISTER command. All bits are volatile.2.These program/erase controller settings apply only to PROGRAM or ERASE command cy-cles in progress, or to the specific WRITE command cycles in progress as shown here.3.Status bits are reset automatically.4.Error bits must be reset by CLEAR FLAG STATUS REGISTER command.5.Typical errors include operation failures and protection errors caused by issuing a com-mand before the error bit has been reset to 0.Command DefinitionsTable 16: Command Set128Mb, 3V , Multiple I/O Serial Flash MemoryCommand Definitions。

MEMORY存储芯片TMS320C6678ACYPA中文规格书

2.5.2.5 I2C Boot Device Configuration

2.5.2.5.1 I2C Master Mode

In master mode, the I2C device configuration uses ten bits of device configuration instead of seven as used in other boot modes. In this mode, the device will make the initial read of the I2C EEPROM while the PLL is in bypass mode. The initial read will contain the desired clock multiplier, which will be set up prior to any subsequent reads.

9

8

7

6

5

Reserved

BAR Config

Table 2-9

PCI Device Configuration Field Descriptions

Bit

Field

9

Reserved

8-5

BAR Config

4-3

Reserved

End of Table 2-9

Description Reserved PCIe BAR registers configuration This value can range from 0 to 0xf. See Table 2-10. Reserved

TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor

国内外IC品牌大全

国内外IC品牌大全IC(Integrated Circuit,集成电路)是现代电子技术中的重要组成部分,广泛应用于各个领域。

在市场上,有许多知名的国内外IC品牌,本文将为您介绍一些具有代表性的品牌。

一、国内IC品牌1. 中芯国际(SMIC):中芯国际是中国领先的半导体集成电路制造企业,成立于2000年,总部位于上海。

中芯国际提供各种类型的集成电路产品,包括模拟芯片、数字芯片、存储芯片等。

2. 瑞芯微(Rockchip):瑞芯微成立于2001年,总部位于北京。

作为一家专注于嵌入式芯片设计的公司,瑞芯微主要生产应用于智能手机、平板电脑、智能电视等产品的芯片。

3. 全志科技(Allwinner):全志科技成立于2007年,总部位于北京。

全志科技专注于移动互联网应用处理器的研发和销售,在平板电脑、智能电视、智能家居等领域具有广泛的应用。

4. 美芯(MEX):美芯是中国领先的模拟集成电路设计公司,成立于2002年,总部位于上海。

美芯专注于提供高性能、高可靠性的模拟集成电路产品,广泛应用于通信、消费电子等领域。

5. 立锜(Leadtrend):立锜成立于1997年,总部位于台湾。

立锜是一家专注于模拟集成电路设计的公司,产品涵盖了电源管理、LED驱动、音频放大等领域。

二、国外IC品牌1. 英特尔(Intel):英特尔是全球知名的半导体制造商,总部位于美国加利福尼亚州。

英特尔主要生产微处理器,广泛应用于个人电脑、服务器、嵌入式系统等领域。

2. 三星电子(Samsung Electronics):三星电子是韩国最大的电子公司之一,总部位于首尔。

三星电子生产各种类型的集成电路产品,包括存储芯片、处理器、显示器等。

3. 台积电(TSMC):台积电是全球领先的半导体代工厂商,成立于1987年,总部位于台湾。

台积电提供先进的制程技术,为各大芯片设计公司提供代工服务。

4. 高通(Qualcomm):高通是全球领先的无线通信技术公司,总部位于美国加利福尼亚州。

MEMORY存储芯片MT40A1G8PM-083EA中文规格书

MEMORY存储芯片MT40A1G8PM083EA中文规格书一、产品概述MT40A1G8PM083EA是一款高性能的MEMORY存储芯片,采用先进的生产工艺,具有低功耗、高速读写、大容量等特点。

本产品适用于各类电子设备,如计算机、服务器、嵌入式系统等,为用户提供稳定可靠的存储解决方案。

二、主要特性1. 存储容量:1GB(8GBIT x 128)2. 工作电压:1.2V / 1.5V / 1.8V(可调)3. 数据传输速率:最高可达2133Mbps4. 封装形式:BGA(Ball Grid Array)5. 工作温度范围:40°C至+95°C6. 低功耗设计,支持深度节能模式7. 兼容JEDEC标准,具备ECC错误校验功能三、产品参数1. 尺寸规格:12mm x 12mm x 1.2mm2. 引脚数量:244个3. 引脚间距:0.8mm4. 电源需求:VDDQ(1.2V / 1.5V / 1.8V),VDD(1.2V / 1.5V / 1.8V)5. 输入输出信号:DQ、DQS、DQS、DM、RESET、CKE、CS、ODT、RAS、CAS、WE6. 时序参数:根据不同工作频率,提供多种时序配置,以满足不同应用需求四、应用领域1. 服务器及数据中心2. 高性能计算3. 嵌入式系统4. 工业控制5. 消费类电子产品敬请关注后续内容,我们将为您提供更多关于MT40A1G8PM083EA 存储芯片的详细信息。

五、兼容性与接口1. 支持DDR4 SDRAM接口,兼容JEDEC DDR4规范。

2. 适用于单通道、双通道和四通道配置,可根据实际应用需求灵活选择。

3. 支持突发长度为8和16的读写操作,提高数据传输效率。

六、可靠性保障1. 内置温度传感器,实时监测芯片工作温度,保障芯片在适宜环境下运行。

2. 采用高品质材料,提高芯片的抗干扰能力和耐用性。

3. 经过严格的老化测试,确保产品在长时间使用下的可靠性。

MEMORY存储芯片MT29F64G08CBAAAL74A3WC1中文规格书

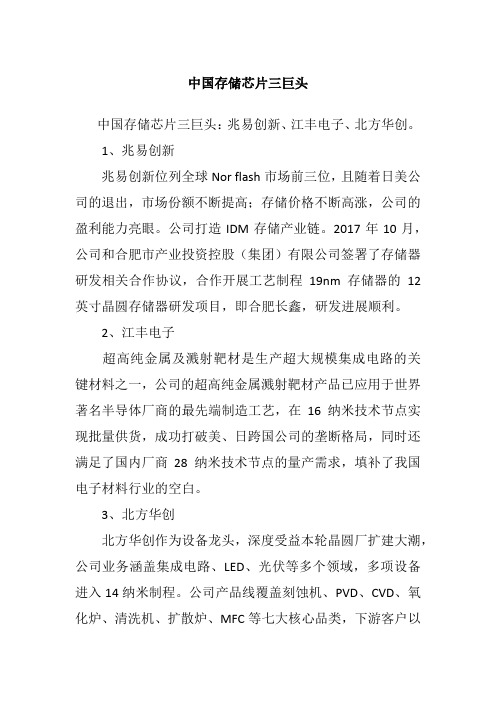

State DiagramFigure 2: Simplified State DiagramSRX = Self refresh exit WRITE = WR, WRS4, WRS8WRITE AP = WRAP , WRAPS4, WRAPS8ZQCL = ZQ LONG CALIBRATION ZQCS = ZQ SHORT CALIBRATIONCommandsequenceACT = ACTIVATEMPR = Multipurpose registerMRS = Mode register setPDE = Power-down entryPDX = Power-down exitPRE = PRECHARGE PREA = PRECHARGE ALL READ = RD, RDS4, RDS8 READ AP = RDAP , RDAPS4, RDAPS8REF = REFRESH RESET = START RESET PROCEDURE SRE = Self refresh entryFunctional DescriptionDDR3 SDRAM uses a double data rate architecture to achieve high-speed operation.The double data rate architecture is an 8n-prefetch architecture with an interface de-signed to transfer two data words per clock cycle at the I/O pins. A single read or writeoperation for the DDR3 SDRAM effectively consists of a single 8n-bit-wide, four-clock-cycle data transfer at the internal DRAM core and eight corresponding n-bit-wide, one-half-clock-cycle data transfers at the I/O pins.The differential data strobe (DQS, DQS#) is transmitted externally, along with data, foruse in data capture at the DDR3 SDRAM input receiver. DQS is center-aligned with datafor WRITEs. The read data is transmitted by the DDR3 SDRAM and edge-aligned to thedata strobes.The DDR3 SDRAM operates from a differential clock (CK and CK#). The crossing of CKgoing HIGH and CK# going LOW is referred to as the positive edge of CK. Control, com-mand, and address signals are registered at every positive edge of CK. Input data is reg-istered on the first rising edge of DQS after the WRITE preamble, and output data is ref-erenced on the first rising edge of DQS after the READ preamble.Read and write accesses to the DDR3 SDRAM are burst-oriented. Accesses start at a se-lected location and continue for a programmed number of locations in a programmedsequence. Accesses begin with the registration of an ACTIVATE command, which is thenfollowed by a READ or WRITE command. The address bits registered coincident withthe ACTIVATE command are used to select the bank and row to be accessed. The ad-dress bits registered coincident with the READ or WRITE commands are used to selectthe bank and the starting column location for the burst access.The device uses a READ and WRITE BL8 and BC4. An auto precharge function may beenabled to provide a self-timed row precharge that is initiated at the end of the burstaccess.As with standard DDR SDRAM, the pipelined, multibank architecture of DDR3 SDRAMallows for concurrent operation, thereby providing high bandwidth by hiding row pre-charge and activation time.A self refresh mode is provided, along with a power-saving, power-down mode. Industrial TemperatureThe industrial temperature (IT) device requires that the case temperature not exceed–40°C or 95°C. JEDEC specifications require the refresh rate to double when T C exceeds85°C; this also requires use of the high-temperature self refresh option. Additionally,ODT resistance and the input/output impedance must be derated when T C is < 0°C or>95°C.Automotive TemperatureThe Automotive temperature (AT) device requires that the case temperature not exceed–40°C or 105°C. Micron specification requires the refresh rate to 4X when T C exceeds95°C; this also requires use of the high-temperature self refresh option. Additionally,ODT resistance and the input/output impedance must be derated when T C is < 0°C or>95°C.General Notes•The functionality and the timing specifications discussed in this data sheet are for theDLL enable mode of operation (normal operation).•Throughout this data sheet, various figures and text refer to DQs as “DQ.” DQ is to beinterpreted as any and all DQ collectively, unless specifically stated otherwise.•The terms “DQS” and “CK” found throughout this data sheet are to be interpreted asDQS, DQS# and CK, CK# respectively, unless specifically stated otherwise.•Complete functionality may be described throughout the document; any page or dia-gram may have been simplified to convey a topic and may not be inclusive of all re-quirements.•Any specific requirement takes precedence over a general statement.•Any functionality not specifically stated is considered undefined, illegal, and not sup-ported, and can result in unknown operation.•Row addressing is denoted as A[n:0]. For example, 1Gb: n = 12 (x16); 1Gb: n = 13 (x4,x8); 2Gb: n = 13 (x16) and 2Gb: n = 14 (x4, x8); 4Gb: n = 14 (x16); and 4Gb: n = 15 (x4,x8).•Dynamic ODT has a special use case: when DDR3 devices are architected for use in asingle rank memory array, the ODT ball can be wired HIGH rather than routed. Referto the Dynamic ODT Special Use Case section.•A x16 device's DQ bus is comprised of two bytes. If only one of the bytes needs to beused, use the lower byte for data transfers and terminate the upper byte as noted:–Connect UDQS to ground via 1kȍ* resistor.–Connect UDQS# to V DD via 1kȍ* resistor.–Connect UDM to V DD via 1kȍ* resistor.–Connect DQ[15:8] individually to either V SS, V DD, or V REF via 1kȍ resistors,* or floatDQ[15:8].*If ODT is used, 1kȍ resistor should be changed to 4x that of the selected ODT.。

MEMORY存储芯片MT29F64G08CBABAWP-B中文规格书

Table 42: DDR3L 34 Ohm Driver I OH/I OL Characteristics: V DD = V DDQ = DDR3L@1.283DDR3L 34 Ohm Output Driver SensitivityIf either the temperature or the voltage changes after ZQ calibration, then the tolerancelimits listed in Table 38 (page 67) can be expected to widen according to Table 43 andTable 44.Table 43: DDR3L 34 Ohm Output Driver Sensitivity DefinitionNote: 1.˂T = T - T(@CALIBRATION); ˂V = V DDQ - V DDQ(@CALIBRATION); and V DD = V DDQ.Table 44: DDR3L 34 Ohm Output Driver Voltage and Temperature SensitivityDDR3L Alternative 40 Ohm DriverTable 45: DDR3L 40 Ohm Driver Impedance CharacteristicsNotes: 1.Tolerance limits assume RZQ of 240˖ ±1% and are applicable after proper ZQ calibra-tion has been performed at a stable temperature and voltage (V DDQ = V DD ; V SSQ = V SS ).Refer to DDR3L 40 Ohm Output Driver Sensitivity (page 70) if either the temperature or the voltage changes after calibration.2.Measurement definition for mismatch between pull-up and pull-down (MM PUPD ). Meas-ure both R ON(PU) and R ON(PD) at 0.5 × V DDQ :MM PUPD = ×100R ON(PU) - R ON(PD)R ON,nom3.For IT and AT devices, the minimum values are derated by 6% when the device operates between –40°C and 0°C (T C ).A larger maximum limit will result in slightly lower minimum currents.DDR3L 40 Ohm Output Driver SensitivityIf either the temperature or the voltage changes after I/O calibration, then the tolerance limits listed in Table 45 can be expected to widen according to Table 46 and Table 47(page 71).Table 46: DDR3L 40 Ohm Output Driver Sensitivity DefinitionNote: 1.˂T = T - T (@CALIBRATION), ˂V = V DDQ - V DDQ(@CALIBRATION); and V DD = V DDQ .Output Characteristics and Operating Conditions Table 48: DDR3L Single-Ended Output Driver CharacteristicsNotes: 1.RZQ of 240˖ ±1% with RZQ/7 enabled (default 34˖ driver) and is applicable after prop-er ZQ calibration has been performed at a stable temperature and voltage (V DDQ = V DD ;V SSQ = V SS ).2.V TT = V DDQ /2.3.See Figure 31 (page 75) for the test load configuration.4.The 6 V/ns maximum is applicable for a single DQ signal when it is switching either from HIGH to LOW or LOW to HIGH while the remaining DQ signals in the same byte lane are either all static or all switching in the opposite direction. For all other DQ signal switch-ing combinations, the maximum limit of 6 V/ns is reduced to 5 V/ns.5.See Figure 28 (page 66) for IV curve linearity. Do not use AC test load.6.See Slew Rate Definitions for Single-Ended Output Signals (page 75) for output slew rate.7.See Figure 28 (page 66) for additional information.8.See Figure 29 (page 73) for an example of a single-ended output signal.4Gb: x4, x8, x16 DDR3L SDRAM Output Characteristics and Operating Conditions。

MEMORY存储芯片MT29F1G16ABBDAH4-IT_D中文规格书

NAND Flash MemoryMT29F1G08ABADAWP, MT29F1G08ABBDAH4, MT29F1G08ABBDAHC, MT29F1G16ABBDAH4, MT29F1G16ABBDAHC, MT29F1G08ABADAH4Features•Open NAND Flash Interface (ONFI) 1.0-compliant1•Single-level cell (SLC) technology•Organization–Page size x8: 2112 bytes (2048 + 64 bytes)–Page size x16: 1056 words (1024 + 32 words)–Block size: 64 pages (128K + 4K bytes)–Device size: 1Gb: 1024 blocks •Asynchronous I/O performance–t RC/t WC: 20ns (3.3V), 25ns (1.8V)•Array performance–Read page: 25µs3–Program page: 200µs (TYP, 3.3V and 1.8V)3–Erase block: 700µs (TYP)•Command set: ONFI NAND Flash Protocol •Advanced command set–Program page cache mode5–Read page cache mode5–One-time programmable (OTP) mode–Read unique ID–Internal data move•Operation status byte provides software method for detecting–Operation completion–Pass/fail condition–Write-protect status•Internal data move operations supported within the device from which data is read •Ready/busy# (R/B#) signal provides a hardware method for detecting operation completion•WP# signal: write protect entire device•First block (block address 00h) is valid when ship-ped from factory with ECC. For minimum required ECC, see Error Management.•Block 0 requires 1-bit ECC if PROGRAM/ERASE cy-cles are less than 1000•RESET (FFh) required as first command after pow-er-on•Alternate method of device initialization (Nand_In-it) after power up4 (contact factory)•Quality and reliability–Data retention: 10 years–Endurance: 100,000 PROGRAM/ERASE cycles •Operating Voltage Range–V CC: 2.7–3.6V–V CC: 1.7–1.95V•Operating temperature:–Commercial: 0°C to +70°C–Extended (ET): –40ºC to +85ºC•Package–48-pin TSOP type 1, CPL2–63-ball VFBGANotes: 1.The ONFI 1.0 specification is available at2.CPL = Center parting line.3.See Electrical Specifications for t R_ECC andt PROG_ECC specifications.4.Available only in the 1.8V VFBGA package.5.Supported only with ECC disabled.Command Definitions Table 5: Command SetREAD ID Parameter TablesTable 6: READ ID Parameters for Address 00hParameter Page Data Structure Tables Table 8: Parameter Page Data Structure。

MEMORY存储芯片MTFC4GACAJCN-1M WT中文规格书

NAND MCP 1Gb+512Mb LPDDR1 End Of LifePCN: 33753Published: 2020-05-28Type:End of LifeDescription:Micron will End of LIfe the NAND MCP 1Gb+512 (J4MK) LPDDR1 due to lackof market demand.Reason:Change in Market DemandProduct Affected:The 1Gb+512 NAND MCP product listed belowAffected Micron Part Number Recommended Replacement Customer Part Number Component*Materials that have been ordered are in bold.Method ofMarketing part numberIdentification:Micron Sites Affected:All SitesLast Purchase Date*:2020-11-28质量等级领域:宇航级IC、特军级IC、超军级IC、普军级IC、禁运IC、工业级IC,军级二三极管,功率管等;应用领域:航空航天、船舶、汽车电子、军用计算机、铁路、医疗电子、通信网络、电力工业以及大型工业设备祝您:工作顺利,生活愉快!以深圳市美光存储技术有限公司提供的参数为例,以下为MTFC4GACAJCN-1M WT的详细参数,仅供参考Last Shipment Date:2021-05-28Early placement of orders is encouraged as an increase in demand for this product could potentially exceed Micron's ability to meet all requests. All products from a previously accepted order that have not shipped as of the last-time purchase date will be considered non-cancelable and non-returnable. Changes to confirmed request dates will also require written approval by Micron. Should additional supply be available after the last-time purchase date, Micron may accept orders for product and such orders placed will be considered non-cancelable and non-returnable.NOTE: Per JEDEC Standard JESD46-C Section 3.2.3; lack of acknowledgment of this PCN within 30 days constitutes acceptance of change.T hank youLegal Disclaimer: The information contained in this message may be privileged and confidential. It is intended to be read only by the individual or entity to whom it is addressed or by their designee. If the reader of this message is not the intended recipient, you are on notice that any distribution of this message, in any form, is strictly prohibited. If you have received this message in error, please immediately notify the sender and delete or destroy any copy of this message.。

MEMORY存储芯片厂家以及中国代理商

MEMORY存储芯片厂家以及中国代理商MEMORY存储芯片厂家以及中国代理商1.存储芯片厂家:韩系:三星,海力士(现代)欧美系:美光,ST,恩智浦,英特尔,英飞凌,TI(德州仪器),ADI(亚德若)。

micron代理商深圳宇航军工半导体有限公司深圳市美光存储技术有限公司北京军融量子通讯有限公司聊城市通达通讯工程有限公司上海申羽嘉通讯技术有限公司SAMSUNG代理商深圳宇航军工半导体有限公司深圳市美光存储技术有限公司河北翼龙通讯器材有限公司广东开普勒通讯科技有限公司SK HYNIX代理商深圳宇航军工半导体有限公司深圳市美光存储技术有限公司铁岭科讯通讯工程有限公司泰安市美达通讯器材有限公司上海晨冠通讯科技有限公司INTEL代理商深圳宇航军工半导体有限公司深圳市美光存储技术有限公司江苏禾茂通讯工程有限公司湖南雨禾通讯有限公司湖南汉江通讯科技有限公司ST代理商深圳宇航军工半导体有限公司深圳市美光存储技术有限公司迪信通通讯科技江苏有限公司杭州利通数码通讯有限公司山东通通通讯科技有限公司恩智浦代理商深圳宇航军工半导体有限公司深圳市美光存储技术有限公司上海华凌通讯有限公司英飞凌代理商深圳宇航军工半导体有限公司深圳市美光存储技术有限公司上海展唐通讯有限公司山东宏景通讯器材有限公司陕西康汇通讯有限公司TI代理商深圳宇航军工半导体有限公司深圳市美光存储技术有限公司北京敏思通讯有限公司江苏维特利通讯科技有限公司华标通讯科技江苏有限公司ADI代理商深圳宇航军工半导体有限公司深圳市美光存储技术有限公司宁波瑞嘉通讯技术有限公司蚌埠海荣通讯工程有限公司渭南耀飞晟达通讯设备有限公司。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MEMORY存储芯片厂家以及中国代理商1.存储芯片厂家:

韩系:三星,海力士(现代)

欧美系:美光,ST,恩智浦,英特尔,英飞凌,TI(德州仪器),ADI(亚德

若)。

micron代理商

深圳宇航军工半导体有限公司深圳市美光存储技术有限公司北京军融量子通讯有限公司

聊城市通达通讯工程有限公司上海申羽嘉通讯技术有限公司SAMSUNG代理商

深圳宇航军工半导体有限公司深圳市美光存储技术有限公司河北翼龙通讯器材有限公司

广东开普勒通讯科技有限公司

SK HYNIX代理商

深圳宇航军工半导体有限公司

深圳市美光存储技术有限公司

铁岭科讯通讯工程有限公司

泰安市美达通讯器材有限公司

上海晨冠通讯科技有限公司INTEL代理商

深圳宇航军工半导体有限公司

深圳市美光存储技术有限公司

江苏禾茂通讯工程有限公司

湖南雨禾通讯有限公司

湖南汉江通讯科技有限公司ST代理商

深圳宇航军工半导体有限公司深圳市美光存储技术有限公司迪信通通讯科技江苏有限公司杭州利通数码通讯有限公司山东通通通讯科技有限公司恩智浦代理商

深圳宇航军工半导体有限公司深圳市美光存储技术有限公司上海华凌通讯有限公司

英飞凌代理商

深圳宇航军工半导体有限公司深圳市美光存储技术有限公司上海展唐通讯有限公司

山东宏景通讯器材有限公司陕西康汇通讯有限公司

TI代理商

深圳宇航军工半导体有限公司深圳市美光存储技术有限公司北京敏思通讯有限公司

江苏维特利通讯科技有限公司华标通讯科技江苏有限公司

ADI代理商

深圳宇航军工半导体有限公司深圳市美光存储技术有限公司宁波瑞嘉通讯技术有限公司

蚌埠海荣通讯工程有限公司

渭南耀飞晟达通讯设备有限公司。