ATmega128单片机概述、系统结构解析知识讲解

第2章_ATmega128硬件结构

广州大学 机电学院 庞志

$100CA

$1006:LDI R1,$0A $1008:LDS R2,$FF00 $100A:ADD R2,R1 $100C:STS $$FFFF0000(($$110A)) $FF00,R2

R1=$0A R2=$$11AA0

2020年5月19日星期二

广州大学 机电学院 庞志

广州大学 机电学院 庞志

ATmega128

单 片 机 方 框 图

2020年5月19日星期二

广州大学 机电学院 庞志

ATmega128

单 片 机 指 令 执 行 过 程

2020年5月19日星期二

广州大学 机电学院 庞志

$1006

10+(0xFF00$)1=0>0(60:xLFDFI 0R0)1,$0A

当RAMPZ0=1: ELPM/SPM可以访问程序存储器地址 $8000——$FFFF(高64K字节)

2020年5月19日星期二

广州大学 机电学院 庞志

2.2.3 指令执行时序

AVR CPU由系统时钟clkCPU驱动。

并行取指和执行时序

2020年5月19日星期二

广州大学 机电学院 庞志

单时钟周期ALU 操作

模拟比较器

2020年5月19日星期二

广州大学 机电学院 庞志

2.1.2 主要性能 (续)

特殊的处理器特点

上电复位 可编程的掉电检测 片内RC振荡器 片内/片外中断源 6种睡眠模式: 空闲模式、ADC噪声抑制模式、省电模

式、掉电模式、Standby模式以及扩展的Standby模式 可选的时钟频率 可选ATmega103兼容模式 全局上拉禁止功能

Bit 6 – T: 位拷贝存储 Bit 4 – S: 符号位,S=N⊕V Bit 2 – N: 负数标志 Bit 0 – C: 进位标志

ATmega128 单片机硬件电路设计

ATmega128 单片机硬件电路设计在本系统中,本小节主要讲ATmega128 单片机的内部资源、工作原理和硬件电路设计等。

2.5.1 ATmega128 芯片介绍ATmega128 为基于AVR RISC 结构的8 位低功耗CMOS 微处理器。

片内ISP Flash 可以通过SPI 接口、通用编程器,或引导程序多次编程。

引导程序可以使用任何接口来下载应用程序到应用Flash 存储器。

通过将8 位RISC CPU 与系统内可编程的Flash 集成在一个芯片内,ATmega128 为许多嵌入式控制应用提供了灵活而低成本的方案。

ATmega128 单片机的功能特点如下:(1)高性能、低功耗的AVR 8 位微处理器(2)先进的RISC 结构①133 条指令大多数可以在一个时钟周期内完成② 32x8 个通用工作寄存器+外设控制寄存器③全静态工作④工作于16 MHz 时性能高达16 MIPS ⑤只需两个时钟周期的硬件乘法器(3)非易失性的程序和数据存储器① 128K 字节的系统内可编程Flash ②寿命: 10,000 次写/ 擦除周期③具有独立锁定位、可选择的启动代码区(4)通过片内的启动程序实现系统内编程① 4K 字节的EEPROM ② 4K 字节的内部SRAM ③多达64K 字节的优化的外部存储器空间④可以对锁定位进行编程以实现软件加密⑤可以通过SPI 实现系统内编程(5)JTAG 接口(与IEEE 1149.1 标准兼容)①遵循JTAG 标准的边界扫描功能②支持扩展的片内调试③通过JTAG 接口实现对Flash,EEPROM,熔丝位和锁定位的编程(6)外设特点①两个具有独立的预分频器和比较器功能的8 位定时器/ 计数器②两个具有预分频器、比较功能和捕捉功能的16 位定时器/ 计数器③具有独立预分频器的实时时钟计数器④两路8 位PWM ⑤ 6 路分辨率可编程(2 到16 位)的PWM ⑥输出比较调制器⑦ 8 路10 位ADC ⑧面向字节的两线接口⑨两个可编程的串行USART ⑩可工作于主机/ 从机模式的SPI 串行接口(7)特殊的处理器特点①上电复位以及可编程的掉电检测②片内经过标定的RC 振荡器③片内/ 片外中断源④ 6 种睡眠模式: 空闲模式、ADC 噪声抑制模式、省电模式、掉电模式、Standby 模式以及扩展的Standby 模式⑤可以通过软件进行选择的时钟频率⑥通过熔丝位可以选择ATmega103 兼容模式⑦全局上拉禁止功能ATmega128 芯片有64 个引脚,其中60 个引脚具有I/O 口功能,资源比较丰富,下面对ATmega128 的各个引脚做简单介绍:VCC:数字电路的电源。

ATmega128的中断系统

任意电平变化触发表示只要引脚上有逻辑电平的变化就会 产生中断申请(不管是上升沿还是下降沿都引起中断触发) 产生中断申请(不管是上升沿还是下降沿都引起中断触发)

4种触发方式中,还有以下的一些不同的特点: 种触发方式中,还有以下的一些不同的特点: 种触发方式中 1.低电平触发是不带中断标志类型的,即只要中断输入引脚PD2 低电平触发是不带中断标志类型的,即只要中断输入引脚 低电平触发是不带中断标志类型的 保持低电平, 或PD3保持低电平,那么将一直会产生中断申请。 保持低电平 那么将一直会产生中断申请。 2.MCU对INT0和INT1的引脚上的上升沿或下降沿变化的识别 对 和 的引脚上的上升沿或下降沿变化的识别 触发),需要I/O时钟信号的存在 ),需要 时钟信号的存在( 时钟同步检测), (触发),需要 时钟信号的存在(由I/O时钟同步检测), 时钟同步检测 属于同步边沿触发的中断类型。 属于同步边沿触发的中断类型。 3.MCU对INT2的引脚上的上升沿或下降沿变化的识别(触 对 的引脚上的上升沿或下降沿变化的识别( 的引脚上的上升沿或下降沿变化的识别 ),以及低电平的识别 触发)是通过异步方式检测的, 以及低电平的识别( 发),以及低电平的识别(触发)是通过异步方式检测的,不 需要I/O时钟信号的存在。因此,这类触发类型的中断经常作 需要 时钟信号的存在。因此, 时钟信号的存在 为外部唤醒源,用于将处在Idle休眠模式,以及处在各种其它 休眠模式, 为外部唤醒源,用于将处在 休眠模式 休眠模式的MCU唤醒。这是由于除了在空闲(Idel)模式时, 唤醒。 休眠模式的 唤醒 这是由于除了在空闲( )模式时, I/O时钟信号还保持继续工作,在其它各种休眠模式下,I/O时 时钟信号还保持继续工作, 时钟信号还保持继续工作 在其它各种休眠模式下, 时 钟信号均是处在暂停状态的。 钟信号均是处在暂停状态的。

ATMEGA128熔丝位配置详解

ATMEGA128熔丝位配置详解熔丝位配置2009-07-29 11:51在配置熔丝位时应特别注意,部分熔丝位(如OCDEN、JTAGEN和SPIEN等)的配置是不可逆的2009年04月17日星期五 11:28引言AVR系列单片机在仿真调试之前,首先必须对AVR的熔丝位和锁定位进行配置。

如果配置不当,则可能造成单片机不能正常工作,严重时可能导致单片机死锁。

因此,对单片机熔丝位和锁定位的正确配置显得尤为重要。

熔丝位是对单片机具体功能和工作模式的限定,其正确配置与否直接影响到单片机能否正常工作;锁定位是对单片机的程序和数据进行加密,以防止单片机中的程序和数据被读出或写入。

在进行配置时,一般先配置熔丝位,再配置锁定位。

锁定位又分为引导程序区锁定位和程序及数据存储器锁定位两类。

对引导程序区锁定位进行编程可以实现两套保护模式,即应用区保护模式和Boot Loader区保护模式;不同的编程配置可以实现不同的加密级别。

对程序及数据存储器锁定位进行编程可以禁止对并行和SPI/JTAG串行编程模式中Flash和EEPROM进一步编程,从而对程序和存储器中的数据进行保护。

由于引导程序锁定位和程序及数据存储器锁定位的配置具有可逆性,因此可根据不同的需要多次编程,灵活改变。

但是,在配置熔丝位时应特别注意,部分熔丝位(如OCDEN、JTAGEN和SPIEN等)的配置是不可逆的。

在采用单一编程下载情况下(例如只采用JTAG下载或者只采用AVRISP并行下载),一旦配置后将不可改变。

鉴于熔丝位配置的重要性,本文以AVR系列的ATmega128单片机为例,详细介绍熔丝位的配置以及在配置过程中常出现的一些问题,并给出相应的解决办法,成功地解决了因熔丝位配置不当而引起的单片机不能正常工作和死锁等一系列问题。

1 熔丝位的配置ATmega128的熔丝位共有3个字节:熔丝位扩展字节、熔丝位高字节和熔丝位低字节。

表1、表2和表3分别描述了所有熔丝位的功能、默认值以及它们是如何映射到熔丝位字节的。

ATMEGA128--AVR教程

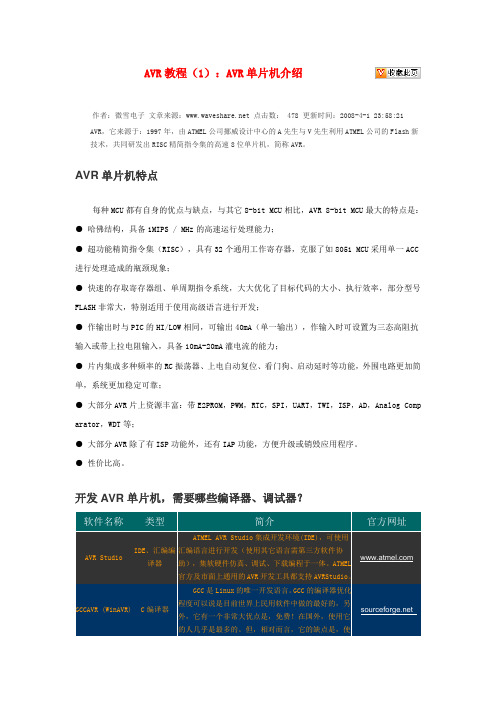

AVR教程(1):AVR单片机介绍作者:微雪电子文章来源: 点击数: 478 更新时间:2008-4-1 23:58:21 AVR,它来源于:1997年,由ATMEL公司挪威设计中心的A先生与V先生利用ATMEL公司的Flash新技术,共同研发出RISC精简指令集的高速8位单片机,简称AVR。

AVR单片机特点每种MCU都有自身的优点与缺点,与其它8-bit MCU相比,AVR 8-bit MCU最大的特点是:●哈佛结构,具备1MIPS / MHz的高速运行处理能力;●超功能精简指令集(RISC),具有32个通用工作寄存器,克服了如8051 MCU采用单一ACC 进行处理造成的瓶颈现象;●快速的存取寄存器组、单周期指令系统,大大优化了目标代码的大小、执行效率,部分型号FLASH非常大,特别适用于使用高级语言进行开发;●作输出时与PIC的HI/LOW相同,可输出40mA(单一输出),作输入时可设置为三态高阻抗输入或带上拉电阻输入,具备10mA-20mA灌电流的能力;●片内集成多种频率的RC振荡器、上电自动复位、看门狗、启动延时等功能,外围电路更加简单,系统更加稳定可靠;●大部分AVR片上资源丰富:带E2PROM,PWM,RTC,SPI,UART,TWI,ISP,AD,Analog Comp arator,WDT等;●大部分AVR除了有ISP功能外,还有IAP功能,方便升级或销毁应用程序。

●性价比高。

开发AVR单片机,需要哪些编译器、调试器?软件名称类型简介官方网址AVR Studio IDE、汇编编译器ATMEL AVR Studio集成开发环境(IDE),可使用汇编语言进行开发(使用其它语言需第三方软件协助),集软硬件仿真、调试、下载编程于一体。

ATMEL官方及市面上通用的AVR开发工具都支持AVRStudio。

GCCAVR (WinAVR) C编译器GCC是Linux的唯一开发语言。

GCC的编译器优化程度可以说是目前世界上民用软件中做的最好的,另外,它有一个非常大优点是,免费!在国外,使用它的人几乎是最多的。

ATMEGA128实验开发板用户手册

ATMEGA128实验开发板用户手册V1.32011年5月E-mail: sdfdlut@1. ATMEGA128单片机概述ATMEGA128单片机是ATMEL公司推出的一款基于AVR内核,采用RISC结构,低功耗CMOS的8位单片机。

由于在一个周期内执行一条指令,ATMEGA128可以达到接近1MIPS/MHz的性能。

其内核将32个工作寄存器和丰富的指令集联结在一起,所有的工作寄存器都与ALU(逻辑单元)直接连接,实现了在一个时钟周期内执行一条指令可以同时访问两个独立的寄存器。

这种结构提高了代码效率,是AVR的运行速度比普通的CISC单片机高出10倍。

ATMEGA128单片机具有以下特点:128KB的可在系统编程/应用编程(ISP/IAP)Flash 程序存储器,4KB E2PROM,4KB SRAM,32个通用工作寄存器,53个通用I/O口,实时时钟计数器(RTC),4个带有比较模式灵活的定时器/计数器,2个可编程的USART接口,一个8为面向字节的TWI(I2C)总线接口,8通道单端或差分输入的10位ADC(其中一个差分通道为增益可调),可编程带内部振荡器的看门狗定时器,一个SPI接口,一个兼容IEEE 1149.1标准的JTAG接口(用于在线仿真调试和程序下载),6种可通过软件选择的节电模式。

2. ATMEGA128实验开发套件本实验开发套件包括:●测试通过的MEGA128实验板1块;●配套资料光盘1张;●AVR ISP并口下载线1条;●5110液晶模块1个;●遥控器1个;●USB ASP下载线(选配);●AVR JTAGICE仿真器(选配)。

其中资料光盘的内容主要包括:●ATMEGA128实验开发板用户手册.pdf(本文档);●AVR教程:⏹WINAVR 使用入门.pdf⏹AVR Studio 使用入门.pdf⏹AVR基本硬件线路设计与分析.pdf⏹芯艺的AVR_GCC教程.pdf⏹AVR的IO结构分析与范例.mht⏹AVR高速嵌入式单片机原理与应用●芯片手册(包括24C02、74HC595以及中文的I2C协议文档等内容)●开发工具软件;⏹AVR Studio V4.12;⏹WINAVR(GCC) 编译器;⏹IAR for AVR V4.10A;⏹并口下载工具PONYPROG V2.06;⏹ICCAVR 双龙提供;图3 新建工程对话框点击Next,进入第三步。

最新atmega128单片机概述-5-安装iccavr

导航、制导与控制

5/28

2.1 第一次注册的结果

导航、制导与控制

6

2.2 第二次注册:

从运行状态进入“ICC AVR”,即可进入软件开发 平台,点击“Help/Register Software,则打开 相应的窗口2。

导航、制导与控制

7/28

2.2 第二次注册的结果

导航、制导与控制

8/28

THANKS!

atmega128单片机概述-5-安 装icca资料: 控制系统说明书—本系统说明书; 控制器接线表—系统接线的全部信息; demo3.hex—系统检验程序; demo3C例程—检验程序C源码;

2. AVR编译器:

《Asmpack》—汇编开发包;

《ICCAVR》—AVRC语言开发包;

《AVR Studio》—AVR开发包;

3. 下载软件:

《Pony prog》—“马头”下载软件;

《双龙下载软件》—国内公司的下载软件;

《串口调试助手》—232口程序.

导航、制导与控制

2/28

1、初步安装“ICCAVR”

直接双击“iccavrdem.exe”即可,但安装完毕后, 只能得到一个使用45天的演示版平台软件,需要 进行相应的注册,才可能继续使用。

导航、制导与控制

3/28

2、注册

在“iccavr keygen.zip”内有两个文件,用于根 据提示信息,产生相应的初始化注册码和序列码。

导航、制导与控制

4/28

2.1 第一次注册:

从运行状态进入“ICC AVR”,即可进入软件开发 平台,点击“Help/Register Software,则打开 相应的窗口1。

9

此课件下载可自行编辑修改,仅供参考! 感谢您的支持,我们努力做得更好!谢谢

ATMEGA128单片机的数据实时采集系统

摘要随着电子科技的不断发展与进步,电压测量成为广大电子领域中必须掌握的过程,并且对测量的精度和采集功能的要求也越来越高,而电压的测量与显示系统甚为重要。

本文介绍的重点是电压数据的采集与显示系统,数据采集与通信控制采用了单片机ATMEGA128来实现,硬件部分是以单片机为核心,还包括ISP下载模块,显示模块,复位和晶振部分,还有一些简单的外围电路。

8路被测电压通过ATMEGA128自带的模-数转换,实现对采集到的数据进行模拟量到数字量的转换,由单片机对数据进行处理,用LED 数码管模块来显示所采集的结果,由相关控制器完成数据接收和显示,c程序编写了更加明了化数据显示界面。

本系统主要包括四大模块:数据采集模块、控制模块、显示模块、A/D转换模块。

绘制电路原理图与工作流程图,并进行调试,最终设计完成了该系统的硬件电路。

在软件编程上,采用了C语言进行编程,开发环境使用相关集成开发环境。

开发了显示模块程序、通道切换程序、A/D转换程序。

关键词:单片机;LED;A/D转换;模块显示;电压测量AbstractAlong with the development of electronic technology progress, voltage measurement of electronic fields become broad must grasp of the process, and the accuracy of measurement and collection function requirements, and more and more is also high voltage measurement and display system is very important. This paper focuses on voltage data acquisition and display system, data collection and communication control using modular design, data collection and communication control adopted MCU ATMEGA128, hardware part is, still include singlechip mode - several module, ISP download module, display module, Reset and part of vibration, and some simple outer circuit. 8 and the voltage to be measured by ATMEGA128 own mode - and to count the collected data for analog to digital, by SCM processing of data, using a digital display module to show the tube, the related results of collecting data receiving and display controller, C programming and the data showed that the interface. This system mainly including four modules: the data acquisition module, control module, display module, A/D conversion module. Draw circuit principle diagram and the work flow, and debugging, finally completed the system design of hardware circuit. In software programming, the C language program development environment, use the integrated development environment. Develop A display module procedures, channel switching procedures, A/D conversion program..Key words: SCM, LED, A/D conversion, module display voltage measurements.目录引言 (1)1绪论 (2)1.1 研究背景及其目的意义 (2)1.2 国内外研究现状 (3)1.3 该课题研究的主要内容 (3)2 数据采集总体设计 (5)2.1 系统设计的基本要求 (5)2.2 数据采集系统结构功能及简介 (5)2.3 硬件开发工具 (6)2.3.1 Altium Designer6.9简介 (6)2.3.2 Altium Designer6.9设计理念 (6)2.3.3 Altium Designer6.9特点 (7)2.4 软件开发工具 (8)2.4.1 ICCA VR (8)2.5 SLISP软件 (9)2.5.1 软件特点 (10)2.5.2 软件使用步骤 (10)3硬件设计 (12)3.1 CUP选型 (12)3.1.1 ATmega128L简介...................................................................................... .123.1.2 ATmega128L特点...................................................................................... .123.1.3 定时器\计数器 ............................................................. 错误!未定义书签。

ATmega128单片机概述、系统结构解析

内部晶振 晶振 JTAG接口 编程计数器 堆栈指针 晶振 时序控制

在线调试

编程Flash

边界扫描

指令寄存器

通用 寄存器 中断单元

编程逻辑

指令译码器

控制线

状态寄存器

两线接口

模 拟 比 较 器

端口E 数据寄存器

端口E方向 数据寄存器

端口B 数据寄存器

端口B方向 数据寄存器

ATmega128单片机概述 ATmega128单片机引脚功能

导航、制导与控制

7/78

2.1 ATmega128单片机概述

基于AVR低功耗CMOS 8位微控制器,近1MIPS/MHz。 6种省电模式: 空闲模式Idle:CPU 停止工作,其他子系统继续工作;

ADC 噪声抑制模式:CPU 和所有的I/O 模块停止运行, 而异步定时器和ADC 继续工作;

导航、制导与控制 18/78

二、ATmega128单片机的 系统结构

19

ATmega128单片机的系统结构 主要内容

1、ATmega128的CPU内核

2、ATmega128 存储器 3、系统时钟及其选项 4、系统控制和复位 5、ATmega128 的中断向量 6、I/O端口 7、定时器/ 计数器(T/C) 8、模数转换器 A/D

AVR 中断响应时间最少为4个时钟周期。 若中断发生时MCU 处于睡眠模式,中断响应时间增加 到8个时钟周期。 中断返回亦需4个时钟。

导航、制导与控制 27/78

1.6.2 ATmega128的中断响应时间

内容

1、ATmega128的CPU内核

2、ATmega128 存储器

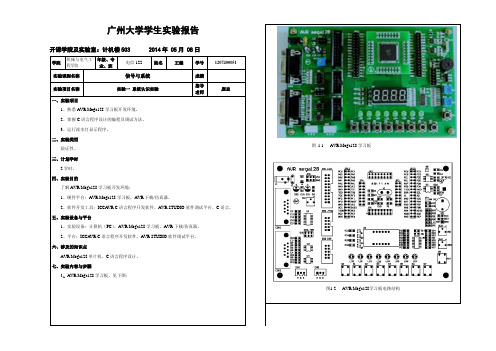

广大ATmega128单片机实验报告实验一 系统认识实验

广州大学学生实验报告开课学院及实验室:计机楼503 2014年 05月 08日学院机械与电气工程学院年级、专业、班电信122 姓名王健学号1207400051实验课程名称信号与系统成绩实验项目名称实验一系统认识实验指导老师庞志一、实验项目1、熟悉AVR Mega128学习板开发环境。

2、掌握C语言程序设计的编程及调试方法。

3、运行流水灯显示程序。

二、实验类型验证性。

三、计划学时2学时。

四、实验目的了解AVR Mega128学习板开发环境:1、硬件平台:AVR Mega128学习板,AVR下载/仿真器。

2、软件开发工具:ICCA VR C语言程序开发软件、AVR STUDIO软件调试平台、C语言。

五、实验设备与平台1、实验设备:计算机(PC),AVR Mega128学习板,AVR下载/仿真器。

2、平台:ICCA VR C语言程序开发软件、AVR STUDIO软件调试平台。

六、涉及的知识点AVR Mega128单片机、C语言程序设计。

七、实验内容与步骤1、AVR Mega128学习板,见下图:图 1.1 AVR Mega128学习板图1.2 AVR Mega128学习板电路结构图1.3 AVR Mega128学习板硬件系统组成连接系统步骤:1)连接AVR下载/仿真器:将AVR下载/仿真器的排线接到AVR Mega128学习板的CH2 JTAG 插座;使用USB连线将AVR下载/仿真器和PC 连接起来。

2)连接AVR Mega128学习板电源:将电源线的圆插头插入到AVR Mega128学习板的J1插座,另一端扁形插头插入PC的USB口,系统运行内置的程序。

2、修改、编译程序1)打开ICCA VR软件,选择Project下拉菜单的Open…打开工程。

图1.4 打开工程示意图2)打开例子程序里面的工程文件01LED.prj:图1.5 打开工程文件示意图3)打开工程后,工程栏里面显示工程包含文件信息,双击右边工程栏中的main.c文件,程序显示在编辑区,可以修改程序。

ATmega128单片机的系统结构综述

3、系统时钟及其选项

Flash 时钟 clkFLASH Flash 时钟控制Flash 接口的 操作。此时钟通常与CPU 时钟是同步的。 异步定时器时钟 clkASY 异步定时器时钟允许异步 定时器/ 计数器直接由外部32 kHz 时钟晶体驱动, 使得此定时器/ 计数器即使在睡眠模式下仍然可 以为系统提供一个实时时钟。 ADC 时钟 clkADC ADC具有专门的时钟。这样可 以在ADC工作的时候停止CPU和I/O时钟以降低 数字电路产生的噪声,从而提高ADC 转换精度。

两种类型的中断: 中断向量表:P91 事件触发并置位中断标志。 只要中断条件满足,就会一直触发。 AVR 退出中断后总是回到主程序并执行一条 指令才可以去执行其他被挂起的中断。 程序存储器空间的最低地址缺省定义为复位和 中断向量。中断向量所在的地址越低,优先级 越高。

1.6 复位和中断处理

3、系统时钟及其选项

时钟源 ATmega128有如下几种通过熔丝位选择的 时钟源。时钟输入到AVR 时钟发生器,并 通往其他合适模块。

3、系统时钟及其选项

默认时钟源 器件出厂时CKSEL = “0001”, SUT = “10”。该默认时钟源为最长启动时间的内 部RC 振荡器。该默认设置保证所有的用 户通过系统内或并行编程得到其需要的时 钟源。

4、系统控制和复位

1.上电复位 AVR内部含有上电复位POR(Power_on Reset) 电路无论何时,只要Vcc低于检测电平Vpot时,器 件进入复位状态。

4、系统控制和复位

2.外部复位 外部复位是由外加在RESET引脚上的低电平将产生 的。当RESET引脚被拉低于Vrst的时间大于1.5µs时 既触发复位过程

AVR单片机Atmega128外扩RAM

AVR单片机Atmega128外扩RAM关键字:AVR单片机Atmega128 外扩RAM由于AVR系列单片机采用的是内部外部RAM统一编址,ATmega128工作在非ATmega 103模式时具有4k+256B的包括寄存器文件(通用工作寄存器)、I/O寄存器、扩展I/O寄存器和内部SRAM的连续内部存储空间。

所以在扩展外部RAM时,和内部SRAM地址重叠的外部RAM地址是不能直接访问的。

也就是说扩展的外部RAM每64k要浪费掉内部SRAM那么大的空间(AT90系列如此)。

所幸的是mega系列解决了这一缺点,专门有一个寄存器XMCRB用来解决对与内部SRAM地址空间相同地址的外部RAM访问。

其低三位XMM2 、XMM1 、XMM0三位的设置,决定高位地址线PC口的哪些口线被释放为普通I/O,而不是作为高位地址。

这样就可以巧妙地屏蔽高位,就ATmega128而言,要避开内部的4k+245B空间,注意到,只要所访问的地址范围大于0X1100(且MCUCR,XMCRA设置正确),那么所访问的就是外部RAM空间。

所以在访问小于4k+245B的外部地址时,只要使地址大于0X10FF就可以访问了。

0X1100用二进制表示为:0001,0001,0000,0000,高位地址线PC5、PC6、PC7没有使用到。

在访问的时候就可设置XMCRB的XMM1、XMM0位为1,释放该三根地址线为普通I/O,将其设为输出。

并且输出0;并在外部地址加上一个虚地址以使地址超过0X1100,如此设置,就可以访问外部0X0000~0X10FF空间了。

超出这个空间,CPU就自动将其识别为外部相应的地址了,不用设置XMCRB寄存器(即不需释放任何总线),也不需加虚地址,按照正常外部RAM访问即可。

在此约定所加的虚地址为0X2000,XMCRB寄存器设置为****,*011,所释放的地址线输出0。

表10-0X10FF范围的寄存器状态和寻址范围(略)表2各寻址范围地址线和寄存器状态表(略)表3各寻址范围地址线和寄存器状态表(略)比如要访问外部0X0200地址,用二进制表示为0000,0010,0000,0000。

用ATmega128控制的多道脉冲幅度分析系统

用ATmega128控制的多道脉冲幅度分析系统在4兆伏静电加速器工作区域内,需建立大范围的核辐射监测系统。

其中多道脉冲幅度分析系统是关键。

对γ射线探测器输出脉宽信号(1~2µs)的峰值进行采集分析,其采集速率必须大于1MS/s[1]。

当前类似系统大都采用C51系列单片机(89C51)作为主控制器,由于C51系列单片机机器周期为12个时钟周期,工作频率为12MHz时指令执行速率仅为1MIPS,其速度慢的缺点影响了多道脉冲分析系统采集及数据传输速率。

我们设计的这套系统第一大特点,采用AVR单片机系列功能最强大的ATmega128,取代C51系列单片机,使系统的工作速度提高了数十倍,采集速率可达到5MS/s。

第二大特点,为解决与上位机通讯速度慢的问题,采用USB 接口技术,使数据传输速率达到1Mbit/s。

因而,该系统从根本上满足了核电信号要求采集速度高,通信容量大的要求。

USB所具有的即插即用、通用性强、易扩展、可靠性高等优点[2]也极大地改善了其使用特性。

1 ATmega128工作原理及其特点ATmega128是AVR系列中功能最强的单片机,运用Harvard结构概念,具有预取指令功能,即程序存储和数据存储具有不同的存储器和总线。

当执行某一指令时,下一指令预先从程序存储器中取出,程序执行效率高[3]。

ATmega128指令执行的时序图如图1所示。

500)this.style.width=500;” border=“0” /> 其机器周期为1个时钟周期,绝大多数指令为单周期指令,工作频率为16MHz时可达到16MIPS的性能。

可产生周期为125ns(频率为8MHz)的方波作为高速模数转换电路的时钟信号,比C51单片机的速度要高20~30倍。

2 ATmega128控制多道脉冲幅度分析系统的结构原理以AVR单片机ATmega128作为控制核心的多道脉冲幅度分析系统主要由程控放大电路、阈值电路、峰值。

Atmega128简介

Atmega128简介Atmega128⽬录主要特性如下:1. · ⾼性能、低功耗的 AVR 8 位微处理器2. · 先进的 RISC 结构3. · ⾮易失性的程序和数据存储器4. · JTAG 接⼝( 与IEEE 1149.1 标准兼容)· 外设特点· 特殊的处理器特点· I/O 和封装1. · 速度等级下⾯对ATmega128的型号标识进⾏解析: ATmega128 是ATMEL公司的 8位系列单⽚机的最⾼配置的⼀款单⽚机,应⽤极其⼴泛主要特性如下:· ⾼性能、低功耗的 AVR 8 位微处理器· 先进的 RISC 结构 – 133 条指令 – ⼤多数可以在⼀个时钟周期内完成 – 32 x 8 通⽤⼯作寄存器 + 外设控制寄存器 – 全静态⼯作 – ⼯作于16 MHz 时性能⾼达16 MIPS – 只需两个时钟周期的硬件乘法器· ⾮易失性的程序和数据存储器 – 128K 字节的系统内可编程Flash 寿命: 10,000 次写/ 擦除周期 – 具有独⽴锁定位、可选择的启动代码区 通过⽚内的启动程序实现系统内编程 真正的读- 修改- 写操作 – 4K字节的EEPROM 寿命: 100,000 次写/ 擦除周期 – 4K 字节的内部SRAM – 多达64K 字节的优化的外部存储器空间 – 可以对锁定位进⾏编程以实现软件加密 – 可以通过SPI 实现系统内编程· JTAG 接⼝( 与IEEE 1149.1 标准兼容) – 遵循JTAG 标准的边界扫描功能 – ⽀持扩展的⽚内调试 – 通过JTAG 接⼝实现对Flash, EEPROM, 熔丝位和锁定位的编程· 外设特点 – 两个具有独⽴的预分频器和⽐较器功能的8 位定时器/ 计数器 – 两个具有预分频器、⽐较功能和捕捉功能的16 位定时器/ 计数器 – 具有独⽴预分频器的实时时钟计数器 – 两路8 位PWM – 6路分辨率可编程(2 到16 位)的PWM – 输出⽐较调制器 – 8路10 位ADC 8 个单端通道 7 个差分通道 2 个具有可编程增益(1x, 10x, 或200x)的差分通道 – ⾯向字节的两线接⼝ – 两个可编程的串⾏USART – 可⼯作于主机/ 从机模式的SPI 串⾏接⼝ – 具有独⽴⽚内振荡器的可编程看门狗定时器 – ⽚内模拟⽐较器· 特殊的处理器特点 – 上电复位以及可编程的掉电检测 – ⽚内经过标定的RC 振荡器 – ⽚内/ ⽚外中断源 – 6种睡眠模式: 空闲模式、ADC 噪声抑制模式、省电模式、掉电模式、Standby 模式以及 扩展的Standby 模式 – 可以通过软件进⾏选择的时钟频率 – 通过熔丝位可以选择ATmega103 兼容模式 – 全局上拉禁⽌功能· I/O 和封装 – 53个可编程I/O ⼝线 – 64引脚TQFP 与 64 引脚 MLF 封装 · ⼯作电压 – 2.7 - 5.5V ATmega128L – 4.5 - 5.5V ATmega128· 速度等级 – 0 - 8 MHz ATmega128L – 0 - 16 MHz ATmega128 ATmega128 TQFP封装现主要有这些型号:ATmega128-16AU、ATmega128-16AI。

ATmega128 ATmega128L 介绍

ATmega128 ATmega128L 介绍

ATmega128 ATmega128L 介绍

ATmega128/128L 带 128K 字节 FLASH 的在线可编程 8 位微控制 器 是 AVR 系列中功能最强的单片机,掌握了 ATmega128 的开发应用, 对其它 AVR 单片机的开发应用等于杀鸡用牛刀,快极了 1 特 点

B 口是一个8 位双向I/O口 每一个引脚都有内部可选上拉电阻 B 口的输出缓冲有对称的驱动特 性 包括吸收和输出电流 当作为输入时 如果外部被拉低 由于上拉电阻的存在引脚将输出电流 在 复位过程中 B 口为三态 即使此时时钟还未起振 B 口还可以用做多种特殊用途 请参阅手册 Port C (PC7..PC0)

通过编程 M103C 熔丝 ATmega128 将在上述RAM I/O引脚和中断向量等方面与ATmega103 兼 容 然而 在这一兼容模式下一些 ATmega128 所拥有的新特性就没有了 • 仅有异步模式的一个 USART 而不是两个 波特率寄存器只有低八位有效 • 一个带两个比较寄存器的16位定时/计数器 而不是两个带三个比较寄存器的16位定时/计数器 • 不支持两线串行接口 • C 口只能作为输出 • G 口只有替换功能(而不是通用 I/O 口) • F 口只能作为数字输入和ADC的模拟输入 • 不支持Boot 装载功能 • 不能调整内部RC振荡器的频率 • 外部存储器接口不能释放任何地址引脚作为通用 I/O 也不能为不同的外部存储器地址区设置不同的 等待状态 另外 还有一些与ATmega103的细小差别 • MCUCSR 中只有 EXTRF 和 PORF • 看门狗超时改变不要求时序 • 外部中断脚 3 - 0 只能作为低电平中断 • USART 没有 FIFO 缓冲 所以数据溢出更早 ATmega103 中未用到的 I/O 位应置 0 以确保在 ATmega128 中的相同操作

AVR单片机ATmega128芯片BootLoader详细介绍

TIFR = TIFR|0x02;

}

}

//每秒向 PC 机发送一个控制字符"C",等待控制字〈soh〉

while(uart_getchar()!=XMODEM_SOH) //receive the start of Xmodem

{

if(TIFR & 0x02)

//timer0 over flow

{

Target: Mega128

Crystal: 16Mhz

Used: T/C0,USART0

*****************************************************/

#include #define SPM_PAGESIZE 256

//M128的一个 Flash 页为256字节(128字)

void quit(void)

{

uart_putchar('O');uart_putchar('K');

uart_putchar(0x0d);uart_putchar(0x0a);

while(!(UCSR0A & 0x20));

//等待结束提示信息回送完成

MCUCR = 0x01;

MCUCR = 0x00;

区本身。引导加载程序还可以对自身进行更新修改,甚至可以将自身删除,使系统的自编程能力消失。引导加载程序区的大小

可以由芯片的熔丝位设置,该段程序区还提供两组锁定位,以便用户选择对该段程序区的不同级别的保护。本节将给出一个实

际的的 Boot Loader 程序,它可以配合 Windows 中的超级终端程序,采用 Xmodem 传输协议,通过 RS232接口下载更新

ATmega128USART资料

2018/11/7

机电系统控制电路设计

9

Atmega128的USART

数据帧格式

串行数据帧由数据字加上同步位( 开始位与停止位) 以 及用于纠错的奇偶校验位构成。USART 接受以下30 种组 合的数据帧格式: 1 个起始位 5、 6、 7、 8 或9 个数据位 无校验位、奇校验或偶校验位 1或2 个停止位 数据帧以起始位开始;紧接着是数据字的最低位,数 据字最多可以有9 个数据位,以数据的最高位结束。如果 使能了校验位,校验位将紧接着数据位,最后是结束位。 当一个完整的数据帧传输后,可以立即传输下一个新的数 据帧,或使传输线处于空闲状态。

机电系统控制电路设计 5

Atmega128的USART

掌握串口通讯需要了解的知识内容为:

电平变换:TTL电平——RS-232电平 了解数据帧格式内容

控制寄存器与状态寄存器的设置

通讯波特率的设置 单片机如何与计算机进行串口通讯 串口调试助手软件 如何实现多机通讯

2018/11/7

2018/11/7 机电系统控制电路设计 1

Atmega128的USART

单片机的通信方式主要有两种:并行通信和串行通信。 并行通信是指数据的各位同时发送或接收。串行通信是 指数据一位一位顺序发送或接收。

单片机的串行接口是一个可编程的全双工串行通信接口。

可以用作异步通信方式(UART)与采用串行接口的外围 设备相连接。 ATmega128 具有两个USART,USART0(PE0-RXD0,PE1TXDO)和USART1(PD2-RXD1,PD3-TXD1)。USART0和 USART1具有不同的I/O寄存器。

机电系统控制电路设计

6

Atmega128的USART

基于ATmega128L的大容量MP3播放机

基于ATMEGA128L的大容量MP3播放机摘要:介绍Atmel公司生产的ATmega128L单片机的特点;提出一种以硬盘为存储介质的MP3播放机的设计方案;给出硬件设计结构和软件设计思路。

引言以Flash为存储介质的MP34播放器,由于其体积小、携带方便、价位合理及其时尚的外围观设计,受到很多人的青睐。

但Flash的价位由于受其制造工艺的制约一直居高不下,从而使MP3播放器的容量仅限于32M、64M、128M等几个档次。

本文旨在提出一种以笔记本硬盘为存储介质的MP3播放机的设计方案。

该款播放机既具有移动硬盘的功能,又可作为MP3播放机使用。

1 系统结构在该系统的设计中,采用Atmel公司生产的ATmega128L作为主控MCU。

整个系统的结构框图如1所示。

PC机通过USB接口实现对硬盘的管理和对MP3歌曲、文档等数据信息的存储。

系统启动后,首先将硬盘上的一部分MP3歌曲送入Flash中存储,由MCU控制将储存于Flash中歌曲的码流信息送入MP3解码芯片中解码,并产生解码输出。

在系统的DAC模块把解码输出转换为模拟音频声音后,经一级音频放大并驱动耳机,实现MP3歌曲的播放功能。

在按键的控制下,通过LCD中菜单选项的选择,实现对歌曲播放模式、声音音效、液晶对比度的调度以及歌曲选择等功能;在播放的同时,LCD上显示的信息除滚动的歌曲名称、演唱者、码流率等ID3信息外,还包括系统供电电池的电量及歌曲播放模式等图标。

系统包括主控MCU、硬盘、Flash缓存、按键、LCD、解码器和D/A转换器等几部分。

2 ATmega128L的主要特点ATmega128L内核为AVR,具有以下特点:*先进的RISC架构,内部具有133条功能强大的指令系统,而且大部分指令是单周期;32个8位通用工作寄存器外围接口控制寄存器。

*内部有128KB在线可重复编程Flash、4KBEEPROM和4KB SRAM。

*有53个I/O引脚,每个I/O口分别对应输入、输出、功能选择、中断等多个寄存器,使功能口和I/O口可以复用,大大增强了端口功能和灵活性,提高了对外围的开发能力。

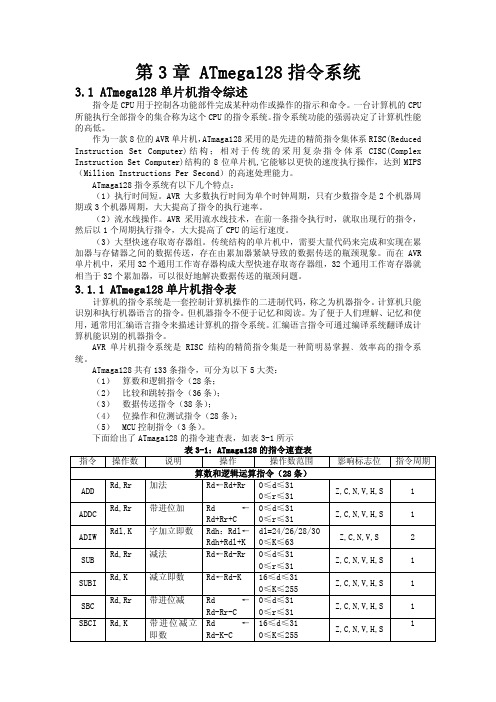

ATmega128指令系统

(1)执行时间短。AVR 大多数执行时间为单个时钟周期,只有少数指令是 2 个机器周

期或 3 个机器周期,大大提高了指令的执行速率。

(2)流水线操作。AVR 采用流水线技术,在前一条指令执行时,就取出现行的指令, 然后以 1 个周期执行指令,大大提高了 CPU 的运行速度。

(3)大型快速存取寄存器组。传统结构的单片机中,需要大量代码来完成和实现在累

SBRS Rr,b

SBIC P,b

SBIS P,b

BRBS s,k BRBC s,k BREQ k BRNE k BRCS k BRCC k BRSH k BRLO k

相对调用子 程序

间接调用子 程序

直接调用子 程序

子程序返回

中断返回

比较相等跳 行

比较

带进位比较

与立即数比 较 寄存器为 0 跳行

寄存器为 1 跳行

识别和执行机器语言的指令。但机器指令不便于记忆和阅读。为了便于人们理解、记忆和使 用,通常用汇编语言指令来描述计算机的指令系统。汇编语言指令可通过编译系统翻译成计

算机能识别的机器指令。

AVR 单片机指令系统是 RISC 结构的精简指令集是一种简明易掌握﹑效率高的指令系

统。

ATmaga128 共有 133 条指令,可分为以下 5 大类: (1) 算数和逻辑指令(28 条;

0≤d≤31 0≤q≤63

2

LD Rd,Z Z 间址取数 Rd←(Z)

0≤d≤31

2

LD Rd,Z+ Z 间 址 取 数 Rd←(Z)

后加 1

Z←Z+1

0≤d≤31

2

LD Rd,-Z Z 减 1 后间址 Z←Z-1

取数

Rd←(Y)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2)AVR单片机在软/硬件开销、速度、性能和成本多方 面取得优化平衡,是高性价比的单片机。

3)内嵌高质量的 Flash程序存储器,擦写方便,支持 ISP和IAP,便于产品 的调试、开发、生产、更新。

AT90S1200/2313/8515/8535 AT89C51

高档ATmega系列单片机

ATmega8/16/32/64/128 存储容量为8/16/32/64/128KB ATmega8515/8535

64脚

6/78 导航、制导与控制

内容

1、AVR单片机简介

AVR单片机主要特性 AVR系列单片机的选型

ATmega128单片机 概述、系统结构

夏洁 2009年3月

1

内容

一、 ATmega128单片机概述系统结构

1、AVR单片机简介(主要特性、选型) 2、ATmega128单片机

二、 ATmega128单片机系统结构

2/78 导航、制导与控制

1、AVR单片机简介

ATMEL公司介绍

是世界上著名的高性能、低功耗、非易失性存 储器和数字集成电路的一流半导体制造公司。

1997年,ATMEL公司出于市场需求,推出 了全新配置的精简指令集RISC单片机高速 8位单片机,简称为AVR。

广泛应用于计算机外设、工业实时控制, 仪器仪表、通信设备、家用电器等各个领 域。

3/78 导航、制导与控制

1.1 AVR单片机主要特性

衡量单片机性能的重要指标

高可靠性、功能强、高速度、低功耗、低价位

ATmega128单片机结构框图

端口F驱动

端口F 数据寄存器

端口F方向 数据寄存器

端口A驱动

端口A 数据寄存器

端口A方向 数据寄存器

端口C驱动

端口C 数据寄存器

端口C方向 数据寄存器

JTAG接口 在线调试 边界扫描 编程逻辑

编程计数器 编程Flash 指令寄存器 指令译码器

控制线

堆栈指针

通用 寄存器

编程计数器 编程Flash 指令寄存器 指令译码器

导航、制导与控制

11/78

ATmega128产品特点

5)特殊微控制器特性

复位、中断源、省电模式等

6)I/O和封装

53个可编程I/O口线 64引脚TQFP与64引脚MLF封装

7)工作电压

2.7~5.5V(ATmega128L) 4.5~5.5V(ATmega128)

8)速度级别

0~8MHZ(ATmega128L) 0~16MHZ(ATmega128)

状态寄存器

内部晶振

晶振 晶振 时序控制

中断单元

两线接口

模

拟 比

端口E 数据寄存器

端口E方向 数据寄存器

端口B 数据寄存器

端口B方向 数据寄存器

端口D 数据寄存器

端口D方向 数据寄存器

端口G 数据寄存器

端口G方向 数据寄存器

较

器

端口E驱动

端口B驱动

端口D驱动

端口G驱动

9 导航、制导与控制

ATmega128产品特点

4/78 导航、制导与控制

1.1 AVR单片机主要时钟分频器

6)高波特率的可靠通信

7)包括多种电路,可增强嵌入式系统的可靠性

电路:自动上电复位、看门狗、掉电检测,

多个复位源等

8)具有多种省电休眠模式、宽电压运行 (2.7~5V),抗干扰能力强,可降低一般8位机 中的软件抗干扰设计的工作量和硬件的使用量。

而异步定时器和ADC 继续工作; 省电模式Power-save:异步定时器继续运行,器件的其

他部分则处于睡眠状态; 掉电模式Power-down:除了中断和硬件复位之外都停止

工作 Standby 模式:振荡器工作而其他部分睡眠; 扩展Standby 模式:允许振荡器和异步定时器继续工作。

8/78 导航、制导与控制

导航、制导与控制

12/78

2.2 ATmega128单片机引脚功能

13 导航、制导与控制

ATmega128单片机结构框图

端口F驱动

端口F 数据寄存器

端口F方向 数据寄存器

端口A驱动

端口A 数据寄存器

端口A方向 数据寄存器

端口C驱动

端口C 数据寄存器

端口C方向 数据寄存器

JTAG接口 在线调试 边界扫描 编程逻辑

1)RICS结构

指令条数 133条指令 – 大多数可以在一个时钟周期内完成

存储器 32 x 8位 通用工作寄存器 + 外设控制寄存器

工作频率 工作于16 MHz 时性能高达16 MIPS

片内乘法器 2个 只需两个时钟周期的硬件乘法器

2)非易失存储器

片上Flash 128K Bytes,104次擦写

2、 ATmega128单片机简介

ATmega128单片机概述 ATmega128单片机引脚功能

7/78 导航、制导与控制

2.1 ATmega128单片机概述

基于AVR低功耗CMOS 8位微控制器,近1MIPS/MHz。 6种省电模式: 空闲模式Idle:CPU 停止工作,其他子系统继续工作; ADC 噪声抑制模式:CPU 和所有的I/O 模块停止运行,

EEPROM 4K Bytes,105次擦写

内部SRAM 4K

可选外部存储器 64K

可编程安全锁、片内可编程SPI接口

3)JITAG接口

边界扫描特性,扩展芯片调试支持,通过其进行可编程Flash、 EEPROM

导航、制导与控制

10/78

ATmega128产品特点

4)外设特性

定时器/计数器 (2个8位)

扩展定时器/计数器 (2个16位)

实时时钟计数器 (1个)

PWM通道 2个8位,6个(分辨率)可编程2~16位

输出比较调制器

8通道10位ADC:

➢ 8个单端通道、7个差分通道、2个可调增益的差分通道

面向字节的双线接口

可编程的连续串口UART 2个

主/从SPI串口、可编程看门狗、片内模拟比较器

9)集成多种器件和多种功能,充分体现了单片机

技术向片上系统SOC的发展方向过渡。

5/78

导航、制导与控制

1.2 AVR系列单片机的选型

AVR单片机有3个档次: 低档Tiny系列单片机, 20脚

Tiny 11/12/13/15/26/28 AT89C1051,AT89C1052

中档(标准) AT90S系列单片机,40脚