基于S3C44BOX的电子词典软件设计与实现DOC

电子行业C语言电子词典报告

电子行业C语言电子词典报告1. 引言本报告旨在介绍电子行业C语言电子词典的设计与实现。

电子词典是一种方便用户查询和使用的工具,具有快速、准确和便捷的特点。

C语言电子词典是专门为C语言程序员设计的词典,用于查询C语言中的关键词、函数和库等相关信息。

本报告将首先介绍电子词典的需求分析,然后详细描述电子词典的设计和实现过程。

最后进行功能测试和性能评估,以验证电子词典的正确性和稳定性。

2. 需求分析电子词典主要针对C语言程序员的需求,具体需求如下:•提供C语言关键词的解释和示例代码;•提供C语言常用函数的说明和用法;•提供C标准库的函数、常量和宏定义等相关信息;•支持用户自定义词汇,并提供相应的解释和示例代码;•支持查询历史记录功能,方便用户追溯查询过的内容;•提供用户界面友好的交互界面,支持快速查询功能。

3. 设计与实现3.1 数据结构设计在设计电子词典的数据结构时,需要考虑到效率和易用性。

本文采用哈希表作为主要的数据结构,用于存储词汇和对应的解释。

哈希表的设计考虑了查询效率的问题,通过合理的哈希函数和解决冲突的方法,来优化查询过程。

每个词汇将作为哈希表的键,对应的解释将作为哈希表的值。

typedef struct Node{char word[MAX_WORD_LENGTH];charexplanation[MAX_EXPLANATION_LENGTH]; } Node;typedef struct Dictionary{Node* nodes[MAX_SIZE];int size;} Dictionary;3.2 查询功能实现电子词典的查询功能是核心功能之一,用户可以输入关键词或函数名进行查询。

查询功能的实现思路如下:1.用户输入关键词;2.根据关键词计算哈希值;3.在哈希表中查找对应的节点;4.如果找到节点,则输出解释和示例代码;5.如果未找到节点,则提示用户未找到相关信息。

3.3 用户界面设计用户界面设计需要考虑到用户的使用习惯和操作习惯,以减小用户的学习成本。

基于人工智能的智能电子词典设计与实现

基于人工智能的智能电子词典设计与实现近年来,随着人工智能技术的不断发展和普及,各种人工智能产品的应用不断扩大,其中智能电子词典也由于其便携、实用的特点而越来越受到人们的追捧。

当前市面上的智能电子词典由于其机能其他不尽人意,面对越来越多的用户需求,本文旨在提出一种基于人工智能的智能电子词典设计,并探讨其实现的方法与技术。

一、智能电子词典的需求与市场智能电子词典是一款便携、实用的翻译工具,其具有词汇量大、海量例句、音频口语、手写输入等实用功能,这使得它成为众多学生、翻译人员和旅游者们不可或缺的一部分。

智能电子词典通过固定词汇的基础上,加入了大量的实用功能,并将其装载进一个便于携带的电子设备中,使人们在学习语言过程中更加高效便利。

据统计,智能电子词典在中国市场占据了极高的份额。

其中以英语智能电子词典的销售量最为突出,二者的销售量占了智能电子词典市场销售总量的八成以上。

由此可见,目前市场对智能电子词典品牌的词汇量和机能的要求已经超出了基础翻译需求,而如何提高其便捷性、准确性、人性化和速度,成为了市面上各种智能电子词典所需要解决的问题。

二、智能电子词典的设计原则与实现思路要实现人工智能的智能电子词典,需从以下几个方面考虑:1. 词汇库的构建词汇库是智能电子词典的基础,在构建智能电子词典的时候,可以通过如今人工智能的语言处理技术来进行词汇库的建立。

通过爬虫技术,可以从不同的网站上获取最新的语言数据,并通过人工智能技术筛选出一些更加权威、更有价值的语言材料,来构筑更加完备、丰富的词汇库。

2. 人性化的交互方式智能电子词典必须注重人性化的交互过程,采用用户友好的界面设计,实现人机交互的舒适度和效率。

在语音输入方面,可以通过语音智能识别技术来实现对人声的识别;在手写输入方面,可以通过对人手写需要进行高精度的识别,从而更方便用户进行输入;在感知需求方面,可以通过智能人机交互技术,特别是视觉、触觉和语言交互,使智能电子词典更智能化、更个性化,从而让用户更舒适地使用。

基于S3C44BOX的电子词典软件设计与实现(DOC)

基于S3C44BOX的电子词典软件设计与实现1 概述此次基于ARM7的电子词典系统开发作业,由我们小组4人合作完成,其中我主要负责软件方面的开发,所做的方面有英译汉软件功能的实现,输入值软件识别功能的实现以及看门狗定时器的实现。

由于不怎么熟悉arm的开发,基本是看着书做,设计思路和方法、功能实现也都是书上怎么来,自己就怎么实现,希望傅老师谅解,这块的基础确实薄弱。

2 S3C44BOX处理器介绍2.1 S3C44BOX简介S3C44BOX微处理器片类集成ARM7TDMI核,采用0.25μm CMOS工艺制造,并在ARM7TDMI核的基础上集成了丰富的外围功能模块,便于低成本设计嵌入式系统应用系统。

片上集成的主要功能如下:➢在ARM7TDMI基础上增加至8KB的Cache。

➢外部扩充存储器控制器(FP/EDO/SDRAM控制,片选逻辑)。

➢LCD控制器(最大支持256色的DSTN),并带有一个LCD专用DMA通道。

➢2个通用DMA通道2个带外部请求引脚的DMA通道。

➢2个带有握手协议的UART,1个SIO。

➢1个多主的I2C总线控制器。

➢1个I2S总线控制器。

➢5个PWM定时器及1个内部定时器。

➢看门狗定时器。

➢71个通用可编程I/O口,8个外部中断源。

➢功耗控制模式:正常,低速,休眠和停止。

➢8路10位ADC。

➢具有日历功能的RTC(实时时钟)。

➢PLL时钟发生器。

2.2 S3C44BOX特点2.2.1 S3C44BOX体系结构➢S3C44BOX是基ARM7TDMI体系结构的SOC。

➢集成了手持设备和通用嵌入式系统应用的解决方案;➢16/32位RISC体系结构和ARM7TDMI处理器内核强大的指令体系;➢Thumb代码压缩机,最大化代码密度同时保持了32位指令的性能;➢基于JTAG的片上集成ICE调试支持解决方案;➢32×8位硬件乘法器;➢实现低功耗SAMBA II(三星ARM处理器嵌入式微控制器总线体系结构)的新型总线结构。

电子词典系统的设计与实现5.0

第三章 数据库设计..................................................................................................... 16

3.1 数据库系统设计................................................................................................................... 16 3.2 电子词典系统数据表结构................................................................................................... 16

电子词典设计与实现

电子词典设计与实现

电子词典的设计与实现可以分为以下几个步骤:

1.需求分析:根据用户需求确定电子词典的功能和特性,例如支持多

种语言、提供联想、显示单词释义、提供例句等。

2.数据收集:收集词典所需的词汇数据,可以通过有关的词典书籍、

在线词典API或者其他途径获取。

3.数据处理:对收集到的词汇数据进行处理和整理,包括建立索引、

分词等操作,以便于后续的查询和展示。

4.用户界面设计:设计电子词典的用户界面,包括框、按钮、显示结

果的区域等元素,要求界面简洁、直观,方便用户使用。

5.查询功能实现:根据用户输入的关键词,在词汇数据中进行查询,

找到对应的词条和释义,并将结果展示给用户。

6.功能扩展:根据需求,可以添加一些附加功能,如联想、生词本管理、发音播放等。

7. 测试与调试:对设计与实现的电子词典进行测试,确保词典的功

能正常运行,没有bug和错误。

8.上线部署:将电子词典部署到服务器或者移动设备上,供用户使用。

9. 后续维护与更新:随着用户使用的反馈和需求变化,持续对电子

词典进行维护和更新,修复bug,添加新功能,提升用户体验。

以上是电子词典设计与实现的一般步骤,具体实现过程可能还会有其

他细节和技术选择,根据具体需求和技术条件进行调整。

C语言电子词典课程设计

C语言电子词典课程设计一、课程目标知识目标:1. 理解C语言中结构体、数组、字符串等基本概念及其应用;2. 学会使用C语言实现基本的查找、插入、删除等数据操作;3. 掌握C语言中文件读写功能,实现对电子词典数据的存储和读取。

技能目标:1. 能够运用结构体创建电子词典的数据结构,并实现单词的录入、查询、修改和删除等功能;2. 学会使用二分查找算法优化电子词典的查询速度,提高程序运行效率;3. 能够独立编写C语言程序,完成一个具有基本功能的电子词典项目。

情感态度价值观目标:1. 培养学生对编程的兴趣,激发他们探索计算机科学领域的热情;2. 培养学生的团队协作意识,学会与他人共同解决问题;3. 培养学生严谨、细心的编程习惯,提高他们面对问题的分析能力和解决能力。

本课程旨在帮助学生在掌握C语言基础知识的基础上,学会运用编程解决实际问题。

结合课程性质、学生特点和教学要求,将课程目标分解为具体的学习成果,以便于后续的教学设计和评估。

在教学过程中,注重培养学生的实际操作能力,提高他们运用C语言解决实际问题的综合素质。

二、教学内容1. C语言基础知识回顾:结构体、数组、字符串、指针等基本概念及其应用。

相关教材章节:第一章至第四章2. 算法介绍:二分查找算法原理及其在电子词典查询中的应用。

相关教材章节:第七章3. 文件读写操作:C语言文件操作函数,实现对电子词典数据的存储和读取。

相关教材章节:第九章4. 电子词典功能实现:- 单词录入:设计录入界面,实现单词信息的输入和保存;- 单词查询:实现按单词查找,展示单词释义;- 单词修改:实现对已录入单词的修改功能;- 单词删除:实现对已录入单词的删除功能。

相关教材章节:第五章、第六章、第七章5. 项目实践:分组进行电子词典项目实践,完成一个具有基本功能的电子词典程序。

教学内容安排和进度:第一周:C语言基础知识回顾,学习结构体、数组、字符串等;第二周:学习文件读写操作,理解二分查找算法;第三周:电子词典功能实现(单词录入、查询、修改、删除);第四周:项目实践,分组完成电子词典项目,并进行演示和评价。

基于快速单词查询模型的嵌入式电子词典的设计与实现的开题报告

基于快速单词查询模型的嵌入式电子词典的设计与实现的开题报告一、选题背景和研究意义随着科技的不断发展,人们越来越依赖移动设备进行阅读和学习。

然而,现有的移动设备上的电子词典并不能完全满足人们的需求。

一方面,现有的电子词典在查询速度上存在一定的问题,无法快速地进行单词查询。

另一方面,现有的电子词典在界面设计上也有不足之处,用户体验较为一般。

因此,本文将研究基于快速单词查询模型的嵌入式电子词典的设计与实现。

该嵌入式电子词典将利用现代化的技术和算法设计出查询速度快、界面友好的电子词典,以更好地满足用户的需求。

二、研究内容和研究计划本文将主要研究以下两个方面:1.基于快速单词查询模型的嵌入式电子词典的设计与实现该研究方向将涉及到电子词典的核心算法、查询速度优化等方面。

在算法方面,我们将探究jieba分词、TF-IDF等算法,并将其应用于电子词典的核心算法中,以实现更快的单词查询速度。

在查询速度优化方面,我们将挑选与硬件平台相适配的算法,并设计出相应的查询优化策略。

2.电子词典的界面设计与用户体验优化该研究方向将涉及到电子词典的界面设计、用户体验和用户反馈的收集等方面。

在界面设计方面,我们将探寻界面设计的最佳实践,并据此设计出更为美观、易用的电子词典。

在用户体验优化方面,我们将对用户行为数据进行收集和分析,并据此优化电子词典的体验,提高用户的使用满意度。

研究计划如下:1.前期文献调研和技术研究(1-2周)2.电子词典的核心算法研究和设计(2-3周)3.优化算法实现和查询速度优化设计(2-3周)4.界面设计和用户体验优化设计(2-3周)5.电子词典的整合和测试(2周)6.论文撰写和准备答辩 (2周)三、研究预期结果本文主要研究基于快速单词查询模型的嵌入式电子词典的设计与实现,预期结果如下:1.设计出支持快速单词查询的嵌入式电子词典2.优化单词查询速度,加快电子词典的查询响应时间3.设计出更为美观、易用的电子词典界面,提升用户的使用体验4.提高电子词典的稳定性和可靠性,提高用户的信任度四、研究的创新点1.在算法方面,本文将探寻jieba分词、TF-IDF等算法,并将其应用到电子词典的核心算法中,以实现更快的单词查询速度。

基于S3C44BOX的电子词典软件设计与实现DOC

基于S3C44BOX的电子词典软件设计与实现(DOC)基于S3C44BOX的电子词典软件设计与实现1 概述此次基于ARM7的电子词典系统开发作业,由我们小组4人合作完成,其中我主要负责软件方面的开发,所做的方面有英译汉软件功能的实现,输入值软件识别功能的实现以及看门狗定时器的实现。

由于不怎么熟悉arm的开发,基本是看着书做,设计思路和方法、功能实现也都是书上怎么来,自己就怎么实现,希望傅老师谅解,这块的基础确实薄弱。

2 S3C44BOX处理器介绍2.1 S3C44BOX简介S3C44BOX微处理器片类集成ARM7TDMI核,采用0.25μm CMOS工艺制造,并在ARM7TDMI核的基础上集成了丰富的外围功能模块,便于低成本设计嵌入式系统应用系统。

片上集成的主要功能如下:➢在ARM7TDMI基础上增加至8KB的Cache。

➢外部扩充存储器控制器(FP/EDO/SDRAM控制,片选逻辑)。

➢LCD控制器(最大支持256色的DSTN),并带有一个LCD专用DMA通道。

➢2个通用DMA通道2个带外部请求引脚的DMA通道。

➢2个带有握手协议的UART,1个SIO。

➢1个多主的I2C总线控制器。

➢1个I2S总线控制器。

➢5个PWM定时器及1个内部定时器。

➢看门狗定时器。

➢71个通用可编程I/O口,8个外部中断源。

➢功耗控制模式:正常,低速,休眠和停止。

➢8路10位ADC。

➢具有日历功能的RTC(实时时钟)。

➢PLL时钟发生器。

2.2 S3C44BOX特点2.2.1 S3C44BOX体系结构➢S3C44BOX是基ARM7TDMI体系结构的SOC。

➢集成了手持设备和通用嵌入式系统应用的解决方案;➢16/32位RISC体系结构和ARM7TDMI处理器内核强大的指令体系;➢Thumb代码压缩机,最大化代码密度同时保持了32位指令的性能;➢基于JTAG的片上集成ICE调试支持解决方案;➢32×8位硬件乘法器;➢实现低功耗SAMBA II(三星ARM处理器嵌入式微控制器总线体系结构)的新型总线结构。

电子词典系统设计实验报告

电子词典系统设计实验报告12121583 曹连强周四6-8一、项目要求:1、在实验板上设计实现一个无操作系统的简易电子词典2、设计友好的人机交互界面3、:字符输入、功能选择、英汉翻译。

二、电子词典系统实现具体功能:1.能够通过键盘输入英文。

键盘作为本系统中最主要的输入设备,需要完成26个英文字母的输入,并且需要上翻页,下翻页,上一行,下一行,翻译,退格等功能。

要求键盘至少要有16个按键,每个按键都可以被处理器及时,准确地读入。

2.提供友好的人机界面,将输入的内容和翻译的结果显示在LCD的相应区域内。

3. 对输入的单词即时翻译。

4.可以记忆3个已经查询过的的单词。

在无操作系统的电子词典系统中,由于是单任务环境,因此此时系统的各个功能模块均按照顺序执行。

初始化后,即进入翻译待机状态,等待用户的输入操作。

当用户输入操作发生后,系统调用键盘或触摸屏中断进行键值读取,将键值传给主函数中的系统功能实现模块,该模块按不同的输入键值进行相应的功能选择,最后将此次操作的结果输出到LCD上。

三、程序设计可将电子词典的软件设计分为如下几个主要模块:键值处理、翻译、词库设计和LCD 显示。

1、键值处理电子词典的输入设备为键盘和触摸屏,要完成的功能为:(1)键盘:10个英文字母和6个功能键输入(2)触摸屏:6各功能键的输入2、翻译:3、词库设计翻译功能中通过将输入单词和词库中相应的单词进行比较得到要显示的翻译结果,因此,词库可采用结构体实现,此结构中包括4项:英文单词、词性、汉语释意、英文例句。

4、LCD显示功能翻页、选行及翻页结果的输出都可以归到LCD显示功能中,这些功能都可以通过调用LCD 实验中的相关函数完成。

四.设计程序////////////////////////////////////////////////////////////#include "Ts_sep.h"#include <string.h>///////////////////////////////////////////////////////////#include "def.h"#include "2410lib.h"#include "option.h"#include "2410addr.h"#include "interrupt.h"#include "lcdlib.h"//#define STN_LCD#define TFT_8_0/////////////////8888888////////////////////////////#define LOOP 1#define ADCPRS 39#define TS_JUSTIFY_LEFTTOP 1#define TS_JUSTIFY_RIGHTBOT 2#define TS_START 3///////////////////8888888888888888//////////////////////void Lcd_Disp_Char(void);void Lcd_Disp_Grap(void);void Frame(void);//设置背景框架void Clearscreen(void);//清屏//void Key_init(void);//初始化键盘void Cursor(int flag);void CursorCl(int flag);void delay( int count );void disp();void translate(int num);static int x=0,y=0,letter=0,flag=0,wei=0,prev[5],i,j;//函数里有调用我换成全局变量int which[20];//此时满足罗列单词int word,w;int m,n;////////////////////////////////////////////////int ts_status = TS_JUSTIFY_LEFTTOP;int ts_lefttop_x, ts_lefttop_y, ts_rightbot_x, ts_rightbot_y;int ts_lcd_x, ts_lcd_y;///////////////////////////////////////////////typedef struct{int w; //单词对应的值int o;int r;int d;int s;char c[20]; //英文单词char e[20]; //翻译}str_word;str_word dictionary[20]={{1,3,5,0,0,"ACE","王牌"},{2,5,5,0,0,"BEE","蜜蜂"},{1,4,4,0,0,"ADD","增加,计算"},{2,1,4,0,0,"BAD","坏的"},{4,5,3,1,4,"DECAD","十;十数"}};////////////////////////////////////////////////////////void Adc_or_TsSep() __attribute__ ((interrupt("IRQ")));void Adc_or_TsSep(void){int i;U32 Ptx[6], Pty[6];rINTSUBMSK |= (BIT_SUB_ADC|BIT_SUB_TC); // Mask sub interrupt (ADC and TC)// TC(Touch screen Control) Interruptif(rADCTSC & 0x100){PRINTF("\nStylus Up!!\n");rADCTSC &= 0xff; // Set stylus down interrupt}else{PRINTF("\nStylus Down!!\n");// <X-Position Read>rADCTSC=(0<<8)|(0<<7)|(1<<6)|(1<<5)|(0<<4)|(1<<3)|(0<<2)|(1);// Down,Hi-Z,AIN5,GND,Ext vlt,Pullup Dis,Normal,X-positionfor(i=0;i<LOOP;i++); //delay to set up the next channelfor(i=0;i<5;i++){rADCCON|=0x1; // Start X-position conversionwhile(rADCCON & 0x1); // Check if Enable_start is lowwhile(!(0x8000&rADCCON)); // Check ECFLGPtx[i]=(0x3ff&rADCDAT0);}Ptx[5]=(Ptx[0]+Ptx[1]+Ptx[2]+Ptx[3]+Ptx[4])/5;// <Y-Position Read>rADCTSC=(0<<8)|(0<<7)|(1<<6)|(1<<5)|(0<<4)|(1<<3)|(0<<2)|(2);// Down,GND,Ext vlt,Hi-Z,AIN7,Pullup Dis,Normal,Y-positionfor(i=0;i<LOOP;i++); //delay to set up the next channelfor(i=0;i<5;i++){rADCCON|=0x1; // Start X-position conversionwhile(rADCCON & 0x1); // Check if Enable_start is lowwhile(!(0x8000&rADCCON)); // Check ECFLGPty[i]=(0x3ff&rADCDAT1);}Pty[5]=(Pty[0]+Pty[1]+Pty[2]+Pty[3]+Pty[4])/5;rADCTSC=(1<<8)|(1<<7)|(1<<6)|(0<<5)|(1<<4)|(0<<3)|(0<<2)|(3);// Up,GND,AIN,Hi-z,AIN,Pullup En,Normal,Waiting modePRINTF("TOUCH Position = (%04d, %04d) ", Ptx[5], Pty[5]);m=Ptx[5];n=Pty[5];if(ts_status == TS_JUSTIFY_LEFTTOP){ts_lefttop_x = Ptx[5];ts_lefttop_y = Pty[5];ts_status = TS_JUSTIFY_RIGHTBOT;PRINTF("\nLeft top (0, 0) -> (%04d, %04d)\n", ts_lefttop_x, ts_lefttop_y);PRINTF(" 请触摸屏幕右下角位置\n");}else if(ts_status == TS_JUSTIFY_RIGHTBOT){ts_rightbot_x = Ptx[5];ts_rightbot_y = Pty[5];ts_status = TS_START;PRINTF("\nRight bottom (319, 239) -> (%04d, %04d)\n", ts_rightbot_x, ts_rightbot_y);PRINTF("[2] 请点击触摸屏\n");}else{/* ts_lcd_x = 320 - (Ptx[5] - ts_rightbot_x) * 1.0 / (ts_lefttop_x - ts_rightbot_x) * 320.0 ;ts_lcd_y = (Pty[5] - ts_lefttop_y) * 1.0 / (ts_rightbot_y - ts_lefttop_y) * 240.0 ;if(ts_lcd_x > 319) ts_lcd_x = 319;if(ts_lcd_x < 0) ts_lcd_x = 0;if(ts_lcd_y > 239) ts_lcd_x = 239;if(ts_lcd_y < 0) ts_lcd_x = 0;PRINTF("LCD Position = (%04d, %04d)\n", ts_lcd_x, ts_lcd_y);*/}}rSUBSRCPND |= BIT_SUB_TC;rINTSUBMSK =~ (BIT_SUB_TC); // Unmask sub interrupt (TC)ClearPending(BIT_ADC);}void Ts_Sep(void){PRINTF("------触摸屏测试------\n");PRINTF("[1] 触摸屏校准\n 请触摸屏幕左上角位置\n");ts_status = TS_JUSTIFY_LEFTTOP;rADCDLY = (50000); // ADC Start or Interval DelayrADCCON = (1<<14)|(ADCPRS<<6)|(0<<3)|(0<<2)|(0<<1)|(0);// Enable Prescaler,Prescaler,AIN7/5 fix,Normal,Disable read start,No operationrADCTSC = (0<<8)|(1<<7)|(1<<6)|(0<<5)|(1<<4)|(0<<3)|(0<<2)|(3);// Down,YM:GND,YP:AIN5,XM:Hi-z,XP:AIN7,XP pullup En,Normal,Waiting for interrupt modepISR_ADC = (unsigned)Adc_or_TsSep;rINTMSK &=~(BIT_ADC);rINTSUBMSK =~(BIT_SUB_TC);// while(1);delay(200);// rINTSUBMSK |= BIT_SUB_TC;//rINTMSK |= BIT_ADC;// PRINTF("----触摸屏测试结束----\n");}//////////////////////////////////////////////////////void Main(void){unsigned char ch='1';/* 配置系统时钟 */ChangeClockDivider(1,1); // 1:2:4ChangeMPllValue(0xa1,0x3,0x1); // FCLK=202.8MHz/* 初始化端口 */Port_Init();/* 初始化串口 */Uart_Init(0,115200);Uart_Select(0);/* 打印提示信息 */PRINTF("\n---LCD测试程序---\n");PRINTF("\n请将UART0与PC串口进行连接,然后启动超级终端程序(115200, 8, N, 1)\n");/* LCD初始化 */Lcd_Port_Init();#ifdef STN_LCDLcd_Init(MODE_CSTN_8BIT);Glib_Init(MODE_CSTN_8BIT);Lcd_CstnOnOff(1);Glib_ClearScr(0xff, MODE_CSTN_8BIT);#else#ifdef TFT_8_0rGPCCON &= ~(3<<8);rGPCCON |= (2<<8);Lcd_Init(MODE_TFT_16BIT_640480);Glib_Init(MODE_TFT_16BIT_640480);Glib_ClearScr(0xffff, MODE_TFT_16BIT_640480);Lcd_PowerEnable(0, 1);Lcd_EnvidOnOff(1);#elseLcd_Init(MODE_TFT_16BIT_240320);Glib_Init(MODE_TFT_16BIT_240320);Glib_ClearScr(0xffff, MODE_TFT_16BIT_240320);Lcd_PowerEnable(0, 1);Lcd_EnvidOnOff(1);#endif#endif#define LCD_DISP_CHAR#ifdef LCD_DISP_CHARLcd_Disp_Grap();#endif//布局Glib_FilledRectangle(0,0,640,240,0xffff); //白底// Glib_Rectangle(60,80,620,110,0x0000);//首字母框Glib_Rectangle(60,80,620,440,0x0000);//主框Glib_Line(290,110,290,410,0x0000);//分割线1Glib_Line(60,110,620,110,0x0000);//分割线2Glib_Line(60,410,620,410,0x0000);//分割线3Glib_Line(172,410,172,440,0x0000);//分割线4Glib_Line(284,410,284,440,0x0000);//分割线5Glib_Line(396,410,396,440,0x0000);//分割线6Glib_Line(508,410,508,440,0x0000);//分割线7// Glib_Rectangle(520,80,620,120,0x0000);//upGlib_disp_hzk16(110,420,"上", 0x0000);// Glib_Rectangle(520,140,620,180,0x0000);//downGlib_disp_hzk16(222,420,"下", 0x0000);// Glib_Rectangle(520,200,620,240,0x0000);//DelGlib_disp_hzk16(334,420,"清屏", 0x0000);// Glib_Rectangle(520,260,620,300,0x0000);//EnterGlib_disp_hzk16(446,420,"查询", 0x0000);// Glib_Rectangle(520,320,620,360,0x0000);//CancelGlib_disp_hzk16(558,420,"返回", 0x0000);Ts_Sep();while(1)//大循环等键按下{Cursor(flag);ch = Key_GetKeyPoll();/////////////////////////////////////////////////////////////////////////////// /////////////////////////////////////if((m>=145&&m<237)&&(n>395&&n<540))ch='E';//qingpinif((m>=145&&m<237)&&(n>678&&n<830))ch='C';//Shangif((m>=145&&m<237)&&(n>540&&n<678))ch='D';//Xiaif((m>=145&&m<237)&&(n>57&&n<219))ch='B';///shanchuif((m>=145&&m<237)&&(n>219&&n<395))ch='F';//quedingm=n=0;/////////////////////////////////////////////////////////////////////////////// /////////////////////////////switch(ch){case '1'://aGlib_FilledRectangle(65,120,280,400,0xffff);//先清罗列单词区letter=1;//1表示输入字母为1Glib_disp_hzk16(90+wei*20,90,"A", 0x0000);//显示界面显示aprev[wei]=1;//存放disp();//显示单词区的单词wei++;//下一个放字母位置if(wei>=5){Glib_disp_hzk16(340,90,"已满", 0x0000);//单词字母小于等于四个delay(1000);Glib_disp_hzk16(340,90,"已满", 0xffff);//清掉"已经满了"};//超出错误,只能查四位break;case '2'://bGlib_FilledRectangle(65,120,280,400,0xffff);//先清罗列单词区letter=2;//1表示输入字母为1Glib_disp_hzk16(90+wei*20,90,"B", 0x0000);//显示界面显示aprev[wei]=2;//存放disp();//显示单词区的单词wei++;//下一个放字母位置if(wei>=5){Glib_disp_hzk16(340,90,"已满", 0x0000);//单词字母小于等于四个delay(1000);Glib_disp_hzk16(340,90,"已满", 0xffff);//清掉"已经满了"};//超出错误,只能查四位break;case '3'://cGlib_FilledRectangle(65,120,280,400,0xffff);//先清罗列单词区letter=3;//1表示输入字母为1Glib_disp_hzk16(90+wei*20,90,"B", 0x0000);//显示界面显示aprev[wei]=3;//存放disp();//显示单词区的单词wei++;//下一个放字母位置if(wei>=5){Glib_disp_hzk16(340,90,"已满", 0x0000);//单词字母小于等于四个delay(1000);Glib_disp_hzk16(340,90,"已满", 0xffff);//清掉"已经满了"};//超出错误,只能查四位break;case '4'://dGlib_FilledRectangle(65,120,280,400,0xffff);//先清罗列单词区letter=4;//1表示输入字母为1Glib_disp_hzk16(90+wei*20,90,"D", 0x0000);//显示界面显示aprev[wei]=4;//存放disp();//显示单词区的单词wei++;//下一个放字母位置if(wei>=5){Glib_disp_hzk16(340,90,"已满", 0x0000);//单词字母小于等于四个delay(1000);Glib_disp_hzk16(340,90,"已满", 0xffff);//清掉"已经满了"};//超出错误,只能查四位break;case '5'://eGlib_FilledRectangle(65,120,280,400,0xffff);//先清罗列单词区letter=5;//1表示输入字母为1Glib_disp_hzk16(80+wei*20,90,"E", 0x0000);//显示界面显示aprev[wei]=5;//存放disp();//显示单词区的单词wei++;//下一个放字母位置if(wei>=5){Glib_disp_hzk16(340,90,"已满", 0x0000);//单词字母小于等于四个delay(1000);Glib_disp_hzk16(340,90,"已满", 0xffff);//清掉"已经满了"};//超出错误,只能查四位break;case '6'://fbreak;case '7'://gbreak;case '8'://hbreak;case '9'://ibreak;case '0'://jbreak;case 'A'://kletter=11;break;case 'C'://上flag--;if(flag>=0&&flag<=3){Cursor(flag);//单词列表选中变色CursorCl(flag+1);}//再上恢复刚才那条的背景色else flag=0;break;case 'D'://下flag++;if(flag>=0&&flag<=3){Cursor(flag);CursorCl(flag-1);}else flag=3;break;case 'E'://cancel清屏Glib_FilledRectangle(70,90,339,109,0xffff);//先清单词区Glib_FilledRectangle(65,120,280,400,0xffff);//先清罗列单词区Glib_FilledRectangle(300,120,610,400,0xffff);//清翻译区for(j=0;j<=10;j++){which[j]=0;};letter=0;wei=0;for(j=0;j<=5;j++){prev[j]=0;};break;case 'F'://enter确定Glib_FilledRectangle(300,120,610,400,0xffff);//主翻译区if(flag>=0&&flag<=3)translate(which[flag]);//显示结果break;case 'B'://del删除Glib_FilledRectangle(70,120,280,400,0xffff);//先清罗列单词区letter=0;wei--;prev[wei]=0;//上一位变0Glib_FilledRectangle(70+wei*30,90,70+wei*30+20,109,0xffff);//消掉一个字母wei--;disp();wei++;break;default:Glib_disp_hzk16(500,90,"←请输入单词", 0x0000);break;}}}void disp(){y=0;//初始单词显示位置for(i=0;i<=20;i++){if((dictionary[i].w==prev[0])&&(wei==0)){//第一个字母正which[y]=i;//存放哪几个单词显示了Glib_disp_hzk16(80,120+32*y,dictionary[i].c, 0x0000);//显示单词y++;//位置改变}if((dictionary[i].w==prev[0])&&(dictionary[i].o==prev[1])&&(wei==1)){//前两个字母正确which[y]=i;//存放哪几个单词显示了Glib_disp_hzk16(80,120+32*y,dictionary[i].c, 0x0000);//显示单词y++;//位置改变}if((dictionary[i].w==prev[0])&&(dictionary[i].o==prev[1])&&(dictionary[i].r==pr ev[2])&&(wei==2)){//前3个字母正确which[y]=i;//存放哪几个单词显示了Glib_disp_hzk16(80,120+32*y,dictionary[i].c, 0x0000);//显示单词y++;//位置改变}if((dictionary[i].w==prev[0])&&(dictionary[i].o==prev[1])&&(dictionary[i].r ==prev[2])&&(dictionary[i].d==prev[3])&&(wei==3)){//前4个字母正确which[y]=i;//存放哪几个单词显示了Glib_disp_hzk16(80,120+32*y,dictionary[i].c, 0x0000);//显示单词y++;//位置改变}}}void translate(int num){//显示单词选项3个Glib_disp_hzk16(300,120,dictionary[num].e, 0x0000);}//void Clearscreen(void) //清屏//{// Glib_FilledRectangle(65,81,499,99,0xffff);// Glib_FilledRectangle(65,121,499,439,0xffff);// Glib_Line(240,120,240,440,0x0000);//}void Cursor(int flag){Glib_FilledRectangle(65,121+flag*32,75,153+flag*32,0x55);}void CursorCl(int flag){Glib_FilledRectangle(65,121+flag*32,75,153+flag*32,0xffff);}void Lcd_Disp_Grap(void){int i,j;for(j=0;j<240;j++)for(i=0;i<320;i++) //RRRGGGBBPutPixel(i,j,((i/40)<<5)+((j/30)<<2)+(((j/15)%2)<<1)+((i/20)%2)); }void delay( int count ){int cnt;for( count = count; count>0; count--)for( cnt = 0; cnt < 100; cnt++);}。

c语言课程设计电子词典

c语言课程设计电子词典随着科技的不断进步和发展,计算机技术也在不断的发展和完善。

计算机编程语言也应运而生,其中c语言成为了最为流行和广泛应用的一种编程语言。

为了更好地学习和掌握c语言,我们需要不断地进行练习和实践。

而课程设计电子词典就是一个非常好的实践项目。

本文将对c语言课程设计电子词典进行详细的介绍和分析。

一、电子词典简介电子词典是一种类似于纸质词典的电子设备。

电子词典将词典内容数字化存储在内部芯片中,通过一个屏幕显示出来。

电子词典拥有很多优点,比如存储空间更大、功能更强大、可搜索性更高等等。

今天,电子词典是很多人学习和工作必不可少的工具之一。

二、c语言课程设计电子词典的设计思路c语言课程设计电子词典是一种将词典内容和c程序功能相结合的设计项目。

他的设计思路如下:1.定义词典内容结构体在程序中需要定义一个结构体,用来存储词典内容。

结构体的成员包括单词、单词的释义、音标等。

typedef struct word{ char name[30]; // 单词名称char symbol[30]; // 单词音标charmean[400]; // 单词含义}word;2.构建词典数据将词典中的单词、释义、音标等内容保存到结构体中。

并将多个结构体数据包含在一个数组中。

word dictionary[] = { { "apple", "[ˈæpl]", "a round fruit with smooth red or yellow skin and firm white flesh" }, { "banana", "[bəˈnɑː.nə]", "a long curved fruit with a yellow skin" }, { "cat", "[kæt]", "a small animal with fur, four legs, a tail, and claws" }, { "dog", "[dɒɡ]", "a common animal with four legs, fur, and a tail" }, { "elephant", "[ˈel.ɪ.fənt]", "a very large grey animal with a long nose called a trunk" }};3.实现单词查询功能在程序中,我们需要实现一个单词查询的功能。

电子词典设计与开发毕业设计

电子词典设计与开发毕业设计随着科技的快速发展,电子词典已成为学生们学习语言的重要工具。

它不仅方便携带,而且可以随时随地帮助解决词汇问题。

然而,随着用户需求的不断增长和技术的发展,电子词典的设计与开发也需要不断地创新和改进。

本文旨在探讨电子词典设计与开发毕业设计的意义、背景、目的、相关文献综述与领域现状、问题以及方法。

电子词典的设计与开发具有重要的现实意义。

随着全球化的进程,语言学习变得越来越重要。

电子词典作为语言学习的辅助工具,可以为学习者提供方便快捷的词汇查询服务。

电子词典具有体积小、存储量大、功能丰富等优点,相较于传统纸质词典更具优势。

随着人工智能技术的发展,电子词典的设计与开发也在不断进步,为学习者提供了更好的学习体验。

本次毕业设计的目的是设计并开发一款功能完善、操作简便、符合用户需求的电子词典。

具体目标包括:实现词汇查询功能,支持多种语言之间的互查及在线翻译;提供例句、解释、词性分类等信息,帮助学习者更好地理解词汇;增加词汇记忆功能,通过艾宾浩斯遗忘曲线等方法辅助用户记忆词汇;优化用户界面,提高操作体验,使得用户能够便捷地使用电子词典;实现词汇量的评估功能,为用户提供学习进度的参考。

在文献综述方面,我们调查了近年来国内外关于电子词典设计与开发的研究成果。

目前,市面上的电子词典种类繁多,但大多数产品仍存在一些问题,如查询速度慢、操作繁琐、词汇量有限等。

现有的电子词典大多只查询功能,而忽略了用户的学习需求和用户体验。

在领域现状方面,人工智能技术的发展为电子词典的设计与开发带来了新的机遇。

机器翻译、自然语言处理等技术使得电子词典可以实现多种语言之间的互查及在线翻译功能。

随着移动互联网的普及,移动端电子词典的市场份额也在逐渐增大。

然而,目前市场上的移动端电子词典大多仍存在操作繁琐、功能单一等问题。

本次毕业设计将采用以下研究方法和技术路线:文献调研:通过查阅相关文献和资料,了解电子词典的设计与开发技术及现有产品的优缺点;用户调研:通过问卷调查、访谈等方式了解用户对电子词典的需求和期望;系统分析:对现有电子词典的功能、性能等方面进行分析和评估;系统设计:根据用户需求和系统分析结果,进行电子词典的系统设计;系统实现:采用Java、Android等技术实现电子词典的功能;系统测试:对电子词典进行测试和优化,确保系统的稳定性和性能;用户反馈:邀请部分用户对电子词典进行试用并收集反馈意见,以便进一步优化产品。

嵌入式课程设计--基于S3C44BOX电子词典软件开发

《嵌入式系统》课程设计说明书基于S3C44BOX电子词典软件开发系、部:计算机与信息科学系组成员:指导教师:职称专业:计算机科学与技术班级:计本0801班完成时间:2011年12月12日摘要随着电子系技术的发展,以ARM微处理器为核心的电子应用系统已经进入人们日常生产生活的各个方面,ARM以其出色的性能优势赢得了广大电子产品开发者的认可。

本文作者根据自己的课程学习,掌握了 ARM系统微处理器相关的基础知识和基本技术,而这些技术需要实地的实验设计来帮助巩固和深入。

本案例属于日常生活当中和学习研究中比较常见和熟悉的应用,不但有比较强的综合性,而且有很高的趣味性。

在我们系统学习了嵌入式系统开发与应用实践课程之后,结合对ARM微处理器的基础知识和基本技术的掌握,实现了简单电子词典设计。

本设计主要解决了基于S3C44B0X 通过I/O控制发光二极管的电子词典。

关键词:ARM微处理器;词典设计;S3C44B0XABSTRACTAlong with the electronic technology development, with ARM microprocessor as the core of the electronic application system has entered people's daily production in all aspects of life, ARM with its excellent performance advantages to win the majority of electronic product developers recognized. In this paper the authors according to their course of study, master of the ARM system related to the basic knowledge and technology, and these technologies require field experiments designed to help consolidate and development. This case belongs to the daily life and study in the more common and familiar with the application, not only have strong comprehensive, but also have high interest.In our system, learning embedded system development and application practice of course, according to the ARM microprocessor basic knowledge and basic technical mastery, the realization of a simple directory design. The design of the main solution based on S3C44B0X through I / O control led flashing.Key words: ARM microprocessor; directory; S3C44B0X目录1 前言 (1)1.1课题研究背景 (1)1.2课程研究目的和意义 (2)1.3 S3C44BOX处理器介绍 (3)2 基于S3C44BOX电子词典开发概述 (4)2.1电子词典系统定义与需求分析 (4)2.2电子词典方案设计 (7)2.2.1硬件设计方案 (7)2.2.2软件设计方案 (7)3 基于S3C4BOX电子词典的硬件开发 (8)3.1基于S3C4BOX的最小系统软件 (8)3.2显示模块 (9)3.3触摸屏及键盘模块 (10)4 基于S3C44BOX电子词典软件开发环境的建立 (10)4.1开发环境 (10)5 基于S3C44BOX电子词典的软件开发 (11)5.1电子词典各模块测试软件设计 (11)5.2电子词典应用软件开发 (13)5.3无操作系统电子词典硬件驱动程序设计 (15)5.3.1Uart驱动程序 (16)5.3.2LCD驱动程序 (16)5.3.3键盘驱动程序 (17)5.3.4触摸屏驱动程序 (17)5.4电子词典系统应用软件个功能模块设计实现 (18)5.4.1键盘接口功能软件 (18)5.4.2触摸屏接口功能软件 (18)5.4.3LCD显示接口功能软件 (18)5.4.4输入键值识别功能软件 (18)5.4.5英译汉功能软件 (21)5.4.6已查单词记忆功能软件 (23)5.4.7汉语词库编写和英语词库编写 (23)6 总结 (26)7 参考文献 (27)1 前言1.1课题研究背景随着3C融合进程和我国传统产业结构升级的加速,人们对设备越来越高的应用需要已经无法满足当前和未来高性能的应用与发展需求。

嵌入式课程设计 - 电子词典硬件设计.

上海电力学院嵌入式系统课程设计报告题目:电子词典的设计姓名:学号:院系:专业年级:同组成员:年月日一、实验内容及要求在LCD屏幕左侧绘制出单词输入框和释义显示框以及一个搜索键,右侧绘制4*4键盘按钮,模拟出简易电子词典的功能,按钮操作用触摸屏或键盘实现均可。

实现功能:(1)LCD屏幕上显示4*4键盘,显示单词及其翻译、例句。

(2)一个键可完成2个英文字母的输入,如左上角第一个键可实现输入a,b两个字母,第一次按下时为输入a,如果需输入b,只需连续快速按键两次即可。

(3)在输入完单词后,点击搜索键,即可在释义显示框中显示该单词的词性、中文解释、示例词组和句子等。

(4)当发现输入的单词在库中不存在时,可实现将该单词添加入库的操作。

二、设计思路(1)通过LCD显示模块画出电子词典操作界面。

(2)对应界面中各键的位置设置键盘对应键值。

(3)设定功能键,实现以下3个功能:①退格键:删除最后一位字母;②搜索∕保存键:对输入框的单词进行判断,若单词存在于词库中,则显示单词词性、词义、例句;若单词不存在则自动进行保存;③转换键:按下后,字母键输出对应的第二个字母。

(4)按键后赋值并显示。

三、软件构架开始LCD模块键盘模块结束四、模块分析(1)键盘模块流程图:源代码:/********************************************************************************************** File : keyboard.c* Author: embest* Desc : keyboard source code* History:*********************************************************************************************//*--- include files ---*/ 开始 键盘初始化 键盘是否按下 Y 读取键值 是否是功能键 Y N 执行功能赋值 显示 结束 N#include "44b.h"#include "44blib.h"#include "def.h"#include "keyboard.h"#include "lcd.h"#include "dict.h"#ifndef KEY_INT#define KEY_INT#endif#ifndef BUT_INT#define BUT_INT#endif/*--- global variables ---*/int input_char,n=0;char word[20];int wordIndex=0;int x = 15;int num=0;int counter=0;/* keyboard control address */volatile UCHAR *keyboard_base = (UCHAR *)0x06000000;/*--- function declare ---*/void init_keyboard();void close_keyboard();void KeyboardInt(void);// __attribute__ ((interrupt ("IRQ")));void Eint4567Isr(void);// __attribute__ ((interrupt ("IRQ")));/*--- function code ---*//****************************************************************************** **************** name: Test_Keyboard* func: test keyboard* para: none* ret: none* modify:* comment:******************************************************************************* *************/void Test_Keyboard(){Uart_Printf("\n Keyboard Test Example\n");Uart_Printf("\n Please press one key on keyboard and look at LED ...\n");// init keyboardinit_keyboard();while(1);// close keyboard// close_keyboard();}/****************************************************************************** **************** name: init_keyboard* func: init keyboard interrupt* para: none* ret: none* modify:* comment:******************************************************************************* *************/extern void isrEINT1(void);extern void isrEint4567(void);void init_keyboard(){/* enable interrupt */rINTMOD = 0x0;rINTCON = 0x1;/* set EINT1 interrupt handler */rINTMSK =~(BIT_GLOBAL|BIT_EINT1|BIT_EINT4567);pISR_EINT1 = (int)isrEINT1;pISR_EINT4567 = (int)isrEint4567;/* PORT G */rPCONG = 0xffff; // EINT7~0rPUPG = 0x0; // pull up enablerEXTINT = rEXTINT|0x20; // EINT1 falling edge moderI_ISPC = BIT_EINT1|BIT_EINT4567; // clear pending bitrEXTINTPND = 0xf; // clear EXTINTPND reg}/****************************************************************************** **************** name: close_keyboard* func: close keyboard interrupt* para: none* ret: none* modify:* comment:******************************************************************************* *************/void close_keyboard(){pISR_EINT1 = NULL;pISR_EINT4567 = NULL;/* Mask interrupt */rINTMSK = rINTMSK | BIT_EINT1 | BIT_EINT4567;}/****************************************************************************** **************** name: KeyboardInt* func: keyboard interrupt handler function* para: none* ret: none* modify:* comment:******************************************************************************* *************/void KeyboardInt(void){int nTemp,i,j,k,m=0;char bbyte;rI_ISPC = BIT_EINT1; // clear pending bitchar pbyte[10];nTemp = key_read();if(nTemp > -1){// Lcd_Draw_HLine(10, 310, 80, WHITE, 50);input_char = nTemp;Lcd_DspAscII8x16(15,45,WHITE,word);switch(input_char){case 0:num=1;break;case 1:num=2;break;case 2:num=3;break;case 3:num=4;break;case 4:num=5;break;case 5:num=6;break;case 6:num=7;break;case 7:num=8;break;case 8:num=9;break;case 9:counter=1;break;case 10:counter=2;break;case 11:counter=3;break;case 12:m=1;Lcd_Draw_HLine(15+n-10, 15+n, 45, WHITE, 16); n-=10;word[wordIndex]='\0';wordIndex--;break;/*if(n==0){word[20]=0;wordIndex=0;Lcd_Draw_HLine(10, 310,85, WHITE, 160);}break;*/case 13:word[wordIndex]='\0';wordIndex=0;for(i=0;i<20;i++){if(strcmp(word,vocab[i].c)==0){j=0;k=i;break;}elsej=1;}if(j==0){//#ifdef Eng_vLcd_DspAscII8x16(15,40,BLUE,vocab[k].c);Lcd_DspAscII8x16(15,60,BLUE,vocab[k].d);Lcd_DspAscII8x16(15,80,BLUE,vocab[k].f);//#elseLcd_DspHz16(15,100,BLUE,vocab[k].e);//#endif}else{Lcd_DspHz16(15,120,BLUE,"未找到相应的单词");DelayMs(600);Lcd_DspHz16(15,120,WHITE,"未找到相应的单词"); }break;case 14:word[wordIndex]='\0';wordIndex=0;for(i=0;i<20;i++){if(strcmp(word,vocab[i].c)==0){j=0;k=i;break;}elsej=1;}if(j==0){//#ifdef Eng_vLcd_DspAscII8x16(15,40,BLUE,vocab[k].c);Lcd_DspAscII8x16(15,60,BLUE,vocab[k].d);Lcd_DspAscII8x16(15,80,BLUE,vocab[k].f);//#elseLcd_DspHz16(15,100,BLUE,vocab[k].e);//#endif}else{if(20>x>0){for(i = 0; i < 20; i++)vocab[x].c[i]=word[i];word[i]='\0';Lcd_DspAscII8x16(15,40,BLUE,vocab[x].c);x++;}elsex=15;//Lcd_DspAscII8x16(15,45,BLUE,word);for(i = 0; i < 20; i++)word[i]='\0';}break;case 15://Lcd_Draw_Box(10,40,310,80,GREEN);break;}if(num!=0&&counter!=0){switch(3*(num-1)+counter-1){case 0:bbyte='a';break;case 1:bbyte='b';break;case 2:bbyte='c';break;case 3:bbyte='d';break;case 4:bbyte='e';break;case 5:bbyte='f';break;case 6:bbyte='g';break;case 7:bbyte='h';break;case 8:bbyte='i';break;case 9:bbyte='j';break;case 10:bbyte='k';break;case 11:bbyte='l';break;case 12:bbyte='m';break;case 13:bbyte='n';break;case 14:bbyte='o';break;case 15:bbyte='p';break;case 16:bbyte='q';break;case 17:bbyte='r';break;case 18:bbyte='s';break;case 19:bbyte='t';break;case 20:bbyte='u';break;case 21:bbyte='v';break;case 22:bbyte='w';break;case 23:bbyte='x';break;case 24:bbyte='y';break;case 25:bbyte='z';break;case 26:bbyte='y';break;}num=0;counter=0;if(m==0){word[wordIndex]=bbyte; wordIndex++;//n+=10;}Lcd_DspAscII8x16(15,210,BLUE,word);// Uart_Printf("Key is:%x \r",input_char);}}/****************************************************************************** **************** name: key_read* func: read key value* para: none* ret: key value, -1 -- error* modify:* comment:******************************************************************************* *************/inline int key_read(){int value;char temp;/* read line 1 */temp = *(keyboard_base+0xfd);/* not 0xF mean key down */if(( temp & KEY_V ALUE_MASK) != KEY_V ALUE_MASK){if( (temp&0x1) == 0 )value = 3;else if( (temp&0x2) == 0 )value = 2;else if( (temp&0x4) == 0 )value = 1;else if( (temp&0x8) == 0 )value = 0;while(( temp & KEY_V ALUE_MASK) != KEY_V ALUE_MASK) // releasetemp = *(keyboard_base+0xfd);return value;}/* read line 2 */temp = *(keyboard_base+0xfb);/* not 0xF mean key down */if(( temp & KEY_V ALUE_MASK) != KEY_V ALUE_MASK){if( (temp&0x1) == 0 )value = 7;else if( (temp&0x2) == 0 )value = 6;else if( (temp&0x4) == 0 )value = 5;else if( (temp&0x8) == 0 )value = 4;while(( temp & KEY_V ALUE_MASK) != KEY_V ALUE_MASK) // release temp = *(keyboard_base+0xfb);return value;}/* read line 3 */temp = *(keyboard_base+0xf7);/* not 0xF mean key down */if(( temp & KEY_V ALUE_MASK) != KEY_V ALUE_MASK){if( (temp&0x1) == 0 )value = 0xb;else if( (temp&0x2) == 0 )value = 0xa;else if( (temp&0x4) == 0 )value = 9;else if( (temp&0x8) == 0 )value = 8;while(( temp & KEY_V ALUE_MASK) != KEY_V ALUE_MASK) // release temp = *(keyboard_base+0xf7);return value;}/* read line 4 */temp = *(keyboard_base+0xef);/* not 0xF mean key down */if(( temp & KEY_V ALUE_MASK) != KEY_V ALUE_MASK){if( (temp&0x1) == 0 )value = 0xf;else if( (temp&0x2) == 0 )value = 0xe;else if( (temp&0x4) == 0 )value = 0xd;else if( (temp&0x8) == 0 )value = 0xc;while(( temp & KEY_V ALUE_MASK) != KEY_V ALUE_MASK) // releasetemp = *(keyboard_base+0xef);return value;}return -1;}/****************************************************************************** **************** name: Eint4567Isr* func:* para: none* ret: none* modify:* comment:******************************************************************************* **************/void Eint4567Isr(void){unsigned char which_int;Uart_Printf("\n SB2 or SB3 had pressed and light LED.");which_int=rEXTINTPND;rEXTINTPND=0xf; //clear EXTINTPND reg.rI_ISPC=BIT_EINT4567; //clear pending_bitif(which_int == 4) // SB2{Led_Display(0x0);Led_Display(0x1);}else if(which_int == 8) // SB3{Led_Display(0x0);Led_Display(0x2);}}(2)LCD模块流程图:开始LCD初始化显示开机画面显示操作界面结束源代码:/****************************************************************************** **************** File:lcd.c* Author: embest* Desc: LCD control and display functions* History:******************************************************************************* **************//*--- include files ---*/#include "lcd.h"//#include "bmp.h"#include "44b.h"/*--- global variables ---*/INT32U aLcdActiveBuffer[LCD_YSIZE][LCD_XSIZE/4];/*--- extern variables ---*/extern const INT8U aucTempBitmap[][76800];/*--- function code ---*//****************************************************************************** **************** name: Lcd_Init()* func: Initialize LCD Controller* para: none* ret: none* modify:* comment:******************************************************************************* **************/void Lcd_Init (void){rDITHMODE=0x12210;rDP1_2 =0xa5a5;rDP4_7 =0xba5da65;rDP3_5 =0xa5a5f;rDP2_3 =0xd6b;rDP5_7 =0xeb7b5ed;rDP3_4 =0x7dbe;rDP4_5 =0x7ebdf;rDP6_7 =0x7fdfbfe;// disable,8B_SNGL_SCAN,WDL Y=16clk,WLH=16clk,rLCDCON1=(0x0)|(2<<5)|(MV AL_USED<<7)|(0x3<<8)|(0x3<<10)|(CLKVAL_COLOR<< 12);// LINEBLANK=10 (without any calculation)rLCDCON2=(LINEV AL)|(HOZV AL_COLOR<<10)|(10<<21);rLCDCON3=0;// 256-color, LCDBANK, LCDBASEUrLCDSADDR1= (0x3<<27) | ( ((unsigned int)aLcdActiveBuffer>>22)<<21 ) | M5D((unsigned int)aLcdActiveBuffer>>1);rLCDSADDR2= M5D((((unsigned int)aLcdActiveBuffer+(SCR_XSIZE*LCD_YSIZE))>>1)) | (MV AL<<21);rLCDSADDR3= (LCD_XSIZE/2) | ( ((SCR_XSIZE-LCD_XSIZE)/2)<<9 );//The following value has to be changed for better display.rREDLUT =0xfdb96420; // 1111 1101 1011 1001 0110 0100 0010 0000rGREENLUT=0xfdb96420; // 1111 1101 1011 1001 0110 0100 0010 0000rBLUELUT =0xfb40; // 1111 1011 0100 0000rLCDCON1=(0x1)|(2<<5)|(MV AL_USED<<7)|(0x3<<8)|(0x3<<10)|(CLKVAL_COLOR<< 12);// rPDATE=rPDATE&0x0e;rPDATE=0xfe;Lcd_Clr();}/****************************************************************************** **************** name: Lcd_Clr()* func: clear LCD screen* para: none* ret: none* modify:* comment:******************************************************************************* **************/void Lcd_Clr(void){INT32U i;INT32U *pDisp = (INT32U*)aLcdActiveBuffer;for (i = 0; i < (SCR_XSIZE * SCR_YSIZE / 4); i++){*pDisp++ = ALLWHITE;}}/****************************************************************************** **************** name: LcdClrRect()* func: fill appointed area with appointed color* para: usLeft,usTop,usRight,usBottom -- area's rectangle acme coordinate* ucColor -- appointed color value* ret: none* modify:* comment: also as clear screen function******************************************************************************* **************/void LcdClrRect(INT16 usLeft, INT16 usTop, INT16 usRight, INT16 usBottom, INT8U ucColor) {INT32U i, j;INT8U *pDisp = (INT8U*)aLcdActiveBuffer;for(i=usTop;i<=usBottom;i++){for(j=usLeft;j<=usRight;j++){LCD_PutPixel(j, i, ucColor);}}}#ifdef MON_LCD/****************************************************************************** **************** name: LcdClrRect()* func: fill appointed area with appointed color* para: usLeft,usTop,usRight,usBottom -- area's rectangle acme coordinate* ucColor -- appointed color value* ret: none* modify:* comment: also as clear screen function******************************************************************************* **************/void LcdClrRect(INT16 usLeft, INT16 usTop, INT16 usRight, INT16 usBottom, INT8U ucColor) {INT16 i=0;INT16 k,l;INT16 m;INT32U ulColor = (ucColor << 28) | (ucColor << 24) | (ucColor << 20) | (ucColor << 16) |(ucColor << 12) | (ucColor << 8) | (ucColor << 4) | ucColor;if((usRight-usLeft)<=8){for(i=usTop;i<=usBottom;i++){for(m=usLeft;m<=usRight;m++){LCD_PutPixel(m, i, ucColor);}}return;}if((usLeft%8)==0)k=usLeft;else{k=(usLeft/8)*8+8;}if(( usRight%8)==0)l= usRight;else{l=( usRight/8)*8;}for(i=usTop;i<=usBottom;i++){for(m=usLeft;m<=(k-1);m++){LCD_PutPixel(m, i, ucColor);}for(m=k;m<l;m+=8){(*(INT32U*)(aLcdActiveBuffer + i * SCR_XSIZE / 2 + m / 2)) = ulColor;}for(m=l;m<=usRight;m++){LCD_PutPixel(m, i, ucColor);}}}#endif/****************************************************************************** **************** name: Lcd_Draw_Box()* func: Draw rectangle with appointed color* para: usLeft,usTop,usRight,usBottom -- rectangle's acme coordinate* ucColor -- appointed color value* ret: none* modify:* comment:******************************************************************************* **************/void Lcd_Draw_Box(INT16 usLeft, INT16 usTop, INT16 usRight, INT16 usBottom, INT8UucColor){Lcd_Draw_HLine(usLeft, usRight, usTop, ucColor, 1);Lcd_Draw_HLine(usLeft, usRight, usBottom, ucColor, 1);Lcd_Draw_VLine(usTop, usBottom, usLeft, ucColor, 1);Lcd_Draw_VLine(usTop, usBottom, usRight, ucColor, 1);}/****************************************************************************** **************** name: Lcd_Draw_Line()* func: Draw line with appointed color* para: usX0,usY0 -- line's start point coordinate* usX1,usY1 -- line's end point coordinate* ucColor -- appointed color value* usWidth -- line's width* ret: none* modify:* comment:******************************************************************************* **************/void Lcd_Draw_Line(INT16 usX0, INT16 usY0, INT16 usX1, INT16 usY1, INT8U ucColor, INT16U usWidth){INT16 usDx;INT16 usDy;INT16 y_sign;INT16 x_sign;INT16 decision;INT16 wCurx, wCury, wNextx, wNexty, wpy, wpx;if( usY0 == usY1 ){Lcd_Draw_HLine (usX0, usX1, usY0, ucColor, usWidth);return;}if( usX0 == usX1 ){Lcd_Draw_VLine (usY0, usY1, usX0, ucColor, usWidth);return;}usDx = abs(usX0 - usX1);usDy = abs(usY0 - usY1);if( ((usDx >= usDy && (usX0 > usX1)) ||((usDy > usDx) && (usY0 > usY1))) ){GUISWAP(usX1, usX0);GUISWAP(usY1, usY0);}y_sign = (usY1 - usY0) / usDy;x_sign = (usX1 - usX0) / usDx;if( usDx >= usDy ){for( wCurx = usX0, wCury = usY0, wNextx = usX1,wNexty = usY1, decision = (usDx >> 1);wCurx <= wNextx; wCurx++, wNextx--, decision += usDy ) {if( decision >= usDx ){decision -= usDx;wCury += y_sign;wNexty -= y_sign;}for( wpy = wCury - usWidth / 2;wpy <= wCury + usWidth / 2; wpy++ ){LCD_PutPixel(wCurx, wpy, ucColor);}for( wpy = wNexty - usWidth / 2;wpy <= wNexty + usWidth / 2; wpy++ ){LCD_PutPixel(wNextx, wpy, ucColor);}}}else{for( wCurx = usX0, wCury = usY0, wNextx = usX1,wNexty = usY1, decision = (usDy >> 1);wCury <= wNexty; wCury++, wNexty--, decision += usDx ) {if( decision >= usDy ){decision -= usDy;wCurx += x_sign;wNextx -= x_sign;}for( wpx = wCurx - usWidth / 2;wpx <= wCurx + usWidth / 2; wpx++ ){LCD_PutPixel(wpx, wCury, ucColor);}for( wpx = wNextx - usWidth / 2;wpx <= wNextx + usWidth / 2; wpx++ ){LCD_PutPixel(wpx, wNexty, ucColor);}}}}/****************************************************************************** **************** name: Lcd_Draw_HLine()* func: Draw horizontal line with appointed color* para: usX0,usY0 -- line's start point coordinate* usX1 -- line's end point X-coordinate* ucColor -- appointed color value* usWidth -- line's width* ret: none* modify:* comment:******************************************************************************* **************/void Lcd_Draw_HLine(INT16 usX0, INT16 usX1, INT16 usY0, INT8U ucColor, INT16U usWidth){INT16 usLen;if( usX1 < usX0 ){GUISWAP (usX1, usX0);}while( (usWidth--) > 0 ){usLen = usX1 - usX0 + 1;while( (usLen--) > 0 ){LCD_PutPixel(usX0 + usLen, usY0, ucColor);}usY0++;}}/****************************************************************************** **************** name: Lcd_Draw_VLine()* func: Draw vertical line with appointed color* para: usX0,usY0 -- line's start point coordinate* usY1 -- line's end point Y-coordinate* ucColor -- appointed color value* usWidth -- line's width* ret: none* modify:* comment:******************************************************************************* **************/void Lcd_Draw_VLine (INT16 usY0, INT16 usY1, INT16 usX0, INT8U ucColor, INT16U usWidth){INT16 usLen;if( usY1 < usY0 ){GUISWAP (usY1, usY0);}while( (usWidth--) > 0 ){usLen = usY1 - usY0 + 1;while( (usLen--) > 0 ){LCD_PutPixel(usX0, usY0 + usLen, ucColor);}usX0++;}}/*--- extern variables ---*/extern INT8U g_auc_Ascii8x16[];/****************************************************************************** **************** name: Lcd_DspAscII8x16()* func: display 8x16 ASCII character string* para: usX0,usY0 -- ASCII character string's start point coordinate* ForeColor -- appointed color value* pucChar -- ASCII character string* ret: none* modify:* comment:******************************************************************************* **************/void Lcd_DspAscII8x16(INT16U x0, INT16U y0, INT8U ForeColor, INT8U * s){INT16 i,j,k,x,y,xx;INT8U qm;INT32U ulOffset;INT8 ywbuf[16],temp[2];for( i = 0; i < strlen((const char*)s); i++ ){if( (INT8U)*(s+i) >= 161 ){temp[0] = *(s + i);temp[1] = '\0';return;}else{qm = *(s+i);ulOffset = (INT32U)(qm) * 16; //Here to be changed tomorrowfor( j = 0; j < 16; j ++ ){ywbuf[j] = g_auc_Ascii8x16[ulOffset + j];}for( y = 0; y < 16; y++ ){for( x = 0; x < 8; x++ ){k = x % 8;if( ywbuf[y] & (0x80 >> k) ){xx = x0 + x + i*8;LCD_PutPixel(xx, y + y0, (INT8U)ForeColor);}}}}}}/*--- extern variables ---*/extern INT8U g_auc_Ascii6x8[];#define XWIDTH 6/****************************************************************************** **************** name: Lcd_DspAscII6x8()* func: display 6x8 ASCII character string* para: usX0,usY0 -- ASCII character string's start point coordinate* ForeColor -- appointed color value* pucChar -- ASCII character string* ret: none* modify:* comment:******************************************************************************* **************/void Lcd_DspAscII6x8(INT16U usX0, INT16U usY0,INT8U ForeColor, INT8U* pucChar) {INT32U i,j;INT8U ucTemp;while( *pucChar != 0 ){for( i=0; i < 8; i++ ){ucTemp = g_auc_Ascii6x8[(*pucChar) * 8 + i];for( j = 0; j < 8; j++ ){if( (ucTemp & (0x80 >> j)) != 0 ){LCD_PutPixel(usX0 + i, usY0 + 8 - j, (INT8U)ForeColor);}}}usX0 += XWIDTH;pucChar++;}}#ifndef Eng_v/****************************************************************************** **************** name: Lcd_DspHz16()* func: display chinese character string in 16x16 dot array* para: usX0,usY0 -- ASCII character string's start point coordinate* ForeColor -- appointed color value* pucChar -- ASCII character string* ret: none* modify:* comment:******************************************************************************* **************/extern const INT8U g_auc_HZK16[];void Lcd_DspHz16(INT16U x0, INT16U y0, INT8U ForeColor, INT8U *s){INT16 i,j,k,x,y,xx;INT8U qm,wm;INT32U ulOffset;INT8 hzbuf[32],temp[2];for( i = 0; i < strlen((const char*)s); i++ ){if( ((INT8U)(*(s+i))) < 161 ){temp[0] = *(s+i);temp[1] = '\0';break;}else{qm = *(s+i) - 161;wm = *(s + i + 1) - 161;ulOffset = (INT32U)(qm * 94 + wm) * 32;for( j = 0; j < 32; j ++ ){hzbuf[j] = g_auc_HZK16[ulOffset + j];}for( y = 0; y < 16; y++ ){for( x = 0; x < 16; x++ ){k = x % 8;if( hzbuf[y * 2 + x / 8] & (0x80 >> k) ){xx = x0 + x + i * 8;LCD_PutPixel( xx, y + y0, (INT8U)ForeColor);}}}i++;}}}#endif/****************************************************************************** **************** name: Lcd_Test()* func: LCD test function* para: none* ret: none* modify:* comment:******************************************************************************* **************/void Lcd_Test(void){int i, j;Uart_Printf("\n LCD display Test Example(please look at LCD screen)\n");/* initial LCD controller */Lcd_Init();/* clear screen */Lcd_Clr();/* draw rectangle pattern */#ifdef Eng_v // english versionLcd_DspAscII8x16(10,0,BLUE,"Embest S3CEV40");#elseLcd_DspAscII8x16(100, 50, RED, "2009073 20091989 ");Lcd_DspHz16(155, 70, RED, "马一鸣");Lcd_DspAscII8x16(100, 90, BLACK, "2009073 20091993 ");Lcd_DspHz16(155, 110, BLACK, "邓家坤");Lcd_DspAscII8x16(100, 130, BLUE, "2009073 20092022 ");Lcd_DspHz16(155, 150, BLUE, "蒋赵睿");DelayMs(500);Lcd_DspHz16( 100, 100, BLUE, "欢迎使用电子词典");Lcd_DspAscII8x16(100, 50, WHITE, "2009073 20091989 ");Lcd_DspHz16(155,70, WHITE, "马一鸣");Lcd_DspAscII8x16(100, 90, WHITE, "2009073 20091993 ");Lcd_DspHz16(155, 110, WHITE, "邓家坤");Lcd_DspAscII8x16(100, 130, WHITE, "2009073 20092022 ");Lcd_DspHz16(155, 150, WHITE, "蒋赵睿");DelayMs(500);Lcd_Clr();Lcd_DspHz16(15,15,BLUE,"电子词典");#endif//Lcd_DspAscII8x16(10,24,GREEN-55,"ShenZhen Embest Info&Tech Co.,LTD");Lcd_Draw_Box(5,30,115,180,GREEN);/*显示窗口*/Lcd_Draw_Box(5,190,75,230,GREEN);/*输入窗口*/Lcd_Draw_Box(75,190,115,230,GREEN);/*搜索键*/Lcd_Draw_Box(120,30,165,75,GREEN);/*abc*/Lcd_Draw_Box(170,30,215,75,GREEN);/*def*/Lcd_Draw_Box(220,30,265,75,GREEN);/*ghi*/Lcd_Draw_Box(270,30,315,75,GREEN);/*jkl*/Lcd_Draw_Box(120,80,165,125,GREEN);/*mno*/Lcd_Draw_Box(170,80,215,125,GREEN);/*pqr*/Lcd_Draw_Box(220,80,265,125,GREEN);/*stu*/Lcd_Draw_Box(270,80,315,125,GREEN);/*vwx*/Lcd_Draw_Box(120,130,165,175,GREEN);/*yz*/Lcd_Draw_Box(170,130,215,175,GREEN);/*选择1*/Lcd_Draw_Box(220,130,265,175,GREEN);/*选择2*/Lcd_Draw_Box(270,130,315,175,GREEN);/*选择3*/Lcd_Draw_Box(120,180,165,225,GREEN);/*back*/Lcd_Draw_Box(170,180,215,225,GREEN);/*ent*/Lcd_Draw_Box(220,180,265,225,GREEN);/*save*/Lcd_Draw_Box(270,180,315,225,GREEN);/* output ASCII symbol */Lcd_DspAscII6x8(90,210,BLACK,"scan");Lcd_DspAscII6x8(140,50,BLACK,"abc");Lcd_DspAscII6x8(190,50,BLACK,"def");Lcd_DspAscII6x8(240,50,BLACK,"ghi");Lcd_DspAscII6x8(290,50,BLACK,"jkl");Lcd_DspAscII6x8(140,100,BLACK,"mno");Lcd_DspAscII6x8(190,100,BLACK,"pqr");Lcd_DspAscII6x8(240,100,BLACK,"stu");Lcd_DspAscII6x8(290,100,BLACK,"vwx");Lcd_DspAscII6x8(140,150,BLACK,"yz");Lcd_DspAscII6x8(190,150,BLACK,"ch1");Lcd_DspAscII6x8(240,150,BLACK,"ch2");Lcd_DspAscII6x8(290,150,BLACK,"ch3");Lcd_DspAscII6x8(140,200,BLACK,"back");Lcd_DspAscII6x8(190,200,BLACK,"ent");Lcd_DspAscII6x8(240,200,BLACK,"save");Lcd_DspAscII6x8(290,200,BLACK," ");/*for (j = 0; j < 1000000 * 5; j++);while (1){for (i = 0; i < 5; i++){BitmapView320x240x256((INT8U*)(aucTempBitmap[i]));for (j = 0; j < 1000000 * 5; j++);}}*/}/****************************************************************************** **************** name: Lcd_Test_board()* func: LCD test function for board all test* para: none* ret: none* modify:* comment:******************************************************************************* **************/void Lcd_Test_board(void){int i, j;/* initial LCD controller */Lcd_Init();/* clear screen */Lcd_Clr();/* draw rectangle pattern */#ifdef Eng_v // english versionLcd_DspAscII8x16(10,0,BLUE,"Embest S3CEV40 ");#elseLcd_DspHz16(10,10,BLUE,"英蓓特三星实验平台");#endif。

电子词典系统4

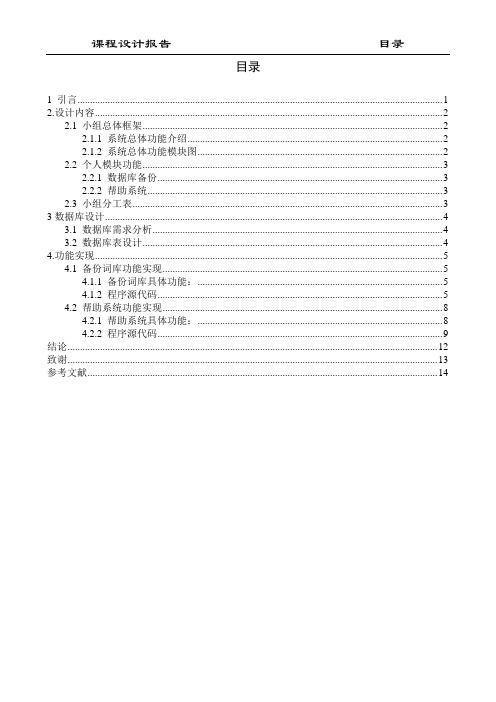

目录1 引言 (1)2.设计内容 (2)2.1 小组总体框架 (2)2.1.1 系统总体功能介绍 (2)2.1.2 系统总体功能模块图 (2)2.2 个人模块功能 (3)2.2.1 数据库备份 (3)2.2.2 帮助系统 (3)2.3 小组分工表 (3)3数据库设计 (4)3.1 数据库需求分析 (4)3.2 数据库表设计 (4)4.功能实现 (5)4.1 备份词库功能实现 (5)4.1.1 备份词库具体功能: (5)4.1.2 程序源代码 (5)4.2 帮助系统功能实现 (8)4.2.1 帮助系统具体功能: (8)4.2.2 程序源代码 (9)结论 (12)致谢 (13)参考文献 (14)1 引言在这一周的课设中,我们小组开发的课题是电子词典功能的实现。

电子词典作为一种学习工具,有着不可估量的市场前景。

作为一名学生,我们在学习英语的时候会经常碰到很多的生词,有时,为了读懂一篇文章,经常是读文章用一小时,但是其中却有半个小时都在翻阅英语字典。

所以我们小组为了解决这一问题,才将选材方向定位于电子词典的功能实现,主要的目的就是为同学们解决这一问题。

在做电子词典功能实现的时候,我们小组主要从以下几个方面入手,即:英汉互译、汉英互译、单词发音。

在英译汉、汉译英这两个功能模块上,我们首先提供了一个查询界面,即使用者需要输入要查询的关键字,点击确定按钮,屏幕上就会出现其对应的答案。

在做这个模块的时候,我们主要解决了JAVA与数据库的链接问题,进而实现其功能。

在娱乐天地中,扫雷游戏是用JAVA来实现的。

之所以要加入这一模块,是因为我们充分考虑到在学习疲惫之余可以让使用者能够有个放松的空间,同时也提高其整体的娱乐性。

从系统的可扩展性方面考虑,我们在系统中加入了对单词库的添加、删除、修改功能。

有了这个功能模块,将给予使用者带来很大的方便。

当然也存在一种情况,即刚开始接触而不懂得如何去使用电子词典,为此我们特地的加入了帮助界面,帮助界面是用JAVA小程序完成的。

毕业设计--基于Android的电子词典软件的设计与实现 (含外文翻译)

LANZHOU UNIVERSITY OF TECHNOLOGY毕业设计基于Android的电子词典软件的设计与实现学生姓名学号专业班级指导教师学院计算机与通信学院摘要本文设计了基于Android平台的电子词典软件。

此英文词典包括两部分,一部分是离线的英文词典,一部分是在线的英文词典。

离线的英文词典主要是使用Android自带的轻量级数据库SQLite来保存单词信息,系统通过SQLite数据库的query方法来查找到与指定英文相对应的单词的中文释义。

在线的英文词典是利用oracle数据库来保存单词信息,然后利用Http 协议解析出单词信息显示到手机界面上,同时还能够增加、删除、更新单词信息。

当然,对于查询到的生疏的单词可以添加到单词本以便于随时复习。

关键词:Android,oracle数据库,SQLite数据库,英文单词AbstractIn this paper, we design and implementation about electronic dictionary software which is based on the Android platform. English dictionary mainly include two parts, and one is to realize the offline English dictionary, the other is to realize the online English dictionary. Offline English dictionary is mainly used a lightweight database SQLite that belongs to Android to preserve words information, we find the specified English word corresponding to the Chinese interpretation by using query method of SQLite database. Offline English dictionary use an oracle database to save the word information, and then parse out the word information to display in the mobile phone interface by Http protocol, at the same time there have the functions that is used to increase, delete, update word information. Of course, we can add unfamiliar word to the note of word in order to review at any time.Keywords: Android; oracle database; SQLite database; English words目录第1章绪论 (1)第2章系统需求分析 (3)2.1 软件的功能要求 (3)2.2 需求分析 (3)2.3 功能需求(用例图分析) (4)2.3.1 基本功能需求例图 (4)2.3.2 离线词典的例图 (6)2.3.3 在线查询用例图 (7)2.3.4 添加到单词本的用例图 (8)2.4 系统结构图和流程图 (10)2.5 系统界面需求 (14)2.6 运行环境 (15)2.6.1 关键技术 (15)2.6.2 运行环境 (16)第3章数据库的设计 (16)3.1 在线词典的服务器端的数据库设计 (16)3.1.1 数据库中数据表的设计 (16)3.1.2 在线词典的客户端的数据库设计 (17)3.1.3 离线时的数据库的设计 (18)3.1.4 软件数据模型 (19)3.2 连接数据库 (20)3.2.1 数据库的创建 (20)3.2.2.数据库的操作 (20)3.2.3 数据的查看 (21)3.2.4 服务器和客户端的连接 (21)第4章环境的搭建 (23)4.1关于Android的简单介绍 (23)4.1.1 Android环境的搭建 (23)4.1.2Android命令行的使用 (24)4.1.3 Android工程的简单介绍 (25)4.2 Java Web环境的搭建 (28)第5章具体功能模块的设计 (31)5.1 查询模块的设计 (32)5.1.1 离线查询 (32)5.1.2 在线查询 (33)5.2 添加单词模块 (35)5.3 删除单词模块 (36)5.4 修改单词模块 (37)5.5 菜单模块的实现 (38)5.6 生词本模块的设计 (42)第6章系统测试与性能分析 (44)6.1测试 (44)6.2 性能测试及分析 (45)总结 (46)参考文献 (47)附录一:英文翻译原文 (48)附录二:英文翻译译文 (56)附录三:程序清单 (63)致谢 (70)第1章绪论如今,英语在人们的工作、学习中显得越来越重要,而手机词典软件的出现无疑带来了极大的便利,遇到遇到生疏的英语单词,现在拿起手机就能轻松解决。

c语言电子词典程序设计.doc

沈阳工程学院课程设计设计题目:电子词典系别信息工程系班级计本083 学生姓名学号 22指导教师姜柳、吕海华职称讲师、讲师起止日期:2009年6月15日起——2009年6月26日止沈阳工程学院课程设计任务书课程设计题目:电子词典(第 1 组)系别信息工程系班级计本075学生姓名于满盛学号 2008412322指导教师姜柳、吕海华职称讲师、讲师课程设计进行地点:实训F任务下达时间: 2009年 6月 15日起止日期:2009年6月15日起——2009年6月26日止教研室主任姜柳 2009年6月15日批准一、课程设计的原始资料及依据在计算机中建立有限规模的电子英汉词典,利用程序实现电子英汉词典的查找、增加、删除、修改等功能。

查阅有关资料,进一步理解程序设计模块化的思想,并利用此思想编写一个简单的电子词典。

通过本设计可以加深理解利用程序设计思想开发一个系统的整个流程,提高分析问题、解决问题和实际动手的能力。

二、课程设计主要内容及要求1.认真阅读资料,掌握程序设计模块化的思想。

2.要求在设计的过程中,建立清晰的层次结构。

3.画出主要的功能结构图和主要模块的流程图。

4.实现功能:⑴查找单词。

⑵增加单词。

⑶万年历⑷修改单词。

⑸显示单词。

⑹保存单词。

⑺返回⑻帮助⑼退出5. 要求操作简单,用户界面友好。

6. 运行程序,检查结果是否和理论值一致。

7. 环境使用Windows,Turbo C环境。

三、对课程设计说明书撰写内容、格式、字数的要求1.课程设计说明书是体现和总结课程设计成果的载体,主要内容包括:设计题目、设计目的、设备器材、设计原理及内容、设计步骤、遇到的问题及解决方法、设计总结、参考文献等。

一般不应少于3000字。

2.在适当位置配合相应的实验原理图、功能模块图、算法流程图等图表进行说明。

应做到文理通顺,内容正确完整,书写工整,装订整齐。

3.设计总结部分主要写本人完成工作简介以及自己的设计体会,包括通过课程设计学到了什么,哪里遇到了困难,解决的办法以及今后的目标。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于S3C44BOX的电子词典软件设计与实现1 概述此次基于ARM7的电子词典系统开发作业,由我们小组4人合作完成,其中我主要负责软件方面的开发,所做的方面有英译汉软件功能的实现,输入值软件识别功能的实现以及看门狗定时器的实现。

由于不怎么熟悉arm的开发,基本是看着书做,设计思路和方法、功能实现也都是书上怎么来,自己就怎么实现,希望傅老师谅解,这块的基础确实薄弱。

2 S3C44BOX处理器介绍2.1 S3C44BOX简介S3C44BOX微处理器片类集成ARM7TDMI核,采用0.25μm CMOS工艺制造,并在ARM7TDMI核的基础上集成了丰富的外围功能模块,便于低成本设计嵌入式系统应用系统。

片上集成的主要功能如下:➢在ARM7TDMI基础上增加至8KB的Cache。

➢外部扩充存储器控制器(FP/EDO/SDRAM控制,片选逻辑)。

➢LCD控制器(最大支持256色的DSTN),并带有一个LCD专用DMA通道。

➢2个通用DMA通道2个带外部请求引脚的DMA通道。

➢2个带有握手协议的UART,1个SIO。

➢1个多主的I2C总线控制器。

➢1个I2S总线控制器。

➢5个PWM定时器及1个部定时器。

➢看门狗定时器。

➢71个通用可编程I/O口,8个外部中断源。

➢功耗控制模式:正常,低速,休眠和停止。

➢8路10位ADC。

➢具有日历功能的RTC(实时时钟)。

➢PLL时钟发生器。

2.2 S3C44BOX特点2.2.1 S3C44BOX体系结构➢S3C44BOX是基ARM7TDMI体系结构的SOC。

➢集成了手持设备和通用嵌入式系统应用的解决方案;➢16/32位RISC体系结构和ARM7TDMI处理器核强大的指令体系;➢Thumb代码压缩机,最大化代码密度同时保持了32位指令的性能;➢基于JTAG的片上集成ICE调试支持解决方案;➢32×8位硬件乘法器;➢实现低功耗SAMBA II(三星ARM处理器嵌入式微控制器总线体系结构)的新型总线结构。

2.2.2 系统(存储)管理➢支持大/小端方式;➢寻址空间:每bank32M字节(共256M字节);➢支持每bank可编程的8/16/32位数据总线宽度;➢7个bank具有固定的bank起始地址和可编程的bank大小;➢1个bank具有可编程的bank起始地址和bank大小;➢8个存储器bank:-6个ROM,SRAM存储器bank;-2个ROM/SRAM/DRAM(快速页面,EDO和同步DRAM);➢所有的存储器bank具有可编程的操作周期;➢支持外部等待信号延长总线周期;➢支持掉电时DRAM/SDRAM的自刷新模式;➢支持均匀/非均匀的DRAM地址。

2.2.3 Cache存储器和部SRAM➢4路组相联统一的8KB指令/数据Cache;➢未用的Cache空间用来作为4/8 KB Cache存储空间可作为片的SRAM使用;➢支持LRU(近期最少使用)替换算法➢采用保持主存储器与cache容一致性的“写穿式”策略➢写存储器具有4级深度➢当缓冲区出错时,采用“请求数据优首先填充”技术2.2.4 时钟和电源管理➢低功耗➢片上PLL使MCU工作时钟最大达到75MHz➢可以通过软件设置各功能模块的输入时钟➢电源模式:正常,慢速,空闲和停止模式;◆正常模式正常工作模式;◆低速模式不加PLL的低时钟频率模式;◆休眠模式只停止CPU的时钟;◆SL空闲模式 LCD控制器工作◆停止模式停止所有的时钟;➢通过EINT[7:0]或RTC报警中断从停止模式唤醒2.2.5 中断控制器➢30个中断源(看门狗定时器,6个定时器,6个UART,8个外部中断,4个DMA,2个RTC,1个ADC,1个I2C,1个SIO)➢采用向量化的IRQ中断模式以减少中断的延迟➢可选的电平/边沿模式触发外部中断➢电平/边沿模式具有可编程的优先级➢支持FIQ为紧急的中断请求进行服务2.2.6 定时器和PWM(脉宽调制)➢5通道16位具有PWM功能的定时器,1通道16位部定时器(可进行基于DMA或中断的操作)➢可编程的占空比周期,频率,和优先级➢能产生死区➢支持外部时钟源2. 2.7 RTC(实时时钟)➢充分的时钟特性:毫秒,秒,分钟,小时,日,星期,月,年➢32.768KHz时钟;➢定时警报,可用于唤醒CPU;➢可产生时钟节拍中断2.2.8 通用I/O口➢8个外部中断口➢71个多功能输入/输出口2.2.9 UART(异步串行通讯)➢2通道UART,可进行基于DMA或中断的操作➢支持5位,6位,7位或8位串行数据传输/接收➢支持在发送/接收期间的H/W握手功能➢可编程的波特率➢支持IrDA 1.0(115.2Kbps)➢支持用于测试的回馈模式➢每个通道具有2个部32字节的FIFO分别用于输入和输出2.2.10 DMA(直接存储器操作)控制器➢2通道通用DMA(直接存储器操作)控制器,不需要CPU干预➢2通道DMA桥(外设DMA)控制器➢支持I/O到存储器,存储器到I/O,I/O到I/O的6种DMA请求:软件,4个部功能模块(UART,SIO,定时器,IIS),和外部引脚。

➢在同时发生的多个DMA之间具有可编程的优先级顺序;➢采用猝发式的传输模式以提高FPDRAM, EDODRAM和SDRAM的数据传输速率;➢支持在外部设备到存储器和存储器到外部设备之间采用fly-by模式2.2.11 A/D转换器➢8通道的ADC➢最大500k SPS/10-bit2.2.12 LCD 控制器➢支持彩色/黑白/灰度LCD屏➢支持单路扫描和双路扫描➢支持虚拟显示屏功能➢系统存储器用来作为显示缓存➢用专门的DMA来从系统存储器中获得图象数据➢可编程的屏幕大小➢灰度等级:16级灰度;➢最多256种颜色2.2.13 看门狗定时器➢16位的看门狗定时器➢在定时器溢出时发出中断请求或系统复位2.2.14 I2C总线接口➢1通道多主I2C总线,可进行基于中断的操作模式➢可进行串行,8位,双向数据传输,标准模式速度达到100Kbit/S,快速模式达到400Kbit/s2.2.15 I2S总线接口➢1通道音频I2S总线接口,可进行基于DMA的操作➢串行,每通道8/16位数据传输➢支持MSB-justified数据格式2.2.16 SIO(同步串行I/O)➢1通道SIO,可进行基于DMA或中断的操作➢可编程的波特率➢支持8位串行数据的传输和接收操作2.2.17 工作电压围➢核2.5V,I/O口:3.0V到3.6V2.2.18 工作频率➢最大75MHz2.2.19 封装➢160LQFP/160FBGA2.3 S3C44BOX功能结构框图图1 S3C44BOX功能结构框图2.4S3C44BOX芯片引脚定义图2 S3C44BOX芯片引脚定义图3 基于S3C44BOX电子词典开发嵌入式系统以其体积小,性能好,功耗低,可靠性高以及面向行业应用的特点已被广泛应用与各个领域。

其中电子词典是嵌入式系统消费电子领域典型的应用实例,它具有完整的输入/输出设备。

3.1 电子词典系统定义与需求分析电子词典系统应具备以下功能要求:(1)能够通过键盘、触摸屏输入英文a~z:实现字母输入;Page up/down:显示上/下一个被查询过的单词;Line up/down:光标移至上/下一行,在单词输入过程中,在单词翻译区会有拼写相近单词显示,用Line up/down按键可以上下选择这些单词;Enter:翻译,将当前单词与词库中的容相比较,如有一致则显示其容,否则给出提示;Back space:退格,删除单词最末尾的字母并将光标前移一位;提供触摸屏输入六个功能键。

(2)提供友好的人机界面,将输入的容和翻译的结果显示在LCD的相应区域。

(3)对输入的单词即时翻译。

(4)可以记忆3个已经查询过的单词。

图3-1 查询界面3.2 电子词典方案设计为实现电子词典功能需求,结合嵌入式系统软硬件协同技术设计,采取以下设计方案。

3.2.1硬件设计依据ARM芯片的选择原则,此处选择集成了丰富的外围功能模块,便于低成本设计嵌入式应用系统的S3C44BOX处理器作为系统的主控制器。

利用其置的LCD控制器实现LCD控制接口;利用I²C总线控制器实现键盘控制接口;利用A/D转换器实现触摸屏控制接口;利用UART实现调试接口;利用GPIO连接LED灯显示有关状态。

以上5个硬件部分的开发中,其中第1,2,3,5本组其他同学完成,第4个部分UART实现调试接口的开发与应用,在本文档中重点说明,由本人单独完成。

3.2.2软件设计本电子词典软件只要完成键盘操作,菜单操作及LCD显示功能。

根据软件模块化设计方法将系统软件分为3个模块;词库编写,功能控制软件设计,人机交互接口功能设计。

我负责软件的总体设计图,实现其基本功能。

其中按键分别具有如下功能:a~z:实现字母输入;Page up/down:显示上/下一个被查询过的单词;Line up/down:光标移至上/下一行,在单词输入过程中,在单词翻译区会有拼写相近单词显示,用Line up/down按键可以上下选择这些单词;Enter:翻译,将当前单词与词库中如相比较,若一致则显示其容,否则给出提示;Back space:退格,删除单词最末尾的字母并将光标前移一位。

本电子词典系统还需要提供触摸输入,在触摸屏上划分出6个区域,分别对应键盘上的6个功能键。

4 开发环境电子词典硬件模块测试软件和无操作系统电子词典应用软件的开发采用了相同的交叉开发环境。

宿主机PC机上运行ARM公司为方便用户在基于ARM 核处理器上进行软件开发而推出的集成开发工具ARMADS(ARM Developer Suite)最新版本1.2在Codewarrior IDE(Integrate Development Environment)集成开发环境中编辑电子词典软件程序,通过交叉编译器和交叉器对软件进行编译,。

最终生成可执行文件,通过在线仿真器Multi-ICE将此可真行文件下载到目标板运行。

在线仿真器通过并口宿主机,通过JTAG接口目标机。

串口线直接宿主机和目标板,在宿主机PC机上显示吊饰信息。

为加快软件开发的进度,在电子词典硬件平台未建立起来以前先使用Embest EDUKIT 实验板作为目标本吊饰各功能模块软件。

5 开发功能说明和代码5.1英译汉功能软件由于要查的英文单词有两种输入方式:一种是通过在输入框中输入字母;另一种是通过上一行/下一行键在选择框里显示的单词中进行选择,所以用参数Position表示输入方式(TRUE:输入框,FALSE:选择框查找)。

具体实现流程如图所示:/************************************************************ name: translate* func: Translation function implementation program * para: none* ret: none* modify:* comment*************************************************************/ U8 transate(S8* word,U8 Position,U8 No){U8 k=0;Trans_Clear();Dis_Chinese(20,55,Gui_WHITE,”正在查找,请等待!”);if(!Position){strcpy(word,vocab[No].c);Disp_String(word,English_area.x0+5,English_area.y0+2);}for(k=0;k<ALL_WNo;k++){if(strcmp(word,vocab[k].c)==0){Trans_Clear();Disp_String(vocab[k].d,20,55);Disp_chinese(20,75,GUI_WHITE,vocab[k].e);Disp_String(vocab[k].f,20,95);Return k;}}Trans_Clear()’Dis_Chinese(20,55,GUI_WHITE,”查无此词!”);return (k=ALL_WNo);}/******************************************************************** * name: KeyboardInt* func: keyboard interrupt handler function* para: none* ret: none* modify:* comment:********************************************************************/ void KeyboardInt(void){int nTemp,i,j,k,m=0;char bbyte;rI_ISPC = BIT_EINT1; // clear pending bitchar pbyte[10];nTemp = key_read();if(nTemp > -1){// Lcd_Draw_HLine(10, 310, 80, WHITE, 50);input_char = nTemp;Lcd_DspAscII8x16(15,45,WHITE,word);switch(input_char){case 0:num=1;break;case 1:num=2;break;case 2:num=3;break;case 3:num=4;break;case 4:num=5;break;case 5:num=6;break;case 6:num=7;break;case 7:num=8;break;case 8:num=9;break;case 9:counter=1;break;case 10:counter=2;break;case 11:counter=3;break;case 12:m=1;Lcd_Draw_HLine(15+n-10, 15+n, 45, WHITE, 16);n-=10;word[wordIndex]='\0';wordIndex--;break;/*if(n==0){word[20]=0;wordIndex=0;Lcd_Draw_HLine(10, 310,85, WHITE, 160);}break;*/case 13:word[wordIndex]='\0';wordIndex=0;for(i=0;i<20;i++){if(strcmp(word,vocab[i].c)==0){j=0;k=i;break;}elsej=1;}if(j==0){//#ifdef Eng_vLcd_DspAscII8x16(15,40,BLUE,vocab[k].c);Lcd_DspAscII8x16(15,60,BLUE,vocab[k].d);Lcd_DspAscII8x16(15,80,BLUE,vocab[k].f);//#elseLcd_DspHz16(15,100,BLUE,vocab[k].e);//#endif}else{Lcd_DspHz16(15,120,BLUE,"未找到相应的单词"); DelayMs(600);Lcd_DspHz16(15,120,WHITE,"未找到相应的单词"); }break;case 14:word[wordIndex]='\0';wordIndex=0;for(i=0;i<20;i++){if(strcmp(word,vocab[i].c)==0){j=0;k=i;break;}elsej=1;}if(j==0){//#ifdef Eng_vLcd_DspAscII8x16(15,40,BLUE,vocab[k].c);Lcd_DspAscII8x16(15,60,BLUE,vocab[k].d);Lcd_DspAscII8x16(15,80,BLUE,vocab[k].f);//#elseLcd_DspHz16(15,100,BLUE,vocab[k].e);//#endif}else{if(20>x>0){for(i = 0; i < 20; i++)vocab[x].c[i]=word[i];word[i]='\0';Lcd_DspAscII8x16(15,40,BLUE,vocab[x].c);x++;}elsex=15;//Lcd_DspAscII8x16(15,45,BLUE,word);for(i = 0; i < 20; i++)word[i]='\0';}break;case 15://Lcd_Draw_Box(10,40,310,80,GREEN);break;}if(num!=0&&counter!=0){switch(3*(num-1)+counter-1){case 0:bbyte='a';break;case 1:bbyte='b';break;case 2:bbyte='c';break;case 3:bbyte='d';break;case 4:bbyte='e';break;case 5:bbyte='f';break;case 6:bbyte='g';break;case 7:bbyte='h';break;case 8:bbyte='i';break;case 9:bbyte='j';break;case 10:bbyte='k';break;case 11:bbyte='l';break;case 12:bbyte='m';break;case 13:bbyte='n';break;case 14:bbyte='o';break;case 15:bbyte='p';break;case 16:bbyte='q';break;case 17:bbyte='r';break;case 18:bbyte='s';break;case 19:bbyte='t';break;case 20:bbyte='u';break;case 21:bbyte='v';break;case 22:bbyte='w';break;case 23:bbyte='x';break;case 24:bbyte='y';break;case 25:bbyte='z';break;}num=0;counter=0;if(m==0){word[wordIndex]=bbyte;wordIndex++;//n+=10;}}Lcd_DspAscII8x16(15,210,BLUE,word);// Uart_Printf("Key is:%x \r",input_char); }}5.2输入键值识别功能软件本电子词典设计中共有26个字母键和6个功能键。