手机开发流程框图

新产品开发流程管理

23

主要的子流程

硬件设计流程 软件设计流程 文件控制流程 质量控制的Gate流程 工程管理流程 错误报告及纠正流程 系统工程流程

24

新产品开发流程

组织构造管理

25

组织构造

行政组织构造 工程组织构造

26

开发的行政组织构造

开发部门

系统设计组 软件组

硬件设计组

开发支持组

系统测试组

软件系统设计组

机械设计组

31

硬件设计流程

phase1

立项

系统 定义

phase2

系统 设计 子系统 模块定义

phase3 phase4 phase5 phase6

子系统/ 模块设 计及测试 系统定义

子系统/模 块认证及 测试系统

设计

系统认证 和测试系 统认证

试消费 (Pilot-run)

完成

设计输出

硬件子 系统定义

硬件子 系统设计

新产品开发流程

深圳市东大博彦企业管理咨询公司

1

主要内容 1

新产品开发流程是关键流程 新产品流程介绍 新产品流程简介 新产品开发流程详解 概况 主要的子流程 硬件开发流程 软件开发流程 质量控制流程 文件控制流程 工程管理流程

2

主要内容2

组织构造介绍 工程管理方法 开发人员的管理和考核 词汇表 参考资源

3

第一部分

新产品开发流程是 关键流程

4

新产品开发的现实情况

新产品代表企业60%的年销售额和50%利润 80年代中期:33%和22% 90年代中期:50%和40% 当今成功的企业有大量的新产品 在产品开发上的革新增加企业对投资者的回报 新产品是企业将来成长的新颖血液

算法框图的基本结构及设计

03

算法框图的设计原则

清晰性

总结词

确保算法框图的逻辑清晰,易于理解。

VS

详细描述

算法框图的设计应遵循清晰的原则,使得 读者能够快速理解算法的逻辑流程。每个 节点和线条都应具有明确的含义,避免使 用模糊或含糊不清的符号。同时,应尽量 减少不必要的细节,突出关键信息,使整 个框图简洁明了。

完整性

总结词

基于算法框图的流程分析,可以制定出更有效的优化 方案。

06

算法框图的设计实例

排序算法的框图设计

01 02 03

冒泡排序

通过重复地遍历待排序的数列,一次比较两个元素,如果 他们的顺序错误就把他们交换过来,遍历数列的工作是重 复地进行直到没有再需要交换,也就是说该数列已经排序 完成。

选择排序

在未排序的序列中找到最小(或最大)的元素,存放到排 序序列的起始位置,然后再从剩余未排序的元素中继续寻 找最小(或最大)元素,然后放到已排序序列的末尾。以 此类推,直到所有元素均排序完毕。

插入排序

将待排序的元素插入到已经排好序的有序序列中,从而得 到一个新的、个数加一的有序序列,算法适用于少量数据 的排序,时间复杂度为O(n^2)。

分治算法的框图设计

归并排序

采用分治法的思想,将待排序的序列分成两个子序列,分别对子序列进行排序,然后将有序的子序列合并成一个 有序的序列。

二分查找

将待查找的序列分成已排序和未排序两部分,每次从未排序部分取中间元素与已排序部分进行比较,如果中间元 素大于已排序部分的最大值,则未排序部分中大于中间元素的部分不需要再考虑;如果中间元素小于已排序部分 的最大值,则未排序部分中小于中间元素的部分不需要再考虑。

算法框图的基本结构及设计

Libero开发流程基础_063009

Actel FPGA Libero开发流程(基础)关于Actel成立于1985年非易失性FPGA领导企业反熔丝和闪存技术2007年收益达到1.97亿美元拥有1.45亿现金和投资无债务连续72季实现预计(pro-forma)利润率 拥有550多名员工全球开发和支持中心在世界各地拥有3500多家客户100%符合RoHS标准要求需要的软件Actel 提供全套FPGA 开发软件Libero,包含Viewdraw图形输入Verilog HDL /VHDL 输入Synplify/Synplify pro 综合Designer 布局布线ModelSim AE 仿真全套软件免费下载软件License 免费使用期限一年,满一年Actel 自动发送新的License 到你的注册邮箱需要的软件(续)to: 需要的软件(续)点击客户入门,new User需要的软件(续) 给出你的信箱--Submit需要的软件(续) 完成该表格--Submit需要的软件(续)这样你就可以进行免费License 申请需要的软件(续) 申请免费License需要的软件(续) 选择一年免费Gold 。

需要的软件(续)需要的软件(续)给出你的硬盘ID ---Submit到C: dir..C868-6CBA…几分钟后你会收到license需要的软件(续)需要的软件(续)按照邮件内容设置License 即可 下载软件,顺序点击指示位置需要的软件(续)下载两个文件,安装LiberoIDE , 选择Gold,…, 再安装SP2需要的软件(续)需要的软件(续) 安装后的计算机桌面需要的软件(续)启动Libero8.5—help—license detail需要的软件(续)若license 设置不正确,软件会提示。

至此,软件已具备。

Actel FPGA 结构简介Actel的技的术优势出色的真正基于闪存的技术全面的低功耗特性较任何其它解决方案更为安全卓越的可靠性上电即用高集成度实现更低的总体成本可重编程和易失性Actel FPGAActel FPGA 技术:Flash: Flash 开关Antifuse: 反熔丝 目前产品系列FusionIGLOO\e\plusProASIC3\EProASIC PLUSAxceleratorA54SXAeXA54SXFPGA ChipRAM/FIFOCharge Pumps Pro I/OVersaTileFROM NVM JTAG ISPISP AES DecryptionPLL/CCC VersaNets设计Libero开发流程(基础)Libero Demo 设计该设计包含下列模块/单元: •1 PLL锁相环•2 两个计数器count1,count2 •1 个或门产生异步复位 •Clock 和Reset 输入•3 LED 驱动输出Libero开发流程(基础)-创建新项目-创建Count1/PLL 模块-创建Count2模块-创建顶层模块-功能仿真-使用Synplify综合-布局布线-编程设计框图Step 1 –创建新项目Libero_demo 选择Project—New Project创建新项目Libero_demo(续)键入项目名,项目位置,选择使用的语言,所有设计存储于所选位置,以项目名字为目录的子目录下,--选择下一步创建新项目Libero_demo(续)选择系列,门数和封装,并选择完成,得到右边创建锁相环PLL 分频或倍频选择右边Catalog—clock & management—PLL static-双击鼠标右健,如下图,选择相应项创建锁相环PLL 分频或倍频创建锁相环PLL 分频或倍频红色下划线数字是你真正得到的频率和相位,我们得到0.75Mhz 的时钟,选择产生,得到如下,输入pll1,--OK创建锁相环PLL 分频或倍频可以看到已产生pll1 和使用的资源报告产生计数器count1如同锁相环产生分频,选择Catalog—Basic blocks—counter—双击鼠标右健接着产生计数器如图选择实现方式,宽度,清零等,最后产生接着产生计数器可以看到有两个模块产生Count2 的产生下面我们通过HDL 编辑器产生第二个计数器,点击HDL Editer, 如下图Count2 的产生我们给文件名count2, 注意文件名和模块名可以不一致,一个文件可以包含多个模块Count2 的产生在文本编辑器里完成如图输入,击鼠标右健给予语法检查顶层模块top到目前,我们已建立了两个计数器,一个PLL 分频模块,我们需要在顶层用这些建立设计用建立计数器count2同样的方法建立top文件内容如下:module top(input CLOCK, input RESET,output[2:0] q);wire tb_clka;wire tb_aclr;wire tb_lock,tb_gla;wire [17:0]tb_q;assign tb_aclr=(~tb_lock)| RESET;/*********** pll1, counter1, counter2 instantiations *********/pll1 p1(.POWERDOWN(1),.CLKA(CLOCK),.LOCK(tb_lock),.GLA(tb_gla));count1 c1(.Aclr(tb_aclr),.Clock(tb_gla),.Q(tb_q));count2 c2(.aclr(tb_aclr),.clock(tb_q[17]),.Q(q));endmodule问题:我怎么知道PLL1和count1 模块的信号名?答案:打开相应生成的HDL 文件,Copy 模块端口即可顶层模块Libero并不知道顶层是那个模块,你需要如下设置仿真设计需要输入,这些输入在testbench模块里生成。

RF电路与测试

1710MHz--l785MHz 1805MHz—1880MHz

双工频率间隔:

45MHz,载波间隔:200kHz

95MHz

每载波时隙数:

8(当前全速率)/16(今后半速率)

8(当前全速率)/16(今后半速率)

每帧长度:

4.615ms,每时隙长:577μs

4.615ms,每时隙长:577μs

传输速率:

4, 对于直接变化的线性接收机,解调用的本振

VCO

信号由射频VCO产生经过分频、移相处理得到。

不论那种解调电路,输出的都是基带信号RXI/Q. GSM的基带信号频率为 67.707KHz。CDMA基带频率为615KHz。

接收机单元—电路结构

无线接收机有两大类: 外差式接收机;直接变化的接收机。

多数的移动通讯设备的接收机都是采用超外差(Super-Heterodyne)的接收机, 其关键部件为“下变频器”--通常所指的“接收混频器”,可以根据混频单元来区 分:超外差一次变频接收机、超外差二次变频接收机。

接收机中AGC的作用是:当天线端的RF信号电平在大范围内变化时,保证 I/Q输出信号的电平基本不变;在监听时隙探测相邻小区基站的下行广播信 号强度,配合完成越区切换功能。

接收机单元—天线电路

Antenna: 天线电路:

把电路中的高频信号与空中高频电磁波信号进行转换. 分离接收、发射射频信号,使接收、发射信号到各自目标电路去。

GSM 1st Mixer LNA

AGC

RX 1st IF SAW

AMP

AGC

2nd Mixer

RX 2nd IF SAW

AMP AGC

I/Q正交 解调器

IP OUT IN OUT QP OUT QN OUT

手机开发流程框图

3D 模型可行性评

3D 模型修改

估 制定结构设计进度

3D 模型评估报告 结构设计进度表

计划表 详细结构设

结 构 设 计计内 部

结构设计进度表 结构设计进展

汇报 结构设计修

评审

改

结构 设计 验证 评审

制 作 working

sample

working sample

模具制作检 结构设计外部评验证

相 关讨资 料 准 结构设计修

PCB 投板

硬件

结构

硬件电路

结构尺寸

P原CB理布图板设

要求

计 PCB

GERBER 投 板 前 审

PCB 投板查

参考文件:

LCD 认证流程图:

阶段

硬件

结构

其他各部 项目需求/ 产品定义

其他各部

样品 提供

SPEC

样 品 需 尺寸

LCD 供求应商数据收集

和供选应择商提供样品

表单 表单

各部 确认

电 性 能 尺寸确认

表单 硬件需求分析报告 硬件开发计划 硬件测试计划

硬件 详细 设计

详细硬件设

内部计设计评

审 PCB 毛坯图设

计

硬件 实现 测试

PCB 布板流 投板前程 审查 硬件调试 硬件内部评 硬件审修改 评审后发布并

归档

参考文件: 1、 PCB 布板流程图 2、 LCD 认证流程图

PCB 布板流程图:

关键 器件 采购

手

机

开

发

流

程

框

图

:

阶段 项目 立项 阶段

项目 总体 规划

流程图

市场信息反馈

任命项目经理 成立项目团队小

软件定制开发单模板

材料费

开发周期

注:

回复日期:

收到此回复后5个工作日内事业部没有收到相关确认的,事业部视为本次申请自动放弃,如有需求请另行提交相关需求单。

付款方式:计入大区成本。

委托方负责人签字:

日期:

项目起止日期:年月日至年月日 Nhomakorabea承接部门

技术支持部

研发负责人

备注

填表说明:

1、

2、研发内容:注明用户需求的可满足项和不满足项目。

3、研发负责人:负责对软件定制开发需求的开发单批准、软件定制开发项目成本确认。

软件定制开发单

编号:

所属大区:

□直营

申请单位名称

申请日期

人

项目名称

用户单位名称

申请日期

人

软件定制开发范围

□常规□一线□二线□研发院□OEM厂商

软件名称

软件版本/型号

(如有前置机需注明前置机版本及自身版本)

用户系统需求详细描述:

1、现有系统界面,要修改的功能的截图(用红色标注出要修改的内容)。

2、新增的功能,注明新增的功能名称,提供设计图(用红色标注出要修改的内容);无法提供图片的,请按以下要求提供详细需求描述:

1)要做的功能名称。

2)要做的功能目标、范围。

3)要实现的功能流程框图。

4)要实现的功能流程说明。

3、接口对接提供接口附件。

个性化答复

预算管理员意见

研发人员

研发内容

软件定制开发类型

□“0”系统定制开发□部分定制开发

能否纳入产品

纳入到产品的功能列表

能否纳入工程项目

工程项目计划截至日期

初次下单

上次单号

研发费用

嵌入式软件开发流程

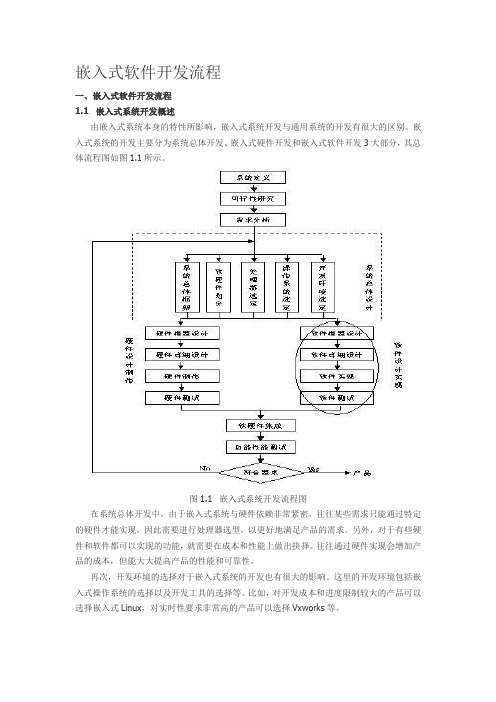

嵌入式软件开发流程一、嵌入式软件开发流程1.1 嵌入式系统开发概述由嵌入式系统本身的特性所影响,嵌入式系统开发与通用系统的开发有很大的区别。

嵌入式系统的开发主要分为系统总体开发、嵌入式硬件开发和嵌入式软件开发3大部分,其总体流程图如图1.1所示。

图1.1 嵌入式系统开发流程图在系统总体开发中,由于嵌入式系统与硬件依赖非常紧密,往往某些需求只能通过特定的硬件才能实现,因此需要进行处理器选型,以更好地满足产品的需求。

另外,对于有些硬件和软件都可以实现的功能,就需要在成本和性能上做出抉择。

往往通过硬件实现会增加产品的成本,但能大大提高产品的性能和可靠性。

再次,开发环境的选择对于嵌入式系统的开发也有很大的影响。

这里的开发环境包括嵌入式操作系统的选择以及开发工具的选择等。

比如,对开发成本和进度限制较大的产品可以选择嵌入式Linux,对实时性要求非常高的产品可以选择Vxworks等。

1.2 嵌入式软件开发概述嵌入式软件开发总体流程为图4.15中“软件设计实现”部分所示,它同通用计算机软件开发一样,分为需求分析、软件概要设计、软件详细设计、软件实现和软件测试。

其中嵌入式软件需求分析与硬件的需求分析合二为一,故没有分开画出。

由于在嵌入式软件开发的工具非常多,为了更好地帮助读者选择开发工具,下面首先对嵌入式软件开发过程中所使用的工具做一简单归纳。

嵌入式软件的开发工具根据不同的开发过程而划分,比如在需求分析阶段,可以选择IBM的Rational Rose等软件,而在程序开发阶段可以采用CodeWarrior(下面要介绍的ADS 的一个工具)等,在调试阶段所用的Multi-ICE等。

同时,不同的嵌入式操作系统往往会有配套的开发工具,比如Vxworks有集成开发环境Tornado,WindowsCE的集成开发环境WindowsCE Platform等。

此外,不同的处理器可能还有对应的开发工具,比如ARM的常用集成开发工具ADS、IAR和RealView等。

android开发计算器设计开发报告

a n d r o i d开发计算器设计开发报告Revised by Petrel at 2021《安卓开发》程序设计报告题目简单计算器开发专业(班级)网工111班姓名张波波学号指导教师赵(老师)日期2014.5.7目录一、设计说明: (4)1.设计内容:Android简单应用程序开发,简单计算器。

(4)2程序说明: (4)二、开发环境: (4)三、概要设计: (4)3.1系统的总体 (4)四、程序流程和系统功能设计 (5)4.1程序流程设计 (5)4.2.系统功能设计 (6)4.3基于Android平台系统具体设计 (6)4.3.1总体模块详细设计 (6)4.3.2输入模块详细设计 (6)4.3.3显示模块详细设计 (7)4.3.4计算模块详细设计 (7)五、计算器系统实现 (8)5.1Android应用程序构成 (8)六、截图说明 (9)1、图标 (9)2界面 (9)3运算界面 (9)4错误输入 (9)5设计平台界面 (9)6签名导出apk (9)七、总结 (9)课程设计任务书一、设计说明:1.设计内容:Android简单应用程序开发,简单计算器。

2程序说明:1、计算器界面友好,方便使用。

2、具有基本的加、减、乘、除功能,还有+—、开方、平方功能。

3、能够判断用户输入运算数是否正确。

4、4、支持小数运算。

5、具有退格功能,能够删除最后一个输入,ce。

6、具有清除功能,删除所有,c。

7、具有结果存储功能,能够显示存储器状态,支持触屏手机。

8、9、支持最低版本2.0,最高版本4.4。

开发时为4.2二、开发环境:开发环境:本系统是采用Eclipse+EclipseMe+JDK+ADT作为开发平台。

事实上为了节约时间就直接用Google公司安给的直接绑定好的adt-bundle-windows-x86_64开发,只需要配置下环境变量,无需要关联等操作。

三、概要设计:3.1系统的总体整个程序基于android技术开发,出总体模块外主要分为输入模块、显示模块以及计算模块(包括一些其她功能)这三大部分。

嵌入式软件开发流程

嵌入式软件开发流程一、嵌入式软件开发流程1.1 嵌入式系统开发概述由嵌入式系统本身的特性所影响,嵌入式系统开发与通用系统的开发有很大的区别。

嵌入式系统的开发主要分为系统总体开发、嵌入式硬件开发和嵌入式软件开发3大部分,其总体流程图如图1.1所示。

图1.1 嵌入式系统开发流程图在系统总体开发中,由于嵌入式系统与硬件依赖非常紧密,往往某些需求只能通过特定的硬件才能实现,因此需要进行处理器选型,以更好地满足产品的需求。

另外,对于有些硬件和软件都可以实现的功能,就需要在成本和性能上做出抉择。

往往通过硬件实现会增加产品的成品,但能大大提高产品的性能和可靠性。

再次,开发环境的选择对于嵌入式系统的开发也有很大的影响。

这里的开发环境包括嵌入式操作系统的选择以及开发工具的选择等。

本书在4.1.5节对各种不同的嵌入式操作系统进行了比较,读者可以以此为依据进行相关的选择。

比如,对开发成本和进度限制较大的产品可以选择嵌入式Linux,对实时性要求非常高的产品可以选择Vxworks等。

由于本书主要讨论嵌入式软件的应用开发,因此对硬件开发不做详细讲解,而主要讨论嵌入式软件开发的流程。

1.2 嵌入式软件开发概述嵌入式软件开发总体流程为图4.15中“软件设计实现”部分所示,它同通用计算机软件开发一样,分为需求分析、软件概要设计、软件详细设计、软件实现和软件测试。

其中嵌入式软件需求分析与硬件的需求分析合二为一,故没有分开画出。

由于在嵌入式软件开发的工具非常多,为了更好地帮助读者选择开发工具,下面首先对嵌入式软件开发过程中所使用的工具做一简单归纳。

嵌入式软件的开发工具根据不同的开发过程而划分,比如在需求分析阶段,可以选择IBM的Rational Rose等软件,而在程序开发阶段可以采用CodeWarrior(下面要介绍的ADS 的一个工具)等,在调试阶段所用的Multi-ICE等。

同时,不同的嵌入式操作系统往往会有配套的开发工具,比如Vxworks有集成开发环境Tornado,WindowsCE的集成开发环境WindowsCE Platform等。

基于WiFi的智能LED照明控制系统的设计

基于WiFi的智能LED照明控制系统的设计引言随着互联网技术的不断发展,智能家居的出现为人们享受生活提供了一个广阔的平台。

无线传输技术被广泛应用到具有远程控制功能的智能LED照明系统中,通过手机APP远程控制终端设备的应用越来越多。

目前,主流的无线传输技术主要有NRF905或者NRF2401等短距离无线通信、Zigbee技术、蓝牙、GSM和WiFi等。

WiFi技术具有速度快、可靠性高的特点,可以方便组建网络,对于普通的家庭照明控制,它是实现无线智能照明系统的较好的解决方案[1,2]。

设计一个基于WiFi的智能LED 照明控制系统,实现移动终端远程控制智能家居中的LED灯,具有很好的市场应用价值。

1 系统设计系统设计主要分为三个部分:手机客户端、服务器和基于WiFi的无线模块客户端。

1)手机客户端:编写一个手机APP程序,通过TCP/IP协议连接到Internet网络;设计UI界面,设计人性化交互操作界面,通过APP程序发送数据给服务器。

2)服务器:接收手机客户端发送来的数据,对发送来的数据进行存储,然后将手机客户端发送来的数据发送给基于WiFi的无线模块客户端。

3)基于WiFi的无线模块客户端:根据设计要求,基于WiFi的无线模块选用HF-LPB100WiFi模块,采用Cortex-M3内核的ARM作为主控芯片,控制WiFi模块。

通过TCP/IP协议连接服务器,然后接收手机客户端发送来的数据,识别后通过控制继电器来实现控制LED的通断、色度和亮度[3],系统总体设计如图1所示。

图1 系统框图Fig.1 Diagram of system block2 硬件电路设计1)LED电路。

为了实现LED的色度控制,选用RGB红绿蓝七彩色LED 灯珠,控制器的P2口接地控制所有LED的通断,P1口控制蓝色LED,P3口控制绿色LED,P4口控制红色LED。

通过P1、P3和P4三原色合成七种颜色,设计中通过一个GPIO和三个PWM可实现控制整个LED输出不同的颜色和亮度。

13-J2ME-Java程序设计与实践教程(第2版)-杨丽萍-清华大学出版社

Java程序设计与实践教程—清华大学出版社

当startApp()方法被调用的时候 MIDlet进入active状态, 即运行状态。

在 active状态调用 destroyApp(boolean unconditional) 或pauseApp()方法可以使得 MIDlet进入destroyed或者 pause状态。

destroyApp(boolean unconditional)方法被调用时, AMS通知 MIDlet进入destroyed状态。

MIDlet三个状态:pause、active和 destroyed

Java程序设计与实践教程—清华大学出版社

13.1.2 MIDlet程序的生命周期

图13-2 MIDlet状态图

Java程序设计与实践教程—清华大学出版社

13.1.2 MIDlet程序的生命周期

启动MIDlet时,应用管理软件会先创建一个MIDlet实例并 使其处于pause状态

Java程序设计与实践教程—清华大学出版社

13.1.1 J2ME简介

2.J2ME体系结构

Java虚拟机 配置层(CLDC或CDC) 简表(MIDP)

图13-1 J2ME体系结构框图

Java程序设计与实践教程—清华大学出版社

13.1.1 J2ME简介

2.J2ME体系结构 KVM (Kilobyte virtual machine ):J2ME应用程序虚拟机 配置层(CLDC或CDC):KVM和Java类库的最小集合。 CLDC(Connected Limited Devices Configuration,有限连 接设备配置):第一个面向小型设备的Java应用开发规范, J2ME核心配置之一,可支持一个或多个profile。其目标为面向 小型的、网络连接速度慢、能源有限且资源有限的设备,如手 机,PDA等。 CDC(Connected Devices Configuration,连接设备配置): 主要用于运算能力相对较佳、电力供应相对充足的嵌入式装置 (如冷气机、电冰箱、电视机机顶盒)。 移动信息设备简表MIDP(Mobile Information Device Profile): 定义于CLDC上层, 补充了CLDC配置,并且提供应用程序语义和控 件、用户界面、持久存储器、网络和用于移动电话的计时器、双 通道呼叫器和其他无线电设备。MIDP应用程序被叫做MIDlet,所 有的MIDlet都包含扩展类javax.Microedition.midlet的主要类。

基于手机APP的闸机远程控制系统设计

基于手机APP的闸机远程控制系统设计刘虹羚【期刊名称】《《电子世界》》【年(卷),期】2019(000)022【总页数】2页(P149-150)【作者】刘虹羚【作者单位】南京科技职业学院电气与控制学院【正文语种】中文本系统用于自动检票机设备,主要实现自动检票机的远程控制和状态数据的获取与分析。

系统包括闸机通道控制器模块,闸机主控单元模块和闸机监控器模块。

系统设计的核心是闸机监控器模块,分为硬件设计和软件设计两个方面。

闸机监控器能够与闸机主控单元实现通讯,获取设备故障信息、报警信息、工作信息等状态数据,并通过GPRS模块将状态数据上传到云端服务器,进行数据的分析与统计。

手机APP应用软件,能够对闸机数据进行获取和显示,并且可以对闸机进行远程操作。

引言:自动检票机,也称闸机,是一种智能通道管理设备,用于管理不同身份人员的通行,可应用于写字楼、景区、地铁、学校、工厂等场所。

闸机设备最基本的功能是实现身份验证(或支付),并对通过授权的人员进行放行,适用于各种收费、门禁场合的出入口通道处。

目前,国内外市场上的闸机能通过有线网将设备内的数据信息与后台服务器进行交互,工作人员需要通过管理计算机对闸机进行远程控制与管理,但是无法让现场管理员在本地方便地对闸机设备进行实时的设置、状态监测和远程控制,这给本地现场的设备管理工作带来了一定的难度。

本文介绍的基于手机APP的闸机远程控制系统,本地管理员可以通过手机APP对闸机进行远程控制和状态监测,闸机监控器可以将闸机数据与后台云端联网,实现设备的预测性维护以及全生命周期管理。

本文在系统总体设计基础上,重点研究了闸机监控器子系统的设计,包括硬件设计和软件设计两个部分。

1 系统总体设计整个闸机控制系统结构如图1所示,主要包含工控机、通道控制器、通道传感器、伺服控制器、闸机监控器等。

工控机是闸机的主控单元,与读卡器、人脸识别器、二维码扫描器等身份验证模块连接,实现对票卡、人员、或二维码的有效性验证,并将验证结果,发送给通道控制器。

PSoC开发流程和一般MCU开发流程有什么区别?

PSoC开发流程和一般MCU开发流程有什么区别?低调的华丽——PSoC 6 BLE Pioneer Kit 评测系列之二前言老子有云:大音希声,大象无形。

低调而不失张扬,这是笔者初见PSoC 6 BLE Pioneer 时的感受。

虽然早已在媒体介绍上见过PSoC 6 BLE Pioneer的宣传照片,但是第一次看到PSoC 6 BLE Pioneer摆在面前,还是小小的惊喜了一下。

PSoC 6 BLE Pioneer无论在设计还是包装,到软件开发等方面,都为我们带来了更好的体验!PSoC是Cypress推出的可编程片上系统,2002年推出第一款商用产品PSoC 1,十几年来不断推陈出新,今天的PSoC 6系列,可谓是PSoC产品的集大成者。

硬件内核也从最初的M8C演变到了今天的ARM Cortex-M4,PSoC 63则使用了双核,即包含ARM Cortex-M4及ARM Cortex-M0 。

PSoC 6 BLE Pioneer套件还为我们带来了CapSense电容触控和最新的BLE 5及USB Type-C的全新体验,加上一块2.7吋的墨水屏,配合PSoC 6的业内最低功耗特性,配置不可谓不华丽。

先简单科普下PSoC。

PSoC的全称是Programmable System-on-Chip,即可编程片上系统或可编程片上芯片。

PSoC一般由内核、可配置的模拟及数字模块以及可编程的互联线路组成。

与FPGA相比,二者都需要在上电时对设备进行配置,不同的是PSoC通过从内置闪存中加载指令来进行配置。

可配置模块是PSoC与其它微控制器最大的区别。

开箱与PSoC 4 Pioneer Kit不同的是,PSoC 6 BLE Pioneer套件中还配备了墨水屏,所以体积也大了许多,看上去倒像是个手机盒子。

PSoC 6 BLE Pioneer的目标很明确,面向IoT应用,主打低功耗、灵活配置及内置安全功能,不过以文无第一,武无第二的角度来看,Cypress此次显得非常自信,宣称是自己是最低功耗的领导者。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硬件 实现 测试

手机开发流程框图

PCB 布板流程 投板前审查

硬件调试 硬件内部评审

硬件修改 评审后发布并归档

软件 打样、试产

PCB 贴片 整机测试

PCB 数据 器件规格书 硬件子系统软件 装配图 硬件单元测试分析报告 电装总结报告 硬件系统测试版本 硬件系统测试分析报告 硬件评审验证报告 发布版本

手机开发流程框图

手机开发流程框图:

阶段 项目 立项 阶段 项目 总体 规划

设计 阶段

设 计 T1 验

流程图

市场信息反馈

任命项目经理 成立项目团队小组

项目建议书 可行性分析

签发项目任务书

需求分析评审

各部需求分析

产品定义

系统分析

确定里程碑 编制质量控制计划

编制项目计划书 风险控制计划

系统分析评审

软件 软设件 计

开模

参考文件: 《工业设计流程》,《ID 设计流程》 附录 2. 软件设计流程图:

阶段

软件 需求 分析

软件 详细 设计

流程图

软件需求分析(包括技术风险评估)

软件开发计划和配置管理计划 进度计划表 软件测试计划

详细软件设计

内部设计评审

表单

软件需求规格书 软件开发计划 软件开发风险控制计划 软件测试计划

软件详细设计说明书 软件接口设计说明书 软件设计内部评审记录

软件 实现 测试

手机开发流程框图

编码调试 单元测试 软件集成/调试 发布系统测试版本 软件修订 评审后发布并归档

编写测试用例 软件系统测试

单元源代码 单元调试报告 单元测试用例 单元测试分析报告 集成后的软件及源代码 软件集成调试报告 软件操作手册 系统测试软件 系统测试用软件文档 软件系统测试分析报告 发布版本

阶段

硬件

结构

样品 提供

SPEC

样品需求

尺寸

LCD 供应商数据收集和选择

供应商提供样品

其他各部

各部 确认

电性能 SPEC

尺寸确认

各部提出修改要求

与供应商沟通 SPEC 供应商供样

软件确认

各部确认

装机

是

否

是否通过

装机验证 封样

表单

参考文件:

流程

硬件 PCB 设计 流程

结构设计及 制作流T程1 图

评审,过程文件归档

工艺 工艺说明 T1 设计

流程

装机准备

少量装机

例试报告及分析 装机报告

整机测试及评估

文档

可行性分析报告 项目任务书

需求分析报告 需求分析评审报告 产品定义 产品技术规范 项目开发计划 风险控制计划 质量控制计划 系统分析文档

产品技术总体设计方案 (包括工艺) 系统分析评审报告 软件设计过程文档 硬件设计过程文档 结构设计过程文档 工艺设计过程文档 软件 PCB T1 设计文档 工艺说明 分单元测试报告

参考文件:

附录 3. 硬件设计流程图:

阶段

硬件 需求 评估

硬件 详细 设计

流程图

硬件需求分析(包括技术风险评估)

硬件开发计划和配置管理计划 进度计划表 硬件测试计划键器 件采购

LCD 认 证流程

表单

硬件需求分析报告 硬件开发计划 硬件测试计划

硬件详细设计说明书 硬件电路原理图 硬件 BOM 硬件设计内部评审记录

CTA 手工下单

例试、整机测试评估 量封产样版本确定

软硬件结 构及工艺 调整 生产工版艺本准升备级

全套文件归档

量产

量产转移

转移

附录:1、结构设计及制作流程图

2、软件设计流程图

3、硬件设计流程图

附录 1. 结构设计及制作流程图:

T2 设计文档 试产报告 例试分析报告 整机测试评估报告 软件 CTA 版本 硬件 CTA 版本

装机报告 例试分析报告 整机测试评估报告 软件 FTA 版本 硬件 FTA 版本

FTA 准备

修模

软硬件及工艺调整 版本升级

手机开发流程框图

证 T2

阶 FTA

段

FTA

CTA 材 料 下单

T3

CTA 准备

小批量试产

试产准备

例试、整机测试及评估

软硬件及 工艺调整

版本升级

修模

第二次试产

试产准备

CTA

量产 准备 阶段

结构 设计 验证 评审

制作 working sample

working sample 验证

模具制作检讨

结构设计外部评审

相关资料准备 结构设计修改

签订商务合同

结构设计内部评审记录 workingsample 配色表 workingsample 验收报告 结构 BOM 结构设计外部评审记录 模具制作检讨记录表 模具制作申请表 模具备品清单 模具制作注意事项表 工装夹具制作清单 物料进度按排需求表 配色方案表 模具制作进度表

参考文件: 1、 PCB 布板流程图 2、 LCD 认证流程图

PCB 布板流程图:

阶段 布板 需求 设计

PCB 确认

硬件

硬件电路原理 图 PCB 布板设计

结构

结构尺寸要求

PCB GERBER 投板前审查

PCB 投板

PCB 投板

其他各部

项目需求/产 品定义

表单

手机开发流程框图

参考文件:

LCD 认证流程图:

T3 设计文档 试产报告 例试分析报告 整机测试评估报告

全套 DVT 报告 工艺文件

阶段 结构 可行 评估 结构 详细 设计

流程图

3D 模型可行性评估

3D 模型修改

表单

3D 模型评估报告 结构设计进度表

制定结构设计进度计划表 详细结构设计

结构设计进展汇报

结构设计进度表

结构设计内部评审

结构设计修改

手机开发流程框图