基于VHDL的可控脉冲发声器 设计

一种脉冲控制的可变频率脉冲声发生器设计

路 和 功率放 大 电路 三部 分 。其 总体 的构造 图如 图 l

所示 。

的脉冲声信号而且还可实现 的控 制 。

2 设 计 思路 与原 理

笔者 的主要思路是 利用一脉 冲控制矩形波产生 电

21 矩 形 波产 生原 理 .

其采用基本 的触发脉冲发生器 ,触发脉 冲就是指 具有一定 自动动作的 电路处于静止 时 。为使该 电路动

垒 篓 型 蔓堂 国 查 曼 蔓 生

作 所 施 加 的 脉 冲 。触 发 脉 冲 的作 用 是产 生 和分 配 触 发 脉 冲 具体 发声 装 置 由一 片 5 5 时 器 和 一 个 R 。 5定 C正

X E Sa-a U h ojn

( o e e o f m t n a d C m u i t n E g e r g ot nv r t o hn ,T iu n 0 0 5 ,C ia C l g fI o ai n o m n ai n i e n ,N r U i s y fC ia a a 3 0 1 hn ) l n r o c o n i h e i y

该 设 计 主 要 包 括 矩 形 波 产 生 电路 、 弦 波 产 生 电 正

和现场吸声测量 中回 脉冲声的产生方法多种多样 , 。 如传 统方法 中使用模拟信号如气球 、 发令枪 、 电火 花式 脉冲 声源, 现代方法 中使用计算机产生数字信号 , 通过扬声 器发 出的可控波形脉冲声发生器1 但这些装 置也存在 3 ] 。 很多不便之处 , 如电火花式声源频率不单一 , 以应用 难 于频率单一的环境 中 .可控波形脉冲声发生器装置过 于繁琐笨重 , 不利 于携带等 。 笔者研究 了一 种低频 范围的脉 冲声 生成技术 , 介 绍了其工作原理和声源设计方案。制作 了一 种方便 携 带、 性价 比高 的脉冲声源。 该声源不仅能发 出频率单一

VHDL语言蜂鸣器

蜂鸣器输出报警声实验一.实验目的学习交流蜂鸣器的发音原理。

二.实验内容在SmartSOPC实验箱上的蜂鸣器输出报警笛声。

三.实验原理SmartSOPC实验箱上有1个交流蜂鸣器BUZZER,通过跳线JP6的BEEP与芯片相连接。

为了增强I/O口的驱动能力,在此采用了PNP型三极管,这样只要在BEEP上输入一定频率的脉冲蜂鸣器就会发出音乐。

四.实验程序实验源程序如下:Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity aa isPort( clk:in std_logic;beep:out std_logic);end aa;Architecture m1 of aa issignal beep_r:std_logic;signal count:std_logic_vector(15 downto 0);beginbeep<=beep_r;process(clk)beginif clk'event and clk='1' thencount<=count+'1';end if;end process;process(count(15))beginbeep_r<=not beep_r ;end process;end m1;五.实验步骤(1)、在QuartusII中建立一个工程项目文件beep.qpf,并在该项目下新建VHDL源程序文件输入源程序代码并保存。

(2)、选择目标器件并对相应的引脚进行锁定,在这里在这里所选择的目标器件为Altera 公司Cyclone系列的EP1C12Q240C8芯片,引脚锁定的方法如表6.1,将未使用的管脚设置为三态输入。

表1 引脚锁定方法信号引脚信号引脚1C6 1C12 EDA 1C6 1C12 EDA beep 175 175 175 clk 28 28 28(3)、对该工程文件进行全程编译处理,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

基于VHDL可编程m序列发生器的设计及应用

m 序列 广泛应 用 于数字基 带信 号进行 加扰 , 改 善 数字 序列 的位 定 时质 量 与 帧 同步 和 自适 应 时 域 均 衡性 能 , 同时 也是 构 造 平衡 G L O D码 的基 础 . 目 前 , 序 列产 生 电路 的实 现方 法主要 有 3种 : i n 1 )门电路实 现 . 方法设 计简 单 , 随移位 寄 该 但 存 器级 数 的增长 , 电路 装 调 困难 , 占用 的 印制 板 且

计输 入 、 速处 理和器 件编 程 引. 快

线 性反 馈移 位寄存 器 的特征 多项 式 :

摘要 : 介绍 了在 实 际教 学 中应 用 V L设计 出一 种能产 生 1 序 列数 字信 号 的发 生 器. HD T I 该序 列发 生 器具 有序 列长 度 和反 馈 连 接 设 置 , 能产 生 多种 i 列 波形 的 特 点. 软 件 上 采 用 Ata公 司 的 n序 在 lr e

种 序列 . 在今 天 的数 字 信 号 的传 输 中 , 发送 机往

往要 加扰码 器 , 对应 的接 收 端要 加 解 扰器 , n 相 而 l

序列 属 于伪 噪声 序列 和 伪 随 机序 列 , 容 易产 生 、 它

规律 性强 、 很 好 的 自相 关 性 和 较 好 的互 相 关 特 有

一

2 S 程实现 . )D P编 该方 法专 业性 过强 , 适合 不

实际教 学 中应 用. 3 H L与 C L )V D P D实现 . 由于 C L P D的高 集成

度, 而且 V L语 言 编程 较 为 方便 , 可 以大 大减 HD 故

少 电路 的装调 的 困难.

V D H L已成 为 电子工 程 领 域 事实 上 的 通 用硬

vhdl实验报告--蜂鸣器

vhdl实验报告--蜂鸣器VHDL 实验报告蜂鸣器一、实验目的本次实验的主要目的是通过使用 VHDL 语言来设计并实现一个蜂鸣器的控制电路,深入理解数字电路的设计原理和 VHDL 编程的基本方法,掌握硬件描述语言在实际电路设计中的应用,提高自己的逻辑思维和问题解决能力。

二、实验原理蜂鸣器是一种一体化结构的电子讯响器,采用直流电压供电。

常见的蜂鸣器分为有源蜂鸣器和无源蜂鸣器两种。

有源蜂鸣器内部自带了振荡源,只要给其供电就能发出固定频率的声音;无源蜂鸣器则需要外部提供一定频率的脉冲信号才能发声。

在本实验中,我们使用 VHDL 语言来控制一个无源蜂鸣器。

通过编写代码,生成特定频率的脉冲信号,从而驱动蜂鸣器发声。

三、实验设备及工具1、计算机2、 Quartus II 软件3、开发板四、实验内容及步骤1、设计思路首先,需要确定蜂鸣器发声的频率。

通过计算得出所需的时钟周期数。

然后,使用计数器来产生特定频率的脉冲信号。

最后,将脉冲信号输出到蜂鸣器的控制引脚。

2、 VHDL 代码编写```vhdllibrary ieee;use ieeestd_logic_1164all;use ieeenumeric_stdall;entity buzzer_control isport(clk : in std_logic;rst : in std_logic;buzzer : out std_logic);end entity;architecture Behavioral of buzzer_control isconstant CLK_FREQ : integer := 50_000_000; 系统时钟频率constant BUZZER_FREQ : integer := 1000; 蜂鸣器发声频率signal counter : integer range 0 to CLK_FREQ/BUZZER_FREQ 1; signal clk_div : std_logic;beginprocess(clk, rst)beginif rst ='1' thencounter <= 0;clk_div <='0';elsif rising_edge(clk) thenif counter = CLK_FREQ/BUZZER_FREQ 1 thencounter <= 0;clk_div <= not clk_div;elsecounter <= counter + 1;end if;end if;end process;buzzer <= clk_div;end architecture;```3、编译与仿真将编写好的 VHDL 代码在 Quartus II 软件中进行编译。

VHDL音频发生器课程设计

VHDL音频发生器课程设计一、课程目标知识目标:1. 学生能理解VHDL语言的基本语法和结构,掌握利用VHDL进行数字电路设计的基本方法。

2. 学生能掌握音频发生器的原理,了解其工作流程及组成结构。

3. 学生能运用VHDL语言编写程序,实现一个简易的音频发生器。

技能目标:1. 学生能够运用所学知识,使用VHDL设计并实现音频发生器,提高实际操作能力。

2. 学生通过课程学习,培养解决实际问题的能力,学会查阅资料、分析问题、设计方案、调试程序等过程。

情感态度价值观目标:1. 学生在学习过程中,培养对电子设计、编程的兴趣和热情,提高创新意识和团队协作精神。

2. 学生能够认识到电子技术在现实生活中的应用,增强对科技发展的关注,培养社会责任感和使命感。

本课程针对高中年级学生,结合电子技术课程内容,以VHDL语言为基础,设计一个音频发生器。

课程性质为实践性、综合性,注重培养学生的动手能力和实际问题解决能力。

在教学过程中,要求教师引导学生积极参与,注重启发式教学,鼓励学生提出问题、解决问题,从而实现课程目标。

通过本课程的学习,学生能够达到以上所述的知识、技能和情感态度价值观目标,为后续相关课程学习打下坚实基础。

二、教学内容本课程教学内容主要包括以下几部分:1. VHDL语言基础:讲解VHDL的基本语法、数据类型、运算符、信号与变量等,对应教材第1章内容。

2. 数字电路设计原理:介绍数字电路设计的基本概念、原理和方法,重点讲解时钟信号、触发器、计数器等基本电路,对应教材第2章内容。

3. 音频发生器原理:分析音频发生器的工作原理、组成结构以及关键参数,对应教材第3章内容。

4. VHDL程序设计:结合实际案例,教授如何利用VHDL语言编写程序,实现数字电路的设计,对应教材第4章内容。

5. 音频发生器设计与实现:引导学生运用所学知识,设计并实现一个简易的音频发生器,包括程序编写、调试与优化等,对应教材第5章内容。

6. 实践操作与总结:安排学生进行实践操作,培养动手能力,并对设计过程中遇到的问题进行总结和分析,提高解决问题能力。

课程设计(论文)基于vhdl的简易乐曲演奏器的设计

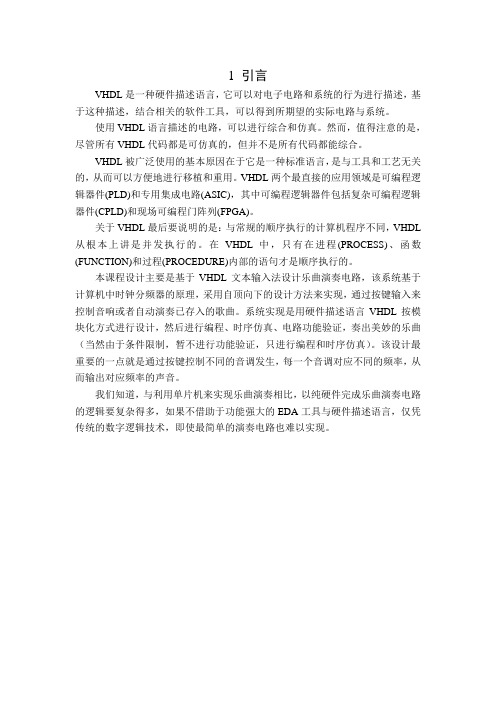

1 引言VHDL是一种硬件描述语言,它可以对电子电路和系统的行为进行描述,基于这种描述,结合相关的软件工具,可以得到所期望的实际电路与系统。

使用VHDL语言描述的电路,可以进行综合和仿真。

然而,值得注意的是,尽管所有VHDL代码都是可仿真的,但并不是所有代码都能综合。

VHDL被广泛使用的基本原因在于它是一种标准语言,是与工具和工艺无关的,从而可以方便地进行移植和重用。

VHDL两个最直接的应用领域是可编程逻辑器件(PLD)和专用集成电路(ASIC),其中可编程逻辑器件包括复杂可编程逻辑器件(CPLD)和现场可编程门阵列(FPGA)。

关于VHDL最后要说明的是:与常规的顺序执行的计算机程序不同,VHDL 从根本上讲是并发执行的。

在VHDL中,只有在进程(PROCESS)、函数(FUNCTION)和过程(PROCEDURE)内部的语句才是顺序执行的。

本课程设计主要是基于VHDL文本输入法设计乐曲演奏电路,该系统基于计算机中时钟分频器的原理,采用自顶向下的设计方法来实现,通过按键输入来控制音响或者自动演奏已存入的歌曲。

系统实现是用硬件描述语言VHDL按模块化方式进行设计,然后进行编程、时序仿真、电路功能验证,奏出美妙的乐曲(当然由于条件限制,暂不进行功能验证,只进行编程和时序仿真)。

该设计最重要的一点就是通过按键控制不同的音调发生,每一个音调对应不同的频率,从而输出对应频率的声音。

我们知道,与利用单片机来实现乐曲演奏相比,以纯硬件完成乐曲演奏电路的逻辑要复杂得多,如果不借助于功能强大的EDA工具与硬件描述语言,仅凭传统的数字逻辑技术,即使最简单的演奏电路也难以实现。

2 整体功能介绍2.1准备知识在本次设计中采用了铃声《北京欢迎你》作为要播放的乐曲,它的旋律如下:3 5 3 2 3 2 3 3 2 6 1 3 2 22 1 6 1 23 5 2 3 6 5 6 2 1 12 1 6 1 23 5 2 3 6 5 5 3 -2 3 2 1 5 6 2 5 3 3 2 3 (加粗表示低音,其他为中音)根据声乐知识,组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能连续演奏所需的两个基本要素,获取这两个要素所对应的数值以及通过纯硬件的手段来利用这些数值实现所希望乐曲的演奏效果是本实验的关键。

基于VHDL的PWM信号发生器的设计论文

Yi bin University EDA技术及应用课程设计报告题目基于VHDL的PWM信号发生器系别物理与电子工程学院专业电子信息科学与技术学生姓名学号班级2013 年 12月 21日摘要本次课程设计是基于VHDL的PWM信号发生器,PWM信号发生器应用所学的数字电路和模拟电路的知识进行设计。

在设计过程中,所有电路仿真均基于Quartus II 9.1仿真软件。

本课程设计介绍了PWM 信号发生器的设计方案及其基本原理,并着重介绍了PWM信号发生器各单元电路的设计思路,原理及仿真,整体电路的的工作原理,控制器件的工作情况。

设计共有三大组成部分:一是原理电路的设计,本部分详细讲解了电路的理论实现,是关键部分;二是性能测试,这部分用于测试设计是否符合任务要求。

三是是对本次课程设计的总结。

关键词: PWM信号发生器仿真设计目录第1章绪论1.1 EDA 和QuartusⅡ的简介及起源 (1)1.2 EDA的优势及发展趋势 (1)第2章系统设计思路 (3)第3章可自加载加法计数器的设计 (4)第4章信号发生器设计过程 (6)第5章软件仿真5.1 Quartus Ⅱ软件简介 (8)5.2 用Quartus Ⅱ的仿真步骤和图像 (9)5.3 逻辑综合结果 (12)第6章设计总结 (13)第7章参考文献 (15)附录设计程序 (16)第1章绪论1.1 EDA和QuartusⅡ的简介及起源EDA是英文“electronic design automation”(电子自动化设计)的缩写,EDA技术是20世纪90年代迅速发展起来的,是现代电子设计的最新技术潮流,是综合现代电子技术和计算机技术的最新研究成果,是电子线路设计与分析的一门技术。

EDA包括电子线路的设计、计算机模拟仿真和电路分析及印制电路板的自动化设计三个方面的内容。

随着可编程逻辑器件迅速发展,出现了功能强大的全新的EDA工具。

具有较强描述能力的硬件描述语言(VHDL、Verilog、HDL)及高性能综合工具的使用,使过去单功能电子产品开发转向系统级电子产品开发。

基于 VHDL 的函数信号发生器的设计--毕业设计

长江大学工程技术学院毕业论文学院:专业班级:学号:姓名:指导教师:辅导教师:________~________学年________年____月至 ________年____月基于 VHDL 的函数信号发生器的仿真设计【摘要】数字技术和计算机技术已经广泛运用于工业、农业、医学、教育、军事、生活等各个领域,其应用之深之广令人惊叹。

电子设计自动化技术已日趋成为现代电子设计技术的核心,这种技术又称为 EDA(Electronic Design Automation)技术。

EDA 技术基于硬件描述语言 HDL。

VHDL 是 HDL 的一种,并广泛应用在电子设计中。

锯齿波、三角波、方波、正弦波等多种波形均可以从函数信号发生器中产生。

我们在电路实验中也广泛运用到函数信号发生器。

本文基于 VHDL 语言设计各个波形产生模块,然后在 QUARTUS II 软件上实现波形的编译及仿真,通过四选一数据选择器选择输出三角波、锯齿波、矩形波或正弦波中的一种规定波形,并采用调频模块和调幅模块进行调频调幅,可以产生多种波形。

【关键词】:函数信号发生器;EDA 技术;VHDL;QUARTUS II 软件目录1 基于VHDL的函数信号发生器的设计…………………………………………1.1信号发生器的发展现状……………………………………………………1.2研究信号发生器目的和意义………………………………………………1.3主要研究设计内容、关键问题及解决思路………………………………1.3.1主要研究内容…………………………………………………………1.3.2关键问题………………………………………………………………1.3.3解决思路………………………………………………………………2系统设计………………………………………………………………………2.1设计要求与任务……………………………………………………………2.2设计方案……………………………………………………………………2.3相关模块介绍………………………………………………………………2.3.1时钟脉冲与复位………………………………………………………2.3.2调频与调幅……………………………………………………………2.4相关组合对应关系…………………………………………………………3 系统仿真………………………………………………………………………3.1相关工具简介………………………………………………………………3.2波形数据产生模块…………………………………………………………3.2.1锯齿波…………………………………………………………………3.2.2三角波…………………………………………………………………3.2.3方波……………………………………………………………………3.2.4正弦波…………………………………………………………………4 调控模块………………………………………………………………………4.1波形输入控制模块…………………………………………………………4.2波形输出控制模块…………………………………………………………4.3频率控制模块………………………………………………………………4.4幅度控制模块………………………………………………………………5 结果分析………………………………………………………………………6 结论……………………………………………………………………………前言信号发生器也被称为信号源或振荡器,被广泛应用于生产实践与科学技术。

基于FPGA的脉冲型音乐播放器的设计

基于FPGA/CPLD的脉冲信号型乐曲播放器的设计摘要用纯硬件来完成乐曲演奏电路的逻辑非常复杂,仅凭传统的数字逻辑技术,即使最简单的电路也难以实现。

但是借助于功能强大的EDA工具和硬件描述语言,就可以轻松的实现设计。

本设计利用可编程逻辑器件设计一个控制器让不同频率的脉冲信号有序的输出并驱动扬声器发声,最终完成一首乐曲的演奏。

设计以《世上只有妈妈好》为例,分析了硬件电路发声的基本原理,探讨了可以实现设计的方案,利用VHDL语言在QuartusⅡ上编程设计了节拍发生器、分频器、顺序控制、音高控制等模块的功能。

最后,运用原理图编辑器调出已经设计好的各个模块,根据设计的要求进行连线、加输入输出脚,得到了总体设计的仿真实体。

并对总体设计进行了功能仿真和下载。

本设计完成了乐曲《世上只有妈妈好》的32个音符64个节拍的播放,每个节拍0.5秒,整曲播放时长为32秒。

基于FPGA,利用Quartus Ⅱ和VHDL语言完成的脉冲型乐曲播放器,其特点是设计简单、灵活、设计周期短;缺陷是实现播放的乐曲种类单一,播放时间长度较短,若想要实现较长的乐曲播放,则需要很长的源程序。

关键词:FPGA,EDA,VHDL,QuartusⅡ,乐曲播放器The design of the pulse-type music player based on FPGA / CPLDAbstractIt is very complex to complete the music playing logic circuit using pure hardware. Only depend on the traditional digital logic technology, it is difficult to achieve even the simple circuit. However, it is very ease to achieve by using the EDA tools and hardware description language. The design finished a controller that output a series of orderly pulse signal with different frequencies and driven speaker with, by using the programmable logic device ,and finally complete the concert of a music.The music <shi shang zhi you ma ma hao> was used as an example. The basic principal of the hardware circuit sing was analyzed. How could achieve the player’s faction was also discussed. Following functional module was designed in Quartus II by using VHDL language: pulse generator, frequencies divider, sequence control, pitch control and so on. Finally, simulate entity was build in the Block Editor of the Quartus II , using all of the module which has been designed and according to the design’s requirements to connect, and plus input and output pin. Following these, the player’s entity was simulated and downloaded. The <shi shang zhi you ma ma hao>’s note 32 of the 64 players beat was completed in this design. One beat was sat as 0.5 seconds long, and the whole song was played within 32 seconds。

基于VHDL可编程m序列发生器的研制

基于 VHDL 可编程 m 序列发生器的研制赵林军(陕西理工学院 电子与信息工程系 陕西 汉中 723003)摘 要: 提出一种可实现周期ƒ初相位编程控制的 m 序列发生器逻辑电路的设计方案。

给出了 V HDL 与 C P L D 的实现 方 案。

程序经编译、仿真、测试后, 可以实现设计要求。

该器件在M C S 51 的控制下, 实现m 序列的周期、初相位的编程变关键词: m 序列发生器; V HDL ; 逻辑电路; C P L D中图分类号: TN 914142文献标识码: B文章编号: 1004 373X (2004) 14 033 02Re s ea r ch an d D eve lop m en t of Programm a b le m Sequen ce Gen e ra tor Ba sed on VHDLZHA O L in jun(D ep a r t m en t o f E lec t ro n i c & Info rm a t i o n E ng inee r ing , Shaanx i U n i ve r s ity o f T echno lo gy , H anzho ng , 723003, C h ina )A b stra c t : T h e a r t i c l e in t r o d uce s o n e o f m sequ en ce gen e r a t o r s , w h ich deve l op ed ba s in g o n V HDL lan guage an d can beenp ro g r am m ab le o n p e r i o d s f r om 22 - 1 to 232- 11 W e exp lica t ed m ak in g p r i n c i p le an d w o rk i n g co u r s e , fu r t h e r m o re , gave th e h a r d w ir ec i rcu it o f th e i m p lem en t th a t h a s g r ea t l y p rac t i ca l and refe r en t i a l va l ue 1Keywords : m sequ en ce gen e r a t o r ; V HDL ; lo g i ca l c i rcu it ; C P L Dm 序列广泛应用于数字基带信号进行加扰, 改善数字 序列的位定时质量与帧同步和自适应时域均衡性能, 同时 也是构造平衡 G OL D 码的基础。

一种脉冲波形可调的声音信号发生器设计

一种脉冲波形可调的声音信号发生器设计周致【摘要】音频信号发生器是测量声音信号处理设备性能指标必不可少的仪器,文章首先论述了声音信号发生器的研究现状,然后针对现有技术存在的问题,提出一种可分别调节输出电压的占空比、频率、幅度的脉冲波形可调的声音信号发生器,且该声音信号发生器的占空比、频率、幅度可实现单一的调节。

最后针对设计的信号发生器进行了实验,实验结果表明文章提出并设计的新型脉冲波形可调的声音信号发生器实用且具有明显的优势。

%Audio signal generator is essential equipment to measure the sound signal and deal with equipment performance. The paper compendiously summarizes the overseas and domestic research status of voice signal generators. Then we put forward a new voice signal generator to solve the problems of existing technology, in which the duty ratio of output voltage, frequency, amplitude adjustable pulse waveform of the voice signal generator can be adjusted respectively, and the sound the duty ratio, frequency and amplitude of the signal generator can realize the single adjustment. The experimental results show that the proposed new type of pulse waveform with adjustable voice signal generator is practical and has obvious advantages.【期刊名称】《江苏科技信息》【年(卷),期】2016(000)009【总页数】3页(P70-72)【关键词】音频信号发生器;脉冲波形可调;设计【作者】周致【作者单位】山东科技大学电气与自动化工程学院,山东青岛 266590【正文语种】中文声音是人类表达思想、进行社会交流的主要载体。

任意波发生器的VHDL设计【文献综述】

文献综述电子信息工程任意波发生器的VHDL设计前言信号源作为一种基本电子设备,在教学、科研和在工程技术保障中有着广泛的使用。

从理论到工程对信号的发生进行深入研究,不论是从教学科研角度,还是从工程技术保障服务角度出发都有着积极的意义。

信号发生器是一种历史最为悠久的测量仪器。

早在二十年代,当电子设备刚开始出现时,它就出现了。

随着通信和雷达技术的发展,四十年代出现了主要用于测试各种接收机的标准信号发生器,使信号发生器从定性分析的测试仪器成为定量分析的测量仪器。

同时还出现了可用来测试脉冲电路或用作脉冲调制器的脉冲信号发生器。

由于早期的信号发生器机械结构比较复杂,功率比较大,电路比较简单(与数字仪器、示波器等相比),因此发展速度较慢。

直到1964年才出现了第一台全晶体管的信号发生器。

自六十年代以来,信号发生器有了迅速的发展,出现了函数发生器、扫频信号发生器、合成信号发生器、程控信号发生器等新种类。

各类信号发生器的主要性能指标也都有了大幅度的提高,同时在简化机械结构、小型化、多功能等各方面也有了显著的进展。

信号发生器的应用非常广泛,种类繁多,其中按输出波形又可分为正弦波信号发生器、脉冲波信号发生器、函数发生器和任意波发生器等。

主题任意波形发生器(简称AWG)是随着不断进步的计算机技术和微电子技术在测量仪器中的应用而形成和发展起来的一类新型信号源。

[1]它广泛应用于电子测量、电力工程、物矿勘探、医疗、振动分析、声学分析、故障诊断及教学科研等方面,是工程师进行产品研发和生产的必备仪器之一。

它的主要功能是为待测设备提供稳定、可靠并可以人工调节和控制的信号源,如正弦波、方波、三角波、锯齿波、白噪声和扫频信号以及用户定义的任意波形。

[2]任意波发生器是以D/A变换器为核心的,由时钟电路、存储器电路、控制逻辑(计数器电路、地址译码电路)、计算机、滤波放大器等环节组成的,能将具有幅度量化特征和时间抽样特点的离散数据组按顺序发出,生成模拟信号波形的一种数字化模拟信号发生装置,其技术内涵和实质是使用离散的数字化方式产生连续的模拟信号波形;用有限个量值状态及其阶跃过渡过程描述具有无限个量值状态的信号波形。

基于VHDL的可控脉冲发声器 设计

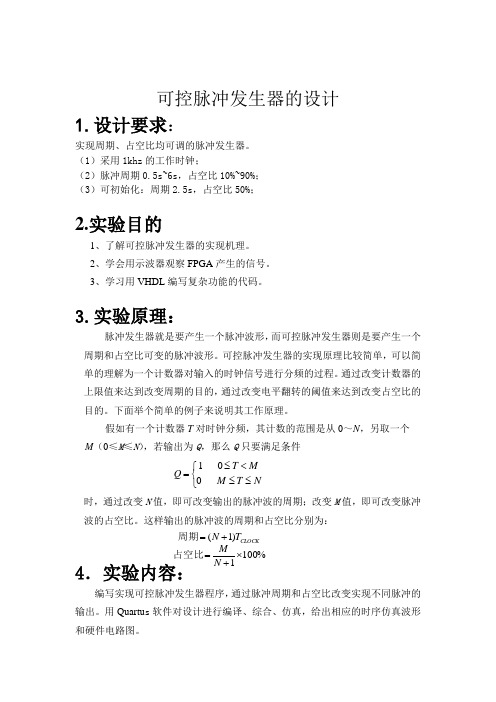

可控脉冲发生器的设计1.设计要求:实现周期、占空比均可调的脉冲发生器。

(1)采用1khz 的工作时钟;(2)脉冲周期0.5s~6s ,占空比10%~90%;(3)可初始化:周期2.5s ,占空比50%;2.实验目的1、了解可控脉冲发生器的实现机理。

2、学会用示波器观察FPGA 产生的信号。

3、学习用VHDL 编写复杂功能的代码。

3.实验原理:脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是要产生一个周期和占空比可变的脉冲波形。

可控脉冲发生器的实现原理比较简单,可以简单的理解为一个计数器对输入的时钟信号进行分频的过程。

通过改变计数器的上限值来达到改变周期的目的,通过改变电平翻转的阈值来达到改变占空比的目的。

下面举个简单的例子来说明其工作原理。

假如有一个计数器T 对时钟分频,其计数的范围是从0~N ,另取一个 M (0≤M ≤N ),若输出为Q ,那么Q 只要满足条件时,通过改变N 值,即可改变输出的脉冲波的周期;改变M 值,即可改变脉冲波的占空比。

这样输出的脉冲波的周期和占空比分别为:4.实验内容:编写实现可控脉冲发生器程序,通过脉冲周期和占空比改变实现不同脉冲的输出。

用Quartu s 软件对设计进行编译、综合、仿真,给出相应的时序仿真波形和硬件电路图。

⎩⎨⎧≤≤<≤=N T M M T Q 001%1001)1(⨯+=+=N M T N CLOCK 占空比周期5.程序设计及仿真:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity exp10 isport( Clk : in std_logic; --时钟输入Rst : in std_logic; --复位输入NU,ND : in std_logic; --输入:控制频率的改变MU,MD : in std_logic; --输入:控制占空比的改变Fout : out std_logic --波形输出);end exp10;architecture behave of exp10 issignal N_Buffer,M_Buffer : std_logic_vector(10 downto 0);signal N_Count :std_logic_vector(10 downto 0);signal clkin : std_logic;signal Clk_Count : std_logic_vector(12 downto 0); --产生一个低速时钟,用于按键判断beginprocess(Clk) --计数器累加beginif(Clk'event and Clk='1') thenif(N_Count=N_Buffer) thenN_Count<="00000000000";elseN_Count<=N_Count+1;end if;end if;end process;process(Clk) --波形判断beginif(Clk'event and Clk='1') thenif(N_Count<M_Buffer) thenFout<='1';elsif(N_Count>M_Buffer and N_Count<N_Buffer) then Fout<='0';end if;end if;end process;process(Clk)beginif(Clk'event and Clk='1') thenClk_Count<=Clk_Count+1;end if;clkin<=Clk_Count(12);end process;process(clkin) --频率及占空比的改变1beginif(clkin'event and clkin='0') thenif(Rst='0') thenM_Buffer<="010********";N_Buffer<="10000000000";elsif(NU='0') thenN_Buffer<=N_Buffer+1;elsif(ND='0') thenN_Buffer<=N_Buffer-1;elsif(MU='0') thenM_Buffer<=M_Buffer+1;elsif(MD='0') thenM_Buffer<=M_Buffer-1;end if;end if;end process;end behave;(2)仿真图:6.引脚绑定:7.心得体会:在课程设计的这段时间里,我认为收获还是很多的,不但进一步掌握了数字电子技术的基础知识及一门专业仿真软件的基本操作,还提高了自己的设计能力及动手能力,同时对于抢答器来了个系统的总结。

(完整word版)基于VHDL语言信号发生器的设计.EDA课程设计

EDA 课程设计报告书课题名称 基于VHDL 语言信号发生器的设计 姓 名易金祥学 号 081220139 院 系 物理与电信工程系 专 业 电子信息工程 指导教师周来秀 讲师2011年 6月10日※※※※※※※※※ ※※ ※※ ※※2008级学生EDA 课程设计基于VHDL语言信号发生器的设计1、设计目的1) 掌握使用EDA工具设计信号发生器系统的设计思路和设计方法,体会使用EDA综合过程中电路设计方法和设计思路的不同,理解层次化设计理念。

2) 熟悉在Quartus II环境中,用文本输入方式与原理图输入方式完成电路的设计,同时掌握使用这两种方式相结合的EDA设计思路。

3) 通过这一部分的学习,对VHDL语言的设计方法进行进一步的学习,对其相关语言设计规范进行更深层次的掌握,能够更加熟练的做一些编程设计。

2、设计的主要内容和要求通过使用VHDL语言及Quartus II软件,设计多功能信号发生器的每个模块,将正弦波模块,方波模块,三角波模块,阶梯波模块创建相应的元件符号,同时设计好4选1数据选择器模块,再通过原理图输入方式,将各个模块组合起来,设计成一个完整的多种信号发生器电路,同时将各个模块单独进行仿真,设计各个模块的仿真波形,最后进行总原理图电路仿真,设计该信号发生器的总的仿真波形。

信号发生器:体现在它能自动的实现四种波形的转换。

根据题目的分析与整体构思可知,要完成设计任务必须完成以下要求:1、设计好用于波形切换的四路数据选择器selector4_1;2、设计好用于总电路设计的各个信号输出模块;3、设计好数模(D/A)转换器。

3、整体设计方案基本设计方案:在现有单一信号发生器的基础上,加上其它信号模块,通过组合与设计,用数模转换器(D/A)将选中的信号源发出的信号由数字信号转换为模拟信号,再用示波器显示出来,其信号发生器的结构框图如图3.1所示。

信号发生器由各个单一信号模块组合而成,其中信号产生模块将产生所需的各种信号,信号发生器的控制模块可以用数据选择器实现,用4选1数据选择器实现对四种信号的选择。

一种基于VHDL的超声波电源的PWM电路的设计

一种基于VHDL的超声波电源的PWM电路的设计车保川【摘要】PWM是超声波电源常用的调节功率的重要方法之,传统PWM控制电路往往存在电路设计复杂、可靠性较差等不足。

为此,在介绍PWM基本原理基础上,提出了一种新颖的基于FPGA产生PWM的方法。

利用VHDL语言进行了详细的设计说明,并在modelsim软件中进行了仿真验证。

结果表明:以FPGA 为载体设计的PWM控制电路,可以方便地进行PWM脉宽的宽度,实现功率调节。

【期刊名称】《机电信息》【年(卷),期】2010(000)012【总页数】2页(P73-74)【关键词】PWM;超声波电源;VHDL【作者】车保川【作者单位】常州市广播电视大学,江苏常州213001【正文语种】中文【中图分类】TN79目前,超声波电源常常使用专用的集成芯片如TL494、SG3525等来产生PWM (脉冲宽度调制)波形,并由其通过反馈信号来实现对PWM波形的宽度调节,从而获得稳定的输出。

通过这种方式构成的传统PWM控制电路往往存在电路设计复杂、体积大、抗干扰能力差以及设计困难、设计周期长等缺点,当控制电路设计完成后,就是一个相对独立的系统,调节、控制方式不能再更改,系统的总体协调功能差。

因此PWM控制电路的模块化、集成化已成为发展趋势。

它不仅可以使系统体积减小、重量减轻且功耗降低,同时可使系统的可靠性大大提高。

可编程芯片尤其是CPLD/FPGA(复杂可编程逻辑器件/现场可编程门阵列)具有通用性强、灵活性好的特点,这些芯片可以用VHDL(非常高速集成电路硬件描述语言)进行至顶向下的设计开发,设计者不需要了解硬件的结构就通过软件编程用硬件来实现所需的控制器,系统的抗干扰性能优于单片机系统。

此外,使用CPLD/FPGA 的控制器可以在不改变主电路的前提下通过重新编程就可以获得不同的控制方式,从而提高和升级系统的性能。

针对以上情况,本文给出一种基于FPGA器件的PWM控制电路设计。

VHDL做PWM发生器的大作业

VHDL 大作业――PWM发生器姓名:贾胜文学号:036086279一.功能描述如下图所示:D0-D7为8位数据输入,A为内部脉宽寄存器/计数分频器选择信号,LOAD为所存信号输入,当有上升沿在LOAD上时,D0-D7上的数据被锁存进内部脉宽寄存器(A为高电平)或计数分频器(A为低电平)。

COUNTCLK为内部8位分频计数器时钟,当有上升沿出现在COUNTCLK上时,内部分频计数器值减1,当计数值0时再减1,分频计数器就重新从分频寄存器中装入计数初值,准备进行下一论计数,同时让内部的PWM周期计数器加1。

RS为内部PWM周期计数器、分频计数器清零信号,高电平有效。

PWMOUT为PWM信号输出端。

内部PWM周期计数器计数的同时与脉宽寄存器值比较,前者比后者小时,PWMOUT 输出高电平否则输出低电平。

这样通过改变分频寄存器中的值就可以改变PWM信号的周期,改变脉宽寄存器中的值就可以改变PWM信号的脉宽。

二.源程序:LIBRARY ieee;USE ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity pwm isport(a:in std_logic; --脉宽寄存器/分频寄存器选择.1-脉宽寄存器,0-分频寄存器countclk: in std_logic;--分频计数器计数信号rs: in std_logic;--分频计数器、PWM周期计数器清零信号load: in std_logic;--数据装载信号dat: in std_logic_vector(7 downto 0);--8位数据输入pwmout: out std_logic);--PWM信号输出end pwm;architecture work of pwm issignal mycounter,cmpdat,fenpindat,fenpincount:integer range 0 to 255;signal theout:std_logic;begindataload_block:process(load)beginif(load'event and load='1') thenif a='1' thencmpdat<=conv_integer(dat);elsefenpindat<=conv_integer(dat);end if;end if;end process;counter_block:process(countclk,rs)beginif (countclk'event and countclk='1') then if rs='0' thenif fenpincount=0 thenfenpincount<=fenpindat;mycounter<=mycounter+1;if cmpdat<mycounter thentheout<='0';elsetheout<='1';end if;elsefenpincount<=fenpincount-1;end if;elsemycounter<=0;fenpincount<=fenpindat;end if;end if;end process;pwmout<=theout;end work;三.仿真时序图四.附件:源程序:pwm.vhd仿真时序:pwm.scf。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

可控脉冲发生器的设计

1.设计要求:

实现周期、占空比均可调的脉冲发生器。

(1)采用1khz 的工作时钟;

(2)脉冲周期0.5s~6s ,占空比10%~90%;

(3)可初始化:周期2.5s ,占空比50%;

2.实验目的

1、了解可控脉冲发生器的实现机理。

2、学会用示波器观察FPGA 产生的信号。

3、学习用VHDL 编写复杂功能的代码。

3.实验原理:

脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是要产生一个周期和占空比可变的脉冲波形。

可控脉冲发生器的实现原理比较简单,可以简单的理解为一个计数器对输入的时钟信号进行分频的过程。

通过改变计数器的上限值来达到改变周期的目的,通过改变电平翻转的阈值来达到改变占空比的目的。

下面举个简单的例子来说明其工作原理。

假如有一个计数器T 对时钟分频,其计数的范围是从0~N ,另取一个 M (0≤M ≤N ),若输出为Q ,那么Q 只要满足条件

时,通过改变N 值,即可改变输出的脉冲波的周期;改变M 值,即可改变脉冲波的占空比。

这样输出的脉冲波的周期和占空比分别为:

4.实验内容:

编写实现可控脉冲发生器程序,通过脉冲周期和占空比改变实现不同脉冲的输出。

用Quartu s 软件对设计进行编译、综合、仿真,给出相应的时序仿真波形和硬件电路图。

⎩⎨⎧≤≤<≤=N T M M T Q 001%1001)1(⨯+=+=N M T N CLOCK 占空比周期

5.程序设计及仿真:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity exp10 is

port( Clk : in std_logic; --时钟输入

Rst : in std_logic; --复位输入

NU,ND : in std_logic; --输入:控制频率的改变

MU,MD : in std_logic; --输入:控制占空比的改变

Fout : out std_logic --波形输出

);

end exp10;

architecture behave of exp10 is

signal N_Buffer,M_Buffer : std_logic_vector(10 downto 0);

signal N_Count :std_logic_vector(10 downto 0);

signal clkin : std_logic;

signal Clk_Count : std_logic_vector(12 downto 0); --产生一个低速时钟,用于按键判断

begin

process(Clk) --计数器累加

begin

if(Clk'event and Clk='1') then

if(N_Count=N_Buffer) then

N_Count<="00000000000";

else

N_Count<=N_Count+1;

end if;

end if;

end process;

process(Clk) --波形判断

begin

if(Clk'event and Clk='1') then

if(N_Count<M_Buffer) then

Fout<='1';

elsif(N_Count>M_Buffer and N_Count<N_Buffer) then Fout<='0';

end if;

end if;

end process;

process(Clk)

begin

if(Clk'event and Clk='1') then

Clk_Count<=Clk_Count+1;

end if;

clkin<=Clk_Count(12);

end process;

process(clkin) --频率及占空比的改变1

begin

if(clkin'event and clkin='0') then

if(Rst='0') then

M_Buffer<="010********";

N_Buffer<="10000000000";

elsif(NU='0') then

N_Buffer<=N_Buffer+1;

elsif(ND='0') then

N_Buffer<=N_Buffer-1;

elsif(MU='0') then

M_Buffer<=M_Buffer+1;

elsif(MD='0') then

M_Buffer<=M_Buffer-1;

end if;

end if;

end process;

end behave;

(2)仿真图:

6.引脚绑定:

7.心得体会:

在课程设计的这段时间里,我认为收获还是很多的,不但进一步掌握了数字电子技术的基础知识及一门专业仿真软件的基本操作,还提高了自己的设计能力及动手能力,同时对于抢答器来了个系统的总结。

更多的是让我看清了自己,明白了凡事需要耐心,实践是检验学习的唯一标准。

理论知识的不足在这次课设中表现的很明显。

这将有助于我今后的学习,端正自己的学习态度,从而更加努力的学习。

总之,通过本次课程设计不但让我又学到了一些知识,而且也提高了我的综合能力。

使我在各方面都得到了锻炼,非常感谢我们的指导老师,使我这次

的课程设计任务圆满完成。