多通道可调脉宽脉冲发生器设计

脉冲序列发生器设计

摘要脉冲序列检测器广泛应用于现代数字通信系统中,随着通信技术的开展,对多路脉冲序列信号检测要求越来越高。

现代通信系统的开展方向是功能更强、体积更小、速度更快、功耗更低,大规模可编程逻辑器件FPGA器件的集成度高、工作速度快、编程方便、价格较低,易于实现设备的可编程设计,这些优势正好满足通信系统的这些要求。

随着器件复杂程度的提高,电路逻辑图变得过于复杂,不便于设计。

VHDL(VHSIC Hardware Description Language)是随着可编程逻辑器件的开展而开展起来的一种硬件描述语言。

VHDL具有极强的描述能力,能支持系统行为级、存放器输级和门级三个不同层次的设计,实现了逻辑设计师多年来梦寐以求的“硬件设计软件化〞的愿望,给当今电子通信系统设计带来了革命性的变化。

本文针对传统的脉冲序列检测器方案,提出了一种基于对脉冲序列检测器设计的新方案,该方案相对于传统的设计方法更适合于现代数字通信系统,不但大大减少了周边的设备,也使系统设计更加灵活,稳定性更好,性价比更高,可以满足多种环境下的检测系统的要求。

关键词:多路数据选择器、Multisim、计数器、序列检测器目录摘要 (1)1目录 (1)2.设计内容及设计要求 (2)实验目的 (3)3.2参考电路 (4)3.3实验内容及主电路图 (5)3.4多谐振荡器的介绍 (6)3.5计数器的介绍 (9)3.6数据分析 (12)3.7数据选择器的介绍 (14)4实验结果 (16) (17)设计总结 (18)致谢 (19)参考文献 (20)2设计内容及技术要求1、设计并制作一个脉冲序列发生器,周期性的产生8位长度的任意脉冲序列,脉冲序列可以通过设置电路自由设置。

2、能够检测出设置的脉冲序列,在每出现一次设置的脉冲序列时,点亮一次LED;3、时钟脉冲周期为1HZ;4、对设置的脉冲序列值通过适当的方式进展指示;5、电源:220V/50HZ的工频交流电供电;6、〔直流电源局部仅完成设计仅可,不需制作,用实验室提供的稳压电源调试,但要求设计的直流电源能够满足电路要求〕7、按照以上要求设计电路,绘制电路图,对设计的的电路用Multisim或OrCAD/PspiceAD9进展仿真,用万用板焊接元器件,制作电路,完成调试、测试,撰写设计报告。

可变脉宽方波发生器的设计

成绩评定实习报告实习名称:毕业实习实习单位:中国电信浦江分公司指导教师:王晶专业班级:通信工程 0801班(本)姓名学号:张俊杰 0830********实习时间: 2011.12.20—2012.03.15教务处制二O一二年四月实习报告一、实习说明(1)实习时间:2011年12月20日至2012年3月15日(2)实习地点:中国电信浦江分公司(3)实习性质:顶岗实习二、实习单位简介中国电信集团公司是按照国家电信体制改革方案组建的特大型国有通信企业。

中国电信作为中国主体电信企业和最大的基础网络运营商,拥有世界第一大固定电话网络,覆盖全国城乡、通达世界各地,成员单位包括遍布全国的31个省级企业,在全国范围内经营电信业务中国电信浦江分公司是浙江的通信|计算机|互联网企业,主要服务产品有:电信。

中国电信浦江分公司是具有百年历史的国有电信运营企业,拥有200多名员工。

主要经营县内、国际各类固定电信网络设施,包括本地无线环路;基于电信网络的语音、数据、图像及多媒体通信与信息服务;进行国际电信业务对外结算,开拓海外通讯市场;经营与通讯及信息业务相关的系统集成、技术开发、技术服务、信息咨询、广告、出版、设备生产销售和进出口、设计施工等业务;并根据市场发展需要,经营国家批准或允许的其他业务。

三、实习环境我被安排在ADSL社区实习,也就是大家说的社区经理,实习期间,都是一名师傅带着我进入这门行业,在他的指导下,学习与实践,而实习内容主要是ADSL的安装与维护。

经过师傅的悉心教导,很快我就熟悉了ADSL的各项原理,实际操作能力也有所提高,以下就是我的一些实习体会。

四、实习过程(1)了解过程我刚来报到时,遇到很多新的面孔,由于和他们未熟悉,所以不敢和他们说太多的话,而且对工作未曾了解,开始觉得不太适应。

后来我慢慢发现,只要真诚待人,虚心请教同事,他们也很乐意和我交往。

还教会我一些技术,由此我深感真诚的重要性,在公司里不但要学会如何做事,而且要学会如何做人。

PWM (脉冲宽度调制)原理与实现

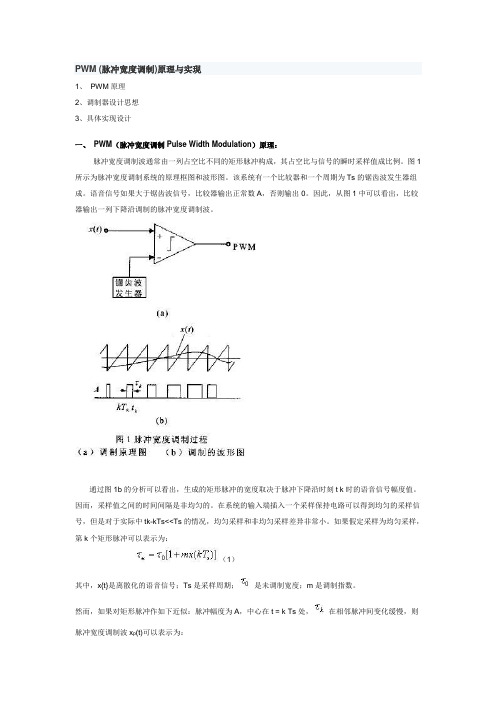

PWM (脉冲宽度调制)原理与实现1、PWM原理2、调制器设计思想3、具体实现设计一、PWM(脉冲宽度调制Pulse Width Modulation)原理:脉冲宽度调制波通常由一列占空比不同的矩形脉冲构成,其占空比与信号的瞬时采样值成比例。

图1所示为脉冲宽度调制系统的原理框图和波形图。

该系统有一个比较器和一个周期为Ts的锯齿波发生器组成。

语音信号如果大于锯齿波信号,比较器输出正常数A,否则输出0。

因此,从图1中可以看出,比较器输出一列下降沿调制的脉冲宽度调制波。

通过图1b的分析可以看出,生成的矩形脉冲的宽度取决于脉冲下降沿时刻t k时的语音信号幅度值。

因而,采样值之间的时间间隔是非均匀的。

在系统的输入端插入一个采样保持电路可以得到均匀的采样信号,但是对于实际中tk-kTs<<Ts的情况,均匀采样和非均匀采样差异非常小。

如果假定采样为均匀采样,第k个矩形脉冲可以表示为:(1)其中,x{t}是离散化的语音信号;Ts是采样周期;是未调制宽度;m是调制指数。

然而,如果对矩形脉冲作如下近似:脉冲幅度为A,中心在t = k Ts处,在相邻脉冲间变化缓慢,则脉冲宽度调制波x p(t)可以表示为:(2)其中,。

无需作频谱分析,由式(2)可以看出脉冲宽度信号由语音信号x(t)加上一个直流成分以及相位调制波构成。

当时,相位调制部分引起的信号交迭可以忽略,因此,脉冲宽度调制波可以直接通过低通滤波器进行解调。

二、数字脉冲宽度调制器的实现:实现数字脉冲宽度调制器的基本思想参看图2。

图中,在时钟脉冲的作用下,循环计数器的5位输出逐次增大。

5位数字调制信号用一个寄存器来控制,不断于循环计数器的输出进行比较,当调制信号大于循环计数器的输出时,比较器输出高电平,否则输出低电平。

循环计数器循环一个周期后,向寄存器发出一个使能信号EN,寄存器送入下一组数据。

在每一个计数器计数周期,由于输入的调制信号的大小不同,比较器输出端输出的高电平个数不一样,因而产生出占空比不同的脉冲宽度调制波。

基于FPGA的可调制脉宽调制发生器的设计

基于FPGA的可调制脉宽调制发生器的设计科研创新训练研究报告题目:基于FPGA的可调制脉宽调制发生器的设计学院:测试与光电工程学院专业名称:电子科学与技术班级学号: 11083229学生姓名:郑煌盛指导教师:柴明钢2014 年11月 14日基于FPGA的可调制脉宽调制发生器的设计与实现摘要:随着电子技术的发展,特别是ASIC(专用集成电路)设计技术的日趋完善,数字化的EDA(电子设计自动化)工具给电子设计带来了巨大变革,在电机控制等许多应用场合,需要产生多路频率和脉冲宽度可调的PWM(脉宽调制)波形,这可通过FPGA(现场可编程门阵列)丰富的硬件资源和可以配置I/O引脚来实现。

嵌入式系统中FPGA的应用设计关键是系统软硬件功能的划分,现场可编程门阵列(FPGA)和数字信号处理器(DSP)的飞速发展,使得数字控制技术逐渐取代模拟控制技术实现系统的控制功能。

数字化控制具有速度快、控制精度高以及控制方案灵活的优点,并且可以利用较少的器件获得更理想的结果,因此具有很高的应用价值。

本设计基于FPGA设计了一个可调制的PWM发生器,使用VHDL(超高速硬件描述语言)进行了控制输出的脉冲宽度的功能设计。

本文首先从数据获取,然后用VHDL语言对数据进行处理,使得获得的数据能够对脉冲宽度进行控制,并通过在Quartus II软件中进行了仿真验证,最后进行了下载调试。

结果表明,符合系统设计要求,从而完成了本次研究与设计。

关键词:FPGA 脉宽调制(PWM)数据获取 VHDL目录基于FPGA的可调制脉宽调制发生器的设计与实现 .................................................... - 3 -一PWM脉宽调制发生器的设计 .............................................................................. - 6 -1.1 PWM概述说明 ............................................................................................... - 6 -1.2 脉宽调制发生器设计方法猜想........................................................................ - 6 -1.2.1 方案一的设计: ....................................................................................... - 6 -1.2.2 方案二的设计........................................................................................... - 7 -1.2.3 方案的选择:........................................................................................... - 8 -二脉宽调制FPGA输入设计..................................................................................... - 8 -2.1脉宽调制数值输入方法的设计...................................................................... - 8 -2.1.1方法一:................................................................................................ - 8 -2.1.2方法二:................................................................................................ - 9 -2.1.3方法一和二的选择比较: ...................................................................... - 9 -2.2VHDL数值输入使然模块的设计.................................................................... - 9 -2.2.1VHDL使然程序设计: ........................................................................... - 9 -2.2.1 VHDL使然软件模块设计 ........................................................................ - 10 -2.2.2VHDL使然模块波形仿真...................................................................... - 11 -2.3 VHDL输入数值处理模块的设计.................................................................... - 11 -2.3.1 输入数值处理程序设计 .......................................................................... - 11 -2.3.2 VHDL输入数值软件模块设计 ............................................................... - 12 -2.3.3 VHDL数值输入模块软件仿真 ................................................................. - 13 -2.4相频检波模块的设计 .................................................................................. - 13 -2.4.1 相频检波模块软件实现 .......................................................................... - 13 -2.4.2 相频检波模块仿真 ................................................................................... - 14 -2.5脉宽调制数值输入方案仿真结果总结......................................................... - 14 -2.5.1 VHDL模块的设计综合 ............................................................................ - 14 -2.5.2 VHDL模块综合仿真................................................................................ - 15 -2.6数码显示管的数值显示设计 ....................................................................... - 16 -2.6.1数码管原理图说明 ............................................................................... - 16 -2.6.2 数码显示管VHDL程序设计.................................................................... - 16 -2.6.3数码管VHDL显示模块设计 ................................................................. - 18 -2.6.4VHDL程序仿真..................................................................................... - 19 -2.7FPGA下载与配置 ........................................................................................ - 19 -三VHDL脉宽调制硬件实现 ................................................................................... - 21 -3.1FPGA芯片选择............................................................................................ - 21 -3.2 电路图的设计 ............................................................................................... - 22 -3.3 实验数据验证 ............................................................................................... - 22 -四、问题及展望........................................................................................................ - 25 -五结束语 ............................................................................................................... - 26 -参考文献................................................................................................................... - 27 -一 PWM脉宽调制发生器的设计1.1 PWM概述说明PWM(脉宽调制)是现代控制技术常用的一种控制信息输出,可以有效地利用数字技术控制模拟信号的技术。

基于AVR单片机的多模式音频调制脉宽治疗仪设计

pulse its

width adjusted for

blood

pressure

in

spontaneously

and

mechanism”.Experimental animal study results show that the audio-pulse width

modulation

technology

学位论文作者签名:韵分饿迫程

新虢f彳,洲)

日期:沙胡年毛月(El

中ln大学硕士学经论文

基于AVR荤片机的多模式鹰频调箭脉童治疗仪设计

第一章绪论

1.1引言

针灸是传统中医的一种治疗方法,在中国具有悠久的历史,据考古资料证明, 针灸疗法起源于人类开始用火之后的旧石器时代,最早见于文字记载的是《左

传》。中医学理论有记载【l】,大凡疼痛,多是因为经络闭阻不通、气血瘀滞不行

one

is more superior by using

ATmega64蠢s the main control chip。An audio signal generatoL USB data transformer, audio file storage,audio file information display functions

参数共同决定的。这些脉冲具有以下一些特点:脉冲频率不固定,脉宽在工作参

数设定后由音频信号调制,脉冲幅度可调,但每次调整后输出等幅脉冲。以往音

频调制脉冲技术中,一般是以脉冲幅度作为调制对象,其脉冲频率不变,即输出 脉冲的幅度根据音频信号调制而时高时低,而脉冲间隔不变。这种技术的弊端是: 一方面,在不确定的音频信号调制下,可能产生幅度很高的或幅度间相差过大的 脉冲,导致患者产生不适感;另一方面,当脉冲幅度变化不大的情况下,固定频 率的脉冲刺激会使患者的耐受性加强,从而降低治疗效果。

完整版可调脉冲设计

可调脉冲设计与分析摘要我们知道,555电路在应用和工作方式上一般可归纳为3类。

每类工作方式又有很多个不同的电路。

在实际应用中,除了单一品种的电路外,还可组合出很多不同电路,如:多个单稳、多个双稳、单稳和无稳,双稳和无稳的组合等。

这样一来,电路变的更加复杂。

为了便于我们分析和识别电路,更好的理解555电路,这里我们这里按555电路的结构特点进行分类和归纳,把555电路分为3大类、8种、共18个单元电路。

每个电路除画出它的标准图型,指出他们的结构特点或识别方法外,还给出了计算公式和他们的用途。

555时基电路是一种将模拟功能与逻辑功能巧妙地结合在同一硅片上的组合集成电路。

该电路可以在最基本的典型应用方式的基础上,根据实际需要,经过参数配置和电路的重新组合,与外接少量的阻容元件就能构成不同的电路,因而555电路在波形的产生与变换、测量与控制、家用电器、电子玩具等许多领域中都得到了广泛应用。

关键字:NE555目录第一章可调脉冲发生器设计与分析简介 (3)1.1可调脉冲发生器设计与分析绪论 (3)第二章可调脉冲发生器设计与分析设计与分析 (4)2.1方案与论证 (4)2.2总体框图及模块设计 (5)2.3总体电路设计 (7)2.4系统测试,抗干扰及注意细节 (9)第三章可调脉冲发生器设计与分析结果分析论证 (9)3.1硬件调试 (9)3.2结果分析得出结论 (10)参考文献 (11)第一章可调脉冲发生器设计与分析简介555 芯片是定时器,是一种模拟和数字功能相结合的中规模集成器件。

一般用双极性工艺制作的称为555,用CMOS 工艺制作的称为7555,除单定时器外,还有对应的双定时器556/7556。

555 定时器的电源电压范围宽,可在4.5V~16V 工作,7555 可在3~18V 工作,输出驱动电流约为200mA,因而其输出可与TTL、CMOS 或者模拟电路电平兼容1.1可调脉冲发生器设计与分析绪论ne555是一种应用特别广泛作用很大的的集成电路,属于小规模集成电路,在很多电子产品中都有应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《电子技术应用》2007年第5期本刊邮箱:eta@ncse.com.cn图2单片机和CPLD的硬件连接原理图

高重复频率的固体开关技术是脉冲功率领域研究的重点之一。

在兆赫兹重复频率下,适合构成固体开关的功率电子器件有金属氧化物半导体场效应晶体管(MOS-FET)、

砷化镓光导开关(GaAs-PCSS)等。

对于将功率MOS-FET器件作为固体开关的脉冲功率源,由于单个功率MOSFET器件的耐压和输出电流能力有限,为了得到更高的电压和更大的电流,需要对大量的功率MOSFET器件进行串联和并联。

美国利弗莫尔国家实验室(LLNL)用于产生20kV、400A的脉冲功率源,一共使用了720个功率MOS-FET器件[1]。

这些功率MOSFET器件在产生输出脉冲时是

同步触发的,这样就需要有多通道的同步触发信号。

功率MOSFET的开关速度非常快,一般为十几纳秒。

因此,对同步输出的触发信号需要的时间抖动要小于MOSFET器件的开关时间,

否则将会引起并联的

MOSFET器件的电流不均匀,导致器件损坏。

MOSFET器

件的开关完全是由输入栅极驱动信号决定的,为了能使功率MOSFET器件能在MHz的重复频率下工作,要求触发信号源有很小脉宽的输出能力。

本文介绍了一种可用于兆赫兹重复频率的脉冲功率源上作为触发信号的多通道可调脉宽、频率的脉冲发生器的设计。

1系统的组成和工作原理

脉冲发生器的系统结构如图1,整个系统由控制部分和光纤发射电路部分组成。

在控制部分中,单片机89S52和可编程逻辑器件(CPLD)ispLSI1032E组成了脉冲产生的逻辑硬件核心。

单片机负责接收并解析上位机(PC机)的设置信息,如输出脉冲的宽度,频率和个数,通过运算得

到CPLD所需的分频数,并通过8位总线传输给CPLD,由

CPLD产生多个通道同步输出的脉冲信号。

单片机还可以

读取CPLD中关于输出脉冲的设置,处理后返回到上位机作为诊断信息。

CPLD的优点是可用I/O口多,可以实现多通道的同步输出。

光纤发射电路将每一路控制产生的脉冲信号经驱动增强电路之后,分成12路的同步脉冲,用光纤发射器件以光信号的方式输出。

2硬件设计

控制部分的核心是单片机和CPLD器件,它们之间的接口方式一般有独立方式和总线方式两种。

独立方式最大的优点是接口逻辑无须遵循单片机内固定的总线方式的读写时序。

总线方式具有编程简单、速度快的优点。

本设计采用8位总线方式,图2为硬件连接原理图。

设计

多通道可调脉宽脉冲发生器设计

张良,秦玲,刘承俊,章林文

(中国工程物理研究院流体物理研究所,四川绵阳621900)

摘要:一种用于功率MOSFET器件触发信号产生的多通道可调脉宽脉冲发生器。

该装置具有控制简单,多个通道时间抖动小的特点。

关键词:信号发生器多通道脉宽可调

29

《电子技术应用》2007年第5期

欢迎网上投稿www.aetnet.cnwww.aetnet.com.cn图4脉冲信号发生器控制程序用户界面

图3单路光纤发射原理图

中选用的CPLD是Lattice公司的ispLSI1032E-

125LJ,CPLD的时钟采用80MHz的有源晶振,

产生的脉冲的最小脉宽为12.5ns,最大的脉冲宽度为12.5×256=3187.5ns。

在脉冲串输出模式下最多可以输出255个脉冲;在连续输出模式下,输出脉冲个数不受限制。

这样的设计可以满足脉冲功率源的应用范围。

单路光纤发射电路原理图见图3。

为了使光纤发射器件有足够的驱动电流,电路中用了3个与非门并联驱动。

每一个CPLD的输出端口都由光纤发射电路分成12路同步光信号输出,因此,最后能得到的触发信号的路数可以是非常多的,足以满足现阶段开展的脉冲功率源的研究需要。

3软件设计

信号发生器需要编写上位机(PC机)、单片机和CPLD的程序。

在PC机上,用Microsoft

VisualStudio2005作为开发平台,以VB作为

开发语言,采用System.IO.Ports.SerialPort作为串口通信的控件,编写了上位机的控制程序。

SerialPort控件很好地封装了串口通信的操作,编写程序仅仅需要调用Write和ReadByte这两个函数[2]。

PC的功

能模块包括设置和获取信号发生器输出脉冲的宽度、数量、频率、复位单片机等。

开发的脉冲信号发生器控制程序的用户界面如图4所示。

单片机89S52程序的各个函数模块之间的关系和程序流程如图5和图6所示。

整个程序以串口中断处理函数作为程序的主流程。

同时,由于把CPLD作为单片机的外部数据存储器,单片机对CPLD的控制程序就简化为对CPLD映射的几个端口的读写。

CPLD以Lattice公司的ispLevel3做为开发工具,用VHDL作为开发语言,包括端口映射模块和脉冲生成模

块。

端口映射模块模拟单片机的读写时序,将CPLD映

射为单片机的0x80~0x82这几个地址。

其VHDL语言关键代码如下:process(ALE,RD)begin

if((ALEandRD)=′

1′)thenread<=′1′

;endif;

if((ALEandRD)=′0′)then

read<=′0′

;endif;endprocess;

--从总线上读数据

process(read)begin

if(read′EVENTandread=′0′)then

caseALE_Addressis

when″

10000000″=>P0<=baseSettingPeriod;

when″10000001″=>P0<=

baseSettingWidth;

when″10000010″=>P0<=

baseSettingPulsenumber;

30

《电子技术应用》2007年第5期本刊邮箱:eta@ncse.com.cn脉冲宽度电压最大值电压最小值周期

12.6ns

4.3V-1.4V124.7ns

表1波形的测量结果

图9波形实验结果

图6单片机程序流程图

whenothers=>P0<=″ZZZZZZZZ″

;endcase;

endif;

endprocess;

--写数据到总线上

process(WR)beginif(WR′eventandWR=′0′)thencaseALE_Addressis

when″10000000″=>baseSettingPeriod<=P0;when″10000001″=>baseSettingWidth<=P0;when″10000010″=>baseSettingPulsenumber<=P0;whenothers=>null;endcase;endif;

endprocess;

端口映射部分的仿真结果如图7所示。

脉冲生成部分由两个主要process组成,一个process用来产生单个的脉冲,另一个则用来产生设定数量的脉

冲。

仿真的波形如图8所示。

4实验结果

图9是在周期为125ns、脉宽为12.5ns时的实验波形。

对波形的测量结果如表1。

由测量结果可知,实验波形的脉冲宽度以及周期的测量值与相应的设置值之间的误差非常小。

对二路光信号进行接收、放大和调

理之后的波形的测量显示方法得到的多路功率MOSFET器件的触发信号,时间抖动可以小于1ns,相对于功率

MOSFET开关时间(十几个ns),其时间抖动带来的开关

动作不同步效应可以忽略。

因此,采用这种方式设计的多通道触发电路可以适应脉冲功率源的应用要求。

本文介绍的使用51内核的单片机和CPLD器件为硬件核心搭建的多通道可调脉宽的脉冲信号发生器,

可以产生足够数量的同步光信号,满足兆赫兹重复频率的脉冲功率源的大量同步触发信号的应用要求。

参考文献

[1]COOKEG,ALLENFV,AnayaEM,etal.Solid-

StatemodulatorR&DatLLNL.InternationalWorkshoponRecentProgressofInductionAcceleratorsTsukuba,Japan,2002.

[2]MicrosoftCorporation.MicrosoftMSDNLibrary.http://

msdn2.microsoft.com/zh-cn/library/system.io.ports.serialport.aspx

(收稿日期:2006-10-30)

图7CPLD仿真51单片机的读写时序

图8脉冲生成程序的仿真结果

31。