第五章 MOS电路版图设计

MOS管及简单CMOS逻辑门电路原理图

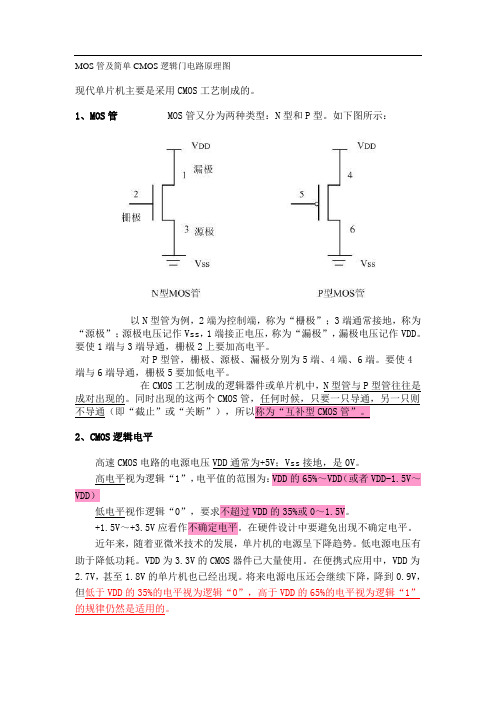

MOS管及简单CMOS逻辑门电路原理图现代单片机主要是采用C MOS工艺制成的。

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMO S2、CMOS逻辑电平高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)低电平视作逻辑“0”,要求不超过V DD的35%或0~1.5V。

+1.5V~+3.5V应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为3.3V的CMO S器件已大量使用。

在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门非门(反向器)是最简单的门电路,由一对CMO S管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与VDD一致,输出高电平。

4、与非门与非门工作原理:①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V DD 一致,输出高电平。

《微电子与集成电路设计导论》第五章 集成电路基础

图5.2.10 与非门电路

图5.2.11-5.2.14 电路图

图5.2.15 与非门输出响应

当A、B取不同组合的 逻辑电平时,与非门 电路的输出响应如图 5.2.15所示。

2. 或非门电路

A=0,B=0

A=0,B=1

A=1,B=0

A=1,B=1

图5.2.16 或非门电路

图5.2.17-5.2.20 A=0,B=0时的电路图

性能指标:除增益和速度外,功耗、电源电压、线性度、噪声和最大 电压摆幅等也是放大器的重要指标。此外,放大器的输入输出阻抗将 决定其应如何与前级和后级电路进行相互配合。在实际中,这些参数 几乎都会相互牵制,一般称为“八边形法则”,茹右下图所示。

➢ 增益:输出量Xout与输入量Xin的比值

➢ 带宽:指放大器的小信号带宽。

特性参数相同,当电压翻转上升时,漏极电流

ID

Kn

W L

Vin

VTN

2

0

I

Imax

即一周期的平均电流

Imean

1 6

Kn

W L

1 VDD

VDD VTN

3

Tclk

综上,短路功耗最终为

Psc VDDImean

CMOS逻辑门电路

1.与非门电路

A=0,B=0

A=0,B=1

A=1,B=0

A=1,B=1

许的临界电平和理想逻辑电平之间的范围为 CMOS电路的直流噪声容限,定义为

VNH VOH VIH

VNL VIL VOL

图5.2.6 极限输出电平定义的噪声容限

(2)极限输出电平定义的噪声容限 根据实际工作确定所允许的最低的输出

高电平VOHmin,它所对应的输入电平定义为 关门电平VOFF;给定允许的最高的输出低电 平VOLmax,它所对应的输入电平定义为开门 电平VON。开门电平和关门电平与CMOS电 路的理想输入逻辑电平之间的范围就是 CMOS电路的噪声容限。如左图所示是反相 器的噪声容限 输入高电平噪声容限:

集成电路版图设计基础第五章:匹配

school of phye

basics of ic layout design

19

匹配方法 之三:虚设器件 dummy device

• 当这些电阻被刻蚀的时候,位于中间的器件所处的环境肯定与两边 的不同,位于两边的器件所受的腐蚀会比中间的器件多一些,这一 点点的区别也许会对匹配产生非常不可预知的结果。 • 为了使上述电阻在加工上面也保持一致,最简单的办法就是在两边 分别放臵一个 “虚拟电阻”(“dummy resistor ”),而实际上它 们在电路连线上没有与其它任何器件连接,它们只是提供了一些所 谓的“靠垫”, 以避免在两端过度刻蚀。这就是虚拟器件, 保证所 有器件刻蚀一致。 dummy etch

real resistors

school of phye

basics of ic layout design

20

匹配方法 之三:虚设器件 dummy device

• Ending elements have different boundary conditions than the inner elements => use dummy

• 之十三:掩模设计者不会心灵感应。

mask designer are not phychic.

• 之十四:注意临近的器件。

watch the neighbors.

school of phye

basics of ic layout design

6

简单匹配 - matching single transistor

school of phye

basics of ic layout design

16

匹配方法 之二:交叉法 interdigitating device

第五章MOS管数字集成电路基本逻辑单元设计

[4](美)Wayne Wolf. Modern VLSI Design System on Silicon. 北京:科学出版社,2019.

[5] 朱正涌. 半导体集成电路. 北京:清华大学出版社,2019. [6] 王志功,沈永朝.《集成电路设计基础》电子工业出版

现,如图5.4.5所示,这同样是一个4选1数据选择器。

图5.4.5 CMOS传输门实现的4选1数据选择器

5.5 锁存器和触发器 5.5.1 锁存器 1.RS锁存器 (1)基于二输入与非门的RS锁存器

图5.3.4 多米诺逻辑电路结构

图5.3.5 多米诺CMOS电路级联

5.4 MOS管传输逻辑电路 5.4.1 MOS管传输门 1.工作原理

(a)NMOS管传输门

(b)PMOS管传输门

图5.4.1 晶体管传输门

对于NMOS管,当输入信号为高电平时,NMOS 管导通,而当输入信号为低电平,NMOS管关断,如 图5.4.1(a)所示。对于PMOS管,当输入信号为低 电平时,PMOS管导通,而当输入信号为高电平时, PMOS管关断,如图5.4.1(b)所示。当开关打开时, 就可以进行信号传输,所以MOS管也称为传输门。 2、应用

章次

第一章 第二章 第三章 第四章 第五章 第六章 第七章 第八章

教学进度表

题目

绪言 MOS晶体管 MOS管反相器 半导体集成电路基本加工工艺与设计规则 MOS管数字集成电路基本逻辑单元设计 MOS管数字集成电路子系统设计 MOS管模拟集成电路设计基础 集成电路的测试与可测性设计 总计

教学时 数

2学时 4学时 6学时 6学时

___

MOS集成电路的版图设计

热电子的F-N隧道电流穿过氧化膜进入浮栅的方法来改变阈

值电压,从而实现存储器的编程和擦除。MOS PROM从器

件结构上分两类:一类是浮栅型,包括浮栅雪崩注入MOS

• ESD(electrostatic Discharge)静电放电损伤

不可恢复的

输入栅保护电路

特点

• 在正常输入电压时,无电流通过 • 当电压升高但远低于栅击穿电压时就会有电流通过 • 对异常电压进行钳位 • 对浪涌电压迅速响应 • 提供从管子放电的路径

最常用的设计是采用电阻-二级管电路

以为λ 单位的设计规则 微米设计规则

版图举例

输入保护电路

倒相器、门电路

总结版图的设计技巧

作业

名词解释

硅栅MOS工艺 SOICMOS

以反向器为例,简要说明P阱CMOS工艺流 程,画出P阱CMOS的剖面图,说明CMOS 电路的主要优点。 由CMOS电路的版图画出其电路图,说明 逻辑关系。(课堂完成)

第五章内容

• MOS集成电路的寄生效应 • CMOS电路中的锁定效应 • MOS集成电路的工艺设计 • MOS集成电路的版图设计规则 • MOS集成电路的版图设计举例

补充

输入缓冲器

作为电平转换的接口电路动大电容(几十、上百pF)

MOS集成电路的版图设计举例

500~800μm2

• 隔离环起到了抑制锁定效应的作用

高速CMOS电路的 输入栅保护电路

图5-35

• 多晶硅电阻、磷扩散电阻 • Dn1和Dn2寄生二极管 • 电路图 • 版图 • 剖面图

MOS集成电路的版图设计举例

输入栅保护电路版图举例 倒相器图形举例 门电路图形举例 版图设计技巧

毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]

![毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]](https://img.taocdn.com/s3/m/15f996a177232f60dccca185.png)

目录摘要 (3)第一章引言 (3)§ (3)§ CMOS 电路的发展和特点 (5)第二章CMOS运算放大器电路图 (8)§Pspice软件介绍 (8)Pspice运行环境 (12)Pspice功能简介 (12)§CMOS运算放大器电路图的制作 (14)§小结 (20)第三章版图设计 (20)§L-EDIT软件介绍 (20)§设计规则 (21)§集成电路版图设计 (24)PMOS版图设计 (24)NMOS版图设计 (27)CMOS运算放大器版图设计 (27)优化设计 (32)第四章仿真 (40)§DRC仿真 (41)§LVS 对照 (42)第五章总结 (48)附录 (50)参考文献 (52)致谢 (53)摘要介绍了CMOS运算放大电路的版图设计。

并对PMOS、NMOS、CMOS运算放大器版图、设计规则做了详细的分析。

通过设计规则检查(DRC)和版图与原理图对照(LVS)表明,此方案已基本达到了集成电路工艺的要求。

关键词:CMOS 放大器 NMOS PMOS 设计规则检查版图与原理图的对照AbstractThe layout desigen of CMOS operation amplifer is presented in this the layouts and design rules of PMOS,NMOS, and CMOS operation amplifer. The results of design rule check(DRC)and layout verification schmatic(LVS) shown that the project have already met to the needs of IC fabricated processing. Keywords: CMOS Amplifer NMOS PMOS DRC LVS第一章引言1.1 集成电路版图设计的发展现状和趋势集成电路的出现与飞速发展彻底改变了人类文明和人们日常生活的面目。

MOS管及简单CMOS逻辑门电路原理图

MOS管及简单CMOS逻辑门电路原理图现代单片机主要是采用CMOS工艺制成的。

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMOS管,任何时候,只要一只导通,另一只则不导通(即“截止”或“关断”),所以称为“互补型CMOS管”。

2、CMOS逻辑电平高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)低电平视作逻辑“0”,要求不超过VDD的35%或0~1.5V。

+1.5V~+3.5V应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为3.3V的CMOS器件已大量使用。

在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门非门(反向器)是最简单的门电路,由一对CMOS管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与V DD一致,输出高电平。

4、与非门与非门工作原理:①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V DD 一致,输出高电平。

②、A输入高电平,B输入低电平时,1、3管导通,2、4管截止,C端电位与1管的漏极保持一致,输出高电平。

第五章 MOS集成电路的版图设计-1

四川大学物理科学与技术学院

NLDD (198)

P31

P+

P well

P+

N well

P+

P substrate

NMOS S/D Extension (SDE)

专用集成电路设计实验室

四川大学物理科学与技术学院

PLDD (197)

BF2

P+

P well

P+

N well

P+

P substrate

PMOS S/D Extension (SDE)

硅圆片及其芯片部位

Classification of Silicon Technology

IC设计主要流程

复杂的 物理 化学 过程

系统总体方案

电路设计 工艺设计

版图设计

生成PG带制作掩模版 工艺流片 测试、划片封装

硅平面工艺是制造MOS IC 的基础。利用不同的 掩膜版,可以获得不同功能的集成电路。因此, MOS IC版图的设计就成为开发新品种和制造合格 集成电路的关键。 目前的版图设计方法有三种:

专用集成电路设计实验室

四川大学物理科学与技术学院

Vtp Implant (197)

BF2

P+

P well

P+

N well

P+

P substrate

Channel profiling. Typically involves more than one implantation steps for adjusting PMOS device threshold (shallow) and increase anti-punch-through robustness (deep).

第5章_电容版图设计

Sandwich电容

A

A

Metal2

B

Metal4 Metal3 B

Metal2 Metal3

Metal2 Metal1

Poly1 Metal1

横向通量电容

本章主要内容

IC电容及其类型

CH7

电容匹配

边缘效应

dummy

C1

C1

C1

C1

C1

C1

C1

Better!

每层互连线都与上一层金属和下一层金属垂直可 以减小重叠电容。

电容器件类型

容值受偏压影响大,在CMOS、 BiCMOS工艺中很少使用。

MOS电容

C1 C2

N+

RS RS

N+

C RS

NWell P-sub

MOS电容的下极板是轻掺杂的衬底或N阱,因此有较大的寄 生串联电阻,所以应避免使用太长沟道的MOS来制作电容。

pip电容poly2poly1nwellpsubpip电容制作于n阱上可以起到屏蔽噪声的作用poly1metal1绝缘层绝缘层绝缘层绝缘层metal1metal1metal2mip电容mim电容堆叠电容三明治电容增大了单位面积的容值metal2绝缘层绝缘层metal1metal2metal3metal4poly1poly1metal2metal2metal4metal1metal1metal3metal3sandwich电容横向通量电容本章主要内容ch7ch7ch7ch7电容匹配ic电容及其类型边缘效应dummyc1c1c1c1c1c1c1c1better

集成电路版图基础

第5章 电容版图设计

本章主要内容

IC电容及其类型

CH7

电容匹配

第五章 MOS集成电路的版图设计-3

单元配置恰当

芯片面积降低10﹪,管芯成品率/圆片可提高 15~20﹪ 多用并联形式;少用串联形式。为什么? 大跨导管采用梳状或马蹄形,小跨导管采用 条状图形,使图形排列尽可能规整

由于MOS管串联,所以Ineff=IDn1=IDn2=> kneff=kn/2=> kn/N 由于MOS管并联,所以Ineff=IDn1+IDn2=> kneff=2kn

VBS位置,产生效果

体效应因子r

F

MOS管的衬底偏置效应

r

2 0 Si qN C ox

A

CMOS电路版图设计对布线和接触孔的特殊要求 为抑制Latch up,要特别注意合理布置电源接触孔 和VDD引线,减小横向电流密度和横向电阻Rs、Rw

• 采用接衬底的环形VDD布线 • 增多VDD、VSS接触孔,加大接触面积,增加连线牢固性 • 对每一个VDD孔,在相邻阱中配以对应的VSS接触孔,以 增加并行电流通路 • 尽量使VDD、VSS接触孔的长边相互平行 • 接VDD的孔尽可能离阱近一些 • 接VSS的孔尽可能安排在阱的所有边上

寄生电阻:可用阻容网络等效(公式5-1) 随着器件电路尺寸按比例不断缩小,由互连系统产生的延迟已不容 忽略 边际电容效应 寄生沟道(场区)防治措施 寄生双极型晶体管 pnpn四层结构 等效电路 触发条件和防止措施

Latch-up效应

主要工艺流程

AL栅CMOS工艺(了解) 多晶硅栅NMOS工艺 硅栅CMOS工艺 P阱CMOS工艺流程 N阱CMOS工艺流程 双阱CMOS工艺流程

布线合理

布线面积往往为其它电路元器件总面积的几倍,在 多层布线中尤为突出

第五章-MOS集成电路版图设计

若 N L ,则有:

L

(Vout)

rc 2

L2

(5.3) (5.4) (5.5)

王向展

08.04.2020

6

集总 模型

集成电路原理与设计

集总模型即将整个长连线等效为 一总的R总、C总

图5.2 集总模型等效电路

(V o) u tR 总 C 总 dW L otx o L x W rcL 2

线间介质厚度;扩散层=1/(Nq) 。

r

d W

c ox W

tox

(5.1)

节点i的电位Vi响应与时间t的关系:

c L V i (V i 1 V i)(V i V i 1)

t

r L

(5.2)

王向展

08.04.2020

5

集成电路原理与设计

当L0,有:

r

c

dV dt

2V x2

近似处理,求解得:

(V ou ) t rc( L )2[N (N 21 )]

王向展

08.04.2020

11

集成电路原理与设计

5.1.3 寄生沟道

当互连跨过场氧区时,如果互连电位足够高,可能使场区 表面反型,形成寄生沟道,使本不应连通的有源区导通,造成 工作电流泄漏,使器件电路性能变差,乃至失效。

预防措施:

(1)增厚场氧厚度t´OX,使 V´TF,但需要增长场氧时间,

对前部工序有影响,并将造 成台阶陡峭,不利于布线。

王向展

图5.4 寄生沟道形成示意图

08.04.2020

12

集成电路原理与设计

(2)对场区进行同型注入,提高衬底浓度,使V´TF。但注

王向展

08.04.2020

10

MOS管及简单CMOS逻辑门电路原理图

MOS 管及简单CMOS 逻辑门电路原理图现代单片机主要是采用CMO 工艺制成的。

1、MOS 管 MOS 管又分为两种类型:N 型和P 型。

如下图所示:V DD45 Ic6=VssP 型MOS 管以N 型管为例,2端为控制端,称为“栅极”;3端通常接地,称为 “源极”;源极电压记作Vss , 1端接正电压,称为“漏极”,漏极电压记作VDD 要使1端与3端导通,栅极2上要加高电平。

对P 型管,栅极、源极、漏极分别为 5端、4端、6端。

要使4 端与6端导通,栅极5要加低电平。

在CMO 工艺制成的逻辑器件或单片机中,N 型管与P 型管往往是 成对出现的。

同时出现的这两个 CMO 管,任何时候,只要一只导通,另一只则 不导通(即“截止”或“关断”),所以称为“互补型—CMO 管”。

.2、CMO 逻辑电平高速CMO 电路的电源电压 VDD S 常为+5V; Vss 接地,是0V 。

高电平视为逻辑“ 1”,电平值的范围为:VDD 勺65%-VDD 或者VDD-1.5V 〜VDD低电平视作逻辑“ 0”,要求不超过 VDD 的35%或 0〜1.5V 。

+1.5 V 〜+3.5V 应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有 助于降低功耗。

VDD 为3.3V 的CMO 器件已大量使用。

在便携式应用中, VDC 为2.7V ,甚至1.8V 的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V , 但低于VDD 的 35%勺电平视为逻辑“ 0”,高于VDD 勺65%勺电平视为逻辑“ 1” 的规律仍然是适用的。

VDD VssV DD_ VssI 订]原理图非门(反向器)是最简单的门电路,由一对 CMOS 管组成。

其工作原理如 下: A 端为高电平时,P 型管截止,N 型管导通,输出端C 的电平与Vss 保持一 致,输出低电平;A 端为低电平时,P 型管导通,N 型管截止,输出端C 的电平 与V DD —致,输出高电平。

版图技术——CMOS集成电路的版图设计

(2)最小间距 例如,金属、多晶、有源区或阱都必须保持最小间距。 (3)最小包围 例如,N阱、N+离子注入和P+离子注入包围有源区应该有足够的余量;多晶硅、 有源区和金属对接触孔四周要保持一定的覆盖。

⑤ 完整的MOS管版版图必须包含两个部分:a)由源、栅和漏组成的器件;b) 衬底连接。

(a)PMOS管

(b)NMOS管 完整的MOS管版图图形

5.1.2 MOS管阵列的版图实现

1.MOS管串联

(1) 两个MOS管的串联。 N1的源、漏区为X和Y,N0的源、漏区为Y和Z。Y是它们的公共区域,如 果把公共区域合并,得到图5.7(d)所示的两个MOS管串联连接的版图。 从电流的方向可以决定,当MOS管串联时,它们的电极按S-D-S-D-S-D方 式连接。

① MOS管的四种布局图

② 直线形排列的NMOS管

结构图 立体结构和俯视图

③ 源区、沟道区和漏区合称为MOS管的有源区(Active),而有源区之外的区域 定义为场区(Fox)。有源区和场区之和就是整个芯片表面。 Fox + Active = Surface

芯片表面包含有源区和场区两部分

④ N阱CMOS集成电路使用P型衬底,NMOS管直接制作在P型衬底上,PMOS 管做在N阱内。

第5章 CMOS集成电路的版图 设计

主要内容 5.1 MOS 场效应管的版图实现 5.2 版图设计规则 5.3 版图系统的设置 5.4 版图的建立 5.5 版图的编辑 5.6 棍棒图 5.7 版图设计方法概述

5.1 MOS 场效应管的版图实现

5.1.1 单个MOS管的版图实现

《第五章MOS器件》PPT课件

• 对于MOSFET来说,最令人关注的是反型的 表面状态。当栅偏压VG 0时,P型半导 体表面的电子浓度将大于空穴浓度,形成 与原来半导体导电类型相反的N型导电层, 它不是因掺杂而形成的,而是由于外加电 压产生电场而在原P型半导体表面感应出来 的,故称为感应反型层。这一反型层与P型 衬底之间被耗尽层隔开,它是MOSFET的导 电沟道,是器件是否正常工作的关键。反 型层与衬底间的P-N结常称为感应结。

电荷。单位为C/cm2。 QGQS 0

• 由于Q0是不变的,因此

2021/4/27

实用文档

15

中国科学技术大学物理系微电子专业

6、半导体表面状态

2021/4/27

实用文档

16

积累:

电荷分布 QS

中国科学技术大学物理系微电子专业

积累情况下能带图及电荷分布

-d

x

Qm

EiEF

PP nie

kT

E(X) 电场分布 靠近氧化层的半导体表面

形成空穴积累

x

2021/4/27

实用文档

17

耗尽:

Vg>0

EF

2021/4/27

中国科学技术大学物理系微电子专业

Ec

Ei EF E

v

(x) Qm

电荷分布

wx -d

电场分布

QscqNAW

E(X)

实用文档

x

18

强反型:

中国科学技术大学物理系微电子专业

2021/4/27

np nieEFEik T

实用文档

氧化物陷阱电荷Qot:和SiO2的缺陷有关,分布在SiO2 层内,和工艺过程有关的Qot可以通过低温退火除掉 大部分。

可动离子电荷Qm:如Na+等碱金属离子,在高温和高 压下工作时,它们可以在氧化层内移动。因此,在

MOS管功率放大器电路图与原理图文及其解析

MOS管功率放大器电路图与原理图文及其解析放大器电路的分类本文介绍MOS管功率放大器电路图,先来看看放大器电路的分类,按功率放大器电路中晶体管导通时间的不同可分:甲类功率放大器电路、乙类功率放大器电路和丙类功率放大器电路。

甲类功率放大器电路,在信号全范围内均导通,非线性失真小,但输出功率和效率低,因此低频功率放大器电路中主要用乙类或甲乙类功率放大电路。

功率放大器是根据信号的导通角分为A、B、AB、C和D类,我国亦称为甲、乙、甲乙、丙和丁类。

功率放大器电路的特殊问题(1)放大器电路的功率功率放大器电路的任务是推动负载,因此功率放大电路的重要指标是输出功率,而不是电压放大倍数。

(2)放大器电路的非线形失真功率放大器电路工作在大信号的情况时,非线性失真时必须考虑的问题。

因此,功率放大电路不能用小信号的等效电路进行分析,而只能用图解法进行分析。

(3)放大器电路的效率效率定义为:输出信号功率与直流电源供给频率之比。

放大电路的实质就是能量转换电路,因此它就存在着转换效率。

常用MOS管功率放大器电路图MOS管功率放大器电路图是由电路稳压电源模块、带阻滤波模块、电压放大模块、功率放大模块、AD转换模块以及液晶显示模块组成。

(一)MOS管功率放大器电路图-系统设计电路实现简单,功耗低,性价比很高。

该电路,图1所示是其组成框图。

电路稳压电源模块为系统提供能量;带阻滤波电路要实现50Hz频率点输出功率衰减;电压放大模块采用两级放大来将小信号放大,以便为功率放大提供足够电压;功率放大模块主要提高负载能力;AD转换模块便于单片机信号采集;显示模块则实时显示功率和整机效率。

(二)MOS管功率放大器电路图-硬件电路设计1、带阻滤波电路的设计采用OP07组成的二阶带阻滤波器的阻带范围为40~60 Hz,其电路如图2所示。

带阻滤波器的性能参数有中心频率ω0或f0,带宽BW和品质因数Q。

Q值越高,阻带越窄,陷波效果越好。

2、放大电路的设计电压放大电路可选用两个INA128芯片来对微弱信号进行放大。

第五章 MOS集成电路的版图设计-2.

Vin (Polysilicon)

vdd N WELL

Pimp

Nimp

Nimp

Vout Pimp

CMOS 的反相器的橫截面圖與佈局(layout)圖

p管薄氧化区与n管薄氧化区的间距p阱cmos工艺版图设计规则图形设计规则及内容规则m原因阱区阱区阱的最小宽度9保证光刻精度和器件尺寸阱间的最小距离20防止不同电位阱间干扰有源区有源区最小宽度6保证器件尺寸减小窄沟效应最小间距6减小寄生效应阱内n有源区与阱最小间距9保证光刻精度和场区尺寸阱内p有源区与阱最小间距6保证形成良好的阱接触阱外n有源区与阱最小间距6保证阱和衬底间pn结的特性阱外p有源区与阱最小间距9抑制latchup多晶硅多晶硅最小线宽3保证器件特性和多晶硅电导保证器件特性和多晶硅电导最小间距3防止多晶硅联条硅栅在有源区外的最小露头4保证形成完整的mosfet硅栅与有源区最小内间距4保证电流在硅栅内的均匀流动保证电流在硅栅内的均匀流动多晶硅与有源区最小外间距2保证沟道区尺寸防短路注入注入对有源区最小覆盖3保证源漏区能完整地注入对外部有源区最小间距6防止p区n区互相影响注入区最小宽度6保证足够的接触区注入区最小间距3防止互相影响引线孔引线孔引线孔最小面积33保证孔的形成和良好接触孔间最小间距3保证良好接触孔距硅栅的最小间距3防止源漏与栅短路有源区多晶硅对孔的最小覆盖多晶硅对孔的最小覆盖2防止漏电和短路多晶硅接触孔与有源区的最小间距多晶硅接触孔与有源区的最小间距3防止漏电和短路金属金属金属引线的最小线宽3保证金属线的形成和良好导电保证金属线的形成和良好导电宽引线最小间距线宽10m线宽线宽10m36防止金属联条对引线孔的最小覆盖2保证接触和防止断路压焊点面积1102可靠接触压焊点间距90可靠接触钝化钝化金属对钝化孔的最小覆盖6可靠接触版图数据交换格式?通用格式

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

HMEC

集成电路设计原理

微电子中心

5.1.1 MOS管宽长比(W/L)的确定 VDD 1. NMOS逻辑门电路 (1)NMOS逻辑门电路是有比电路, ML 根据VOL的要求,确定最小R 。 Vi Vo 2 MI (VDD VTL ) VOL E/E饱和负载 2R(VOHVTI) VTD 2 VDD VOL 2 (V V ) E/D OH TE R MD (2) 根据负载CL情况和速度要求(tr Vo 和tf) 确定负载管和等效输入管的 ME Vi 最小W/L 。 4

21

HMEC

集成电路设计原理

微电子中心

5.2.3 优化设计 4. 复用单元的设计

将常用结构的 组合图形(包括电 路单元)按设计规 则要求设计为可复 用的单元,供设计 过程中调用, 减少设计错 误,并便于 修改。

Active Contact

Poly Via1 Contact

PAD

22

HMEC

集成电路设计原理

MOS管的源漏区具 有可互换性。

11

HMEC

集成电路设计原理

微电子中心

§5-2 版图的布局布线

12

HMEC

集成电路设计原理

微电子中心

思考题

1. 布局布线的策略是什么? 2. 复用单元设计有什么好处?

13

HMEC

集成电路设计原理

微电子中心

5.2.1 布局 1.布局的基本原则 芯片的布局设计是要解决电路图或逻辑 图中的每个元件、功能单元在版图中的位置 摆布、压焊点分布、电源线和地线以及主要 信号线的走向等。 首先确定电路中主要单元(元件)的位 置,再以主要单元为中心安置次主要单元和 次要单元。 相关单元(包括压点)要尽量靠近,以 主要单元为主调整单元(器件)的形状和位 置,方便布线,缩短布线。

Vi VDD n+ p+ RW p+ Vo n+ RS GND 25 n+ GND p+ VO IRs Rs Rw NIRw VDD

VO

P-

N-阱 P-Sub

HMEC

集成电路设计原理

微电子中心

5.3.2 抗闩锁设计的基本原则 (1)减小RS和RW :均匀且充分设计阱和衬 底的电源和地的欧姆接触,并用金属线连接, 必要时采用环结构。 (2)减小β npn和β pnp :加大MOS管源漏区 距阱边界的距离,必要时采用伪收集极结构。

HMEC

集成电路设计原理

微电子中心

第五章 MOS电路版图设计

1

HMEC

集成电路设计原理

微电子中心

§5-1 MOS管图形尺寸的设计

2ห้องสมุดไป่ตู้

HMEC

集成电路设计原理

微电子中心

思考题

1. MOS管沟道的宽长比(W/L)如何确定?

2. MOS管沟道的宽度(W)和长度(L)如何 确定? 3. MOS管源漏区尺寸如何确定?

8

HMEC

集成电路设计原理

微电子中心

5.1.2 MOS管沟道长度(L)的确定 (1)要考虑MOS管的耐压能力, 一般MOS管的击穿电压由源 漏穿通电压决定: W L

BVDSP=qNBL /2osi

(2)要考虑工艺水平。 (3)要考虑沟道长度调制效应对特性的影响。

9

2

HMEC

集成电路设计原理

微电子中心

HMEC

集成电路设计原理

微电子中心

5.4.3电阻-二极管保护电路 2. 版图示例

40

HMEC

集成电路设计原理

微电子中心

pad

5.4.4 MOS晶体管保护电路 1. 基本原理 利用保护管NMOS和 VDD PMOS的饱和导通或沟道穿 通效应以及漏极寄生二极管 MP 完成静电泄放。 R 保护管W/L要足够大以 便获得小的导通电阻,并采 MN 用抗闩锁的保护环结构。 R为N+电阻,起延迟、缓冲 VSS 作用。

14

HMEC

集成电路设计原理

微电子中心

5.2.1 布局 2.布局示例1 电子表芯片

液晶显示译码电路

定时电路

比较电路

走时电路

分频电路 振荡器

报 时 驱 动

调节控制电路

15

HMEC

集成电路设计原理

微电子中心

5.2.1 布局 2.布局示例2 存储器模块

读写 控制

输入输出

地址 译码

SRAM存储矩阵

16

HMEC

HMEC

集成电路设计原理

微电子中心

5.1.1 MOS管宽长比(W/L)的确定 1. NMOS逻辑门电路(续) VDD

(3) 根据静态功耗的要求 来确定负载管最大的W/L 。 (4) 根据上述结果最终 确定负载管和等效输 入管的W/L 。

(5) 根据输入结构和 等效输入管的W/L确 A 定每个输入管的W/L 。

集成电路设计原理

微电子中心

5.2.2 布线 1. 布线基本原则 最常用的布线层有金属、多晶硅和扩 散区,其寄生电阻和寄生电容有所不同。 电源线、地线选择金属层布线,线宽要 考虑电流容量(一般1mA/m)。 长信号线一般选择金属层布线,应尽量 避免长距离平行走线。 多晶硅布线和扩散区布线不能交叉而 且要短。必须用多晶硅走长线时,应同时 用金属线在一定长度内进行短接。

HMEC

集成电路设计原理

微电子中心

5.4.2 MOS电路抗静电设计思想 抗静电设计就是在电路的端口增设保 护电路,使得静电电荷形成的高压在到达 正常电路之前,通过保护电路将静电电荷 泄放掉,而保护电路自身也不被损坏。 (1)保护电路不能影响正常电路的功能; (2)保护电路放电电阻尽可能小; (3)放电回路能承受高的瞬态功耗; (4)保护电路应有抗闩锁能力; (5)保护电路占用尽可能小的芯片面积。

HMEC

集成电路设计原理

微电子中心

5.4.5双极晶体管保护电路 2.版图示例

44

5.1.3 MOS管沟道宽度(W)的确定

(1)根据已确定的W/L 和L的值来确定W的值。

(2)对于窄沟(长沟)器件,应根据工艺水平 先考虑确定沟道宽度W,然后再根据已确定 W/L的值来确定L的值。 L W

10

HMEC

集成电路设计原理

微电子中心

5.1.4 MOS管源漏区尺寸的确定

一般是根据MOS管的沟道宽度W和相 关的设计规则来确定源漏区最小尺寸。源 漏区尺寸越小,寄生电容以及漏电就越小。 对于W/L较大的器件一般采用叉指状 图形。

27

HMEC

集成电路设计原理

微电子中心

5.3.3 内部电路的抗闩锁设计 版图示例1

28

HMEC

集成电路设计原理

微电子中心

5.3.3 内部电路的抗闩锁设计 版图示例2

29

HMEC

集成电路设计原理

微电子中心

5.3.3 内部电路的抗闩锁设计 版图示例3

30

HMEC

集成电路设计原理

微电子中心

5.3.4 芯片外围电路的抗闩锁设计 外围电路主要是指输入/输出单元电路, 一方面易受高压影响,另一方面工作电流 很大。因此,极易发生闩锁效应,通常都 采用双环保护结构,而且保护环上要充分 开孔,用金属线直接连到电源或地上。

B

VDD

ML Vi MI VDD F MD

C

Vo

Vi

ME

Vo

5

HMEC

集成电路设计原理

微电子中心

5.1.1 MOS管宽长比(W/L)的确定 2. CMOS逻辑门电路 (1) 根据抗干扰能力(噪声容限、 Vi 输入转折电压V*)确定0范围。

VDD MP Vo MN

V* =

VDD+ VTP +VTN o 1 + o

HMEC

集成电路设计原理

微电子中心

5.4.3电阻-二极管保护电路 1. 基本原理(续) R2为N+电阻,起延迟、 VDD 缓冲作用,防止外来高 Dp1 电压直接作用于MOS管 MP pad R1 R2 的栅极。阻值一般在几 十左右。 MN Dn1 Dn2是R2形成的寄生二极 Dn2 管,起到进一步的保护 VSS 作用。 39

VDD A B

VDD MP Vo MN

F

7

HMEC

集成电路设计原理

微电子中心

5.1.1 MOS管宽长比(W/L)的确定 3. 传输门电路

(1)MOS的W/L直接影响传输门的导通电阻,

因而影响传输速度。因此,根据传输速

度的要求(考虑负载情况和前级驱动情

况)来确定MOS管的W/L.

(2) 对于CMOS传输门,一般应当考虑NMOS 管和PMOS管特性的对称性。

31

HMEC

集成电路设计原理

微电子中心

5.3.4 芯片外围电路的抗闩锁设计 双环结构示意图

地 P

电 源 N P P N阱

电 源 N

地 P

电 源 地 N P N N P衬底

地 P

电 源 N

32

HMEC

集成电路设计原理

微电子中心

5.3.4 芯片外围电路的抗闩锁设计

输出驱动单元局部版图示例

33

HMEC

微电子中心

5.2.3 优化设计 2. 器件排序优化 通过排序优化可以提高速度,减小漏电。

OUT OUT D A B C

A

D

B

C

OUT

OUT

GND

GND

20

HMEC

集成电路设计原理

微电子中心

5.2.3 优化设计 3. 宽沟器件的优化设计

(1)宽沟器件可以由 多个器件合成,方便 布局布线,减小栅极 电阻。 (2)宽沟器件源漏区 开孔要充分,提高沟 道特性的一致性(尤 其是模拟电路)。