16QAM调制解调系统设计的设计

基于FPGA的16QAM调制解调电路设计毕业设计(论文)

毕业设计(论文)设计(论文)题目:基于FPGA的16QAM调制解调电路设计摘要正交振幅调制(QAM)技术有着非常广泛的应用范围,不仅在移动通信领域应用,而且在有线电视传输、数字视频广播卫星通信(DVB-S)等领域也都得到广泛应用。

它在调制过程中利用了相位和幅度两维空间资源,比只利用单一维度空间资源的PSK和ASK调制方式频谱利用率高,不仅如此,QAM的星座点比PSK的星座点更分散,星座点之间的距离因此更大,所以能提供更好的传输性能。

本文在对QAM调制解调的基本原理、调制端的基带成形理论研究的基础上,通过Matlab 软件的Simulink仿真平台实现了16QAM调制解调系统的建立及实验验证。

之后利用Alera 公司的Quartus II软件加载ModelSim作为软件开发环境,设计并实现了16QAM调制解调系统的串并转换、差分和星座映射、DDS和加法器等关键模块。

关于载波信号发生器的设计,本文釆取传统DDS采用的正弦查表来实现DDS中相位幅度的转换。

本文主要研究了基于FPGA的16QAM调制与解调的实现。

釆用Verilog硬件描述语言对16QAM调制解调系统中的关键模块进行描述,完成了功能上的仿真验证,通过对比验证了设计的正确性,为下一步的硬件实现打下了很好的基础。

说明了QAM调制和解调的原理,,然后对各系统组成模块分析与仿真之后提出基于FPGA的16QAM调制与解调的总体设计方案。

最后用Verilog语言编写程序完成了整个系统的仿真,并对编好的程序其进行了编译调试。

首先对16QAM调制解调总体进行了系统仿真;然后用Verilog语言在Quartus II软件平台下完成了系统各功能模块的编写、功能与时序仿真和综合,最后把各模块组成的顶层原理图编译成的程序下载到EPMC20T100C5芯片上,手动输入基带信号,经过芯片处理后,基带信号得以有效恢复。

【关键词】正交振幅调制FPGA 调制解调现场可编程逻辑门阵列ABSTRACTQAM(Quadrature Amplitude Modulation) is a new modulation technique, because of the use of phase and amplitude two-dimensional space resources in the modulation process, it has a higher efficiency than PSK and ASK modulation witch use only a single dimension of space resources. Moreover, the QAM constellation points of PSK constellation points more dispersed, the distance between the constellation points is therefore, so it is able to provide better transmission performance. With the rise of third generation mobile communication and the transmission capacity increases, M-ary quadrature amplitude modulation of MQAM (Multiple quadrature the Amplitude Modulation) will be more widely used. This paper studies the realization of FPGA-based 16QAM modulation and demodulation. Firstly, the principle of QAM modulation is presented, and the modeling of the 16QAM modulation&demodulation system is built with the SystemView software.Then, by way of analyzing system composition modules and partial simulation, the design of the l6QAM modulation system based on FPGA is put forwards. Finally the whole system simulation is realized with Verilog, And programmed to compile debug. In this paper, the principle and design method of carrier recovery, quadrature coherent demodulator, FIR low pass filter and sampling and decision are detailedly introduced.Firstly, The system of 16QAM is simulated with SystemView. Then, each functional module is implemented with Verilog HDL on the Quartus II sofiware flat, and the function&timing simulation and the synthesis are finished. Finally, the program compiled from the top schematic diagram is downloaded to the EP2C35F672C6N chip and when manually entered the baseband signal, the signal can be effectively recovered.【Key words】Quadrature amplitude modulation FPGA modulation demodulation field programmable logic gate array目录前言.................................................................................................................................... - 1 - 第一章概述........................................................................................................................ - 3 - 第一节课题研究背景及意义......................................................................................... - 3 - 第二节QAM技术现状与发展 ...................................................................................... - 3 - 第三节本文内容和结构................................................................................................. - 5 - 第四节本章小结............................................................................................................. - 5 - 第二章QAM调制解调整体设计 ......................................................................................... - 6 - 第一节16QAM调制的方法和原理 .............................................................................. - 6 - 第二节16QAM解调方法和原理 .................................................................................. - 8 - 第三节本章小结............................................................................................................. - 9 - 第三章QAM调制器分模块设计 ....................................................................................... - 10 - 第一节FPGA概述 ....................................................................................................... - 10 - 第二节串/并转换模块.................................................................................................. - 12 - 第三节DDS载波和线性加法器模块.......................................................................... - 14 - 第四节差分编码和星座映射模块............................................................................... - 22 - 第五节时钟分频模块................................................................................................... - 25 - 第六节本章小结........................................................................................................... - 27 - 第四章QAM解调器分模块设计 ....................................................................................... - 28 - 第一节解调器顶层模块设计....................................................................................... - 28 - 第三节DDS载波恢复模块设计.................................................................................. - 33 - 第四节乘法器模块设计............................................................................................... - 37 - 第四节低通滤波器模块设计....................................................................................... - 38 - 第五节采样判决模块设计........................................................................................... - 39 - 第六节电平转换模块设计........................................................................................... - 41 - 第七节本章小结........................................................................................................... - 41 - 第五章调制解调系统的仿真............................................................................................ - 42 - 第一节仿真参数设置................................................................................................... - 42 - 第二节仿真结果........................................................................................................... - 42 -一、16QAM调制器的仿真结果 ........................................................................... - 42 -二、16QAM解制器的仿真结果 ........................................................................... - 46 -第三节仿真结果分析................................................................................................... - 50 - 第五节本章小结........................................................................................................... - 50 -结论.................................................................................................................................... - 52 - 致谢.................................................................................................................................... - 53 - 参考文献................................................................................................................................ - 54 - 附录.................................................................................................................................... - 55 -一、英文原文................................................................................................................. - 55 -二、英文翻译................................................................................................................. - 62 -三、源程序..................................................................................................................... - 68 -四、其他......................................................................................................................... - 74 -前言在许多领域现场可编程门阵列(FPGA)芯片都有广泛的应用,尤其是在数字通信领域当中,FPGA极强的实时性和并行处理能力能够完成对信号的实时处理。

MATLAB环境下16QAM调制及解调仿真程序说明

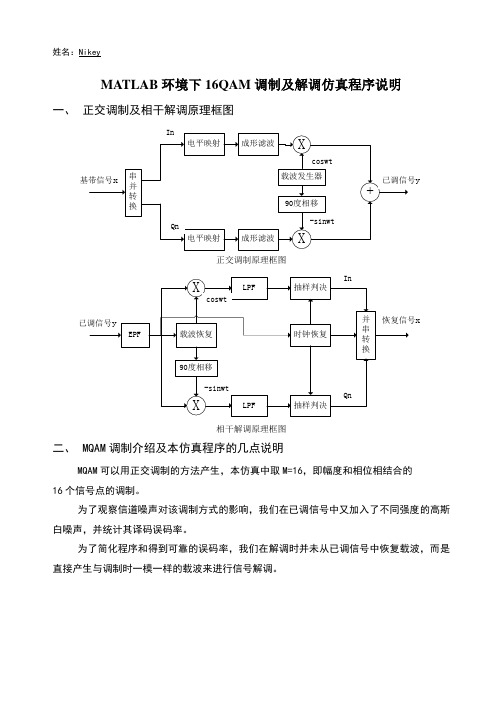

姓名:NikeyMATLAB环境下16QAM调制及解调仿真程序说明一、正交调制及相干解调原理框图正交调制原理框图相干解调原理框图二、MQAM调制介绍及本仿真程序的几点说明MQAM可以用正交调制的方法产生,本仿真中取M=16,即幅度和相位相结合的16个信号点的调制。

为了观察信道噪声对该调制方式的影响,我们在已调信号中又加入了不同强度的高斯白噪声,并统计其译码误码率。

为了简化程序和得到可靠的误码率,我们在解调时并未从已调信号中恢复载波,而是直接产生与调制时一模一样的载波来进行信号解调。

三、仿真结果图附源程序代码:clear;clc;echo off;close all;N=10000; %设定码元数量fb=1; %基带信号频率fs=32; %抽样频率fc=4; %载波频率,为便于观察已调信号,我们把载波频率设的较低Kbase=2; % Kbase=1,不经基带成形滤波,直接调制;% Kbase=2,基带经成形滤波器滤波后,再进行调制info=random_binary(N); %产生二进制信号序列[y,I,Q]=qam(info,Kbase,fs,fb,fc); %对基带信号进行16QAM调制y1=y; y2=y; %备份信号,供后续仿真用T=length(info)/fb; m=fs/fb; nn=length(info);dt=1/fs; t=0:dt:T-dt;subplot(211);%便于观察,这里显示的已调信号及其频谱均为无噪声干扰的理想情况%由于测试信号码元数量为10000个,在这里我们只显示其总数的1/10plot(t(1:1000),y(1:1000),t(1:1000),I(1:1000),t(1:1000),Q(1:1000),[0 35],[0 0],'b:'); title('已调信号(In:red,Qn:green)');%傅里叶变换,求出已调信号的频谱n=length(y); y=fft(y)/n; y=abs(y(1:fix(n/2)))*2;q=find(y<1e-04); y(q)=1e-04; y=20*log10(y);f1=m/n; f=0:f1:(length(y)-1)*f1;subplot(223);plot(f,y,'r');grid on;title('已调信号频谱'); xlabel('f/fb');%画出16QAM调制方式对应的星座图subplot(224);constel(y1,fs,fb,fc); title('星座图');SNR_in_dB=8:2:24; %AWGN信道信噪比for j=1:length(SNR_in_dB)y_add_noise=awgn(y2,SNR_in_dB(j)); %加入不同强度的高斯白噪声y_output=qamdet(y_add_noise,fs,fb,fc); %对已调信号进行解调numoferr=0;for i=1:Nif (y_output(i)~=info(i)),numoferr=numoferr+1;end;end;Pe(j)=numoferr/N; %统计误码率end;figure;semilogy(SNR_in_dB,Pe,'red*-');grid on;xlabel('SNR in dB');ylabel('Pe');title('16QAM调制在不同信道噪声强度下的误码率');%产生二进制信源随机序列function [info]=random_binary(N)if nargin == 0, %如果没有输入参数,则指定信息序列为10000个码元 N=10000;end;for i=1:N,temp=rand;if (temp<,info(i)=0; % 1/2的概率输出为0elseinfo(i)=1; % 1/2的概率输出为1endend;function [y,I,Q]=qam(x,Kbase,fs,fb,fc);%T=length(x)/fb; m=fs/fb; nn=length(x);dt=1/fs; t=0:dt:T-dt;%串/并变换分离出I分量、Q分量,然后再分别进行电平映射I=x(1:2:nn-1); [I,In]=two2four(I,4*m);Q=x(2:2:nn); [Q,Qn]=two2four(Q,4*m);if Kbase==2; %基带成形滤波I=bshape(I,fs,fb/4); Q=bshape(Q,fs,fb/4);end;y=I.*cos(2*pi*fc*t)-Q.*sin(2*pi*fc*t); %调制%QAM信号解调function [xn,x]=qamdet(y,fs,fb,fc);dt=1/fs; t=0:dt:(length(y)-1)*dt;I=y.*cos(2*pi*fc*t);Q=-y.*sin(2*pi*fc*t);[b,a]=butter(2,2*fb/fs); %设计巴特沃斯滤波器I=filtfilt(b,a,I);Q=filtfilt(b,a,Q);m=4*fs/fb; N=length(y)/m; n=(.6:1:N)*m; n=fix(n);In=I(n); Qn=Q(n); xn=four2two([In Qn]);%I分量Q分量并/串转换,最终恢复成码元序列xnnn=length(xn); xn=[xn(1:nn/2);xn(nn/2+1:nn)];xn=xn(:); xn=xn';%基带升余弦成形滤波器function y=bshape(x,fs,fb,N,alfa,delay);%设置默认参数if nargin<6; delay=8; end;if nargin<5; alfa=; end;if nargin<4; N=16; end;b=firrcos(N,fb,2*alfa*fb,fs);y=filter(b,1,x);%二进制转换成四进制function [y,yn]=two2four(x,m);T=[0 1;3 2]; n=length(x); ii=1;for i=1:2:n-1;xi=x(i:i+1)+1;yn(ii)=T(xi(1),xi(2));ii=ii+1;end;yn=; y=yn;for i=1:m-1;y=[y;yn];end;y=y(:)'; %映射电平分别为;;;%四进制转换成二进制function xn=four2two(yn);y=yn; ymin=min(y); ymax=max(y); ymax=max([ymax abs(ymin)]); ymin=-abs(ymax); yn=(y-ymin)*3/(ymax-ymin);%设置门限电平,判决I0=find(yn< ; yn(I0)=zeros(size(I0)); I1=find(yn>= & yn<; yn(I1)=ones(size(I1)); I2=find(yn>= & yn<; yn(I2)=ones(size(I2))*2; I3=find(yn>=; yn(I3)=ones(size(I3))*3; %一位四进制码元转换为两位二进制码元T=[0 0;0 1;1 1;1 0]; n=length(yn);for i=1:n;xn(i,:)=T(yn(i)+1,:);end;xn=xn'; xn=xn(:); xn=xn';%画出星座图function c=constel(x,fs,fb,fc);N=length(x); m=2*fs/fb; n=fs/fc;i1=m-n; i=1; ph0=(i1-1)*2*pi/n;while i <= N/m;xi=x(i1:i1+n-1);y=2*fft(xi)/n; c(i)=y(2);i=i+1; i1=i1+m;end;%如果无输出,则作图if nargout<1;cmax=max(abs(c));ph=(0:5:360)*pi/180;plot*cos(ph),*sin(ph),'c');hold on;for i=1:length(c);ph=ph0-angle(c(i));a=abs(c(i))/cmax*;plot(a*cos(ph),a*sin(ph),'r*');end;plot([ ],[0 0],'k:',[0 0],[ ],'k:');hold off; axis equal; axis([ ]);end;。

16QAM调制与解调

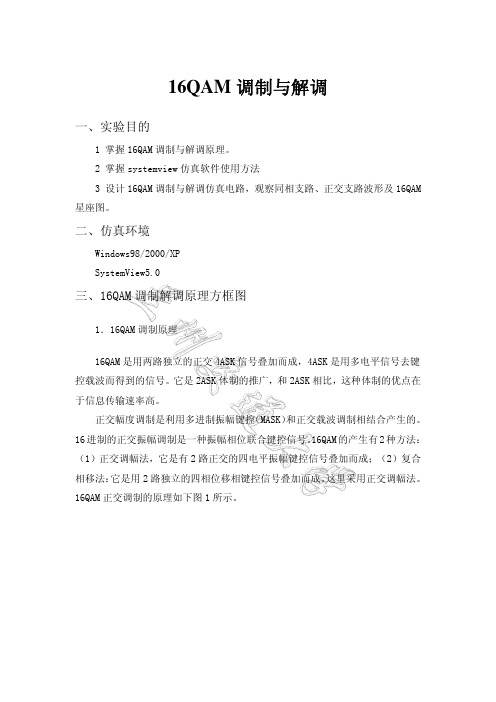

16QAM调制与解调一、实验目的1 掌握16QAM调制与解调原理。

2 掌握systemview仿真软件使用方法3 设计16QAM调制与解调仿真电路,观察同相支路、正交支路波形及16QAM 星座图。

二、仿真环境Windows98/2000/XPSystemView5.0三、16QAM调制解调原理方框图1.16QAM调制原理16QAM是用两路独立的正交4ASK信号叠加而成,4ASK是用多电平信号去键控载波而得到的信号。

它是2ASK体制的推广,和2ASK相比,这种体制的优点在于信息传输速率高。

正交幅度调制是利用多进制振幅键控(MASK)和正交载波调制相结合产生的。

16进制的正交振幅调制是一种振幅相位联合键控信号。

16QAM的产生有2种方法:(1)正交调幅法,它是有2路正交的四电平振幅键控信号叠加而成;(2)复合相移法:它是用2路独立的四相位移相键控信号叠加而成。

这里采用正交调幅法。

16QAM正交调制的原理如下图1所示。

图1 16QAM 调制器图中串/并变换器将速率为R b 的二进制码元序列分为两路,速率为R b /2.2-4电平变换为R b /2的二进制码元序列变成速率为R S =R b /log 216的4个电平信号,4电平信号与正交载波相乘,完成正交调制,两路信号叠加后产生16QAM信号.在两路速率为R b /2的二进制码元序列中,经2-4电平变换器输出为4电平信号,即M=16.经4电平正交幅度调制和叠加后,输出16个信号状态,即16QAM. R S =R b /log 216=R B /4.2.16QAM 解调原理16QAM 信号采取正交相干解调的方法解调,解调器首先对收到的16QAM 信号进行正交相干解调,一路与t c ωcos 相乘,一路与t c ωsin 相乘。

然后经过低通滤波器,低通滤波器LPF 滤除乘法器产生的高频分量,获得有用信号,低通滤波器LPF 输出经抽样判决可恢复出电平信号。

16QAM 正交相干解调如图2所示。

16QAM的调制与解调

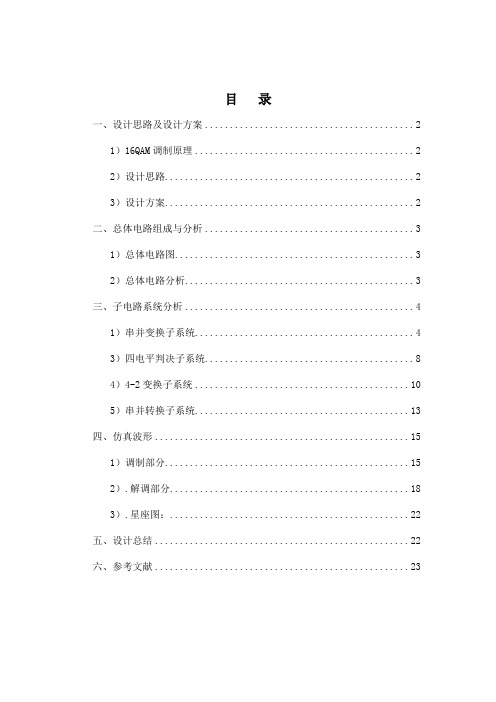

目录一、设计思路及设计方案 (2)1)16QAM调制原理 (2)2)设计思路 (2)3)设计方案 (2)二、总体电路组成与分析 (3)1)总体电路图 (3)2)总体电路分析 (3)三、子电路系统分析 (4)1)串并变换子系统 (4)3)四电平判决子系统 (8)4)4-2变换子系统 (10)5)串并转换子系统 (13)四、仿真波形 (15)1)调制部分 (15)2).解调部分 (18)3).星座图: (22)五、设计总结 (22)六、参考文献 (23)一、设计思路及设计方案1)16QAM调制原理在16QAM中,数据信号由相互正交的两个载波合成。

16QAM是一种矢量调制,将输入比特先映射(一般采用格雷码)到一个复平面(星座)上,形成复数调制符号,然后将符号的I、Q分量(对应复平面的实部和虚部,也就是水平和垂直方向)采用幅度调制,分别对应调制在相互正交(时域正交)的两个载波(coswt 和sinwt)上,然后两路正交信号相加得到调制信号。

2)设计思路16-QAM信号,每个样点表示一种矢量状态,16-QAM有16态,每4位二进制数规定了16态中的一态,16-QAM中规定了16种载波和相位的组合,16-QAM的每个符号和周期传送4比特。

16进制的正交振幅调制是一种振幅相位联合键控信号。

16QAM的产生有2种方法:(1)正交调幅法,它是有2路正交的四电平振幅键控信号叠加而成;(2)复合相移法:它是用2路独立的四相位移相键控信号叠加而成。

这里采用正交调幅法。

3)设计方案首先,伪随机码发生器产生速率为Rb的二进制序列,此二进制码流经串一并变换器将分成两个速率为Rb/2的两电平序列,2一4电平变换器将每个速率为Rb/2的两电平序列变成速率为Rb/4,4电平信号,然后分别与两个正交的载波相乘,相加后即产生QAM信号。

QAM信号的解调器同样可以采用正交的相干解调方法。

同相I路和正交Q路的4电平基带信号用判决器判决后,分别恢复出速率等于Rb/2的二进制序列,最后经并一串变换器将两路二进制序列合成一个速率为Rb的二进制序列。

基于FPGA的16QAM调制解调

基于FPGA的16QAM调制解调器的实现组员:目录摘要3一、QAM调制原理3二、QAM的解调原理4三、16QAM调制器的实现51 系统总体框图 52 时钟分频 63 串并转换 64 差分编码和星座映射 65 DDS和线性加法器7四、QAM解调模块设计71 低通滤波器模块设计72 采样判决模块设计8五、16QAM调制器的仿真结果9四、附录121 顶层模块122 时钟分频模块133 串并转换模块144 差分模块和星座映射模块155 DDS 和加法器模块176 testbench 源程序227 用matlab 进行频谱分析23摘要QAM(Quadrature Amplitude Modulation)是一种新的调制技术,它在调制过程中利用了相位和幅度两维空间资源,比只利用单一维度空间资源的PSK 和ASK 调制方式频谱利用率高,不仅如此,QAM 的星座点比PSK 的星座点更分散,星座点之间的距离因此更大,所以能提供更好的传输性能。

随着第三代移动通信的兴起,传输容量增大,多进制正交幅度调制MQAM (Multiple Quadrature Amplitude Modulation)将得到更加广泛的运用。

本文主要研究了基于FPGA 的16QAM 调制与解调的实现。

首先说明了QAM 调制和解调的原理,然后对各系统组成模块分析与仿真之后提出基于FPGA 的16QAM 调制与解调的总体设计方案。

最后用Verilog 语言编写程序完成了整个系统的仿真,并对编好的程序其进行了编译调试。

文中详细介绍了载波恢复、正交相干解调、FIR 低通滤波器和采样判决的基本原理和设计方法。

关键词:正交相干解调,混频,FPGA ,QAM一、QAM 调制原理正交幅度调制(QAM)是一种把数字信息包含在载波的振幅和相位中的数字调制方式,也是ASK 和PSK 的结合。

式(1)表示了QAM 信号,它还可用式(2)来表示在QAM 中是如何结合幅度和相位调制的。

16QAM调制与解调的MATLAB实现及调制性能分析

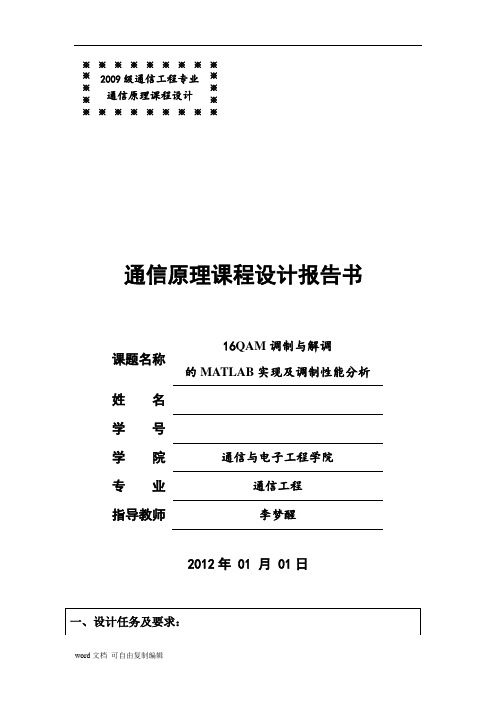

通信原理课程设计报告书课题名称16QAM 调制与解调的MATLAB 实现及调制性能分析姓 名学 号 学 院 通信与电子工程学院专 业 通信工程 指导教师李梦醒2012年 01 月 01日※※※※※※※※※ ※※ ※※ ※※ ※※※※※※※※※2009级通信工程专业通信原理课程设计16QAM调制与解调的MATLAB实现及调制性能分析(1) 掌握16QAM 调制与解调的原理。

(2) 掌握星座图的原理并能熟悉星座图的应用。

(3) 熟悉并掌握MATLAB 的使用方法。

(4) 通过对16QAM 调制性能的分析了解16QAM 调制相对于其它调制方式的优缺点。

2 设计原理正交振幅调制(Quadrature Amplitude Modulation,QAM )是一种振幅和相位联合键控。

虽然MPSK 和MDPSK 等相移键控的带宽和功率方面都具有优势,即带宽占用小和比特噪声比要求低。

但是由图1可见,在MPSK 体制中,随着8/15π图 1 8PSK 信号相位M 的增大,相邻相位的距离逐渐减小,使噪声容限随之减小,误码率难于保证。

为了改善在M 大时的噪声容限,发展出了QAM 体制。

在QAM 体制中,信号的振幅和相位作为两个独立的参量同时受到调制。

这种信号的一个码元可以表示为0()cos() (1)k k k s t A t kT t k T ωθ=+<≤+ (2—1)式中:k=整数;k A 和k θ分别可以取多个离散值。

式(2—1)可以展开为00()cos cos sin sin k k k k k s t A t A t θωθω=- (2—2)令 X k = A k cos θk , Y k = -A k sin θk 则式(2—1)变为00()cos sin k k k s t X t Y t ωω=+ (2—3)8/5π8/3π8/π8/7π8/9π8/11π8/13πk X 和k Y 也是可以取多个离散的变量。

基于simulink的16QAM调制解调系统的设计本科毕业设计论文

基于simulink的16QAM调制解调系统的设计本科毕业设计论文摘要16进制正交振幅调制技术(16QAM)是一种功率和带宽相对高效的信道调制技术,这种方式具有很高的频谱利用率,在调制进制数较高时,信号矢量集的分布也较合理,同时实现起来也较方便。

因此在大容量数字微波通信系统、有线电视网络高速数据传输、卫星通信系统等领域得到了广泛应用。

所以,16QAM应用起来容易实现,并有抗噪声性能强的优点。

本文首先研究了QAM调制解调系统的工作原理。

然后利用Simulink对16QAM调制系统进行仿真,通过分析信号加噪前后的星座图、眼图,以及信噪比变化条件下系统的误码率,从而分析16QAM系统性能。

最后,为了证明16QAM是一种相对优越的调制解调系统,使其与2DPSK的误码率做比较。

通过仿真实验的实现,证明了该系统满足设计要求,能够完成其系统的仿真,并能通过眼图、星座图、误码率来验证系统的性能。

关键词: 16QAM 仿真 2DPSK 误码率AbstractHexadecimal orthogonal amplitude modulation technology (16 QAM) is a kind of power and bandwidth relatively efficient channel modulation technology, this kind of means is of high frequency spectrum efficiency in the modulation system into several high, the distribution of the signal vector set more reasonable also realize rise more convenient also.It has been used widely in field of large-capacity digital microwave communication systems high-speed data transmission cabletelevision network and satellite communications.So,16QAM application up easy to implement and have the advantages of the strong performance of the noise.This article briefly introduce how QAM modulation and demodulation system works. After a simulation of the 16QAM modulation system ,through the analysis of signal is added a noise of the constellation chart, before and after eye chart ,and signal-to-noise ratio change conditions the system BER,so as to analyze 16QAM and system performance.Finally,in order to prove that the 16QAM is a relatively superior demodulation system,makeits and 2DPSK BER compare.Through the simulation test the system to satisfy the design requirements can perform its system simulation and through the eye chart constellation chart BER to verify the performance of the system.Keywords: 16QAM Simulation 2DPSK BER目录第1章绪论 .......................................... 1 1.1 课题研究背景 .................................... 1 1.2 国内外研究现状 .................................. 2 1.3 主要研究内容 .................................... 3 第2章正交振幅调制 ................................... 4 2.1 正交振幅调制的概述 .............................. 4 2.2 MQAM信号的星座图................................ 6 2.3 QAM的调制解调原理 ............................... 9 第3章基于Simulink的16QAM调制解调系统实现与仿真 .. (11)3.1 16QAM调制模块的模型建立与仿真 (13)3.1.1 信号源 (13)3.1.2 串并转换模块 (13)3.1.3 2/4电平转换模块 (15)3.1.4 调制系统的实现 ............................. 18 3.2 16QAM解调模块的模型建立与仿真 (19)3.2.1 相干解调 (19)3.2.2 4/2电平判决 (20)3.2.3 并串转换 ................................... 21 第4章 16QAM系统性能分析 .. (24)I4.1 眼图 .......................................... 24 4.2 星座图 ........................................ 26 4.3 误码率 ........................................ 29 4.4 16QAM与2DPSK系统性能比较 . (31)第5章 16QAM的应用 .................................. 33 第6章结论与总结 .................................... 35 6.1 本文总结....................................... 35 6.2 不足与展望 ..................................... 36 参考文献 ............................................. 38 致谢 ................................................. 40 附录 ................................................. 42 附录A 外文资料 (42)II石家庄铁道大学四方学院毕业设计第1章绪论1.1 课题研究背景当今,通信技术的发展日新月异,通信系统也日趋复杂,因此在各种通信系统的设计研发环节中, 软件仿真已成为必不可少的部分。

基于FPGA的16QAM调制解调器设计与实现

基于FPGA的16QAM调制解调器设计与实现随着无线通信技术的发展,调制解调器在通信系统中起着至关重要的作用。

本文将介绍基于FPGA的16QAM调制解调器的设计与实现。

首先,我们将简要介绍16QAM调制解调器的基本原理,然后详细阐述设计过程,最后通过实验结果进行验证。

一、基本原理16QAM调制解调器是采用16进制的星座图为基础的调制解调器。

在调制过程中,将每个符号映射到星座图的不同点上。

具体而言,16QAM将4个比特位视为一组,分为实部和虚部两个4QAM信号,然后通过串行并行转换将信号映射为星座图上的点。

在解调过程中,采用最小距离法将接收到的信号重新映射到星座图中的最近点,并通过并行串行转换恢复原始信号。

二、设计过程(一)信号生成在FPGA中,通过数字信号发生器生成16QAM的调制信号是必要的。

设计中,我们可以使用DDS(Direct Digital Synthesis,直接数字合成)技术生成16QAM信号的I路和Q路的调制信号。

通过设定合适的相位和幅度,可以生成星座图上的16个不同点的信号。

(二)星座图映射设计中,我们需要将生成的信号映射到星座图上。

我们可以使用查找表的方法,将每个4比特组合对应到一个星座点,然后通过串行并行转换将映射后的信号转化为并行格式。

(三)调制器实现调制器的实现可以使用乘法器和加法器来完成。

将映射后的I路和Q路调制信号与载波信号相乘,并将得到的结果相加即可得到调制后的信号。

最后将得到的信号进行滤波,以去除高频部分。

(四)解调器实现解调器的实现相对复杂一些。

首先,接收到的信号需要经过一低通滤波器,以去除高频部分。

然后,使用最小距离法将滤波后的信号重新映射到星座图上的最近点。

最后,通过对解调后的I路和Q路信号进行串行并行转换,恢复原始信号。

三、实验验证为了验证设计的正确性,我们使用FPGA开发板进行实验。

将设计好的16QAM调制解调器烧录到FPGA中,并通过示波器观察输出信号的波形和星座图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

资料《通信原理及系统课程设计》报告二○一一~二○一二学年第二学期学号091603048姓名张薇班级通信Q0941电子工程系设计任务书【设计题目】16QAM调制与解调系统的设计【设计目的】通过此综合设计,加深基本理论知识的理解,加强理论联系实际,增强动手能力,提高通信系统仿真的设计技能。

【设计内容】1.设计任务:利用所学通信知识,设计一个16QAM调制与解调系统,并用SystemVIEW进行仿真和分析,从而实现理论联系实际的作用。

2.基本要求:(1)用码元速率为19.2Kb/s的随机序列作为实验系统的信号源;(2)用频率为76.8kHz的正交信号作为实验系统的载波信号;(3)用9.6Kb/s的方波信号及其正交信号,作为抽样判决的时钟信号,抽样频率为384kHz;(4)保证串/并变换、并/串变换的正确性;(5)对完成的系统进行性能仿真,加入噪声电压,分析其输出性能。

【提交要求】1.打印设计报告,内容包括:(1)设计思路及设计方案;(1)系统的基本原理框图以及每一个模块的作用;(2)系统设计过程中,每一个用到的图符中主要参数的意义;(3)每一个用到的图符主要参数的设定和设定的依据;(4)仿真系统参数改变时,给仿真结果带来的影响(如高斯白噪声信道的信噪比增加,则误码率减小);(5)仿真的结果(波形截图,总体分析评价等)。

2.仿真程序(需要加注释)。

目录一、设计思路 (5)二、总体方案设计 (5)1、调制方案 (5)2、解调方案 (6)三、总体电路图 (7)四、模块设计及主要参数设置 (7)1、串/并转换 (8)2、低通滤波 (8)3、抽样判决 (9)4、并/串转换 (10)五、仿真结果及分析 (11)1.仿真参数设置 (11)2、仿真结果 (12)3、仿真结果分析 (16)六、小结 (16)一、设计思路16QAM即16进制正交振幅调制,它是一种振幅/相位联合键控(APK)体制。

16QAM的产生有2种方法:(1)正交调幅法,它是有2 路正交的四电平振幅键控信号叠加而成;(2)复合相移法:它是用2路独立的四相位移相键控信号叠加而成。

16QAM信号的振幅和相位作为两个独立的参量同时受到调制。

故这种信号序列的第k个码元可以表示为:S k(t)=A k cos(w0t+φk) kT<t≤(k+1)T (1-1) 式中,k=整数;A k和φk分别可以取多个离散值。

式(1-1)可以展开为:S k(t)=A k cosφk cosw0t-A k sinφk sinw0t (1-2) 令X k=A k cosφk (1-3)Y k=-A k sinφk (1-4) 将式(1-3)和式(1-4)代入式(1-2)得:S k(t)=X k cosw0t+Y k sinw0t (1-5) 由上式可见,16QAM信号可以由两路独立的正交4ASK信号叠加而成,因此,这里采用正交调幅法。

正交幅度调制是利用多进制振幅键控(MASK)和正交载波调制相结合产生的。

二、总体方案设计1、调制方案为了方便产生两路4ASK 信号,这里将基带信号设置成速率为R b 的四进制码元序列。

然后经过串/并转换模块,将该四进制基带码元序列分成两路速率分别为R b /2的四电平信号,再将这两路四电平信号分别与正交载波相乘,完成正交调制,两路信号叠加后产生16QAM 信号。

2、解调方案 16QAM 信号采取正交相干解调的方法解调,解调器首先对收到的16QAM 信号进行正交相干解调,一路与sinw0t 相乘,一路与cosw0t 相乘,然后经过低通滤波输出两路多电平基带信号A(t)和B(t),用门限电平的判决器判决后分别恢复出两路速率为R b /2的四进制序列。

最后经并/串转换模块将两路四进制序列组合成一个四进制序列。

至此,完成16QAM 的解调。

R R coco三、总体电路图图3-1 16QAM调制与解调系统总体电路图四、模块设计及主要参数设置1、串/并转换串/并转换实现的功能是将码元速率为19.2Kb/s的四进制基带码元序列分成两路,其中一路信号可通过直接用采样频率为9600HZ的采样器对该四进制基带码元序列进行采样获得。

要获得另外一路信号,需要先将该四进制基带码元序列延时一个码元周期,再用采样频率为9600HZ的采样器采样。

为了使这两路信号在时间上同步,还需要将第一路信号也延时一个码元周期。

这样就将原四进制基带码元序列分成两路速率相同的四电平信号。

具体电路图如下:图4-1 串/并转换模块电路图(1)采样器的采样速率为9600,采样点时间宽度为0,采样时间偏差0.(2)采样延迟的延迟点数为1.2、低通滤波这里的滤波器选用巴特沃斯低通滤波器,为了将本地载波滤除,从而得到基带信号,设置截止频率为40KHZ.图4-2低通滤波器的参数3、抽样判决抽样判决要实现的功能是将低通滤波输出的不规则波形通过抽样判决,得到规则的方波序列。

如上图所示,低通滤波输出信号的四个电平大致分别为:-1.5V,-0.5V,0.5V,1.5V. 据此设计出一种判决方案,对于每一路信号都进行三次判决。

具体电路图如下:图4-3 抽样判决电路图(1)第一路信号参数第一次判决:阈值电压设置为-1V,当输入电压大于-1V时输出为-0.5V,否则输出为-1.5V;第二次判决:阈值电压设置为0V,当输入电压大于0V时输出为1V,否则输出为0V;第三次判决:阈值电压设置为1V,当输入电压大于1V时输出为1V,否则输出为0V。

(2)第二路信号的判决方法同第一路信号。

4、并/串转换并串转换是串并转换的逆过程,并串转换的目的是将两路四电平信号合成一路四电平信号,从而还原出原基带序列。

具体方法是:用一个频率为9600HZ,脉冲宽度为其周期的一半的脉冲串分别与这两路四电平信号相乘进行采样,并将第二路信号延时一个脉冲宽度。

然后将这两路信号相加,再经过采样保持即恢复原基带序列。

具体电路图如下:图4-4 并串转换模块电路图(1)采样脉冲串的幅度为1V,频率为9600HZ,脉冲宽度为52.08×10-6,偏置为0,相位为0。

(2)延迟器的延迟时间为52.08×10-6。

(3)采样器的采样速率为19200,采样点时间宽度为0,采样时间偏差0。

(4)采样保持器的增益为2。

五、仿真结果及分析1.仿真参数设置(1)信号源参数设置,幅度为3V,频率为19200HZ,电平数为4,偏置为0,相位为0。

(2)系统抽样频率设置,为得到准确的仿真结果,通常仿真系统的抽样频率应大于等于10倍的载频。

本次仿真采样点数取3000,采样频率取384KHZ,采样频率间隔为128HZ。

(3)系统时间设置:通常设系统Start time=0。

为能够清晰观察同相支路和正交支路中每个码元波形及16QAM信号的星座图,在仿真时对系统Stop time 必须进行两次设置,第一次设置一般取系统Stop time=6T~8T,这时可以清楚地观察到同相支路和正交支路中每个码元波形;第二次设置一般取系统Stop time=1000T~5000T,这时可以清楚地观察到16QAM信号的星座图。

(4)高斯白噪声:功率谱密度为0.3,均值为0。

2、仿真结果(1)基带信号波形(2)串并转换输出波形(3)低通滤波输出波形(4)判决输出波形(5)并串转换输出(6)16QAM星座图3、仿真结果分析(1)从图中基带信号波形和并串转换输出波形图可以看出,最后解调出来的波形和原基带信号波形大致相同(有一些延时)。

可见,该16QAM调制与解调系统设计基本正确。

(2)低通滤波器输出波形与并串转换输出波形大致形同,且边缘陡峭,但有一些毛刺,可见解调系统能够较好的解调出由调制端输入的两路四电平信号。

(3)判决输出波形为规则的方波信号,信号的波形与低通滤波器输出波形相同,可见抽样判决模块设计正确。

(4)信号矢量端的分布图称为星座图,这里用低通滤波器输出波形的星座图来描述16QAM信号的空间分布情况,从图中可以看出由于受高斯白噪声,低通滤波器等的影响,使接收16QAM信号的相位有所偏移,但还是围绕调制时的16个相位点。

六、小结经过这次16QAM调制与解调系统的设计,我对SystemVIEW仿真软件的认识进一步加深,并且可以熟练的运用基本库中的元件,不再像刚接触时那样要很长时间才能找到所需要的元件。

同时,我对16QAM调制与解调原理有了比较透彻的认识与理解。

刚开始拿到这可课题的时候我没有思路,后来通过与同学互相讨论,还有网上查阅相关资料思路才渐渐清晰。

但是后来在具体实现的过程中又遇到许多困难,例如在设计并串转换模块的过程中,刚开始我是借鉴的网上一个文档的方案,那个方案比较复杂,还涉及到具体延时时间的设定,我反复的设定参数还是得不到理想的四电平信号和星状图,后来通过自己认真思考才发现,其实串并转换没有那么复杂,可以直接对基带信号采样,延时得出一路信号,然后延时,采样得出另外一路信号。

这使我明白,在做设计的时候,不能原原本本的照搬别人的方案,自己首先要理清思路,在弄懂设计原理的基础上寻求最佳方案。

另外,系统中各元件的参数有时也不一定就是理论值,往往要经过反复的试验,才能得出理想的波形,如低通滤波器截止频率的设定等。

本次设计还有很多不足和待完善的地方,例如基带信号本应该选择二进制码元序列,但是这里我为了避免设计二四电平转换和四二电平转换,选择四进制码元序列作为基带信号。

最后调制出来的波形的前几个码元与基带序列不一样,可能是由于前面的串并转换,低通滤波和并串转换设置的不太理想。

总之,这次16QAM调制与解调系统的设计使我学到了很多东西。

我的逻辑思维能力,分析问题,解决问题的能力得到提高。

同时,还要感谢帮助过我的同学们在我遇到挫折的时候细心地帮助我分析解决问题。