ARM体系结构综述

第2章 ARM体系结构

• 控制位

–

程序状态寄存器PSR(Program Status Register)的最低8位I、F、T和 M[4:0]用作控制位。当异常出现时改变控制位。处理器在特权模式 下时也可由软件改变。

• 中断禁止位 I:置1,则禁止IRQ中断; F:置1,则禁止FIQ中断。 • T位 T=0 指示ARM执行; T=1 指示Thumb执行。 • 模式控制位 M4、M3、M2、Ml和M0(M[4:0])是模式位,决定处理器 的工作模式,如表2.3.1所列。

6 (最低)

6 5

数据中止

IRQ (外部中断请求) FIQ (快速中断请求)

中止(数据)

IRQ FIQ

中止模式

IRQ FIQ

0x0000,0010

0x0000,0018 0x0000,001C

2

4 3

2.4.2 异常类型的含义

(1)复位

• • 处理器的复位电平有效时,产生复位异常 当ARM处理器或协处理器遇到不能处理的指令时,产生未定义指令异常

2.4 ARM微处理器的异常处理

• 异常:在一个正常的程序流程执行过程中,由内 部或外部源产生的一个事件使正常的程序产生暂 时的停止,称之为异常。

2.4.1 ARM体系结构的异常类型

• ARM体系结构支持7种类型的异常

• 异常出现后,强制从异常类型对应的固定存储器地址开始 执行程序。这些固定的地址称为异常向量(Exception Vectors)。

M[4:0]模式控制位

M[4: 0] 10000 10001 10010 10011 10111

处理器工作 模式 用户模式 FIQ模式 IRQ模式 管理模式 中止模式

可访问的寄存器 PC,CPSR,R14~R0 PC,R7~R0,CPSR, SPSR_fiq,R14_fiq~ R8_fiq PC,R12~R0,CPSR, SPSR_irq,R14_irq, R13_irq PC,R12~R0, CPSR, SPSR_svc,R14_svc, R13_svc PC,R12~R0, CPSR, SPSR_abt,R14_abt, R13_abt

ARM体系架构解析ppt课件

2)提供了较大的存储器带宽,各自有自己的

总线。

3)适合于数字信号处理.

4)大多数DSP都是哈佛结构.

5)ARM9是哈佛结构

6)取指和取数在同一周期进行,提高速度,

改进哈佛体系结构分成三个存储区:程序、数据、

程序和数据共用。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

6)将结果回写到寄存器组(res)

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

流水线技术

❖

三级流水线技术

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

因此,把它称为流水线工作方式。

处理器按照一系列步骤来执行每一条指令。典

型的步骤为:

1)从存储器读取指令(fetch)

2)译码以鉴别它是哪一类指令(dec)

3)从寄存器组取得所需的操作数(reg)

4)将操作数进行组合以得到结果或存储器地址(exe)

5)如果需要,则访问存储器存取数据(mem)

冯·诺依曼体系的特点

1)数据与指令都存储在同一存储区中,取指

令与取数据利用同一数据总线。

❖ 2)被早期大多数计算机所采用

❖ 3)ARM7——冯诺依曼体系

❖

结构简单,但速度较慢。取指不能同时取数据

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

ARM体系结构详解精

ARM嵌入式系统第2章ARM体系结构ARM微处理器的编程模型♦ARM徴处理器的工作状态♦ARM体系结构的存储器格式♦ARM体系结构的指令长度及数据宽度♦ARM微处理器的处理器模式♦ARM体系结构的寄存器组织♦ARM微处理器的异常状态字、半字、字节字(Word)在ARM体系结构中,字的长度为32位半字(Half-Word)在ARM体系结构中,半字的长度为16位字节(Byg)在ARM体系结构中,字节的长度为8位。

ARM微处理器的工作状态(1)字对齐:四字节对齐半字对齐:两字节对齐两种状态:♦ARM状态:处理器执行32位的字对齐的令♦Thumb状态:处理器执行16位的、半字对齐的Thumb指令处理器工作状态的转变并不影响处理器的工作模式和相应寄存器中的内容。

I ARM微处理器的工作状态(2 )状态切换:BX {<cond>} <Rm><cond>指令的条件码。

忽略时无条件执行。

<Rm>子存器中为跳转的目标地址,当<Rm><存器的bit[O]为0时, 目标地址处的指令为ARM指令;当<Rm>^存器的bit[O]为1时,目标地址处的指令为Thumb 指令。

伪代码:if ConditionPassed(cond) thenT Flag=Rm[O]PC=Rm AND OxFFFFFFFEARM微处理器在复位或上电时处于ARM状态,发生异常时处于ARM状态。

右ARM体系结构的存储器格式(1)ARM体系结构所支持的最大寻址空间为4GB (2^字节)♦大端格式(Big Endian)字数据的高字节存储在低地址中,而字数据的低字节则存放在高地址中。

♦小端格式(Little Endian)低地址中存放的是字数据的低字节,高地址存放的是字数据的高字节。

字地址字地址右ARM 体系结构的存储器格式(2)(0H)=0123H (4H)=4567H (8H)=89ABHBig Endian(0H)=3210H (4H)=7654H (8H)=BA98HLittle Endian右ARM 体系结构的存储器格式(3)8 9 AB4 5 6 7 0123一 “A ・■ • rO= 0x11223344 I 11 I 22 33 : 44 ILittle endian Big endianR2 =异FI*右 ARM 体系结构的指令长度及数据宽度♦指令长度:32位(在ARM 状态下) 16位(在Thumb 状态下)♦数据宽度: 字节(8位) 半字(16位) 字(32位)三种数据宽度对存储器及外部设备的访问。

ARM体系结构与编程

ARM体系结构与编程

一、ARM体系结构

ARM(Advanced RISC Machine)是由英国ARM公司开发的一种低功耗、超低成本的处理器架构,是移动设备的首选处理器。

ARM架构的处理器有ARM7、ARM9、ARM11、 Cortex-A8 、Cortex-A15等,它们核心架构特点为以下几点:

1.保护模式。

ARM架构的处理器能够在用户模式和两个高级的保护模式之间来回切换。

2.对齐式存储。

ARM架构的处理器采用对齐方式,其二进制指令必须按照固定的位置排列,以便提高存储空间的利用率。

3.浮点处理单元。

ARM架构的处理器具有浮点数处理功能,使数值运算能够高效率地完成。

4.多级缓存。

ARM架构的处理器将原始数据复制到不同级别的快速缓存中,以便快速访问。

二、ARM程序的编程

1、ARM程序的编写

ARM程序的编写可以使用C语言编写,程序开发者需要掌握ARM架构各种中央处理器扩展指令集的使用方法,以便获得更好的效率。

2、编译ARM程序

ARM程序的编译是使用GNU的gcc编译器进行的,它可以将C语言编写的程序编译成ARM架构的机器码,并可以在ARM架构的处理器上运行。

3、调试ARM程序

ARM程序的调试使用GDB程序调试,它可以提供丰富的调试工具,可以跟踪程序执行的步骤,提供全面的程序反馈信息,可以帮助开发者快速定位程序运行出错的地方。

三、总结。

ARM体系结构

ARM9TDMI处理器一个显著的特点是采用 指令和数据分离访问的方式,即采用了指令 缓存(I-Cache)和数据缓存(D-Cache)。 这样可以把指令访问和数据访问单独安排1级 流水线。

2015/9/28

9

ARM9处理能力的提高是通过增加时钟频率和减少指令执行周期实 现的。 (1)时钟频率的提高 ARM9采用了五级流水线,而ARM7采用的是三级流水线,ARM9增 加的流水线设计提高了时钟频率和并行处理能力。五级流水线能够将各 条指令处理分配到5个时钟周期内,在每个时钟周期内同时有5条指令在 执行。在同样的加工工艺下,ARM9 TDMI处理器的时钟频率是ARM7 TDMI的2倍左右。 (2)指令周期的改进 指令周期的改进有助于处理器性能的提高。性能提高的幅度依赖于 代码执行时指令的重叠。 ① load指令和store指令 指令周期数改进最明显的是load指令和store指令。 ② 互锁(interlock)技术 当指令需要的数据因为以前的指令没有执行完,将产生管道互锁。管

操作系统的保护模式 指令或数据预取操作中止时的模 式,该模式下实现虚拟存储器或 存储器保护 当执行未定义的指令时进入该模 式 响应普通中断时的处理模式

未定义模式 IRQ模式

Und Irq

FIQ模式

Fiq

响应快速中断时的处理模式

2015/9/28

21

处理器工作模式

ARM微处理器的运行模式可以通过软件改变,也可以通 过外部中断或异常处理改变。 大多数的应用程序运行在用户模式下,当处理器运行在 用户模式下时,某些被保护的系统资源是不能被访问的。 除用户模式以外,其余的6种模式称为非用户模式或特 权模式; 除去用户模式和系统模式以外的5种又称为异常模式, 常用于处理中断或异常,以及访问受保护的系统资源等情 况。

ARM体系架构

该例中用6个时钟周期执行了6条指令 所有的操作都在寄存器中(单周期执行) 指令周期数 (CPI) = 1

高速缓存(CACHE)

1、为什么采用高速缓存 微处理器的时钟频率比内存速度提高快得多,高速缓存可以提 高内存的平均性能。

2、高速缓存的工作原理 高速缓存是一种小型、快速的存储器,它保存部分主存内容的

拷贝。

高 数据

速

CACHE

CPU

缓 存

主存

控

制

地址

器

数据

总线和总线桥

CPU

高速总线

低速设备

低速总线

软硬功能分配 复杂指令增加硬件的复杂度,使指令执行周期大大加长 ,直接访存次数增多,数据重复利用率低。

不利于先进指令级并行技术的采用 流水线技术

RISC基本设计思想

精简指令集:保留最基本的,去掉复杂、使用频度不高的指令 (选取运算指令、加载、存储指令和转移指令作主指令集) ,以减小CPI: CPUtime=Instr_Count * CPI * Clock_cycle

CISC的主要缺点

指令使用频度不均衡。 高频度使用的指令占据了绝大部分的执行时间,扩充的 复杂指令往往是低频度指令。

大量复杂指令的控制逻辑不规整,不适于VLSI工艺 VLSI的出现,使单芯片处理机希望采用规整的硬联逻辑 实现,而不希望用微程序,因为微程序的使用反而制约 了速度提高。(微码的存控速度比CPU慢5-10倍)。

IC—程序中指令数,CPI—每条指令执行所有周期数

1、ARM体系结构

ARM全球合作伙伴(合作模型)

ARM产品应用领域

Samsung ML5100A Diamond Multimedia Rio 600 JVC "Pixstar" GC-X1 Alba Bush Internet TV

3Com 10/100 PCI NIC

Nintendo Gameboy Advance Lexmark Z52 Color Jetprinter HP Jornado 820

5TE

XScale ARM1020E

6

Thumb-2 SIMD Instructions Multi-processing

7

CoreSight

Improved ARM/Thumb ARM9E-S Interworking ARM966E-S CLZ Saturated arithmetic DSP multiplyaccumulate instructions Extensions: Jazelle (5TEJ)

• •

该例中,用6周期执行了4条指令 指令周期数 (CPI) = 1.5

分支流水线举例

Cycle 1 2 L 3 4 5 6 7 8 9

Address

0x8000 0x8004 0x8008 0x8FEC 0x8FF0 0x8FF4

Operation

BL 0x8FEC SUB ORR AND ORR EOR

Iomega HipZip

Sony MZ-R90 MiniDisc

Ericsson R38Share

Nokia Mediamaster

Psion Revo Plus

ARM体系结构的发展

4T

Halfword and signed halfword / byte support System mode Thumb instruction set ARM7TDMI ARM720T ARM9TDMI ARM940T ARM920T

第2 章 ARM体系结构及编程模型(OBE)汇总

ARM9TDMI的五级流水线

2020/6/24

ARM7TDMI与ARM9TDMI流水线比较

3.ARM9TDMI的五级流水线

ARM7TDMI与ARM9TDMI流水线比较

2020/6/24

ARM7和ARM9流水线比较

• 5级流水线的ARM9内核是哈佛架构,拥有独立的 指令和数据总线;指令和数据的读取可以在同一周 期进行;

ARM1020E XScale ARM9E-S ARM966E-S

SIMD Instructions

6

Multi-processing

V6 Memory architecture (VMSA)

Unaligned data

support

ARM1136EJ-S

ARM系列产品命名规则

ARM 926EJ-S

ARM体系结构的特点

• 1) RISC型处理器结构

– (LOAD/STORD, I-cache, D-cache)

• 2)Thumb指令集 (32/16) • 3)多处理器状态模式 (7) • 4)两种处理器工作状态(2) • 5)嵌入式在线仿真调试(ICE-RT ,JTAG) • 6)灵活方便的协处理器接口 (16个) • 7)低电压功耗的设计

ARM体系结构的发展

Halfword

4

1

and signed halfword /

byte support

System

2

mode

SA-110 SA-1110

3

Early ARM architectures

Thumb instruction set

ARM7TDMI

4T

ARM9TDMI

ARM720T

第三节ARM体系结构

一般的通用寄存器

寄存器类别 寄存器在汇编中的名称

用户

系统

R0(a1)

R1(a2)

R2(a3)其中R0~R7为

R3(a4)

未R分4(v1) 组的寄存器,也

通用寄存器 和程序计数

器

就R是5(v2) 说对于任何处理 R6(v3)

器R模7(v4) 式,这些寄存器 都对应于相同的32位 R8(v5)

管理 (svc) 操作系下统保访护问代码用户模系统式复位的和寄软件存中器断响就应比时进较入方此模式

中止 (abt) 未定义 (und)

用或于存支储便 可持器虚 保,以拟护而使内存且用和操这/ 作个在A系模RM统式7TD的访MI一问没有些一大用特 些处权 受任 控务 的 支软持件硬仿资件真协源处。理器的 未定义指令异常响应时进入此模式

各模式下实际访问的寄存器

用户

系统

管理

中止

未定义

RR00

在汇编语言中寄存

R1

器R0~R13为保存数据

R2

或地址值的通用寄存器。

R3

它们是完全通用的寄存器, R4

不会被体系结构作为特殊

R5

用途,并且可用于任何使

R6

用通用寄存器的指令。

R7

R8

R9

R10

R11

R12

R13

RR1133__ssvc

R13_abt

SSPPSSRR__fifqiq

ARM状态各模式下可以访问的寄存器

寄存器类别 寄存器在汇编中的名称

通用寄存器和 程序计数器

状态寄存器

R0 R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13(SP) R14(LR) R15(PC) CPSR SPSR

ARM体系结构与系统开发

超级模式

(Supervisor)

பைடு நூலகம்多种特权模 变化

用户程序 运行模式

复位后 的缺省模式

主要完成各模式堆栈 的设置,注意不要进 入用户模式

一般为用户模式 User

调用主应用程序

当完成所有的系统初始化工作之后,就需要把程序流程转入 主应用程序。最常见的操作是:

IMPORT … B C_Entry C_Entry

因此,选择ARM还是Thumb指令,需要从存储器特性和系统性能要 求两个方面考虑。

二、基于ARM的嵌入式系统的设计要点--系统初始化过程(1)

基于ARM微处理器的系统一般为复杂的片上系统(SoC),这种复 杂系统的多数硬件模块都是可配置的,需要软件设置为特定的工作状 态,因此在用户的应用程序之前,需要有一些专门的代码完成对系统 的初始化。 由于这类代码直接面对ARM微处理器内核和硬件控制器,一般都 使用汇编语言完成。 初始化代码所完成的操作与具体的硬件平台相关,但一般包括如 下内容:

一、ARM体系结构简介(9)

9、指令系统(ARM or Thumb) 从ARM 体系架构V4T 以 后 , 新 增 了一套16位的指令集:Thumb。 Thumb指令集是ARM的一个子集。 两种指令集的性能分析如下: - 当系统数据总线宽度为32位时,ARM比Thumb有更好的性能表现。 - 当系统数据总线宽度为16/8位时,Thumb比ARM性能更好。 - 同样一段C代码,用Thumb指令编译的结果约为ARM的65%,同时具 有更低的运行功耗。

初始化堆栈(1)

由于ARM微处理器有 7 种运行状态,每一种状态的堆栈指针(SP) 都是独立的(其中System和User模式使用相同的SP)。因此,需要对 每一种模式的SP进行初始化。 采用的方法是:改变当前程序状态寄存器(CPSR)内的状态位, 使处理器切换到不同的状态,然后初始化SP。 但对User模式下SP的初始化应该放在最后,因为ARM微处理器进 入User模式后就无法在切换到其他模式了。

ARM7体系结构详细介绍

ARM7体系结构详细介绍简介ARM(Advanced RISC Machines)是一种32位的RISC(Reduced Instruction Set Computer)处理器架构,广泛应用于嵌入式系统、智能手机和平板电脑等领域。

ARM7是ARM体系结构中的一代经典产品,采用了精简指令集,具有低功耗、高效能和高性价比等特点。

架构特性处理器核心ARM7处理器核心是一个半导体芯片,包含了用于指令解码、执行、访存等任务的硬件单元。

ARM7采用了5级流水线架构,可以实现超过20万条指令每秒的处理性能。

此外,ARM7支持可选的乘法器、除法器和调试接口,以满足不同的应用需求。

寄存器ARM7提供了一组寄存器来存放指令和数据。

寄存器分为通用寄存器和特殊目的寄存器两种。

通用寄存器包括16个32位的寄存器,用于存储临时数据和计算结果。

特殊目的寄存器包括程序计数器(PC)、堆栈指针(SP)等,用于指导程序执行和管理堆栈。

存储器ARM7的存储器包括内部存储器和外部存储器两部分。

内部存储器分为指令存储器和数据存储器,用于存放程序指令和数据。

外部存储器通常是闪存、RAM等,用于扩展存储容量。

ARM7支持32位的地址总线,可以寻址最多4GB的内存空间。

性能与功耗ARM7采用了先进的CMOS工艺,使得它具有低功耗和高性能的特性。

ARM7的功耗通常在几个毫瓦到几十个毫瓦之间,可以满足嵌入式系统对功耗的严格要求。

同时,ARM7的高性能使得它可以处理复杂的计算任务,例如图像处理、音视频处理等。

调试与开发ARM7支持ARM公司定义的JTAG调试接口,可以通过调试器进行程序的单步调试、断点设置等操作。

此外,ARM7还提供了丰富的开发工具和软件支持,开发者可以使用C语言、汇编语言等进行编程,方便快捷地开发ARM7的应用程序。

应用领域由于ARM7具有低功耗、高效能和高性价比等特点,因此广泛应用于各种嵌入式系统和移动设备。

下面是一些主要的应用领域:嵌入式系统ARM7在嵌入式系统中得到了广泛的应用,例如工业控制、智能家居、汽车电子等领域。

ARM体系结构

ARM体系结构

ARM作为一种微处理器体系结构,具有广泛应用范围、高性价比、低功耗等优势,在晶体管规模以及架构方面有着很大的节省,因而受到了越来越多应用者的青睐。

ARM体系结构包括处理器(Processor)、片外存储器(External Memory)、I/O接口(Input/Output Interface)、外围器件(Peripheral Devices)、软件支持(Software Support)等内容。

从处理器来说,ARM体系结构提供了一系列非常细分的机型,它们有不同的特性和操作速度,可以满足不同的性能需求,而且这些机型一般都有较高的可缩放性,所以在产品设计的过程中可以根据实际要求选择合适的特性和速度。

从片外存储器来说,ARM体系结构支持使用不同类型的存储器,比如SRAM、DRAM、Flash等,可以根据应用性能和耗电量的需求,来选择合适的存储器以满足不同应用场景的需求,而且存储器容量也比较可观,一般可以满足大部分应用场景的要求。

从I/O接口来说,ARM体系结构支持多种接口,如USB、I2C、SPI、UART等,通过这些接口可以与周边的外设进行连接,而这些接口的功耗和速度也比较低。

ARM体系架构解析

ARM体系架构解析

ARM体系架构是由英国ARM公司推出的常见的32位RISC处理器架构,其在移动设备、嵌入式系统和服务器市场上有广泛应用。

其发展历史源远

流长,经过数十年的发展,其功能也在不断扩展,ARM体系架构已经成为

一种标准处理器架构。

ARM体系架构主要由四大部分组成,分别是内核、外设、中断和指令集。

其中,内核是ARM体系架构的核心,负责处理计算机的所有功能,包

括控制、数据存储和算法处理等。

外设又称外围设备,是处理器与外部世

界的桥梁,可以操控外部设备,比如键盘、显示器、磁盘和网络等。

中断

则是处理器如何处理外部设备发出的信号,其中有多重中断,监听外部设

备的信号,基于不同的中断模式,让处理器运行起来。

指令集是ARM体系

架构的核心,指令集是一组程序指令,它们描述了处理器如何处理和操作

数据,ARM有自己的专有指令集,被广泛应用到移动设备和嵌入式系统中。

ARM体系架构的另一个重要组成部分就是嵌入式软件,由于ARM的低

功耗、低成本和安全性,使得ARM广泛应用于很多嵌入式系统,而这些嵌

入式系统也需要嵌入式软件的支持,嵌入式软件具有低功耗、低功耗和嵌

入式系统的高稳定性等优点,此外。

arm内核全解析_arm内核体系结构分类介绍

arm内核全解析_arm内核体系结构分类介绍ARM处理器是英国Acor n有限公司设计的低功耗成本的第一款RISC微处理器。

全称为Ad vanced RISC Machine。

ARM处理器本身是32位设计,但也配备16位指令集,一般来讲比等价32位代码节省达35%,却能保留32位系统的所有优势。

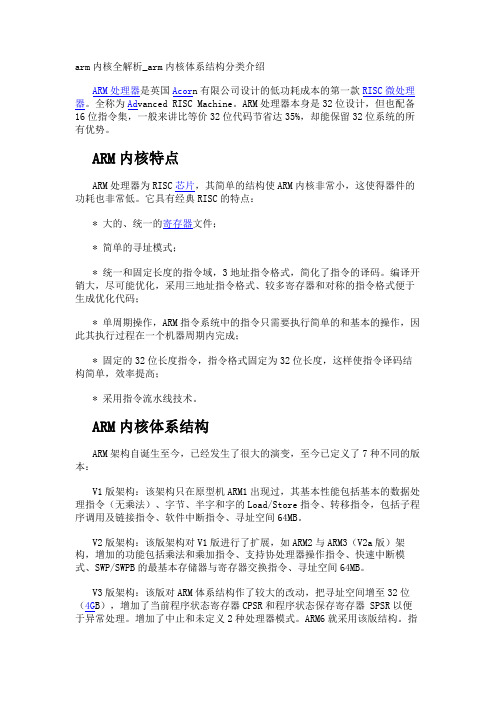

ARM内核特点ARM处理器为RISC芯片,其简单的结构使ARM内核非常小,这使得器件的功耗也非常低。

它具有经典RISC的特点:* 大的、统一的寄存器文件;* 简单的寻址模式;* 统一和固定长度的指令域,3地址指令格式,简化了指令的译码。

编译开销大,尽可能优化,采用三地址指令格式、较多寄存器和对称的指令格式便于生成优化代码;* 单周期操作,ARM指令系统中的指令只需要执行简单的和基本的操作,因此其执行过程在一个机器周期内完成;* 固定的32位长度指令,指令格式固定为32位长度,这样使指令译码结构简单,效率提高;* 采用指令流水线技术。

ARM内核体系结构ARM架构自诞生至今,已经发生了很大的演变,至今已定义了7种不同的版本:V1版架构:该架构只在原型机ARM1出现过,其基本性能包括基本的数据处理指令(无乘法)、字节、半字和字的Load/Store指令、转移指令,包括子程序调用及链接指令、软件中断指令、寻址空间64MB。

V2版架构:该版架构对V1版进行了扩展,如ARM2与ARM3(V2a版)架构,增加的功能包括乘法和乘加指令、支持协处理器操作指令、快速中断模式、SWP/SWPB的最基本存储器与寄存器交换指令、寻址空间64MB。

V3版架构:该版对ARM体系结构作了较大的改动,把寻址空间增至32位(4G B),增加了当前程序状态寄存器CPSR和程序状态保存寄存器 SPSR以便于异常处理。

增加了中止和未定义2种处理器模式。

ARM6就采用该版结构。

指令集变化包括增加了M RS/MSR指令,以访问新增的CPSR /SPSR寄存器、增加了从异常处理返回的指令功能。

5ARM体系结构

配备MMU和 最快 最高 Cache

合理

媒体播放器,产品举 例:MP3,机顶盒, iPOD,智能手机,

PAD

去除MMU, 较快 合理 备有Cache

较低

数字信号处理,产品 举例:汽车ABS系统, 路由器,交换机,航 电系统

没有存储子 系统,即不 含MMU。

5

体系结构版本V3

这个体系结构版本将寻址范围扩展到了32位。 当前程序状态信息由过去存于R15中移到一个 新的当前程序状态寄存器CPSR(Current Program Status Register)中。增加了程序状态 保存寄存器SPSR(Saved Program Status Registers),以便当异常出现时保留CPSR的 内容。增加了2个指令(MRS和MSR),允许 访问新的CPSR和SPSR寄存器。

ARM状态,运行32位的ARM指令集 Thumb状态,运行16位的Thumb指令集 在任何一种工作状态可以通过转移指令切换到另一种

工作状态。 ARM和Thumb之间的状态切换不影响处理器工作模式

和寄存器中的内容。 加电起动时处理器工作在ARM状态。

2024/2/22

12

指令集压缩

对于传统的微处理器体系结构,指令和数据具有同样 的宽度。 与16位体系结构相比,32位体系结构在操纵32位数 据时呈显了更高的性能,并可更有效地寻址更大的 空间。 一般来讲,16位体系结构比32位体系结构具有更高 的代码密度,但只有近似一半的性能。

提高了T变量中ARM/Thumb之间切换的效率; 让非T变量同T变量一样,使用相同的代码生成技 术。增加了一个前导零计数(count leading zeros) 指令,该指令允许更有效的整数除法和中断优先 程序;增加了软件断点指令;为协处理器设计者 增加了更多可选择指令;对由乘法指令如何设置 标志进行了定义。

ARM体系结构ARM简介

;从Arm形状(xíngzhuàn)切换到 Thumb形状(xíngzhuàn)

LDR R0,=Lable+1

BX

R0

;从Thumb形状(xíngzhuàn)切换到 ARM形状(xíngzhuàn)

LDR R0,=Lable

BX

R0

Lable

ADD

R0,R1,第R二十2一页,共43页。

跳转地址标号(偶数〕

尾执行也可进入ARM外形

BX Rm

第二十二页,共43页。

;从ARM外形(wài xínɡ)转变为 Thumb外形(wài xínɡ)

;从Thumb ARM外形(wài xínɡ) 转变为ARM外形(wài xínɡ)

勇于开始,才能找到成功的路

CODE32 LDR R0,=Label+1 BX R0

第九页,共43页。

ARM体系结构还采用一些特别的技术(jìshù),在保证高功用的 前提下尽量添加芯片的面积,并降低功耗

一切的ARM指令都可以依据前面的执行结武断议能否被执行, 从而提高指令的执行效率

可用加载/存储指令批量传输数据,以提高数据的传输效率。 可在一条数据处置指令中同时完成逻辑处置和移位功用。 在循环处置中运用地址的自动增减来提高运转效率

ARM Thumb

PC

PC

Fetch

从存储器中读取指令(zhǐlìng)

PC - 4 PC-2

PC - 8

PC - 4

Decode

Execute

解码(jiěmǎ)指令

寄存器读〔从寄存器Bank〕 移位及ALU操作 寄存器写〔到寄存器Bank 〕

PC指向正被取指的指令(zhǐlìng),而非正在执行的指令(zhǐlìng)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一编ARM编程模式1. Thumb指令集是ARM指令集的重编码的子集,相较于ARM指令集,Thumb指令集有两个不足:1)Thumb的代码执行相同的任务需要相较ARM代码更多的指令数,故不适合一些要求最大化执行时间效率的程序;2)Thumb中不包含一些异常处理需要使用的代码,故不适用编写一些高层次的异常处理代码2. ARM是一个RISC(精简指令集计算机),包含以下一些特性:1) 一个大型统一的寄存器表2) load/store结构,即所有数据操作都仅基于寄存器,而非直接基于内存;3) 简单寻址模式,即所有load/store寻址仅依靠寄存器内容和指令域决定;4) 统一和定长的指令格式,简化了指令的解码。

3. ARM有七种处理器模式,分别为:User(用户模式,即正常指令执行模式),FIQ(快速中断模式),IRQ(通用中断处理模式),Supervisor(超级用户模式,即操作系统保护模式),Abort(中止模式,实现内存或虚拟内存的保护),Undefined(未定义模式),System(系统模式,执行特权的系统进程)。

模式之间的切换可以通过软件控制或外部的中断或异常引起。

4. 正常的应用程序均在User(用户模式)下运行,此时无法获取一些受限的系统资源,也不可以任意切换处理器模式,除非有异常发生。

5. 除了User外的其他六个均为特权模式,他们可以获取各类系统资源,并能实现相互切换。

其中除System外的五个为异常模式。

6. ARM总计拥有37个寄存器,其中31个通用的32-bit寄存器,还有6个32-bit状态寄存器。

而在任意时刻,仅有其中的16个通用寄存器是可见的。

7. ARM体系结构中可见的寄存器为R0-R15,可分成三类:未堆积(unbanked)寄存器R0-R7,堆积(banked)寄存器R8-R14和程序计数器R15。

8. R0-R7为所有模式共享,所有模式共用这8个寄存器。

9. R8-R14为堆积寄存器,其又分成两类。

一类是R8-R12,分为两组,一组是FIQ模式专用,另一组是其他六种模式共用。

另一类是R13和R14,分为六组,分别是User和System共用一组,其他五种异常处理器模式各保有一组R13和R14。

R13和R14一般都用来做特殊的用途,其中R13为堆栈指针(SP);R14为链接寄存器,有两种特殊的功能,一种是发生子程序调用时保存子程序返回地址,另一种是异常发生时保存异常返回地址。

10. PC(R15)保存的是程序计数器,为当前指令的地址+8字节。

同时,由于ARM指令是字对齐的,所以PC的最低两个位bit[0:1]一般为0。

一个例外是当STR或者STM指令保存R15时,则保存的即可能是当前指令地址+8字节,也可能是当前指令地址+12字节,至于是保存8字节的offset还是12字节的offset,则是由实现来确定的。

基于这个原因,应该要尽量避免使用STR或STM指令保存R15。

11. 程序状态寄存器分成CPSR(当前程序状态寄存器)和SPSR(备份程序状态寄存器)。

CPSR所有模式共用,而SPSR则是五个异常模式各有一个。

12. 程序状态寄存器中有两类信息,一类是程序控制码标志,一类是程序控制位。

除此两类使用的位外其他为保留位。

13. 程序状态寄存器中的程序控制码标志主要包含有N标志(负数标志)、Z标志(零标志)、C标志(进位标志)、V标志(溢出标志)和Q标志(DSP指令溢出或饱和标志)。

其中C 标志(进位标志)有四种情况:第一种是加法类指令,若产生进位则C标志置1;第二种是减法类指令,若有借位则置0,否则为1;第三种是移位指令,则C标志为被最后移出的位;最后一种是其他指令,C标志不产生变化。

V标志也分成两种情况:一种是加法或减法类指令,如果发生有符号溢出,则V标志置1;另一种是其他指令,V标志不变。

14. 程序状态寄存器中的程序控制位在CPSR或SPSR的最低八位,包含有I标志(IRQ中断使能)、F标志(FIQ中断使能)、T标志(ARM或Thumb指令选择位,T=1时是Thumb 指令模式)和M[4:0]模式位。

15. 异常是由导致处理器去处理某个事务的内部或外部的源产生的。

在异常处理前的处理器状态应该被保存,这样当异常处理完毕后,系统可以回来原来的处理器状态。

在同一时刻,可以有不止一个的异常产生。

16. ARM共支持七种类型的异常。

当异常发生时,系统会条转到对应某类异常的固定存储地址来进行执行。

这些固定的地址被称作异常向量。

一般它们占据了0x00000000-0x0000001C 的地址空间(高向量模式为0xFFFF0000-0xFFFF001C),其中地址0x00000014(高向量模式为0xFFFF0014)被保留做未来扩充使用。

17. ARM支持的异常是有优先级的,其中SWI(软件中断)和未定义指令不会同时发生,故此两种异常有相同的优先级。

中断优先级保证了在多个异常同时发生的情况下,系统将先进入高优先级异常的执行。

18. ARM支持两种不同的异常向量模式,即正常向量模式和高向量模式。

正常向量模式的地址空间是0x00000000-0x0000001C,而高向量模式的地址空间为0xFFFF0000-0xFFFF001C。

高向量模式需要硬件的支持,而ARM的CP15的Register 1的bit[13]提供了对正常向量模式和高向量模式的配置。

19. ARM支持的内存模式有大端和小端两种。

小端是指对齐位置的字节是对应的字节中的最小有效字节。

而大端是指对齐位置的字节是对应的字节中的最大有效字节。

大小端的设置可通过配置CP15的Register 1的bit[7]来实现。

20. ARM架构中要求指令和数据对齐,即ARM指令的地址最低两位bit[1:0]均为0(Thumb 指令bit[1]为0),而取32位数据时最低两位也应对齐。

如果出现非对齐,则可能的情况有非对齐指令预取和非对齐数据获取。

非对齐指令预取即R15中的地址是一个非对齐的地址,如果出现此情况,可能导致两种结果,一个是出现不可预测的情况,另一个则是忽略最低位的地址取指令。

而load/store类的指令读取了一个非对齐的内存地址,可能出现三种结果:第一是不可预测的情况;第二是忽略最低位实现读取;第三是对忽略最低位,取出数据,并将最低位作为控制位,实现对读取出的数据的旋转操作(仅限于LDR和SWP指令)。

21. ARM架构中PC(R15)保存的是当前指令地址+8(Thumb模式下为当前指令地址+4),原因是ARM内核会预取两条指令,因此PC会指向当前指令的后两条指令。

同时ARM架构支持跳转预测,即当发现跳转指令时,下面预取的指令既可能是跳转指令后接的指令,也可能是跳转目标地址的指令。

22. 理论上,存在这样的情况,即当ARM内核预取了指令后,存储中的对应指令却被修改了。

对于这种情况,ARM忽视这种变化,仍然执行已经预取的指令。

如果第二次再运行到此位置,则将执行修改的后的指令。

23. ARM体系结构中标准的实现I/O功能的方式是使用存储映射I/O(memory-mapped I/O)。

这种方式提供了特殊的一些存储地址,当对这些存储地址实施load或store操作,即实现了对应的I/O功能。

第二编ARM指令集1. 一条ARM指令的最高四位bit[31:28]为条件域(condition field),根据其值的不同来确定当前指令对CPSR中的N、Z、C和V标志的设置与否。

2. ARM指令集支持一个向前或向后32M范围内跳转的Branch指令。

如果是Branch and Link 指令,则除了支持向前或向后的32M范围跳转外,还能将跳转指令的下一条指令地址(返回地址)压入R14(LR)。

而在ARMv4以上支持T的版本中,还有Branch and Exchange指令,此指令可以拷贝通用寄存器Rm的值到PC中,而若其bit[0]为0,则进行ARM至Thumb 的切换。

3. ARM指令集中包含了状态寄存器获取指令MSR和MRS用来对CPSR和SPSR进行操作。

同时ARM指令集还提供了对协处理器的操作指令MCR和MRC。

4. SWI提供了软件中断的功能,此指令的bit[23:0]为一个立即数,ARM处理器会忽略这个立即数,但这个立即数可以提供异常处理程序使用。

第三编ARM寻址模式ARM总共支持五大类的寻址模式,分别是:数据处理操作模式(Data-Processing Operands)、加载和保存字或无符号字节模式(Load and Store Word or Unsigned Byte)、混合的加载和保存模式(Miscellaneous Loads and Stores)、多重的加载和保存模式(Load and Store Multiple)以及协处理器的加载和保护模式(Load and Store Coprocessor)。

第一节数据处理操作模式1. 数据处理操作模式的寻址从指令角度可以分为三类:1)立即数寻址,指令格式如下2)立即数位移寻址:3)寄存器位移寻址:2. 通用的数据处理操作模式的语法是:<opcode> {<cond>} {S} <Rd>, <Rn>, <shifter_operand>其中<shifter_operand>有11种可选属性,分别为1)#<immediate>属于立即数寻址类2)<Rm>属于立即数位移寻址类,是其的一种特殊形式,即直接根据<Rm>的值进行寻址,指令中的shift和shift_imm对应位均为03)<Rm>, LSL #<shift_imm>属于立即数位移寻址类,是根据<shift_imm>对<Rm>中的值进行逻辑(不带进位)左移位4)<Rm>, LSL <Rs>属于寄存器位移寻址类,用<Rs>的值乘以<Rm>的值来达到对<Rm>的值进行逻辑左位移的效果5)<Rm>, LSR #<shift_imm>属于立即数位移寻址类,是根据<shift_imm>对<Rm>中的值进行逻辑右移位6)<Rm>, LSR <Rs>属于寄存器位移寻址类,用<Rs>的值除以<Rm>的值来达到对<Rm>的值进行逻辑右位移的效果7)<Rm>, ASR #<shift_imm>属于立即数位移寻址类,是根据<shift_imm>对<Rm>中的值进行算术(带进位)右移位8)<Rm>, ASR <Rs>属于寄存器位移寻址类,用<Rs>的值对<Rm>的值进行算术右移位9)<Rm>, ROR #<shift_imm>属于立即数位移寻址类,根据<shift_imm>对<Rm>中的值进行右旋转10)<Rm>, ROR <Rs>属于寄存器位移寻址类,用<Rs>的值对<Rm>的值进行右旋转11)<Rm>, RRX属于寄存器位移寻址类,是其的一种特殊形式,根据CPSR中的Carry Flag的值来对<Rm>的值进行右旋转第二节加载和保存字或无符号字节模式1. 加载和保存字或无符号字节模式从指令角度可以分为三类:1)立即数偏移/索引2)寄存器偏移/索引3)按比例的寄存器偏移/索引2. 通用的加载和保存字或无符号字节模式的语法是:LDR|STR{<cond>} {B} {T} <Rd>, <addressing_mode>其中<addressing_mode>有九种可选属性,分别为:1)[<Rn>, #+/-<offser_12>]属于立即数偏移/索引类,寻址模式通过计算对基寄存器Rn加上或减去一个12位立即数偏移来计算寻址地址2)[<Rn>, +/-<Rm>]属于寄存器偏移/索引类,寻址模式通过计算对基寄存器Rn加上或减去索引寄存器Rm的值来计算寻址地址3)[<Rn>, +/-<Rm>, <shift> #<shift_imm>]属于按比例的寄存器偏移/索引类,寻址模式通过计算对基寄存器Rn加上或减去对索引寄存器Rm值的偏移或旋转的结果来计算寻址地址4)[<Rn>, #+/-<offset_12>]!属于立即数偏移/索引类,寻址模式通过计算对基寄存器Rn加上或减去一个12位立即数偏移来计算寻址地址,同时如果条件域中的值与CPSR中的对应位匹配,则新产生的地址会被写回Rn中5)[<Rn>, +/-<Rm>]!属于寄存器偏移/索引类,寻址模式通过计算对基寄存器Rn加上或减去索引寄存器Rm的值来计算寻址地址,同时如果条件域中的值与CPSR中的对应位匹配,则新产生的地址会被写回Rn中6)[<Rn>, +/-<Rm>, <shift> #<shift_imm>]!属于按比例的寄存器偏移/索引类,寻址模式通过计算对基寄存器Rn加上或减去对索引寄存器Rm值的偏移或旋转的结果来计算寻址地址,同时如果条件域中的值与CPSR中的对应位匹配,则新产生的地址会被写回Rn中7)[<Rn>], #+/-<offset_12>属于立即数偏移/索引类,寻址模式使用Rn的值作为当前存储获取的地址,同时如果条件域中的值与CPSR中的对应位匹配,则将基寄存器Rn加上或减去一个12位立即数偏移写回Rn中8)[<Rn>], +/-<Rm>属于寄存器偏移/索引类,寻址模式使用Rn的值作为当前存储获取的地址,同时如果条件域中的值与CPSR中的对应位匹配,则将基寄存器Rn加上或减去索引寄存器Rm的值的结果写回Rn中9)[<Rn>], +/-<Rm>, <shift> #<shift_imm>属于按比例的寄存器偏移/索引类,寻址模式使用Rn的值作为当前存储获取的地址,同时如果条件域中的值与CPSR中的对应位匹配,则将基寄存器Rn加上或减去对索引寄存器Rm 值的偏移或旋转的结果写回Rn中第三节混合的加载和保存模式1. 混合的加载和保存模式从指令角度可以分为两类:1)立即数偏移/索引2)寄存器偏移/索引2. 通用的混合的加载和保存模式的语法是:LDR | STR{<cond>}H|SH|SB|D <Rd>, <addressing_mode>其中<addressing_mode>有六种可选属性,分别为:1)[<Rn>, #+/-<offset_8>]属于立即数偏移/索引类,寻址模式通过计算对基寄存器Rn加上或减去一个8位立即数偏移来计算寻址地址2)[<Rn>, +/-<Rm>]属于寄存器偏移/索引类,寻址模式通过计算对基寄存器Rn加上或减去索引寄存器Rm的值来计算寻址地址3)[<Rn>, #+/-<offset_8>]!属于立即数偏移/索引类,寻址模式通过计算对基寄存器Rn加上或减去一个8位立即数偏移来计算寻址地址,同时如果条件域中的值与CPSR中的对应位匹配,则新产生的地址会被写回Rn中4)[<Rn>, +/-<Rm>]!属于寄存器偏移/索引类,寻址模式通过计算对基寄存器Rn加上或减去索引寄存器Rm的值来计算寻址地址,同时如果条件域中的值与CPSR中的对应位匹配,则新产生的地址会被写回Rn中5)[<Rn>], #+/-<offset_8>属于立即数偏移/索引类,寻址模式使用Rn的值作为当前存储获取的地址,同时如果条件域中的值与CPSR中的对应位匹配,则将基寄存器Rn加上或减去一个8位立即数偏移写回Rn 中6)[<Rn>], +/-<Rm>属于寄存器偏移/索引类,寻址模式使用Rn的值作为当前存储获取的地址,同时如果条件域中的值与CPSR中的对应位匹配,则将基寄存器Rn加上或减去索引寄存器Rm的值的结果写回Rn中第四节多重的加载和保存模式1. 多重的加载和保存模式的指令格式是:此类寻址模式会产生一个地址范围,分别为<start_address>和<end_address>。