蔡觉平老师西电Verilog HDL上机大作业(硬件描述语言)_微电子学院

Verilog HDL数字集成电路设计原理与应用 作者 蔡觉平_ 第1章

HDL语言发展至今,产生了很多种对于数字集成电路 的描述性设计语言,并成功地应用于设计的各个阶段(建模、 仿真、验证和综合等)。20世纪80年代至今,已出现了上百 种硬件描述语言,它们对设计自动化起到了极大的促进和 推动作用,主要有Gateway Design Automation公司提出的 Verilog HDL、美国国防部高级研究计划局(DARPA)设计的 VHDL、美国国防部RPASSP(Rapid Prototyping of Application Specification Signal Processing)计划提出的基于 18 面向对象的OO VHDL(Object Oriented VHDL)、美国杜克 大学的DE VHDL(Duke Extended VHDL)

第1章 Verilog HDL数字集成电路 设计方法概述

➢1.1 数字集成电路的发展和设计方法的演变

➢ 1.2 硬件描述语言

➢1.3 Verilog HDL的发展和国际标准

➢1.4 Verilog HDL和VHDL

➢1.5 Verilog HDL在数字集成电路设计中的优点

➢1.6 功能模块的可重用性

20世纪80年代(第二次变革时期)是标准工艺加工线 (Foundry)公司与IC设计公司共同发展的阶段,主流产品是 MPU、微控制器(Micro Control Unit,MCU)及专用 IC(Application-Specific IC,ASIC)。这时,Foundry和IC设 计公司相结合的方式开始成为集成电路产业发展的新模式。 这一时期,IC产业开始进入以客户为导向的阶段。首先, 标准化功能的IC已难以满足整机客户对系统成本、可靠性 等的要求;其次,由于小尺寸加工技术的进步,软件的硬 9 件化已成为可能,超大规模集成电路(Very Large Scale Integrated,VLSI)开始成为主流芯片;

VerilogHDL复习题与答案

VerilogHDL硬件描述语言复习一、1. Verilog HDL 是在哪一年首次被I E E E标准化的答:Verilog HDL是在1995年首次被IEEE标准化的..2. Verilog HDL支持哪三种基本描述方式答:Verilog HDL可采用三种不同方式或混合方式对设计建模..这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3. Verilog HDL 是由哪个公司最先开发的答:Verilog HDL是由Gateway Design Automation公司最先开发的4. Verilog HDL中的两类主要数据类型什么答:线网数据类型和寄存器数据类型..线网类型表示构件间的物理连线; 而寄存器类型表示抽象的数据存储元件..5. U D P代表什么答:UDP代表用户定义原语6. 写出两个开关级基本门的名称..答:pmos nmos7.写出两个基本逻辑门的名称..答:and or8.在数据流描述方式中使用什么语句描述一个设计答:设计的数据流行为使用连续赋值语句进行描述9. 采用结构描述方式描述1位全加器..答:module full_adda;b;cin;s;co;input a;b;cin;output s;co;wire S1;T1;T2;T3;xorX1S1;a;b;X2s;S1;cin;andA1T3;a;b;A2T2;b;cin;A3T1;a;cin;orO1co;T1;T2;T3;endmodule10. i n i t i a l语句与always 语句的关键区别是什么答: 1 initial语句:此语句只执行一次..2 always语句:此语句总是循环执行; 或者说此语句重复执行..11.采用数据流方式描述2 - 4译码器..答:'timescale 1ns/nsmodule Decoder2×4A;B;EN;Z;input A;B;EN;output 0:3Z;wire abar;Bbar;assign #1 Abar=~A;assign #1 Bbar=~B;assign #2 Z0=~Abar&Bbar&EN;assign #2 Z1=~Abar&B&EN;assign #2 Z2=~A&Bbar&EN;assign #2 Z3=~A&B&EN;endmodule1 2. 找出下面连续赋值语句的错误..assign Reset=#2 Sel^WriteBus;答:不符合连续赋值语句的语法;应该为:assign #2 Reset = ^ WriteBus;二、1. 下列标识符哪些合法;哪些非法C O u n T; 1_2 M a n y; \**1; R e a l ; \wait; Initial答:COunT合法;1_2 Many非法;\**1;Real 非法;\wait合法;Initial合法2. 在Verilog HDL中是否有布尔类型答:没有3. 如果线网类型变量说明后未赋值;其缺省值为多少答:z4. Verilog HDL 允许没有显式说明的线网类型..如果是这样;怎样决定线网类型答:在Verilog HDL 中;有可能不必声明某种线网类型..在这样的情况下;缺省线网类型为1位线网..5.下面的说明错在哪里i n t e g e r 0:3 R i p p l e;答:应该是integer Ripple 0:36. Verilog HDL有哪几大类数据类型答:verilog hdl 有两大类数据类型:线网类型和寄存器类型..7.Verilog HDL有哪几种寄存器类型答:有五种不同的寄存器类型:reg、integer、time、real、realtime..三、1. 假定长度为6 4个字的存储器; 每个字8位;编写Verilog 代码;按逆序交换存储器的内容..即将第0个字与第6 3个字交换;第1个字与第6 2个字交换;依此类推..答:reg 7:0 mem 63:0;integer i = 0;reg 7:0 temp;whilei < 32begintemp = memi;memi = mem63 - i;mem63 - i = temp;i = i + 1;end2. 假定3 2位总线A d d re s s _ B u s; 编写一个表达式;计算从第11位到第2 0位的归约与非.. 答:~& addressBus20:113. 假定一条总线C o n t ro l _ B u s 1 5 : 0 ;编写赋值语句将总线分为两条总线:A b u s 0 : 9 和B b u s 6 : 1 ..答:Abus = ControlBus9:0;Bbus = ControlBus15:10;4. 编写一个表达式;执行算术移位;将Qparity 中包含的8位有符号数算术移位..答:{Qparity7-i:0; Qparity7:8-i}//左移;i表示移的位数{Qparityi-1:0; Qparity7: i}//右移;i表示移的位数5.使用条件操作符; 编写赋值语句选择N e x t S t a t e的值..如果C u rre n t S t a t e的值为R E S E T; 那么N e x t S t a t e的值为G O;如果C u rre n t S t a t e的值为G O;则N e x t S t a t e 的值为B U S Y;如果C u rre n t S t a t e的值为B U S Y;则N e x t S t a t e的值为R E S E T..答:NextState = CurrentState == RESET Go : CurrentState == Go BUSY : RESET6. 如何从标量变量A;B;C和D中产生总线B u s Q0:3 如何从两条总线B u s A 0 : 3 和B u s Y 2 0 : 1 5 形成新的总线B u s R 1 0 : 1答:BusQ3:0 = {D; C; B; A}BusR10:1 = {BusY20:15; BusA3:0}四、1、Verilig HDL提供的内置基本门分为哪几类1 多输入门、2 多输出门、3 三态门2、多输入门与多输出门的区别在哪里答:多输入门:and nand nor or xor xnor 这些逻辑门只有单个输出; 1个或多个输入第一个端口是输出;其它端口是输入..多输出门有:buf; not 这些门都只有单个输入;一个或多个输出最后的端口是输入端口;其余的所有端口为输出端口..3、Verilog HDL内置的mos开关门有哪些答:cmos; nmos; pmos; rcmos; rnmos; rpmos4、门时延值的组成有哪几个值答:1 上升时延2 下降时延3 关断时延5. Verilig HDL提供的内置基本门分为哪几类答:1 多输入门2 多输出门 3 三态门4 上拉、下拉电阻5 MOS开关6 双向开关6.假定一条总线Control_Bus7:0;编写赋值语句将总线分为两条总线:Abus 0:2和Bbus 4 : 1 ..答:Abus=ControlBus2:0;Bbus=ControlBus15:12;7. 编写一个表达式;执行算术移位;将Qparity 中包含的8位有符号数算术左移3位..答:{Qparity4:0; Qparity7:5}8.要求采用数据流方式设计一个半加器;写出完整的Verilig HDL设计模块..答:module half_addSum; Cout;A; B;input A; B;output Sum; Cout;assign Sum=A^B;assign Cout=A&B;endmodule五、1、操作符有按操作数个数分为3 种类型;其中三目操作符有 2 个操作符和 3 个操作数..2、关键字全是小写;标识符的首字符必须是字母或下划线..3、数字A=5’b011 的表示z ..设B=5’b101x1;C=5’b01x11;则操作运算F=B+C的结果F= 5'bxxxxx ..4、VerilogHDL中保存字符串“Hello”需要 5 位..5、声明reg 7:0data4:0表示5 个8 位的存储单元..6、module testq;clk;crt;output q;reg q;Input clk;crt;always @posedge clkbeginifcrt==1q=~q;endendmodule7、数据流建模的主要语法结构是assign LHS_target = RHS_expression; 语句;采用assign 关键字开始..8、线网赋值延迟可以通过普通赋值延迟; 隐式连续赋值延迟和线网声明延迟三种方法来实现..9、模型引用时;要指定实例名;但硬件和用户定义原语例外..10、语句assign #2:3:4;5:6:7portout;clk;in中的典型关断延迟是 4 ;最大关断延时是7 ..11、VerilogHDL语言可以从四个不同的抽象层次描述电路;这四层是开关级、门级、寄存器传送级、算法级12、结构化建模的主要语句是内置门原语和用户定义原语..六、1.门级建模的类型有:Aor和AND BOR和andCand和or DA、B、C都正确 C2.VerilogHDL使用的是逻辑是:A二值逻辑B四值逻辑C三值逻辑D八种强度 B3.不属于寄存器类型的是:Ainteger BregCwand Dtime C4.VerilogHDL语言中;标识符的作用范围是:A本模块B外部模块C所有模块D全局模块 A5.具有多个输出端口的门是:Aand BorCnor Dnot D七、1、语句内部时延与语句前时延效果是否一样答:不一样2、当时延表达式为负数时;时延值是如何处理得到答:取绝对值3、VeriligHDL有几种循环语句分别采用关键字是什么答:总共有四种循环语句;分别采用forever、repeat、while、for..八、1.VerilogHDL语言和C语言的结构化语句有何不同答:1.Verilog HDL是在C语言的基础上发展起来的;保留了C语言的结构特点..2.C语言由函数组成;Verilog由模块module组成3.C语言通过函数名及其端口变量实现调用;Verilog也通过模块名和端口变量实现调用4.C语言有主函数main;Verilog的个module均等价;但必有一个顶层模块;包含芯片系统与外界的所有I/O信号5.C语言是顺序执行;而Verilog的所有module均并发执行6.C 语言与Verilog语法相似..2、VerilogHDL语言的操作符类型有哪些其数据流建模采用什么来描述设计吗答:算术、逻辑、关系、等价、按位、缩减、移位、拼接、条件数据流建模采用算术与逻辑来描述设计3、VerilogHDL语言的优点是什么答:Verilog HDL语言的优势:由于它在其门级描述的底层;也就是晶体管开关的描述方面比VHDL等各种其它的HDL语言有更强的功能..所以在复杂数字逻辑电路和系统的设计仿真时更有优势;描述的设计思想、电路结构和逻辑关系清晰明了;并且设计语言简练、易学易用;其模块化分层结构在大规模设计时更能体现出优势..因此可以看出;Verilog HDL语言在EDA设计中相对与其他的各种硬件描述语言更有优势..4、下列例子中;b;c;d的最终值分别是什么initialbeginb=1’b1;c=1’b0;#10 b=1’b0;endinitialbegind=#25{b|c};end答:b=1'b0、c=1'b0、d=1'b05.一位全减器模块wsub具有三个一位输入:x;y和z前面的借位;两个一位的输出D差和B借位..计算D和B的逻辑等式如下所示:..D..yx=++..+..xyzzzxyyzx..+=B.+yzyzxx写出VerilogHDL数据流描述的该全减器wsub..答: module wsubD;B;x;y;xinput x;y;z;output D;B;assign D=~x*~y*~z+~x*y*~z+x*~y*~Z+x*y*z;assign B=~x*y+~x*z+y*z;endmodule。

[工学]西安电子科技大学verilog教程1-2

![[工学]西安电子科技大学verilog教程1-2](https://img.taocdn.com/s3/m/7e9aa877240c844768eaeea1.png)

西安电子科技大学

雷达信号处理国防科技重点实验室

2. 数字信号处理

数字信处理系统往往要进行一些复杂的数字运算和数据处理, 并且又有实时响应的要求,他们通常是由高速专用数字逻辑系统或专 用数字信号处理器所构成,电路是相当复杂的。因此只有在高速大规 模集成电路设计制造技术进步的基础上,才有可能实现真正有意义的 实时数字信号处理系统。对实时数字信号处理系统的要求不断提高, 也推动了高速大规模集成电路设计制造技术的进步。现代专用集成电 路的设计是借助于电子电路设计自动化(EDA)工具完成的。学习和 掌握硬件描述语言(HDL)是使用电子电路设计自动化工具的基础。

• 由传统的观点出发,可以从三个不同的方面来研究计算,即从数 学、科学和工程的不同角度;由比较现代的观点出发,可以从四 个主要的方面来研究计算,即从算法和数据结构、编程语言、体 系结构、软件和硬件设计方法学。

• 一个复杂的数字系统设计往往是从算法到由硬线连接的门级逻辑 结构,再映射到硅片的逐步实现的过程。

&Moorby,刘明业等译。

西安电子科技大学

雷达信号处理国防科技重点实验室

课时及考试安排

授课时数:30课时 上机时数;14课时 考试时数:90分钟 成绩计算:大作业*40%+考试*60%

西安电子科技大学

雷达信号处理国防科技重点实验室

课程内容安排

第一部分 初级篇

第一章. 概述及设计工具介绍 第二章. Verilog HDL的基本知识 第三章. Verilog HDL基本概念 第四章. 常用Verilog语法之一 第五章.常用Verilog语法之二 第六章.常用Verilog语法之三 第七章.常用Verilog语法之四 第八章.常用Verilog语法之五

蔡觉平老师西电VerilogHDL上机大作业硬件描述语言_微电子学院

《Verilog HDL数字集成电路设计原理与应用》上机作业******* 班级:******* 学号:*******姓名:verilog HDL描述与仿真。

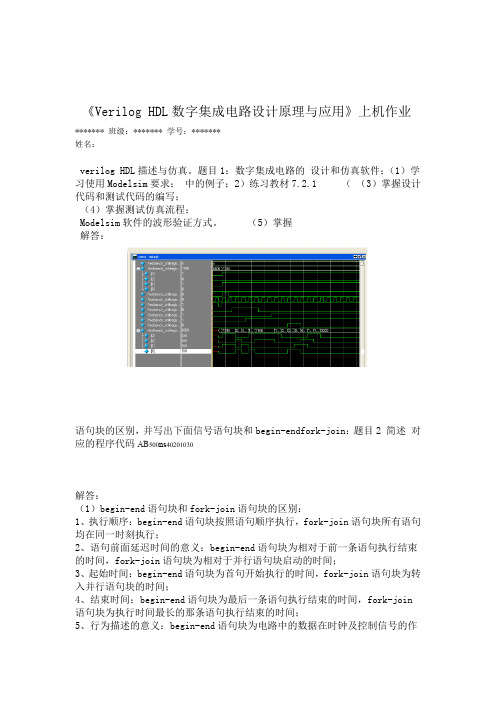

题目1:数字集成电路的设计和仿真软件;(1)学习使用Modelsim要求:中的例子;2)练习教材7.2.1 ((3)掌握设计代码和测试代码的编写;(4)掌握测试仿真流程;Modelsim软件的波形验证方式。

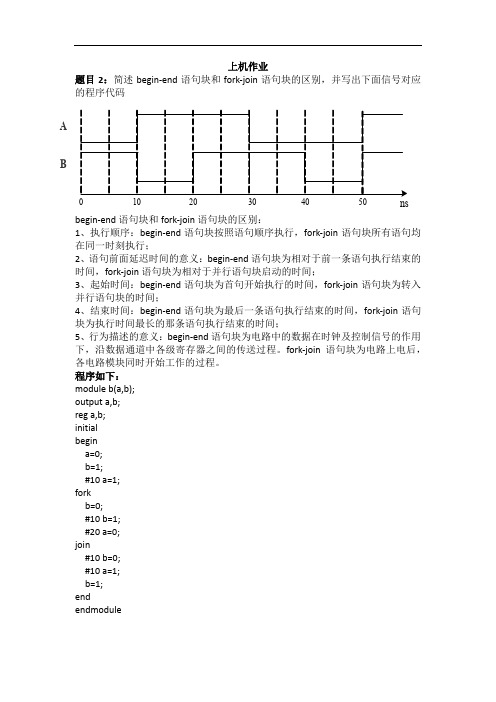

(5)掌握解答:语句块的区别,并写出下面信号语句块和begin-endfork-join:题目2 简述对应的程序代码AB500ns40201030解答:(1)begin-end语句块和fork-join语句块的区别:1、执行顺序:begin-end语句块按照语句顺序执行,fork-join语句块所有语句均在同一时刻执行;2、语句前面延迟时间的意义:begin-end语句块为相对于前一条语句执行结束的时间,fork-join语句块为相对于并行语句块启动的时间;3、起始时间:begin-end语句块为首句开始执行的时间,fork-join语句块为转入并行语句块的时间;4、结束时间:begin-end语句块为最后一条语句执行结束的时间,fork-join 语句块为执行时间最长的那条语句执行结束的时间;5、行为描述的意义:begin-end语句块为电路中的数据在时钟及控制信号的作用下,沿数据通道中各级寄存器之间的传送过程。

fork-join语句块为电路上电后,各电路模块同时开始工作的过程。

(2)程序代码:Begin-end语句:module initial_tb1;reg A,B;initialbeginA=0;B=1;#10 A=1;B=0;#10 B=1;#10 A=0;#10 B=0;#10 A=1;B=1;endendmoduleFrk-join语句:module wave_tb2;reg A,B;parameter T=10;initialforkA=0;B=1;#T A=1;B=0;#(2*T) B=1;#(3*T) A=0;#(4*T) B=0;#(5*T) A=1;B=1;joinendmodule3. 分别用阻塞和非阻塞赋值语句描述如下图所示移位寄存器的电路图。

verilog硬件描述语言上机

verilog硬件描述语言上机《硬件描述语言》上机作业西电微电子\第一题:用Verilog语言的结构描述和行为描述分别设计下面的电路。

A[0] Array B[0]A[1]B[1]A[2]B[2]结构描述:电路设计:module hw1(A,B,Y); input[2:0] A,B;output Y;wire w1,w2,w3;xor U1(w1,A[0],B[0]);xor U2(w2,A[1],B[1]);xor U3(w3,A[2],B[2]);nor U4(Y,w1,w2,w3);endmodule仿真测试:module test_hw1;reg[2:0] A,B;wire Y;hw1 U1(A,B,Y);initialbeginA=3'b000;B=3'b000;#50 A=3'b000;B=3'b000;#50 A=3'b111;B=3'b111;#50 A=3'b000;B=3'b110;#50 A=3'b111;B=3'b000;#50 A=3'b110;B=3'b110;#50 A=3'b011;B=3'b010;#50 A=3'b001;B=3'b011;#50 A=3'b111;B=3'b010;#50 $stop;endinitial $monitor($time,"\tA=%d\tB=%d\tY=%d",A,B,Y); Endmodule行为描述:电路设计:module hw2(A,B,Y);input[2:0] A,B;output Y;wire Y;assign Y=~((A[0]^B[0])||(A[1]^B[1])||(A[2]^B[2])); endmodule 仿真测试:module test_hw2;reg[2:0] A,B;wire Y;hw2 U1(A,B,Y);initialbeginA=3'b000;B=3'b000;#50 A=3'b000;B=3'b000;#50 A=3'b111;B=3'b111;#50 A=3'b000;B=3'b110;#50 A=3'b111;B=3'b000;#50 A=3'b110;B=3'b110;#50 A=3'b011;B=3'b010;#50 A=3'b001;B=3'b011;#50 A=3'b111;B=3'b010;#50 $stop;endinitial $monitor($time,"\tA=%b\tB=%b\tY=%b",A,B,Y); endmodule第二题:参数化电路设计1. 用行为描述方式实现下图所示的具有“one -hot”(独热)状态的环形计数器。

verilog hdl实验报告

verilog hdl实验报告《Verilog HDL实验报告》Verilog HDL(硬件描述语言)是一种用于描述电子系统的硬件的语言,它被广泛应用于数字电路设计和硬件描述。

本实验报告将介绍Verilog HDL的基本概念和使用方法,并通过实验展示其在数字电路设计中的应用。

实验目的:1. 了解Verilog HDL的基本语法和结构2. 掌握Verilog HDL的模块化设计方法3. 熟悉Verilog HDL的仿真和综合工具的使用实验内容:1. Verilog HDL的基本语法和结构Verilog HDL是一种硬件描述语言,其语法和结构类似于C语言。

它包括模块定义、端口声明、信号赋值等基本元素。

在本实验中,我们将学习如何定义Verilog模块,并使用端口声明和信号赋值描述数字电路的行为。

2. Verilog HDL的模块化设计方法Verilog HDL支持模块化设计,可以将复杂的电路分解为多个模块,每个模块描述一个子电路的行为。

在本实验中,我们将学习如何设计和实现Verilog模块,并将多个模块组合成一个完整的数字电路。

3. Verilog HDL的仿真和综合工具的使用Verilog HDL可以通过仿真工具进行功能验证,也可以通过综合工具生成实际的硬件电路。

在本实验中,我们将使用Verilog仿真工具对设计的数字电路进行功能验证,并使用综合工具生成对应的硬件电路。

实验步骤:1. 学习Verilog HDL的基本语法和结构2. 设计一个简单的数字电路,并实现Verilog模块描述其行为3. 使用仿真工具对设计的数字电路进行功能验证4. 使用综合工具生成对应的硬件电路实验结果:通过本实验,我们学习了Verilog HDL的基本概念和使用方法,并成功设计和实现了一个简单的数字电路。

我们使用仿真工具对设计的数字电路进行了功能验证,并使用综合工具生成了对应的硬件电路。

实验结果表明,Verilog HDL在数字电路设计中具有重要的应用价值。

Verilog-HDL数字集成电路设计原理与应用-作者-蔡觉平-第4章

方法2:逻辑代数方式。 组合电路的另一种表达方法是逻辑代数方式,其主要

思想是将真值表用卡诺图来表示,然后化简电路,得出逻

辑函数表达式。图4.2-2是例4.2-1的卡诺图。 通过对卡诺图的化简,可以得到组合电路逻辑输出与

输入之间的逻辑函数表达式:

OUT = AB + BC + AC

与计算机软件所采用的高级程序语言(C语言)类似, Verilog HDL是一种高级程序设计语言,程序编写较简单, 设计效率很高。然而,它们面向的对象和设计思想却完全 不同。

软件高级程序语句是对通用型处理器(如CPU)的编程, 主要是在固定硬件体系结构下的软件化程序设计。处理器 的体系结构和功能决定了可以用于编程的固定指令集,设 计人员的工作是调用这些指令,在固化的体系结构下实现 4 特定的功能。

3'b000 : OUT<=0;

3'b001 : OUT<=0;

3'b010 : OUT<=0;

3'b100 : OUT<=0;

3'b011 : OUT<=1;

3'b101 : OUT<=1;

3'b110 : OUT<=1;

3'b111 : OUT<=1;

25

endcase

endmodule

26

29

30

图4.2-3 逻辑表达式4.2-1的电路结构

其Verilog HDL程序代码如下:

module design(OUT,A,B,C);

output OUT;

input A,B,C;

and U1 (w1,A,B);

VerilogHDL硬件描述-元件例化与原理图

5、举一反三

1、关于仿真的设置问题(clk驱动,仿真周 期:最多1ms) 2、修改动态扫描的时间

(2pow25=33554432 40/(2pow25)=1.19)

3、FPGA引脚的锁定方法: a 常规锁定法Assignments\Pins\(修改完后 要重新编译,否则无效) b tcl scripts(脚本)(注意一定要放在英文目录) 4、其它。(下载器的设置问题)

功能仿真的步骤如下: 1、新建一个仿真文件; 2、设置需要仿真的信号,保存文件; 3、使用Processing>Generate Functional Simulation Netlist 菜单,生成不包含时序信息的功能仿真网表; 4 、使用Assignments>Setting命令,打开Setting对话框; 5、 在设置分类列表中,选择Simulator Settings; 6 、在Simulator mode 中选择Functional; 7 、在Simulator input中,指定矢量波形源文件; 8 、按ok按钮,完成设置; 9 、使用Processing>Start>Start Simulation命令启动仿真。 10、每次程序修改后,需要重新进行第3步。

1、分析具体实例—电子钟 2、演示设计效果。 3、分析语言。 4、以解决具体问题为导向进行学习。

2012年4月8日

3

电子钟实例

1、一个实例—电子钟 2、实验硬件平台 3、硬件框图 4、软件框图 5、用verilog语言实现电子钟(重点)

2012年4月8日 4

1、一个实例—电子钟

1.利用动态扫描方法在八位数 码管上显示出时钟:如12.54.32

2012年4月8日 16

(完整)Verilog_HDL试卷及答案,推荐文档.doc

河北大学课程考核试卷2008 —— 2009 学年第一学期2006 级电气类专业(类)考核科目 EDA 技术课程类别必修考核类型考查考核方式闭卷类别 A一、选择题:1、下列标示符哪些是合法的( B )A、 $timeB、 _dateC、 8sumD、 mux#2、如果线网类型变量说明后未赋值,起缺省值是( D )A、 xB、 1C、 0D、 z3、现网中的值被解释为无符号数。

在连续赋值语句中,assign addr[3:0]=-3;addr 被赋予的值是( A )A、 4’b1101B、 4’b0011C、 4’bxx11D、 4’bzz114、 reg[7:0] mema[255:0] 正确的赋值是( A )A、 mema[5]=3 ’d0,B、 8’d0;C、 1’b1;D、 mema[5][3:0]=4 ’d15、在 code 模块中参数定义如下,请问top 模块中 d1 模块 delay1、 delay2 的值是 ( D )module code(x,y); module top;paramee delay1=1,delay2=1; .code #(1,5) d1(x1,y1);endmodule endmoduleA、( 1,1)B、(5,5)C、( 5,1)D、( 1,5)6、“ a=4’b11001,b=4 ’bx110”选出正确的运算结果( B )A、 a&b=0B、a&&b=1C、b&a=xD、 b&&a=x7、时间尺度定义为timescale 10ns/100ps ,选择正确答案( C )A、时间精度 10nsB、时间单位 100psC、时间精度 100psD、时间精度不确定8、若 a=9,执行 $display( “current value=%0b,a=%0d ”,a,a)正确显示为( B )A、 current value=1001,a=09B、current vale=1001,a=9C、 1001,9D、 current vale=00 001001,a=99、 aways begin #5 clk=0; #10 clk=~clk;end 产生的波形( A )A、占空比 1/3B、 clk=1C、 clk=0D、周期为 1010、在 Verilog 中定义了宏名`define sum a+b+c 下面宏名引用正确的是( C )A、 out= ’sum+d;B、 out=sum+d;C、 out=`sum+d;D、都正确二、填空题:(共 15 分,每小题 3 分)1、某一纯组合电路输入为in1,in2 和 in3,输入出为 out ,则该电路描述中always 的事件表达式应写为always@(in1,in2,in3 ); 若某一时序电路由时钟clk 信号上升沿触发,同步高电平复位信号rst 清零,该电路描述中always 的事件表达是应该写为always @( posedge clk )。

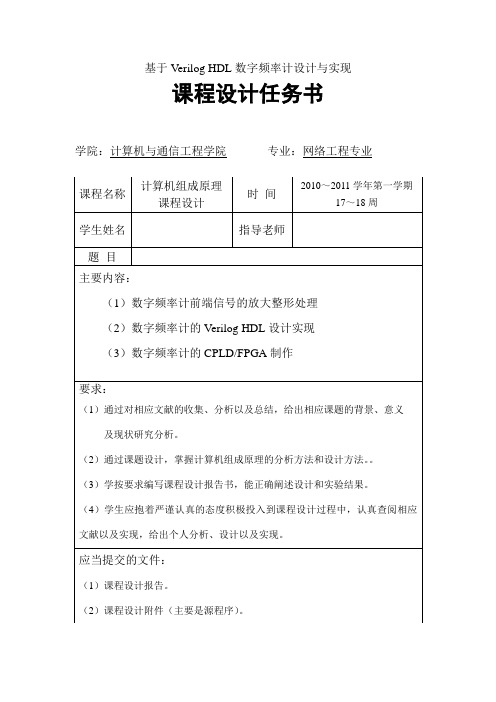

课程设计---基于Verilog HDL数字频率计设计与实现

基于Verilog HDL数字频率计设计与实现课程设计任务书学院:计算机与通信工程学院专业:网络工程专业指导教师对学生在课程设计中的评价指导教师对课程设计的评定意见基于Verilog HDL数字频率计设计与实现摘要:在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

电子计数器测频有两种方式:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法,如周期测频法。

直接测频法适用于高频信号的频率测量,间接测频法适用于低频信号的频率测量。

本文阐述了用Verilog HDL语言设计了一个简单的数字频率计的过程关键词:周期;EDA;Verilog HDL;数字频率计;波形仿真目录1 引言......................................................... - 5 -1.1 数字频率计概述.......................................... - 5 -1.2 频率测量的思想和方法.................................... - 6 -2 Verilog HDL简介............................................. - 9 -2.1 Verilog HDL的简介....................................... - 9 -3 数字频率计系统框图.......................................... - 10 -3.1数字频率计系统框图...................................... - 10 -3.2数字频率计系统部件简介.................................. - 10 -4 基于Verilog HDL数字频率计程序设计.......................... - 11 -4.1数字频率计系统模块划分结构.............................. - 11 -4.2计数模块counter ........................................ - 12 -4.3门控模块gate_control ................................... - 15 -4.4分频模块fdiv ........................................... - 18 -4.5 寄存器模块flip_latch ................................... - 20 -4.6 多路选择模块data_mux ................................... - 22 -4.7 动态位选模块dispselect ................................. - 23 -4.8 BCD译码模块dispdecoder ................................ - 25 -4.9 顶层电路top ............................................ - 28 -5 总结........................................................ - 31 - 参考文献....................................................... - 32 -1 引言在电子测量领域中,频率测量的精确度是最高的,可达10—10E-13数量级。

Verilog HDL数字集成电路设计原理与应用 作者 蔡觉平_ 第2章

字,它是Verilog HDL语言内部的专用词,是事先定义好的 确认符,用来组织语言结构。用户不能随便使用这些关键

字。需注意的是,所有关键字都是小写的。例如,

ALWAYS不是关键字,它只是标识符,与always(关键字) 是不同的。表2.1-1所示为Verilog HDL的常用关键字。 11

2.1.1 空白符

空白符包括空格符(\b)、制表符(\t)、换行符和换页符。

空白符使代码看起来结构清晰,阅读起来更方便。在编译 和综合时,空白符被忽略。

Verilog HDL程序可以不分行,也可以加入空白符采用

多行编写。

4

例2.1-1 空白符使用示例。

initial begin a = 3'b100; b = 3'b010; end

表2.1-1 Verilog HDL中的常用关键字

always and assign attribute begin buf bufif0 bufif1 case casex casez cmos deassign end endattribute endcase endmodule endfunction endprimitive endspecify endtable endtask event for force forever fork function highz0 highz1 if initial inout input integer join large macromodule medium module nand negedge nmos nor not notif0 notif1 or output parameter pmos posedge primitive pull0 pull1 pullup pulldown rcmos real realtime reg release repeat rtran rtranif0 rtranif1 scalared signed small specify specparam strength strong0 strong1 supply0 supply1 table task time tran tranif0 tranif1 tri tri0 tri1 triand trior trireg unsigned vectored wait wand weak0 weak1 while wire wor xnor xor

蔡觉平老师,verilog上机作业解析

上机作业题目2:简述begin-end 语句块和fork-join 语句块的区别,并写出下面信号对应的程序代码begin-end 语句块和fork-join 语句块的区别:1、执行顺序:begin-end 语句块按照语句顺序执行,fork-join 语句块所有语句均在同一时刻执行;2、语句前面延迟时间的意义:begin-end 语句块为相对于前一条语句执行结束的时间,fork-join 语句块为相对于并行语句块启动的时间;3、起始时间:begin-end 语句块为首句开始执行的时间,fork-join 语句块为转入并行语句块的时间;4、结束时间:begin-end 语句块为最后一条语句执行结束的时间,fork-join 语句块为执行时间最长的那条语句执行结束的时间;5、行为描述的意义:begin-end 语句块为电路中的数据在时钟及控制信号的作用下,沿数据通道中各级寄存器之间的传送过程。

fork-join 语句块为电路上电后,各电路模块同时开始工作的过程。

程序如下: module b(a,b); output a,b; reg a,b; initial begin a=0; b=1; #10 a=1; fork b=0; #10 b=1; #20 a=0; join#10 b=0; #10 a=1; b=1; endendmoduleA B题目3.分别用阻塞和非阻塞赋值语句描述如下图所示移位寄存器的电路图。

D Q D Q dinclk D Q D Qout3out2out1out0程序如下:module block1(din,clk,out0,out1,out2,out3); input din,clk;output out0,out1,out2,out3;reg out0,out1,out2,out3;always@(posedge clk)beginout3=out2;out2=out1;out1=out0;out0=din;endendmodulemodule non_block1(din,clk,out0,out1,out2,out3); input din,clk;output out0,out1,out2,out3;reg out0,out1,out2,out3;always@(posedge clk)beginout0<=din;out1<=out0;out2<=out1;out3<=out2;endendmodule题目4:设计16位同步计数器要求:(1)分析16位同步计数器结构和电路特点;(2)用硬件描述语言进行设计;(3)编写测试仿真并进行仿真。

西电微电子学院数字集成电路上机作业

《数字集成电路》上机实验姓名:***班级:***学号:***第一次实验一、实验目的:掌握HSPICES软件的使用方法,用于分析二极管及CMOS反相器的直流特性,通过改变电源电压及MOS管的宽长比得到一组CMOS反相器的电压传输特性曲线,从而理解CMOS反相器电压传输特性曲线的影响因素和调整方法。

二、实验内容:1. 由上图所示,令(1)I S=10-14A,T=300K;(2) I S=10-16A,T=300K;(3) I S=10-14A,T=350K,利用SPICE求解V D1、V D2和I D。

【仿真代码】.TITLE amplifierSHU.LIB 'D:\Digital\lib\csmc06.LIB' TT.TEMP temvalueR1 1 2 2kR2 3 4 2kD1 2 3 DMODD2 4 0 DMOD.MODEL DMOD D Is=isvalue.PARAM temvalue=27 isvalue=1E-14 V1 1 0 DC 2.5.OP.ALTER.PARAM temvalue=27 isvalue=1E-16 .ALTER.PARAM temvalue=77 isvalue=1E-14 .OPIONS LIST NODE POST=2.END【结果】【分析】V D1=525.4463mv、V D2=525.4463mv和I D=362.2768uA2. (1)由下图所示,令Vin从0V变化到2.5V,步长为0.5V,利用SPICE求M1管电流变化的曲线,判断管子的工作状态;当M1的尺寸变化为W/L=4u/1u时,求I M1,并解释两条曲线存在误差的原因。

【仿真代码】.TITLE amplifierSHU.LIB 'D:\Digital\lib\mix025_1.lib' TT.PARAM dd=2.5Vdd 1 0 DC ddVin 2 0 DCM_M1 0 2 1 1 pch L=1U W=4U.DC Vin 0 2.5 0.5.PRINT I(2).OP.OPTION NODE LIST POST.END.TITLE amplifierSHU.LIB 'D:\Digital\lib\mix025_1.lib' TT.PARAM dd=2.5Vdd 1 0 DC ddVin 2 0 DCM_M1 0 2 1 1 pch L=0.25U W=1U .DC Vin 0 2.5 0.5.PRINT I(2).OP.OPTION NODE LIST POST.END【结果】【分析】在1.5V之前是工作在线性区,1.5-2V之间是可变电阻区,2V以后工作在饱和区。

《Verilog HDL硬件描述语言》实验教学大纲

《Verilog HDL硬件描述语言》实验教学大纲

课程代码:MICR3001

课程名称:Verilog HDL硬件描述语言

英文名称:Verilog HDL

实验室名称:微电子实验室

课程学时:72实验学时:18

一、本课程实验教学目的与要求

通过实验要求学生掌握用Verilog HDL硬件描述语言进行集成电路设计的流程和方法。

学会使用Max+plusⅡ,QuartusⅡ设计软件,掌握从HDL源代码的输入→编译→仿真→管脚锁定→下载全过程。

学会用ModelSim设计软件,用Verilog HDL编写测试码对设计模块进行仿真。

二、主要仪器设备及现有台套数

PC,现有35台; EDA实验箱,25套;

1、实验报告:有设计代码,仿真结果,管脚排列,验证结果。

2、考核方式:

(1)实验课的考核方式:教师验收评定成绩。

(2)实验课考核成绩:根据实验完成情况和实验报告是否完整确定,实验课成绩占课程总成绩的10%。

五、实验教材、参考书

1、教材:在编

2、参考书:J.Bhasker著,夏宇闻等译《Verilog HDL入门》.北京航空航天大学出版社.2008出版。

FPGA-Verilog试题(西安电子科技大学)

西安电子科技大学考试时间分钟试题题号一二三四五六七八九十总分分数1.考试形式:闭(开)卷;2.本试卷共四大题,满分100分。

班级学号姓名任课教师一、选择题(每题2分,共18分)1.下面哪个是可以用verilog语言进行描述,而不能用VHDL语言进行描述的级别?(A)(A)开关级(B)门电路级(C)体系结构级(D)寄存器传输级2.在verilog中,下列语句哪个不是分支语句?(D)(A)if-else(B)case(C)casez(D)repeat3.下列哪些Verilog的基本门级元件是多输出(D)(A)nand(B)nor(C)and(D)not4.Verilog连线类型的驱动强度说明被省略时,则默认的输出驱动强度为(B)(A)supply(B)strong(C)pull(D)weak5.元件实例语句“notif1#(1:3:4,2:3:4,1:2:4)U1(out,in,ctrl);”中截至延迟的典型值为(B)(A)1(B)2(C)3(D)46.已知“a=1b’1;b=3b'001;”那么{a,b}=(C)(A)4b'0011(B)3b'001(C)4b'1001(D)3b'101第2页共8页7.根据调用子模块的不同抽象级别,模块的结构描述可以分为(ABC)(A)模块级(B)门级(C)开关级(D)寄存器级8.在verilog语言中,a=4b'1011,那么&a=(D)(A)4b'1011(B)4b'1111(C)1b'1(D)1b'09.在verilog语言中整型数据与(C)位寄存器数据在实际意义上是相同的。

(A)8(B)16(C)32(D)64二、简答题(2题,共16分)1.Verilog HDL语言进行电路设计方法有哪几种(8分)1、自上而下的设计方法(Top-Down)2、自下而上的设计方法(Bottom-Up)3、综合设计的方法2.specparam语句和parameter语句在参数说明方面不同之处是什么(8分)。

Verilog HDL数字集成电路设计原理与应用 作者 蔡觉平 第3章

1. 显式连续赋值语句

显式连续赋值语句的语法格式如下:

<net_declaration><range><name>; assign #<delay><name>= Assignment expression;

这种格式的连续赋值语句包含两条语句:第一条语句

是对连线型变量进行类型说明的语句;第二条语句是对这 个连线型变量进行连续赋值的赋值语句。赋值语句是由关 键词assign引导的,它能够用来驱动连线型变量,而且只能 5 对连线型变量进行赋值,主要用于对wire型变量的赋值。

计数字电路更类似于使用一些高级语言(如C语言)进行编程,

17 而且Verilog HDL行为级建模的语法结构与C语言也非常相 似。Verilog HDL提供了许多行为级建模语法结构,为设计 者的使用提供了很大的灵活性。

行为描述常常用于复杂数字逻辑系统的顶层设计中,

也就是通过行为建模把一个复杂的系统分解成可操作的若

end initial过程块在进行仿真时从模拟0时刻开始执行,它

在仿真过程中只执行一次,在执行完一次后该initial过程块

就被挂起,不再执行。如果一个模块中存在多个initial过程 块,则每个initial过程块都是同时从0时刻开始并行执行的。

initial过程块内的多条行为语句可以是顺序执行的,也可以

图3.2-1 Verilog HDL行为描述中模块的构成框架

表3.2-1 Verilog HDL行为描述语句及其可综合性

类 别 过程语句 initial always 串行语句块 begin-end 并行语句块 fork-join 连续赋值语句 assign 过程赋值语句=、<= if-else case,casez,casex forever 循环语句 repeat while for `define 编译向导语句 `include `ifdef,`else,`endif √ √ √ √ √ √ √ √ √ 语 句 可综合性

Verilog-HDL数字集成电路设计原理与应用-作者-蔡觉平-第7章

仿真的结果取决于设计描述是否准确反映了设计的物 理实现。仿真器不是一个静态工具,需要Stimulus(激励)和 Response(输出)。Stimulus由模拟设计工作环境的Testbench 产生,Response为仿真的输出,由设计者确定输出的有效 性。

目前,仿真工具比较多,其中Cadence公司的NCVerilog HDL、Synopsys公司的VCS和Mentor公司的 ModelSim都是业界广泛使用的仿真工具。

7.1 数字集成电路设计流程简介

在EDA技术高度发达的今天,没有一个设计工程师队 伍能够用人工方法有效、全面、正确地设计和管理含有几 3 百万个门的现代集成电路。利用EDA工具,工程师可以从 概念、算法、协议等开始设计电子系统,

大量工作可以通过计算机完成,并可以将电子产品从系统 规划、电路设计、性能分析到封装、版图的整个过程在计 算机上自动完成。这样做有利于缩短设计周期、提高设计 正确性、降低设计成本、保证产品性能,尤其是可增加一 次投片的成功率,因此这种方法在大规模集成电路设计中 已经普遍被采用。

20

7.1.8 物理验证

物理验证通常包括设计规则检测(DRC)、版图与原理 图对照(LVS)和信号完整性分析

(SI)等。其中DRC用来检查版图设计是否满足工艺线 能够加工的最小线宽、最小图形间距、金属宽度、栅和有 源区交叠的最小长度等。如果版图设计违反设计规则,那 么极有可能导致芯片在加工的过程中成为废品。LVS则用 来保证版图设计与其电路设计的匹配,保证它们的一致性。 21 如果不一致,就需要修改版图设计。SI用来分析和调整芯 片设计的一致性,避免串扰噪声、串扰延迟以及电迁移等 问题。

目前主要的物理验证工具有Mentor公司的Calibre、 Cadence公司的Dracula和Diva以及Synopsys公司的Hercules。 此外,各大厂商也推出了针对信号完整性分析的工具。

verilog hdl 习题答案

verilog hdl 习题答案Verilog HDL 习题答案Verilog HDL(硬件描述语言)是一种用于描述数字电路的硬件描述语言,它被广泛应用于数字系统的设计和验证。

在学习Verilog HDL的过程中,练习题是非常重要的,通过解答习题可以加深对Verilog HDL语言的理解,并提高设计和编程的能力。

下面我们将为您提供一些Verilog HDL习题的答案,希望能够帮助您更好地掌握这门语言。

1. 请编写一个Verilog HDL模块,实现一个4位全加器。

module full_adder(input wire a, b, cin,output wire sum, cout);assign sum = a ^ b ^ cin;assign cout = (a & b) | (b & cin) | (a & cin);endmodule2. 请编写一个Verilog HDL模块,实现一个4位加法器。

module adder_4bit(input wire [3:0] a, b,output wire [3:0] sum);wire c0, c1, c2;full_adder fa0(a[0], b[0], 1'b0, sum[0], c0);full_adder fa1(a[1], b[1], c0, sum[1], c1);full_adder fa2(a[2], b[2], c1, sum[2], c2);full_adder fa3(a[3], b[3], c2, sum[3], );endmodule3. 请编写一个Verilog HDL模块,实现一个4位移位寄存器。

module shift_register(input wire clk, rst, shift,input wire [3:0] in,output wire [3:0] out);reg [3:0] reg_data;always @(posedge clk or posedge rst) beginif(rst)reg_data <= 4'b0;else if(shift)reg_data <= {reg_data[2:0], in[0]};elsereg_data <= in;endassign out = reg_data;endmodule以上是一些常见的Verilog HDL习题的答案,通过这些习题的练习,相信您对Verilog HDL语言的掌握会更加深入。

实验二硬件描述语言(VerilogHDL)软件基本使用方法综述

编译通过后系统信息窗口:报告相关的使用芯片类型、使用的逻辑元素个数 等信息

⑷建立波形文件,设置相关端口信号,同实验一基本相同,设置之后保存波形文 件,重新进行编译。

⑸点击时序仿真按钮,进行仿真,观察结果可知完全符合数字选择电路功能。 这种通过Verilog HDL编程实现的功能与电路设计完成的功能完全相同。

⑷Verilog模块的结构特点 • Verilog程序是由若干模块构成的。每个模块的内容 都嵌在module和endmodule两个关键字之间;每个 模块实现特定的逻辑功能。 • 每个模块首先要进行端口定义,并说明输入和输出 口(input、output或inout),然后对模块的功能 进行定义。 • Verilog程序书写格式自由,一行可以写几个语句, 一个语句也可以分多行写,。 • 除了endmodule等少数语句外,每个语句的最后必 须有分号。 • 可用 /*……*/ 和 //……对Verilog程序作注释。 • Verilog程序书写区分大小写,关键字必须小写。

更多控制端口设置

lpm_counter计数器功能仿真波形

模24方向可控计数器电路

⑸Verilog 模块的模板

•module <顶层模块名> (<输入输出端口列表>); •output 输出端口列表; //输出端口声明 •input 输入端口列表; //输入端口声明 •/*定义数据,信号的类型,函数声明*/ •reg 信号名; •//逻辑功能定义 •assign <结果信号名>=<表达式>; //使用assign语句定义逻辑功能 •//用always块描述逻辑功能 •always @ (<敏感信号表达式>) • begin • //过程赋值 • //if-else,case语句 • //while,repeat,for循环语句 • //task,function调用 • end •//调用其它模块 • <调用模块名module_name > <例化模块名> (<端口列表port_list >); •//门元件例化 • 门元件关键字 <例化门元件名> (<端口列表port_list>); •endmodule

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《Verilog HDL 数字集成电路设计原理与应用》上机作业班级:******* 学号:******* 姓名:*******题目1:数字集成电路的verilog HDL 描述与仿真。

要求:(1)学习使用Modelsim 设计和仿真软件; (2)练习教材7.2.1中的例子;(3)掌握设计代码和测试代码的编写; (4)掌握测试仿真流程;(5)掌握Modelsim 软件的波形验证方式。

解答:题目2: 简述begin-end 语句块和fork-join 语句块的区别,并写出下面信号对应的程序代码A B解答:(1)begin-end语句块和fork-join语句块的区别:1、执行顺序:begin-end语句块按照语句顺序执行,fork-join语句块所有语句均在同一时刻执行;2、语句前面延迟时间的意义:begin-end语句块为相对于前一条语句执行结束的时间,fork-join语句块为相对于并行语句块启动的时间;3、起始时间:begin-end语句块为首句开始执行的时间,fork-join语句块为转入并行语句块的时间;4、结束时间:begin-end语句块为最后一条语句执行结束的时间,fork-join语句块为执行时间最长的那条语句执行结束的时间;5、行为描述的意义:begin-end语句块为电路中的数据在时钟及控制信号的作用下,沿数据通道中各级寄存器之间的传送过程。

fork-join语句块为电路上电后,各电路模块同时开始工作的过程。

(2)程序代码:Begin-end语句:module initial_tb1;reg A,B;initialbeginA=0;B=1;#10 A=1;B=0;#10 B=1;#10 A=0;#10 B=0;#10 A=1;B=1;endendmoduleFrk-join语句:module wave_tb2;reg A,B;parameter T=10;initialforkA=0;B=1;#T A=1;B=0;#(2*T) B=1;#(3*T) A=0;#(4*T) B=0;#(5*T) A=1;B=1;joinendmodule题目3. 分别用阻塞和非阻塞赋值语句描述如下图所示移位寄存器的电路图。

解答:(1)阻塞赋值语句module block2(din,clk,out0,out1,out2,out3);input din,clk;output out0,out1,out2,out3;reg out0,out1,out2,out3;always@(posedge clk)beginout0=din;out1=out0;out2=out1;out3=out2;endendmodule(2)非阻塞赋值语句module non_block1 (din,clk,out0,out1,out2,out3);input din,clk;output out0,out1,out2,out3;reg out0,out1,out2,out3;always@(posedge clk)beginout0<=din;out1<=out0;out2<=out1;out3<=out2;endendmodule题目4:设计16位同步计数器要求:(1)分析16位同步计数器结构和电路特点;(2)用硬件描述语言进行设计;(3)编写测试仿真并进行仿真。

解答:(1)电路特点:同步计数器的时间信号是同步的;每当到达最高计数后就会重新计数。

(2)程序代码:module comp_16 (count, clk, rst );output [15:0] count;input clk,rst;reg [15:0] count;always @ (posedge clk)if (rst)count<=16'b0000000000000000;elseif (count==16'b1111111111111111)count<=16'b0000000000000000;elsecount<=count+1;endmodule(3)仿真代码:module comp_16_tb;wire [15:0] count;reg clk,rst;comp_16 U1 (count, clk, rst );always #1 clk=~clk;initialbeginclk=0;rst=0;#1 rst=1;#10 rst=0;#10 rst=1;#10 rst=0;#99999 $finish;endendmodule题目5. 试用Verilog HDL门级描述方式描述如下图所示的电路。

解答:module zy(D0,D1,D2,D3,S1,S2,T0,T1,T2,T3,Z); output Z;input D0,D1,D2,D3,S1,S2; wire T0,T1,T2,T3,wire1,wire2; not U1(wire1,S1), U2(wire2,S2);and U3(T0,D0,wire2,wire1), U4(T1,D1,S1,wire1), U5(T2,D2,S1,wire2), U6(T3,D3,S1,S2); or U7(Z,T0,T1,T2,T3,); endmodule题目6. 试用查找真值表的方式实现真值表中的加法器,写出Verilog HDL 代码:Z解答:module homework6(SUM,COUT,A,B,CIN);output SUM,COUT;input A,B,CIN;reg SUM,COUT;always@(A or B or CIN)case({A,B,CIN})3'b000:SUM<=0;3'b000:COUT<=0;3'b001:SUM<=1;3'b001:COUT<=0;3'b010:SUM<=1;3'b010:COUT<=0;3'b011:SUM<=0;3'b011:COUT<=1;3'b100:SUM<=1;3'b100:COUT<=0;3'b101:SUM<=0;3'b101:COUT<=1;3'b110:SUM<=0;3'b110:COUT<=1;3'b111:SUM<=1;3'b111: COUT<=1;endcaseendmodule题目7:设计16位同步加法器和乘法器要求:(1)分析16位同步加法器和乘法器结构和电路特点;(2)用硬件描述语言进行设计;(3)编写测试仿真并进行仿真。

解答:(1)16位同步加法器和乘法器结构和电路特点:加法器的进位只用考虑一位,但是乘法器的进位要考虑到32位才行。

(2)程序代码:16位同步加法器:module adder(a,b,c,sum,cout);output [15:0]sum;output cout;input [15:0]a,b;input c;assign {cout,sum}=a+b+c;endmodule16位同步乘法器:module multiplier(a,b,mul);input [15:0]a,b;output [31:0]mul;assign mul=a*b;endmodule(3)仿真代码:16位同步加法器:module adder_tb;reg [15:0]a,b;reg c;wire [15:0]sum;wire cout;initialbegina=8;b=8;c=1;endinitialbegin#10 a=16'b1111111111111111;#10 b=1;endadder U2(.a (a),.b (b),.c(c),.cout(cout),.sum(sum));endmodule16位同步乘法器:module multiplier_tb;reg [15:0]a,b;wire [31:0]mul;initialbegina=3;b=8;endinitialbegin#10 a=100;#15 b=100;endmultiplier U1(.a(a),.b(b),.mul(mul));endmodule仿真截图:加法器:乘法器:题目8. 将下面的状态转移图用Verilog HDL描述。

在图中,状态机的输入只与状态的跳转有关,与状态机的输出无关,因此该状态机为摩尔型状态机。

下面为三段式描述方式。

解答:程序代码:module homework8(clk,out,step,clr);output [2:0]out;input step,clk,clr;reg [2:0]out;reg [1:0]state,next_state;always @(posedge clk)state<=next_state;always @(state or clr)if(clr)next_state<=0;elsecase(state)2'b00:case(step)1'b0:begin next_state<=2'b00;out<=3'b001;end1'b1:begin next_state<=2'b01;out<=3'b001;endendcase2'b01:beginout<=3'b010;next_state<=2'b10;end2'b10:case(step)1'b0:begin next_state<=2'b00;out<=3'b100;end1'b1:begin next_state<=2'b11;out<=3'b100;endendcase2'b11:case(step)1'b0:begin next_state<=2'b11;out<=3'b111;end1'b1:begin next_state<=2'b00;out<=3'b111;endendcaseendcaseendmodule仿真代码:module homework8_tb;reg clk,step,clr;wire [3:0]out;always#5 clk=~clk;initialbegin clk=0;clr=1;step=1;endinitialbegin#5clr=0;#10 step=0;#10step=1;endhomework8 U1(clk,out,step,clr);endmodule仿真截图:题目9. 如下图所示电路,若其延迟时间设定如表所示,试写Verilog HDL程序设计该电路。