Jtag的各种引脚定义

JTAG接口

JTAG接口

JTAG口(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行调试和仿真。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

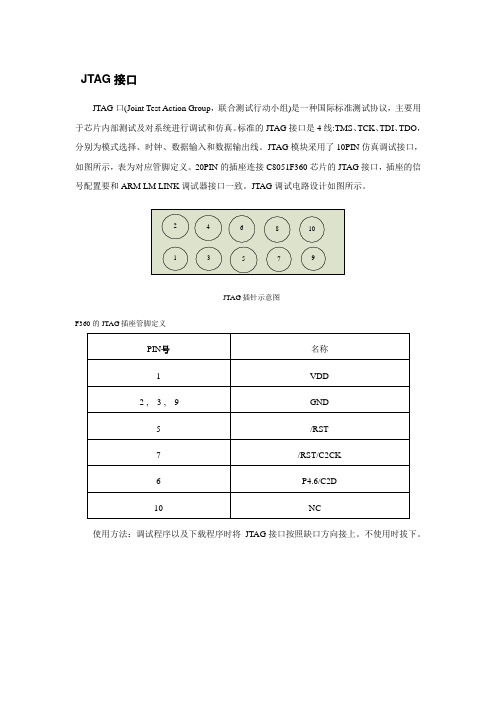

JTAG模块采用了10PIN仿真调试接口,如图所示,表为对应管脚定义。

20PIN的插座连接C8051F360芯片的JTAG接口,插座的信号配置要和ARM LM LINK调试器接口一致。

JTAG调试电路设计如图所示。

136

79

248

5

10

JTAG插针示意图

F360的JTAG插座管脚定义

PIN号名称

1 VDD

2 ,

3 , 9 GND

5 /RST

7 /RST/C2CK

6 P4.6/C2D

10 NC

使用方法:调试程序以及下载程序时将JTAG接口按照缺口方向接上。

不使用时拔下。

Jtag的各种引脚定义

Jtag的各种引脚定义使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。

所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。

以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。

Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。

由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。

正版的Jlink是卖的很贵的。

大概是1000到2000RMB吧。

不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。

所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。

除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。

还有人制作了开源版本的JTAG仿真器——OpenJTAG。

而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。

比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。

还有飞思卡尔公司的USBDM和OSJTAG。

他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。

这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。

JTAG接口引脚定义

标准的JTAG当然是20Pin,但JA TG实际使用的只有4根信号线,再配合电源、地,故又有了很多不同的接口形式,而且现在也渐成标准1.TCK Programmer JTAG Clock(JTAG管脚中的输入时钟信号,对编程和边界扫描都需要)2.GND1 Signal Reference(信号地)3.TDO Target Board Test Data Output(JTAG管脚中串行的输出数据信号,对编程和边界扫描都需要)4.VTref 接开发板电源5.TMS Programmer Test Mode Select(JTAG管脚中的测试选通信号,对编程和边界扫描都需要)6.VJTAG Target Board JTAG Supply V oltage(目标板JTAG电源)7.VPUMP2 Programmer/Target Board Programming Supply V oltage(目标板JTAG电源)8.nTRST Programmer JTAG Test Reset (Hi-Z with 10 kΩ pull-down, HIGH, LOW,ortoggling)(JTAG管脚中异步复位信号,对编程和边界扫描都需要,用10K电阻上拉到Vddp)9.TDI Programmer Test Data Input(JTAG管脚中串行的输入数据信号,对编程和边界扫描都需要)10.GND1 Signal Reference(信号地)Notes:1. Both GND pins must be connected.(所有的地引脚都要连接)2. FlashPro3 can provide VPUMP if there is only one device on the target board.(如果目标板只有一个芯片,则VPUMP可以由FlashPro3提供。

14针与20针jtag接口介绍

JTAG接口定义JTAG(Joint Test Action Group ,联合测试行动小组 ) 是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试, JTAG 技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路 TAP ( Test Access Port ,测试访问口),通过专用的 J TAG 测试工具对内部节点进行测试。

目前大多数比较复杂的器件都支持 JTAG 协议,如 ARM 、 DSP 、 FPGA 器件等。

标准的JTAG 接口是 4 线: TMS 、 TCK 、 TDI 、 TDO ,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

JTAG 测试允许多个器件通过 JTAG 接口串联在一起,形成一个 JTAG 链,能实现对各个器件分别测试。

JTAG 接口还常用于实现 ISP ( In-System Programmable 在系统编程)功能,如对 FLASH器件进行编程等。

通过 JTAG 接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。

目前 JTAG 接口的连接有两种标准,即 14 针接口和 20 针接口,其定义分别如下所示。

14 针JTAG 接口定义:14 针 JTAG 接口定义引脚名称描述1 、 13 VCC 接电源2 、 4 、 6 、 8 、 10 、 14 GND 接地3 nTRST 测试系统复位信号5 TDI 测试数据串行输入7 TMS 测试模式选择9 TCK 测试时钟11 TDO 测试数据串行输出12 NC 未连接20 针 JTAG 接口定义引脚名称描述VTref 目标板参考电压,接电源2 VCC 接电源3 nTRST 测试系统复位信号4、6、8、10、12、14、16、18、20 GND 接地5 TDI 测试数据串行输入7 TMS 测试模式选择9 TCK 测试时钟11 RTCK 测试时钟返回信号13 TDO 测试数据串行输出15 nRESET 目标系统复位信号17 、 19 NC 未连接。

JTAG与SWD引脚对比

JTAG与SWD引脚对比JTAG与SWD引脚对于仿真ARM,TKScope仿真器家庭的AK100/AK100Pro、K8/K9等仿真器提供标准的20PIN调试接口。

接口管脚定义如下。

其中ARM芯片有两种调试模式,一种是JTAG,一种是SWD,二者在管脚上有复用。

具体所用的型号是否支持,需要查看数据手册。

JTAG调试接口引脚JTAG调试接口必须使用VCC、GND电源信号,以及TMS、TCK、TDI、TDO四根调试信号,可选TRST、RESET复位信号和RTCK(同步时钟)信号。

VRef :目标板参考电压信号。

用于检查目标板是否供电,直接与目标板VDD联,并不向外输出电压;GND:公共地信号;TRST:JTAG复位,连接到目标CPU的nTRST引脚,用于复位CPU调试接口的TAP控制器;目标板上应将此脚上拉到高电位,避免意外复位;TDI:仿真器连接至目标CPU的数据输入信号,建议在目标板上将此脚上拉到Vdd;TMS:仿真器输出给目标CPU的JTAG模式设置信号。

必须在目标板上将此脚上拉; TCK:仿真器输出给目标CPU的JTAG时钟信号,建议在目标板上将此脚上拉; TDO:目标CPU返回给仿真器的数据信号;RTCK:目标CPU提供给仿真器的时钟信号。

有些目标要求JTAG的输入与其内部时钟同步。

仿真器利用此引脚的输入可动态地控制自己的TCK速率。

若不使z用此功能,在目标板上将此脚接地,有些芯片可能要求上拉;RESET:仿真器输出至目标CPU的系统复位信号。

’虽然TRST、RESET是可选的信号;但一般都建议接上,使得仿真器能够在连接器件前对器件进行复位,以获得较理想的初始状态,便于后续仿真。

SWD接口引脚SWD是ARM公司提出的另一种调试接口,相对于JTAG接口,使用更少的信号。

四根信号如下:VRef :目标板参考电压信号。

用于检查目标板是否供电,直接与目标板VDD联,并不向外输出电压;GND:公共地信号;SWDIO:串行数据输入输出,作为仿真信号的双向数据信号线,建议上拉;SWCLK:串行时钟输入,作为仿真信号的时钟信号线,建议下拉;SWO:串行数据输出引脚,CPU调试接口可通过SWO引脚输出一些调试信息。

jtag标准 引脚定义

jtag标准引脚定义

JTAG标准的引脚定义

JTAG(Joint Test Action Group)是一种用于测试和调试电子设备的标准接口。

它能够通过几根线路实现对设备内部的观察和控制,用于芯片的生产和维护。

在JTAG标准中,定义了一系列的引脚,用于实现与设备的通信和控制。

根据JTAG标准的定义,JTAG接口包括四根信号线(TMS、TCK、TDO和TDI)和一个共享引脚(TRST)。

这些引脚的定义如下:

1. TMS(Test Mode Select):此引脚用于选择设备的测试模式。

在测试过程中,通过改变TMS引脚的状态,可以控制设备进入不同的测试状态。

2. TCK(Test Clock):此引脚用于提供时钟信号,控制测试数据的传输速率。

TCK信号是通过在TCK引脚上周期性地切换高和低电平来控制的。

3. TDO(Test Data Out):此引脚用于从设备读取测试数据。

在测试过程中,

设备通过TDO引脚将测试数据输出。

4. TDI(Test Data In):此引脚用于向设备输入测试数据。

在测试过程中,通

过TDO引脚将测试数据输入给设备。

5. TRST(Test Reset):此引脚用于将设备重置为初始状态,以便开始测试过程。

TRST引脚是一个共享引脚,可以在需要的情况下选择使用或不使用。

以上就是JTAG标准中定义的引脚及其功能的简要介绍。

这些引脚的正确使用

可以帮助测试人员有效地测试和调试电子设备。

JTAG接口已经成为现代电子设备

测试和调试的关键部分,并广泛应用于各个领域。

5pin jtag标准

5pin jtag标准

JTAG(联合测试行动组)是一种用于测试和调试集成电路的标准接口。

JTAG接口通常包括20个引脚,但也有其他版本,其中包括5引脚JTAG标准。

这种5引脚JTAG标准通常被称为"CJTAG"(Compact JTAG),它是一种用于连接到嵌入式设备的小型JTAG接口。

5引脚JTAG标准通常包括以下引脚:

1. TCK(Test Clock):测试时钟,用于同步测试操作。

2. TMS(Test Mode Select):测试模式选择,用于指定JTAG操作的模式。

3. TDI(Test Data Input):测试数据输入,用于向被测试设备输入测试数据。

4. TDO(Test Data Output):测试数据输出,用于从被测试设备输出测试数据。

5. TRST(Test Reset):测试复位,用于复位JTAG链上的设备。

5引脚JTAG标准通常用于嵌入式设备或其他空间受限的应用,它提供了一种紧凑的接口来进行测试和调试操作。

JTAG简述

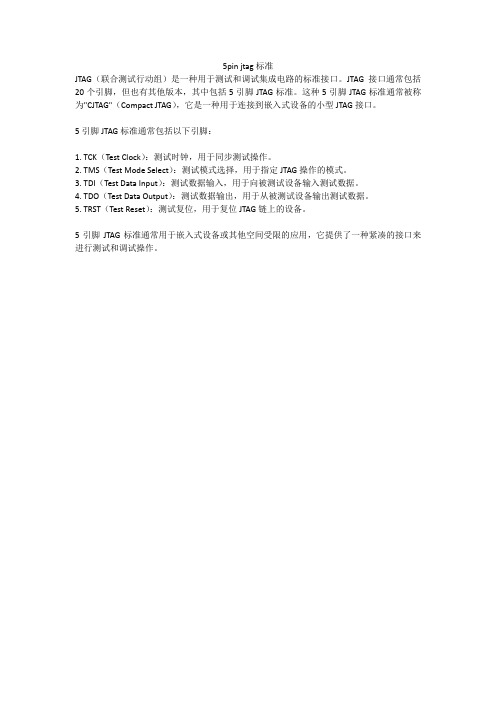

当 TP A 控制器处于该状态时。 指令不发生 变化,当前指令所选择的测试数据寄 存器都将

保持原先的状态。 ( ) as-R 7 PueD 状态 PueD 状态将暂时终止TI TO as-R D 和 D 之间连接的数据寄存器的串行移动。只要 TS M为 低, A 控制器将保持这个状态, TK TP 在 C 上升沿将 TS M 置高,TP A 控制器将移至 Ei -R x D t 2

( ) h f-R S itD 状态 5

在该状态下, D 和T 在 TI D 之间连接调试数据寄存器, TK O 在 C 每个上升沿将数据串 行移 动。 C 上升沿将TS 在TK M 置高,A 控制器将移至Eil R TP xt- 状态,在TK D C 上升沿将TS M 置低, TP A 控制器将移至 SitD 状态。 hf-R

U d t-R paa D

切妞- 1 肠 日- O 加 二1

U dbI pa - aR

0' 0 0 - t

图22 测试访问端口TP - A 控制器状态转移图

TP A 控制器中的 1 个状态详细描述如下: 6 () et i Rst 1 Ts Lgc e 状态 o e 在该状态下,通过 icd 指令,使调试停止。无论处在 TP doe A 控制器何种状态, 只要在 5 次TK C 上升沿 T 置高,都将处于该状态。如果在 TK O C 上升沿中由于错误的US 信号,结束 了该状态,在连续的3 C 上升沿下TS 个TK M 置高, 将返回该状态。

US

输入

TI D

输入

TO D

输出 输入

n RT TS

JA 可以 TG 对同 一块电 路板上多块芯片进行测试。 TS. 和TS nRT TK M 信号并行至各个芯片, C 而 一块芯片的TO D 接至下一芯片的TI D.

JTAG的引脚定义与各种JTAG的引脚序号与引脚名的对应关系

JTAG的引脚定义与各种JTAG的引脚序号与引脚名的对应关系JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。

一、引脚定义Test Clock Input (TCK) -----强制要求1TCK在IEEE 1149.1标准里是强制要求的。

TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

Test Mode Selection Input (TMS) -----强制要求2TMS信号在TCK的上升沿有效。

TMS在IEEE 1149.1标准里是强制要求的。

TMS信号用来控制TAP状态机的转换。

通过TMS信号,可以控制TAP在不同的状态间相互转换。

Test Data Input (TDI) -----强制要求3TDI在IEEE 1149.1标准里是强制要求的。

TDI是数据输入的接口。

所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。

Test Data Output (TDO) -----强制要求4TDO在IEEE 1149.1标准里是强制要求的。

TDO是数据输出的接口。

所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。

Test Reset Input (TRST) ----可选项1这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。

TRST可以用来对TAP Controller进行复位(初始化)。

因为通过TMS也可以对TAP Controll进行复位(初始化)。

所以有四线JTAG 与五线JTAG之分。

(VTREF) -----强制要求5接口信号电平参考电压一般直接连接Vsupply。

这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?)Return Test Clock ( RTCK) ----可选项2可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。

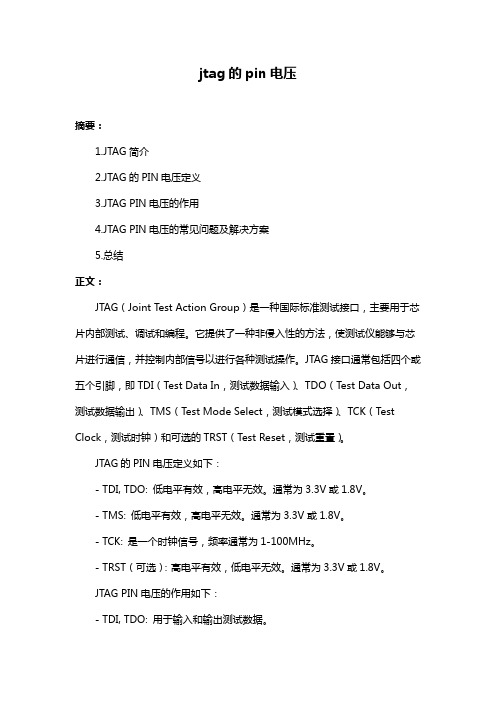

jtag的pin电压

jtag的pin电压摘要:1.JTAG简介2.JTAG的PIN电压定义3.JTAG PIN电压的作用4.JTAG PIN电压的常见问题及解决方案5.总结正文:JTAG(Joint Test Action Group)是一种国际标准测试接口,主要用于芯片内部测试、调试和编程。

它提供了一种非侵入性的方法,使测试仪能够与芯片进行通信,并控制内部信号以进行各种测试操作。

JTAG接口通常包括四个或五个引脚,即TDI(Test Data In,测试数据输入)、TDO(Test Data Out,测试数据输出)、TMS(Test Mode Select,测试模式选择)、TCK(Test Clock,测试时钟)和可选的TRST(Test Reset,测试重置)。

JTAG的PIN电压定义如下:- TDI, TDO: 低电平有效,高电平无效。

通常为3.3V或1.8V。

- TMS: 低电平有效,高电平无效。

通常为3.3V或1.8V。

- TCK: 是一个时钟信号,频率通常为1-100MHz。

- TRST(可选):高电平有效,低电平无效。

通常为3.3V或1.8V。

JTAG PIN电压的作用如下:- TDI, TDO: 用于输入和输出测试数据。

- TMS: 用于选择和控制测试模式。

- TCK: 用于产生测试时钟,驱动JTAG操作。

- TRST(可选):用于重置测试状态,以便在测试过程中进行复位操作。

在实际应用中,JTAG PIN电压可能遇到一些常见问题,例如:1.不同电压等级的PIN连接在一起,可能导致信号干扰或损坏。

2.PIN电压与实际电路中的其他电压等级不匹配,可能影响JTAG功能的正常工作。

3.JTAG接口的ESD保护不足,可能导致静电放电损坏。

针对以上问题,可以采取以下解决方案:1.确保使用相同电压等级的PIN连接,避免不同电压等级的PIN直接相连。

2.在设计电路时,确保JTAG PIN电压与其他电路电压等级匹配。

JTAG使用说明

JTAG使用说明遵循JTAG的器件包含以下几个管脚TCK 测试时钟输入,它和系统时钟不同TDI测试数据输入,通过它数据移位进入器件TDO测试数据输出,通过它数据从器件移出TMS测试模式选择,在JTAG规范中TMS命令选择测试模式TRST测试复位输入,它为TAP控制器提供异步初始化器件的测试支持功能是通过TAP控制器来实现的。

TAP是一个状态机,它控制控制所有相关操作,每种遵循JTAG的器件都有自己的TAP控制器,通过TCK和TMS可以使状态机内部的状态发生变化,从而支持诸如断点、单步、内部观察等调试工作。

本章针对ARM7TDMI介绍调试结构。

ARM的调试体系采用协议转换器来使调试器通过JTAG与ARM核直接通信。

前面JTAG标准中提到的扫描链功能是测试用,这里把它作为调试用:捕获数据总线上的信号并向内核或存储器插入新的信息。

ARM7TDMI-S核内具有EmbeddedICE逻辑,EmbeddedICE逻辑提供对片内调试的支持。

调试指令直接通过扫描链插入ARM内核并执行。

根据插入调试指令的不同,内核可以处于观察、保存或改变状态。

ARM的调试体系可以使程序指令执行速度处于调试速度或全速运行。

在ARM中采用JTAG的特点是:通过JTAG接口可以观察ARM内核状态和系统状态(注意:系统状态包括片内外设,不同于内核状态);不占用额外的目标系统资源;提供传统的断点访问和观察点访问;不再需要另外的UART端口来和监控程序通信。

围绕ARM内核有两个扫描链:围绕整个内核外围的一个扫描链以及仅仅覆盖数据总线和断点的扫描链。

由于后者的链比较短,从而使调试指令和数据可以快速插入内核,避免了额外的时间ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

jtag的工作原理

jtag的工作原理

JTAG(Joint Test Action Group)是一种用于测试和调试电子

设备的接口标准。

其工作原理如下:

1. 链接:JTAG接口通常由四个引脚组成,分别是TCK(测试时钟)、TMS(测试模式选择)、TDI(测试数据输入)和TDO(测试数据输出)。

这四个引脚通过线路与芯片内部的

测试逻辑连接起来。

2. 测试模式选择:在测试之前,需要将JTAG接口设置为测试模式。

通过在TMS引脚上输入一系列控制位,可以实现

JTAG接口的状态切换和操作控制。

例如,可以将JTAG设置

为测试模式、诊断模式或者配置模式。

3. 测试数据输入:测试数据可以通过TDI引脚输入到被测试

的设备中。

这些测试数据可以是测试模式命令、配置数据或者其他需要进行测试的输入信号。

4. 测试数据输出:被测试设备的测试逻辑会产生一些输出信号,这些信号可以通过TDO引脚输出到JTAG接口。

这样,测试

人员可以读取和分析这些信号,并判断设备的状态和运行情况。

5. 时序控制:测试过程中,TCK引脚提供一个时钟信号,控

制JTAG接口的状态转换和数据传输。

测试人员可以通过调整时钟频率来控制测试速度和数据传输的稳定性。

总的来说,JTAG接口利用TCK、TMS、TDI和TDO引脚之

间的通信,实现了对电子设备的测试和调试。

通过该接口,测试人员可以控制设备的状态,输入测试数据,并读取设备的输出信号,从而验证设备的正确性和性能。

JTAG修复刷机成砖头问题

参考图片:JTAG引脚定义:TCK——测试时钟输入;TDI——测试数据输入,数据通过TDI输入JTAG口;TDO——测试数据输出,数据通过TDO从JTAG口输出;TMS——测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式。

可选引脚TRST——测试复位,输入引脚,低电平有效。

含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。

JTAG的TCK、TDI、TMS、TDO分别接PC并口的2、3、4、11线上,通过程序将对JTAG 口的控制指令和目标代码从PC的并口写入JTAG的BSR中电路设计和编程中的注意事项①Flash芯片的WE、CE、OE等控制线必须与SA1110的BSR相连。

只有这样,才能通过BSR控制Flash的相应引脚。

②JTAG口与PC并口的连接线要尽量短,原则上不大于15cm。

③Flash在擦写和编程时所需的工作电流较大,在选用系统的供电芯片时,必须加以考虑。

④为提高对Flash的编程速度,尽量使TCK不低于6MHz,可编写烧写Flash程序时实现。

剩下的工作就是联机和写入备份好的DATA文件.找一个25针LPT的公口按上面的图焊接起来在电脑主板的BIOS里面须把LPT端口设为ecp模式把接口接到电脑上,插上充电器,按开机键,如果线没接错,此时就可在接口软件中发现cpu 了.关于jtag:JTAG是英文“Joint Test Action Group(联合测试行为组织)”的词头字母的简写,该组织成立于1985 年,是由几家主要的电子制造商发起制订的PCB 和IC 测试标准。

JTAG 建议于1990 年被IEEE 批准为IEEE1149.1-1990 测试访问端口和边界扫描结构标准。

该标准规定了进行边界扫描所需要的硬件和软件。

自从1990 年批准后,IEEE 分别于1993 年和1995 年对该标准作了补充,形成了现在使用的IEEE1149.1a-1993 和IEEE1149.1b-1994。

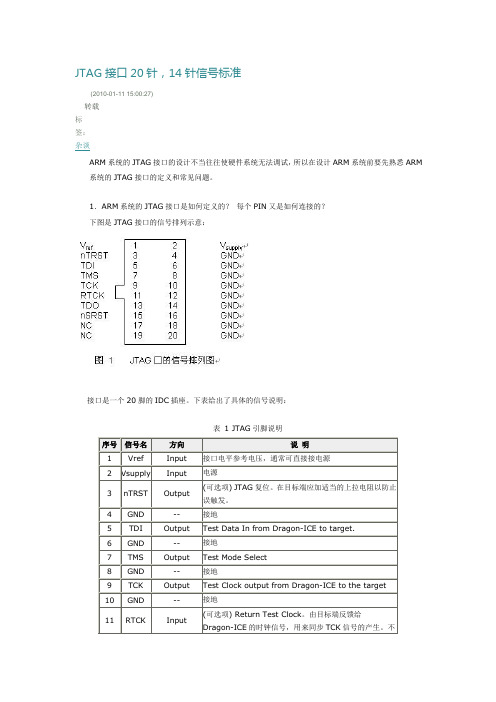

JTAG接口20针,14针信号标准

JTAG接口20针,14针信号标准(2010-01-11 15:00:27)转载标签:杂谈ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM 系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

下表给出了具体的信号说明:表1 JTAG引脚说明序号信号名方向说明1 Vref Input 接口电平参考电压,通常可直接接电源2 Vsupply Input 电源3 nTRST Output (可选项) JTAG复位。

在目标端应加适当的上拉电阻以防止误触发。

4 GND -- 接地5 TDI Output Test Data In from Dragon-ICE to target.6 GND -- 接地7 TMS Output Test Mode Select8 GND -- 接地9 TCK Output Test Clock output from Dragon-ICE to the target10 GND -- 接地11 RTCK Input (可选项) Return Test Clock。

由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。

不使用时可以直接接地。

12GND -- 接地 13TDO Input Test Data Out from target to Dragon-ICE. 14 GND -- 接地15 nSRST Input/Output (可选项) System Reset ,与目标板上的系统复位信号相连。

可以直接对目标系统复位,同时可以检测目标系统的复位情况。

为了防止误触发,应在目标端加上适当的上拉电阻。

16GND -- 接地 17NC 保留 18GND -- 接地 19NC -- 保留 20 GND -- 接地。

JTAG接口的定义及常见问题

JTAG接口的定义及常见问题ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM 系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的?下图是JTAG接口的信号排列示意:接口是一个20脚的IDC插座。

下表给出了具体的信号说明:表 1 JTAG引脚说明序号信号名方向说明1 Vref Input 接口电平参考电压,通常可直接接电源2 Vsupply Input 电源3 nTRST Output (可选项) JTAG复位。

在目标端应加适当的上拉电阻以防止误触发。

4 GND -- 接地5 TDI Output Test Data In from Dragon-ICE to target.6 GND -- 接地7 TMS Output Test Mode Select8 GND -- 接地9 TCK Output Test Clock output from Dragon-ICE to the target10 GND -- 接地11 RTCK Input (可选项) Return Test Clock。

由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。

不使用时可以直接接地。

12 GND -- 接地13 TDO Input Test Data Out from target to Dragon-ICE.14 GND -- 接地15 nSRST Input/Output (可选项) System Reset,与目标板上的系统复位信号相连。

可以直接对目标系统复位,同时可以检测目标系统的复位情况。

为了防止误触发,应在目标端加上适当的上拉电阻。

16 GND -- 接地17 NC -- 保留18 GND -- 接地19 NC -- 保留20 GND -- 接地2.目标系统如何设计?目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。

jtag工作原理详解

jtag工作原理详解JTAG(Joint Test Action Group)工作原理详解JTAG(Joint Test Action Group)是一种用于测试和调试集成电路(IC)的标准接口。

它是由IEEE(Institute of Electrical and Electronics Engineers)制定的一种通信协议,用于在芯片设计和创造过程中进行测试、调试和编程。

JTAG接口通常由四个或者更多的引脚组成,包括TMS(Test Mode Select)、TCK(Test Clock)、TDI(Test Data Input)和TDO(Test Data Output)。

这些引脚允许测试设备与被测试芯片进行通信,并在测试模式下对芯片进行控制和数据传输。

JTAG工作原理如下:1. 测试模式选择(TMS):TMS引脚用于选择测试模式。

通过在TMS引脚上输入不同的测试模式序列,可以控制芯片进入不同的测试模式,如测试模式、编程模式、调试模式等。

2. 测试时钟(TCK):TCK引脚提供测试时钟信号,用于同步测试设备和被测试芯片之间的数据传输。

测试时钟的频率可以根据需要进行调整,通常在几百kHz 到几十MHz之间。

3. 测试数据输入(TDI):TDI引脚用于向被测试芯片输入测试数据。

测试设备可以通过TCK引脚提供的时钟信号,将测试数据逐位地输入到被测试芯片中。

4. 测试数据输出(TDO):TDO引脚用于从被测试芯片输出测试数据。

被测试芯片通过TCK引脚提供的时钟信号,将测试数据逐位地输出到TDO引脚上,供测试设备读取。

在JTAG测试过程中,测试设备通过TMS引脚控制芯片进入测试模式,并通过TCK引脚提供时钟信号。

测试设备可以通过TDI引脚向芯片输入测试数据,并通过TDO引脚从芯片输出测试数据。

通过这种方式,测试设备可以对芯片进行各种测试操作,如扫描路径测试(Scan Path Test)、逻辑状态分析(Logic State Analysis)等。

jtag各类接口针脚定义含义以及swd接线方式

JTAG各类接口针脚定义、含义以及SWD接线方式JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。

一、引脚定义Test Clock Input (TCK) -----强制要求1TCK在IEEE1149.1标准里是强制要求的。

TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

Test Mode Selection Input (TMS) -----强制要求2TMS信号在TCK的上升沿有效。

TMS在IEEE1149.1标准里是强制要求的。

TMS信号用来控制TAP状态机的转换。

通过TMS信号,可以控制TAP在不同的状态间相互转换。

Test Data Input (TDI) -----强制要求3TDI在IEEE1149.1标准里是强制要求的。

TDI是数据输入的接口。

所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。

Test Data Output (TDO) -----强制要求4TDO在IEEE1149.1标准里是强制要求的。

TDO是数据输出的接口。

所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。

Test Reset Input (TRST) ----可选项1这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。

TRST可以用来对TAPController进行复位(初始化)。

因为通过TMS也可以对TAP Controll进行复位(初始化)。

所以有四线JTAG与五线JTAG之分。

(VTREF) -----强制要求5接口信号电平参考电压一般直接连接Vsupply。

这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?)Return Test Clock ( RTCK) ----可选项2可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK 信号的产生,不使用时直接接地。

jtag的pin电压

jtag的pin电压JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

它通过一系列的引脚(Pin)来提供测试和调试功能。

每个引脚都有其特定的电压要求,以下是关于JTAG引脚电压的相关参考内容。

1. VCC(电源)引脚电压:通常为3.3V或5V。

这个引脚提供JTAG逻辑电路所需的电源。

2. TDI(测试数据输入)引脚电压:通常为VCC引脚的电压(3.3V或5V)。

这个引脚用于将测试数据输入到被测芯片中。

3. TDO(测试数据输出)引脚电压:取决于被测芯片的工作电压。

这个引脚用于将测试数据从被测芯片中输出到JTAG控制器。

4. TCK(测试时钟)引脚电压:通常为VCC引脚的电压。

这个引脚提供测试时钟信号,用于同步测试和调试操作。

5. TMS(测试模式选择)引脚电压:通常为VCC引脚的电压。

这个引脚用于控制JTAG设备的状态转换。

6. TRST(测试复位)引脚电压:通常为VCC引脚的电压。

这个引脚用于对JTAG设备进行复位操作。

除了上述的基本引脚,JTAG标准还提供了一些附加引脚,如中断引脚(INT),用于在测试和调试过程中提供额外的控制和信息传输。

需要注意的是,具体的引脚电压要求可能因不同的芯片和设备而异。

因此,在使用JTAG接口进行测试和调试时,建议参考所使用芯片的数据手册或相关文档,以确保正确的电压设置。

JTAG引脚电压的设置对于JTAG测试和调试过程的可靠性和正确性非常重要。

不正确的引脚电压设置可能导致信号传输错误,测试失败或甚至损坏被测芯片。

因此,确保正确理解和设置JTAG引脚电压是进行JTAG测试和调试的关键一步。

总结起来,JTAG的引脚电压设置涉及到VCC、TDI、TDO、TCK、TMS、TRST等引脚,其中VCC是电源引脚,其余引脚主要用于测试和调试操作。

具体的引脚电压要求应参考所使用芯片的数据手册或相关文档,以确保正确的电压设置。

JTAG引脚电压的正确设置是保证测试和调试过程可靠和正确的关键。

关于I2C、UART、SPI、RS232、JTAG,ISP、DEBUG神马的一些概念和理解

一、UART总线和硬件结构-----------Universal Asynchronous Receiver/TransmitterUART是一种通用异步串行数据总线,该总线双向通信,可以实现全双工传输和接收。

因为计算机内部采用并行数据,不能直接把数据发到Modem,必须经过UART整理才能进行异步传输。

串行的两条线TXD --- UART数据发送,RXD --- UART数据接收UART通用异步接收/发送装置,是一个并行输入成为串行输出的芯片,它是用于控制计算机与串行设备的芯片,通常集成在主板上,多数是16550AFN芯片。

,有一点要注意的是,它提供了RS-232C数据终端设备接口 ,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信,所以说UART是一种异步串行全双工总线,硬件映射为一个芯片,可以与使用RS-232接口的设备直接通信二、I2C总线和硬件结构------------Inter-Integrated CircuitI2C,由PHILIPS公司1992 年开发的,I2C串行总线一般有两根信号线,一根是双向的数据线SDA,另一根是时钟线SCL。

所有接到I2C总线设备上的串行数据SDA都接到总线的SDA上,各设备的时钟线SCL接到总线的SCL上,用于连接微控制器及其外围设备,一般在对芯片进行扩展中是使用,通用I/O端口也可以作为I2C 总线接口。

所以说I2C是一种同步串行半双工总线,硬件映射为一个两个接口电路,对于没有I2C总线接口的,可以使用通用I/O端口来实现I2C的功能与其他设备进行通信(根据协议编写程序)三、SPI总线和硬件结构--------------Serial Peripheral Interface高速同步串行口,是一种标准的四线同步双向串行总线,一种四线同步总线系统,一种同步串行外设接口,为全双工通信,是Motorola公司推出的一种同步串行通讯方式,它可以使MCU与各种外围设备以串行方式进行通信以交换信息在主器件的移位脉冲下,数据按位传输,高位在前,低位在后,该接口一般使用4条线:(1 )MOSI –主器件数据输出,从器件数据输入(2)MISO –主器件数据输入,从器件数据输出(3)SCLK –时钟信号,由主器件产生(4)/SS –从器件使能信号,由主器件控制(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)所以说,SPI是同步串行全双工总线,硬件映射为四个接口四、RS-232接口(DB9)是现在主流的串行通信接口之一,传输速率较低,在异步传输时,波特率为20Kbps.接口硬件为9针功能如下:1 DCD 载波检测2 RXD 接收数据3 TXD 发送数据4 DTR 数据终端准备好5 SG 信号地6 DSR 数据准备好7 RTS 请求发送8 CTS 允许发送9 RI 振铃提示还有两个接地线10、11(不是针)串口通信一般用2、3、7、8通信,5、(10、11)接地,其他不用,特别的作为debug口7、8也不用五、COM接口即串行通讯端口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。

所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。

以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。

Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。

由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。

正版的Jlink是卖的很贵的。

大概是1000到2000RMB吧。

不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。

所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。

除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。

还有人制作了开源版本的JTAG仿真器——OpenJTAG。

而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。

比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。

还有飞思卡尔公司的USBDM和OSJTAG。

他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。

这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。

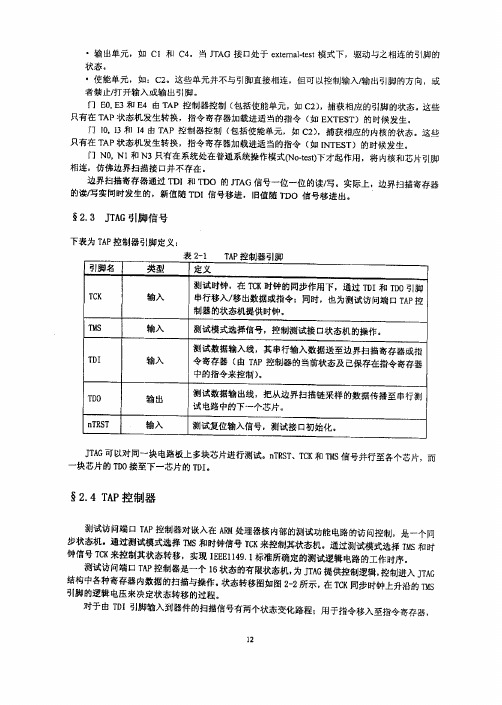

今天我要说的是几种JTAG仿真器的引脚定义,首先我看看比较常见的JTAG 20-Pin的引脚接口如下:

上面的图中已经有了20Pin和10Pin对应的关系了,实际上JTAG的下载和调试至少需要四根线就行了—— TDI、TCK、TDO、TMS。

从20Pin的引脚图中我们也发现右边有九个脚全是GND,这些脚完全可以舍去,所以就有了右边的10Pin的JTAG引脚图。

不过10Pin的引脚图里面引脚也比较多,所以又有人根据JTAG的协议改进产生了新的引脚定义——SWD协议。

SWD协议比JTAG使用的脚更少,至少三根线就可以了——SWCLK、SWDIO、GND。

而且现在的Jlink基本上都支持JTAG和SWD两种协议,你只要使用转接板,或者是直接使用杜邦线连接即可。

最近,我接触到了Freescale的K60芯片,FSL官方有提供了一款开源的JTAG调试工具——OSJTAG。

不知FSL是否是故意与别人不同,它的JTAG引脚与Jlink的引脚又有所不同,如下图所示:

好吧,我做过试验,直接用杜邦线将OSJTAG的引脚与Jlink定义的下载接口相连接,也是可以下载进去程序的,那么干嘛定义那么多的不同的引脚定义呢?统一一点不好么?。