数字电子技术第8章习题解答

数字电子技术第8章 模拟信号与数字信号的转换答案

一、填空题1. DAC ADC2. 采样 保持 量化 编码3. 最小输出模拟量 最小输入模拟量4. 2.565. 正比 之差6. 双积分型 逐次逼近型7. 分辨率8. 1个LSB 的输出变所对应的模拟量的范围 不可二、选择题1. B2. A3. A4. B5. C6. A三、计算与思考题1. 略2. 略3. 略4. 略5. 解:(1)当8位D/A 转换器的最小输出电压增量为0.02V 时,输入代码为01001101所对应的输出电压:U O =0.02(26+23+22+20)=1.54V 。

(2)由于D/A 转换器的转换误差为1/2LSB ,若要求D/A 转换器的精度小于0.25%(精度是转换误差与最大输出电压之比),则其分辨率应小于0.5%,因此这一8位D/A 转换器满足要求。

6. 解:V V LSB 005.010231101211010≈⨯=-⨯=2000005.01012==-N20002≈N11≈N所以,该电路输入二进制数字量的位数N应是11。

7. 解:(1)当8位D/A 转换器的最小输出电压增量为0.02V 时,输入代码为01001101所对应的输出电压:U O =0.02(26+23+22+20)=1.54V 。

(2)8位D/A 转换器的分辨率百分数为:%3922.0%1001218=⨯- (3)由于D/A 转换器的转换误差为1/2LSB ,若要求D/A 转换器的精度小于0.25%(精度是转换误差与最大输出电压之比),则其分辨率应小于0.5%,因此这一8位D/A 转换器满足要求。

8. 解:因为N V u N REF i ⋅=2n REF i V u 2⋅=n REFi V u 2⋅= 所以,当输入电压为4.48V时,1157.114256448.021048.482≈≈⨯=⨯=N (采用四舍五入法) 转换成二进制数为01110011。

当输入电压为7.81V时,2009.199256781.021081.782≈≈⨯=⨯=N (采用四舍五入法) 转换成二进制数为11001000。

数字电子技术课后习题答案(全部)

第一章数制与编码1.1自测练习1.1.1、模拟量数字量1.1.2、(b)1.1.3、(c)1.1.4、(a)是数字量,(b)(c)(d)是模拟量1.2 自测练习1.2.1. 21.2.2.比特bit1.2.3.101.2.4.二进制1.2.5.十进制1.2.6.(a)1.2.7.(b)1.2.8.(c)1.2.9.(b)1.2.10.(b)1.2.11.(b)1.2.12.(a)1.2.13.(c)1.2.14.(c)1.2.15.(c)1.2.16.10010011.2.17.111.2.18.1100101.2.19.11011.2.20.8进制1.2.21.(a)1.2.22.0,1,2,3,4,5,6,71.2.23.十六进制1.2.24.0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F 1.2.25.(b)1.3自测练习1.3.1.1221.3.2.675.521.3.3.011111110.011.3.4.521.3.5.1BD.A81.3.6.1110101111.11101.3.7.38551.3.8.28.3751.3.9.100010.111.3.10.135.6251.3.11.570.11.3.12.120.51.3.13.2659.A1.4自测练习1.4.1.BCD Binary coded decimal 二—十进制码1.4.2.(a)1.4.3.(b)1.4.4.8421BCD码,4221BCD码,5421BCD1.4.5.(a)1.4.6.011001111001.10001.4.7.111111101.4.8.101010001.4.9.111111011.4.10.61.051.4.11.01011001.011101011.4.12.余3码1.4.13.XS31.4.14.XS31.4.15.1000.10111.4.16.1001100000111.4.17.521.4.18.110101.4.19.0101111.4.20.(b)1.4.21.ASCII1.4.22.(a)1.4.23.ASCII American Standard Code for Information Interchange美国信息交换标准码EBCDIC Extended Binary Coded Decimal Interchange Code 扩展二-十进制交换吗1.4.24.10010111.4.25.ASCII1.4.26.(b)1.4.27.(b)1.4.28.110111011.4.29.-1131.4.30.+231.4.31.-231.4.32.-861.5 自测练习 1.5.1 略1.5.2 11011101 1.5.3 010001011.5.4 11100110 补码形式 1.5.5 011111011.5.6 10001000 补码形式 1.5.7 11100010 补码形式习题1.1 (a )(d )是数字量,(b )(c )是模拟量,用数字表时(e )是数字量,用模拟表时(e )是模拟量 1.2 (a )7, (b )31, (c )127, (d )511, (e )40951.3 (a )22104108⨯+⨯+, (b )26108108⨯+⨯+,(c )321102105100⨯+⨯+⨯+(d )322104109105⨯+⨯+⨯+ 1.4 (a )212121⨯+⨯+, (b )4311212121⨯+⨯+⨯+, (c )64212+12+12+12+1⨯⨯⨯⨯(d )9843212+12+12+12+12⨯⨯⨯⨯⨯ 1.5 2201210327.15310210710110510--=⨯+⨯+⨯+⨯+⨯,3210-1-221011.0112+02+12+12+02+12=⨯⨯⨯⨯⨯⨯,210-18437.448+38+78+48=⨯⨯⨯⨯, 10-1-2163A.1C 316+A 16+116+C 16=⨯⨯⨯⨯1.6 (a )11110, (b )100110,(c )110010, (d )1011 1.7 (a )1001010110000, (b )10010111111.8 110102 = 2610, 1011.0112 = 11.37510, 57.6438 = 71.81835937510, 76.EB 16= 118.91796875101.9 1101010010012 = 65118 = D4916,0.100112 = 0.468 = 0.9816,1011111.011012 = 137.328 = 5F.68161.10 168 = 1410,1728 = 12210,61.538 = 49.671875, 126.748 = 86.9375101.11 2A 16 = 4210 = 1010102 = 528, B2F 16 = 286310 = 1011001011112 = 54578, D3.E 16= 211.87510 = 11010011.11102 = 323.78, 1C3.F916 = 451.9726562510 = 111000011.111110012 = 703.76281.12 (a )E, (b )2E, (c )1B3, (d )349 1.13 (a )22, (b )110, (c )1053, (d )2063 1.14 (a )4094, (b )1386, (c )49282 1.15(a )23, (b )440, (c )27771.16 198610 = 111110000102 = 00011001100001108421BCD , 67.31110 = 1000011.010012 =01100111.0011000100018421BCD , 1.183410 = 1.0010112 = 0001.00011000001101008421BCD ,0.904710 = 0.1110012 = 0000.10010000010001118421BCD1.17 1310 = 000100118421BCD = 01000110XS3 = 1011Gray, 6.2510 = 0110.001001018421BCD=1001.01011000 XS3 = 0101.01Gray,0.12510= 0000.0001001001018421BCD= 0011.010*********XS3 = 0.001 Gray1.18 101102 = 11101 Gray,0101102 = 011101 Gray1.19 110110112 = 0010000110018421BCD,45610 = 0100010101108421BCD,1748=0010011101008421BCD,2DA16 = 0111001100008421BCD,101100112421BCD = 010*********BCD, 11000011XS3 = 100100008421BCD1.20 0.0000原= 0.0000反= 0.0000补,0.1001原= 0.1001反= 0.1001补,11001原= 10110反= 10111补1.21 010100原= 010100补,101011原= 110101补,110010原= 101110补,100001原=111111补1.22 1310 = 00001101补,11010 = 01101110补,-2510 = 11100111补,-90 =10100110补1.23 01110000补= 11210,00011111补= 3110,11011001补= -3910,11001000补= -56101.24 1000011 1000001 1010101 1010100 1001001 1001111 1001110 0100001 01000001001000 1101001 1100111 1101000 0100000 1010110 1101111 1101100 1110100 1100001 1100111 11001011.25 0100010 1011000 0100000 0111101 0100000 0110010 0110101 0101111 101100101000101.26 BEN SMITH1.27 00000110 100001101.28 01110110 10001110第二章逻辑门1.1 自测练习2.1.1. (b)2.1.2. 162.1.3. 32, 62.1.4. 与2.1.5. (b)2.1.6. 162.1.7. 32, 62.1.8. 或2.1.9. 非2.1.10. 12.2 自测练习=⋅2.2.1. F A B2.2.2. (b)2.2.3. 高2.2.4. 322.2.5. 16,52.2.6. 12.2.7. 串联2.2.8. (b)2.2.9. 不相同2.2.10. 高2.2.11. 相同2.2.12. (a)2.2.13. (c)2.2.14. 奇2.3 自测练习2.3.1. OC,上拉电阻2.3.2. 0,1,高阻2.3.3. (b)2.3.4. (c)2.3.5. F A B=⋅, 高阻2.3.6. 不能2.4 自测练习1.29 TTL,CMOS1.30 Transisitor Transistor Logic1.31 Complementary Metal Oxide Semicoductor1.32 高级肖特基TTL,低功耗和高级低功耗肖特基TTL1.33 高,强,小1.34 (c)1.35 (b)1.36 (c)1.37 大1.38 强1.39 (a)1.40 (a)1.41 (b)1.42 高级肖特基TTL1.43 (c)习题2.1 与,或,与2.2 与门,或门,与门2.3 (a)F=A+B, F=AB (b)F=A+B+C, F=ABC (c)F=A+B+C+D, F=ABCD2.4 (a )0 (b )1 (c )0 (d )0 2.5 (a )0 (b )0 (c )1 (d )0 2.6 (a )1 (b )1 (c )1 (d )1 2.7 (a )4 (b )8 (c )16 (d )32 2.8 (a )3 (b )4 (c )5 (d )62.9 (a )(b ) A B C D F 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 1 0 1 1 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 1 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 0 0 1 11112.10 Y AB AC =+2.11A B C Y 0 0 0 0 0 0 1 0 011A B C F 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 11110 1 1 11 0 0 01 0 1 11 1 0 01 1 1 12.122.13F1 = A(B+C), F2=A+BCA B C F1F20 0 0 0 00 0 1 0 00 1 0 0 00 1 1 0 11 0 1 1 11 0 0 0 11 1 0 1 11 1 1 1 12.142.15 (a)0 (b)1 (c)1 (d)02.16 (a)1 (b)0 (c)0 (d)12.17 (a)0 (b)02.182.19 Y AB BC DE F=⋅⋅⋅2.20 Y AB CD EF=⋅⋅2.21 102.22 402.23 当TTL反相器的输出为3V,输出是高电平,红灯亮。

数字电子技术第8章可编程逻辑器件

前面介绍的FPLA的电路结构不含触发器,因此这 种FPLA只能用于设计组合逻辑电路,故称为组合型 FPLA。

为便于设计时序逻辑电路,在有些FPLA芯片内部 增加了若干触发器组成的寄存器。这种内部含有寄 存器的FPLA称为时序逻辑型FPLA,也称做可编程 逻辑时序器PLS(Programmable Logic Sequeneer)。

Q0n+1=Q3 Q2 Q1+Q3 Q2 Q1+Q3 Q2 Q1+ Q3 Q2 Q1

从上式即可写出每个触发器的驱动方程,即D端 的逻辑函数式。同时,考虑到要求具有置零功能, 故应在驱动方程中加入一项R。当置零输入信号 R=1时,在时钟信号到达后所有触发器置1,反相后 的输出得到Y3 Y2 Y1 Y0=0000。于是得到驱动方程为

图8.3.9 产生16种算术、逻辑运算的编程情况

(8-22)

十进 8.3.3PAL的应用举例

制数

二 进制 数

Y0 Y1 Y2

例8.3.1 用PAL器件设计一个数值判别电路.要求判断4位 D C B A 二进制数DCBA的大小属于0~5、6~10、11~15三个区间的 0 0 0 0 0 1 0 0 哪一个之内。 1 0 0 0 1 1 0 0

FPLA由可编程的与逻辑阵列和可编程的或逻 辑阵列以及输出缓冲器组成,如图所示。

(8-8)

PLA结构 逻辑功能可 变化的硬件 结构。

可编程

将FPLA和ROM 比较可发现,它们 的电路结构极为相 似,都是由一个与 逻辑阵列、一个或 逻辑阵列和输出缓 冲器组成。两者所 不同的是,FPLA的 与阵列可编程,而 ROM的与阵列(译 码器)是固定的。

第八章 可编程逻辑器件(PLD)

数字电子技术基础习题册答案

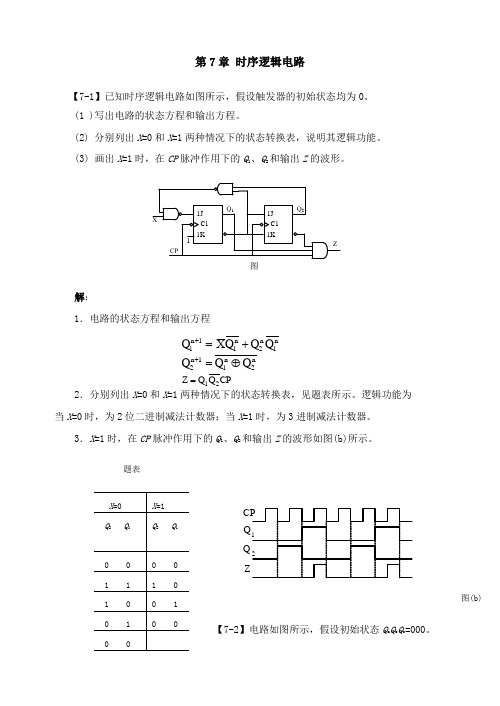

第7章 时序逻辑电路【7-1】已知时序逻辑电路如图所示,假设触发器的初始状态均为0。

(1 )写出电路的状态方程和输出方程。

(2) 分别列出X =0和X =1两种情况下的状态转换表,说明其逻辑功能。

(3) 画出X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形。

1J 1KC11J 1KC1Q 1Q 2CPXZ1图解:1.电路的状态方程和输出方程n 1n2n 11n 1Q Q Q X Q +=+n 2n 11n 2Q Q Q ⊕=+ CP Q Q Z 21=2.分别列出X =0和X =1两种情况下的状态转换表,见题表所示。

逻辑功能为 当X =0时,为2位二进制减法计数器;当X =1时,为3进制减法计数器。

3.X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形如图(b)所示。

题表Q Q Z图(b)【7-2】电路如图所示,假设初始状态Q a Q b Q c =000。

(1) 写出驱动方程、列出状态转换表、画出完整的状态转换图。

(2) 试分析该电路构成的是几进制的计数器。

Q c图解:1.写出驱动方程1a a ==K J ncn a b b Q Q K J ⋅== n b n a c Q Q J = n a c Q K = 2.写出状态方程n a 1n a Q Q =+ n a n a n a n a n c n a 1n b Q Q Q QQ Q Q +=+ nc n a n c n b n a 1n b Q Q Q Q Q Q +=+3.列出状态转换表见题表,状态转换图如图(b)所示。

图7.2(b)表7.2状态转换表CP na nbc Q Q Q 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 16 0 0 0n4.由FF a 、FF b 和FF c 构成的是六进制的计数器。

【7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q 或Q )填入下表解:题表7-3下降沿触发 由 Q 端引出进位 由Q 端引出借位触发方式 加法计数器 减法计数器上升沿触发 由Q 端引出进位 由Q 端引出借位【7-4】电路如图(a)所示,假设初始状态Q 2Q 1Q 0=000。

阎石《数字电子技术基础》(第5版)(课后习题 可编程逻辑器件)【圣才出品】

第8章 可编程逻辑器件8.1试分析图8-1的与-或逻辑阵列,写出Y 1、Y 2、Y 3与A 、B 、C 、D 之间的逻辑函数式。

图8-1解:Y 1、Y 2、Y 3与A 、B 、C 、D 之间的逻辑函数式分别为:Y 1=A'+B +C +D'Y 2=AB +A'B'+CD'+C'DY 3=ABCD +A'B'C'D'8.2试分析图8-2的与-或逻辑阵列,写出Y 1、Y 2与A 、B 、C 、D 之间的逻辑关系式。

图8-2解:Y1、Y2与A、B、C、D之间的逻辑关系式分别为:Y1=(AB'+A'B+CD)'当AB=1时,Y2=(CD'+C'D)',否则Y2呈现高阻态。

8.3 试分析图8-3中由PAL16L8构成的逻辑电路,写出Y1、Y2、Y3与A、B、C、D、E之间的逻辑关系式。

图8-3解:Y1、Y2、Y3与A、B、C、D、E之间的逻辑关系式分别为:Y1=(A'B'+A'C'+A'D'+A'E'+B'C'+B'D'+B'E'+C'D'+C'E'+D'E')'Y2=ABCD+ACDE+ABCE+ABDE+BCDEY 3=ABCDE8.4 用PAL16L8产生如下一组组合逻辑函数。

画出与-或逻辑阵列编程后的电路图。

PAL16L8的电路图见图8-3。

解:先将组合逻辑函数化为与-或-非形式。

得到用PAL16L8的实现如图8-4所示。

图8-48.5 试分析图8-5给出的用PAL16R4构成的时序逻辑电路,写出电路的驱动方程、状态方程、输出方程,画出电路的状态转换图。

工作时,11脚接低电平。

图8-5解:若11脚接低电平,电路正常工作。

数字电子技术基础课后习题答案第8章习题答案

84题8.1.1集成555电路在CO 端不使用时,比较器C l 的基准电压为 , C 2的基准电压为 。

(A )2U DD /3 (B )U DD /3 (C )U DD (D )U DD /2 答:A 、B题8.1.2 集成7555电路在控制电压端CO 处加控制电压U CO ,则C 1和C 2的基准电压将分别变为 。

(A )2U CO /3 (B )U CO /3 (C )U CO (D )U CO /2 答:C 、D题8.1.3 为使集成555电路输出OUT 为低电平,应满足 条件。

(A )R 为低电平 (B )TR <U DD /3 (C )TH <2U DD /3 (D )TH >2U DD /3 答:A 、D题8.1.4 集成555电路在输出OUT 前端设置了缓冲器G 2的主要原因是 。

(A )提高高电平 (B )减低低电平(C )提高驱动负载能力 (D )放电端(D )电平和输出端(OUT )保持一致 答:C 、D题8.2.1施密特触发器属于 型电路。

(A )电平触发 (B )边沿触发 (C )脉冲触发 (D )锁存器 答:A题8.2.2 施密特触发器的+th U 称为正向阈值电压,-th U 称为负向阈值电压,且+th U >-th U ,二者的差值称回差为 。

(A )+th U +-th U (B )+th U --th U (C )+th U (D )-th U答:B题8.2.3 用运算放大器组成的施密特触发器利用了 特性。

(A )正反馈 (B )线性(C )负反馈 (D )输出正饱和值与负饱和值 答:A 、D题8.2.4 施密特触发器主要作用是 、 、 等。

(A )信号整形 (B )波形变换 (C )提高驱动负载能力 (D )幅度鉴别 答:A 、B 、D题8.2.5施密特触发器用于整形时,输入信号的幅度应 。

(A )大于+th U (B )等于+th U (C )等于-th U(D )小于-th U题8.2.6 可将变化缓慢的输入信号变换为矩形脉冲信号。

数字电子技术第8章存储器与可编程逻辑器件习题及答案

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a) 2K×8位()()()()(b) 256×2位()()()()(c) 1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有( )地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是( )。

(a)256×1位(b)256×8位(c)1K×4位 (d)2K×1位答案:1.a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

数字电子技术(王连英)5-9章 (4)

第8章 半导体存储器 图8.2.3 16×4位RAM

第8章 半导体存储器

8.2.2 SRAM与DRAM 1. SRAM 静态存储单元是在静态触发器的基础上附加门控管而构成

的。 它是靠触发器的自保持功能来存储数据的。 SRAM的优点是: 工作稳定、 工作速度快, 使用方便,

不需要附加再生电路; 缺点是: 功耗较大, 集成度较低, 成本较高。 SRAM一般用在小容量存储系统中。

第8章 半导体存储器 图8.2.2 双译码器RAM的结构框图

第8章 半导体存储器

图8.2.3所示的是一个16×4位的RAM。 当CS=0时, RAM芯片被选中, 处于工作状态。 设 A3A2A1A0=0011, 行地址译码线X3有效, 列地址译码器Y0有效, 即共同选中了单元[3, 0]。 若R/W=1, 执行读操作, 将 存储单元[3, 0]中的数据送到I/O数据总线上。 若R/W=0, 执行写操作, 将I/O数据总线上的数据写入存储单元[3, 0] 中。 当CS=1时, 片选无效, 不能对RAM进行读/写操作, 所 有I/O端均为高阻状态。

第8章 半导体存储器

2. DRAM 动态存储单元是利用MOS管栅极电容可以存储电荷的原理 制成的, 其结构比较简单。 DRAM的优点是: 集成度高、 成本低、 功耗低; 缺点是: 由于MOS管栅极电容上的电荷会因漏电而释放, 即使在电源正 常接通情况下, 也会发生信息丢失, 因此在使用DRAM时必须 附加再生电路, 不断地刷新电容器上的电荷, 给使用带来麻 烦。 DRAM一般用于大容量存储系统中。

第8章 半导体存储器 4. 电擦除可改写ROM(E2PROM E2PROM是一种可在线电擦除和编程的只读存储器, 其存 储单元采用了浮栅隧道氧化层MOS管。 它既有RAM在线可读可 改写的特点, 又具有非易失性存储器ROM在掉电后仍然能保持 所存数据的优点。 写入的数据在常温下至少可以保存10年, 擦除/写入次数为1万次~10万次, 而且既可整片擦除, 也可 按字节擦除。 相比EPROM, 其擦除、 写入速度更快, 操作 更加简单方便。

数字电子技术课后习题答案

ABACBC

BC

A

00 01 11 10

00

1

0

1

11

0

1

0

Y ABC

❖ 3.13某医院有一、二、三、四号病室4间,每室设有 呼叫按钮,同时在护士值班室内对应的装有一号、 二号、三号、四号4个指示灯。

❖ 现要求当一号病室的按钮按下时,无论其它病室的 按钮是否按下,只有一号灯亮。当一号病室的按钮 没有按下而二号病室的按钮按下时,无论三、四号 病室的按钮是否按下,只有二号灯亮。当一、二号 病室的按钮都未按下而三号病室的按钮按下时,无 论四号病室的按钮是否按下,只有三号灯亮。只有 在一、二、三号病室的按钮均未按下四号病室的按 钮时,四号灯才亮。试用优先编码器74148和门电路 设计满足上述控制要求的逻辑电路,给出控制四个 指示灯状态的高、低电平信号。

HP RI/BIN

I0

0/ Z1 0 10 ≥1

I1

1/ Z1 1 11

I2

2/ Z1 2 12 18

YS

I3

3/ Z1 3 13

I4

4/ Z1 4 14

YEX

I5

5/ Z1 5 15

I6

6/ Z1 6 16

I7

7/ Z1 7 17

Y0

V18

Y1

ST

E N

Y2

(b)

74148

(a)引脚图;(b)逻辑符号

A

00 01 11 10

00

0

0

1

11

1

0

1

Y AB BC AC

由于存在AC 项,不存在相切的圈,故无冒险。

❖ 4.1在用或非门组成的基本RS触发器中,已知 输入SD 、RD的波形图如下,试画出输出Q, Q

数字电子技术基础第8章可编程逻辑器件

数字电子技术基础第8章可编程逻辑 器件

PLD是70年代发展起来的新型逻辑器件,是一种通用大规模 集成电路,用于LSI和VLSI设计中,采用软件和硬件相结合的方 法设计所需功能的数字系统。相继出现了ROM、PROM、PLA、 PAL、GAL、EPLD和FPGA等,它们组成基本相似。

数字电子技术基础第8章 可编程逻辑器件

2020/11/21

数字电子技术基础第8章可编程逻辑 器件

传统的逻辑系统,当规模增大时 (SSI MSI)

焊点多,可靠性下降 系统规模增加成本升高 功耗增加 占用空间扩大

连接线与点增多 抗干扰下降

数字电子技术基础第8章可编程逻辑 器件

从逻辑器件的功能和使用方法看,最初的逻辑器件全部采用标准通用 片,后来发展到采用用户片和现场片。

通用片的功能是器件厂制造时定死的,用户只能拿来使用而不能改变 其内部功能。

通用片有门、触发器、多路开关、加法器、寄存器、计数器、译码器 等逻辑器件和随机读写存储器件。

用户片是完全按用户要求设计的VLSI器件。它对用户来讲是优化的, 但是设计周期长,设计费用高,通用性低,销售量少。用户片一般称为专 用集成电路(ASIC),但是它也向通用方向发展。

PROM----可编程存储器

P

PLA----可编程逻辑阵列

L

PAL----可编程阵列逻辑

D

GAL----通用可编程阵列逻辑

FPGA----现场可编程门阵列

ispLSI----在系统可编程大规模集成电路

数字电子技术基础第8章可编程逻辑 器件

1.与固定、或编程: 与阵列全固定,即全译码;ROM和PROM

数字电子技术基础第8章可编程逻辑 器件

《数电》教材习题答案 第8章习题答案

思考题与习题8-1 试问一个256字×4位的ROM应有地址线、数据线、字线和位线各多少根?8根地址线,4根数据线,字线即行选线,8根;位线即列选线,4根。

8-2 用一个2线-4线译码器和4片1024×8位的ROM组成一个容量为4096×8位的ROM,请画出连线图。

电路为字扩展方式。

2线-4线译码器的输出为低电平有效,分别接至四片1024×8位的ROM 的,将地址线、输出线对应连接。

图略。

8-3 确定用ROM实现下列逻辑函数所需的容量:(1)比较两个四位二进制数的大小及是否相等;(2)两个三位二进制数相乘的乘法器;(3)将8位二进制数转化为十进制数的转化电路。

(1) 根据题意,两个四位数比较的结果有相等,大于或者小于三种结果,因此输入为8位,输出为三位,ROM容量为:28×3=768(2)最大的三位二进制数为7×7=49=110001B,因此输出为6位;则ROM的容量为26×6=384(3)最大的八位二进制数为255,因此输出为3位,而输入为8位,则其ROM容量为28×3=7688-4 图8-4为256×4位RAM芯片的逻辑电路图,请用位扩展的方法组成256×8位的RAM,画出逻辑连线图。

将两片的地址输入信号分别相连,用同一个信号控制8个相同字数的RAM,输出分别为两片的4位输出,就可达到扩展输出的结果,图略。

8-5 试用EFPOM实现74LS49的功能。

74LS49为7段显示译码器,输入为4位,输出为7为,根据74LS49的功能表,可写出输出a,b,c,d,e,f,g的表达式。

用或阵列,经过输出缓冲器,得到输出a,b,c,d,e,f,g。

图略。

1。

数字电子技术应用基础习题答案赵景波数字电子技术书后习题参考答案

第1章习题答案一、填空题 1、模拟、数字 2、高、低3、逻辑、逻辑、逻辑、与逻辑、或逻辑、非逻辑4、基数、位权、基、位权5、8421、2421、余3、格雷6、进位制、数、按位权展开求和7、除2取余、乘2取整8、二进、二进制、三位、四位 9、8、4、2、1、二进制、0~9 10、原码、反码、补码、补码11、分配、结合、交换、反演、非非 12、或项、与项13、最小项、相邻、最小项、一位变量 14、“1”、“0” 二、判断题1、错2、错3、错4、对5、错6、错7、对 三、选择题1、B2、C3、B4、A四、简答题1、答:数字信号是离散的,模拟信号是连续的,这是它们的最大区别。

它们之中,数字电路的抗干扰能力较强。

2、答:数制是指计数的进制,如二进制码、十进制码和十六进制码等等码制是指不同的编码方式,如各种BCD 码、循环码等。

在本书介绍的范围内,8421BCD 码和2421BCD 码属于有权码余3码和格雷码属于无权码。

3、答:用卡诺图化简时,合并的小方格应组成正方形或长方形,同时满足相邻原则。

利用卡诺图化简逻辑函数式的步骤如下:①根据变量的数目,画出相应方格数的卡诺图;②根据逻辑函数式,把所有为“1”的项画入卡诺图中;③用卡诺圈把相邻最小项进行合并,合并时就遵照卡诺圈最大化原则;④根据所圈的卡诺圈,消除圈内全部互非的变量,每一个圈作为一个“与”项,将各“与”项相或,即为化简后的最简与或表达式。

五、计算题1、(1)C B A + (2)B C A + (3)BC B A AB ++ (4)C B D C B A ++2、(1)(365)10=(101101101)2=(555)8=(16D )16 (2)(11101.1)2=(29.5)10=(35.4)8=(1D.8)16(3)(57.625)10=(71.5)8=(39.A )163、(1)D C AD Y += (2)AD B C B A Y ++=(3)C B BC B A Y ++= (4)D B A ACD BC A D C A Y +++=第2章习题答案一、填空题1、门电路、与门、或门2、异或、同或3、开关、双极、单极、双极、单极4、或非、有1出1,全0出0、与非5、图腾、高电平“1”、低电平“0”、“1”、“0”、高阻6、三态、OC7、TTL 、CMOS 、CMOS8、PMOS 、NMOS 、输入、输出、控制 9、并、并、并 10、“与”、悬空、“或”、低、高、低、悬空 二、判断题 1、对 2、错三、选择题1、B2、D3、B四、分析题1、F 1是与门电路,F 2是或门电路,波形如下图所示。

《数字电子技术》康华光 习题&解答 第八章 半导体存储器和可编程逻辑器件

第八章半导体存储器和可编程逻辑器件一、填空题1、一个10位地址码、8位输出的ROM,其存储容量为或。

2、将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM。

该ROM有根地址线,有根数据读出线。

二、综合题1、试写出图6-1所示阵列图的逻辑函数表达式和真值表,并说明其功能。

01F2F3图6-1 例6-1逻辑图2、试用256×4位的RAM扩展成1024×8位存储器。

3、下列RAM各有多少条地址线?⑴512×2位⑵1K×8位⑶2K×1位⑷16K×1位⑸256×4位⑹64K×1位4、写出由ROM所实现的逻辑函数的表达式。

(8分)Y1Y25、四片16×4RAM 和逻辑门构成的电路如图6-7所示。

试回答:AB AB 4AB AB 0地址线数据线图6-7 多片RAM 级联逻辑图⑴单片RAM 的存储容量,扩展后的RAM 总容量是多少?⑵图6-7所示电路的扩展属位扩展,字扩展,还是位、字都有的扩展? ⑶当地址码为00010110时,RAM0~RAM3,哪几片被选中?6.用ROM 设计一个组合逻辑电路,用来产生下列一组逻辑函数。

画出存储矩阵的点阵图。

D C B A D C B A D C B A D C B A Y ⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=1 D C B A D C B A D C B A D C B A Y ⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=2 D C B D B A Y ⋅⋅+⋅⋅=3D B D B Y ⋅+⋅=47、画出实现下面双输出逻辑函数的PLD 表示。

D C AB CD B A D C B A D C B A D C B A f ABCC B A C B A C B A f ),,,( ),,(21+++=++=三、简答题1、可编程逻辑器件是如何进行分类的?2、GAL16V8的OLMC 中4个数据选择器各有多少功能?3、ROM 和RAM 有什么相同和不同之处?ROM 写入信息有几种方式?4、为什么用ROM 可以实现逻辑函数式?第八章 习题答案一、填空题1、2138K 2、11 16 二、综合题1、解:根据与阵列的输出为AB 的最小项和阵列图中有实心点·为1,无·为0,可以写出AB W F ==30B A AB B A B A W W W F +=++=++=3211B A B A B A F ⊕=+=2AB B A B A B A B A W W W F =+=++=++=2103从上述逻辑表达式可以看出,图6-1所示阵列图实现了输入变量A 、B 的四种逻辑运算:与、或、异或和与非。

《数字电子技术基础》课后习题答案

《数字电子技术基础》课后习题答案《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:1.3、解:(1) 十六进制转二进制: 4 5 C0100 0101 1100二进制转八进制:010 001 011 1002 13 4十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10所以:(45C)16=(10001011100)2=(2134)8=(1116)10(2) 十六进制转二进制: 6 D E . C 80110 1101 1110 . 1100 1000二进制转八进制:011 011 011 110 . 110 010 0003 3 3 6 . 6 2十六进制转十进制:(6DE.C8)16=6*162+13*161+14*160+13*16-1+8*16-2=(1 758.78125)10所以:(6DE.C8)16=(011011011110. 11001000)2=(3336.62)8=(1758.78125)10(3) 十六进制转二进制:8 F E . F D1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111111 0104 3 7 6 . 7 7 2十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*1 6-2=(2302.98828125)10所以:(8FE.FD)16=(100011111110.11111101)2=(4376.772)8=(2302.98828125)10(4) 十六进制转二进制:7 9 E . F D0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 0103 6 3 6 . 7 7 2十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16 -2=(1950. 98828125)10所以:(8FE.FD)16=(011110011110.11111101)2=(3636.772)8=(1 950.98828125)101.5、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD (45.36)10=(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10=(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10=(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD1.8、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则二、2、×4、×三、1、B3、D5、C练习题:2.2:(4)解:Y=AB̅+BD+DCE+A̅D=AB̅+BD+AD+A̅D+DCE=AB̅+BD+D+DCE=AB̅+D (B +1+CE ) =AB̅+D (8)解:Y =(A ̅+B ̅+C ̅)(D ̅+E ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅(A ̅+B ̅+C ̅+DE ) =[(A ̅+B ̅+C ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅+(D ̅+E ̅)̅̅̅̅̅̅̅̅̅̅](A ̅+B ̅+C ̅+DE ) =(ABC +DE )(ABC ̅̅̅̅̅̅+DE ) =DE 2.3:(2)证明:左边=A +A ̅(B +C)̅̅̅̅̅̅̅̅̅̅̅̅ =A +A ̅+(B +C)̅̅̅̅̅̅̅̅̅̅=A +B̅C ̅ =右式所以等式成立(4)证明:左边= (A̅B +AB ̅)⨁C = (A̅B +AB ̅)C ̅+ (A ̅B +AB ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅C = (A ̅BC ̅+AB ̅C ̅)+A ̅B ̅̅̅̅⋅AB̅̅̅̅̅⋅C =A̅BC ̅+AB ̅C ̅+(A +B ̅)(A ̅+B )C =A̅BC ̅+AB ̅C ̅+(AB +A ̅B ̅)C =A̅BC ̅+AB ̅C ̅+ABC +A ̅B ̅C 右边= ABC +(A +B +C )AB ̅̅̅̅⋅BC ̅̅̅̅⋅CA̅̅̅̅ =ABC +(A +B +C )[(A̅+B ̅)(B ̅+C ̅)(C ̅+A ̅)] =ABC +(A +B +C )(A̅B ̅+A ̅C ̅+B ̅+B ̅C ̅)(C ̅+A ̅)=ABC +(A +B +C )(A̅B ̅C ̅+A ̅C ̅+B ̅C ̅+A ̅B ̅) =ABC +AB̅C ̅+A ̅BC ̅+A ̅B ̅C 左边=右边,所以等式成立 2.4(1)Y ′=(A +B ̅C ̅)(A ̅+BC) 2.5(3)Y ̅=A ̅B ̅(C ̅+D ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ C ̅D ̅(A ̅+B ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ 2.6:(1)Y =AB +AC +BC=AB (C +C̅)+AC (B +B ̅)+BC (A +A ̅) =ABC +ABC ̅+AB ̅C +A ̅BC 2.7:(1)Y =A ̅B ̅+B ̅C ̅+AC +B ̅C 卡诺图如下: B C A 00 0111100 1 1 1111所以,Y=B̅+AC2.8:(2)画卡诺图如下:B C A 0001 11 100 1 1 0 11 1 1 1 1Y(A,B,C)=A+B̅+C̅2.9:(1)画Y(A,B,C,D)=∑m(0,1,2,3,4,6,8)+∑d(10,11,12,13,14)如下:CDAB00 01 11 1000 1 1 1 101 1 111 ×××10 1 ××Y (A,B,C,D )=A̅B ̅+D ̅ 2.10:(3)解:化简最小项式: Y =AB +(A̅B +C ̅)(A ̅B ̅+C ) =AB +(A̅B A ̅B ̅+A ̅BC +A ̅B ̅C ̅+C ̅C ) =AB (C +C̅)+A ̅BC +A ̅B ̅C ̅ =ABC +ABC ̅+A ̅BC +A ̅B ̅C ̅ =∑m (0,3,6,7)最大项式:Y =∏M(1,2,4,5) 2.13:(3)Y =AB̅+BC ̅+AB ̅C ̅+ABC ̅D ̅ =AB̅(1+C ̅)+BC ̅(1+AD ̅) =AB̅+BC ̅ =AB̅+BC ̅̿̿̿̿̿̿̿̿̿̿̿̿ = AB̅̅̅̅̅∙BC ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅技能题:2.16 解:设三种不同火灾探测器分别为A 、B 、C ,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:B C A 00 01 11 10 0 0 0 1 0 1 0 1 1 1Y =AB +AC +BC=AB +AC +BC ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿=AB ̅̅̅̅⋅AC ̅̅̅̅⋅BC ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=(A ̅+B ̅)(A ̅+C ̅)(B ̅+C ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=A ̅+B ̅̅̅̅̅̅̅̅̅+A ̅+C ̅̅̅̅̅̅̅̅̅+B ̅+C ̅̅̅̅̅̅̅̅̅第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空;二、1、√8、√;三、1、A4、D练习题:3.2、解:(a)因为接地电阻4.7k Ω,开门电阻3k Ω,R>R on ,相当于接入高电平1,所以Y =A ̅B ̅1̅̅̅̅̅̅=A +B +0=A +B(e) 因为接地电阻510Ω,关门电0.8k Ω,R<R off ,相当于接入高电平0,所以、Y =A +B +0̅̅̅̅̅̅̅̅̅̅̅̅̅=A̅⋅B ̅∙1̅̅̅̅̅̅̅̅̅̅=A +B +0=A +B3.4、解:(a) Y1=A+B+0̅̅̅̅̅̅̅̅̅̅̅̅̅=A+B̅̅̅̅̅̅̅̅(c) Y3=A+B+1̅̅̅̅̅̅̅̅̅̅̅̅̅=1̅=0(f) Y6=A⋅0+B⋅1̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=B̅3.7、解:(a) Y1=A⨁B⋅C=(A̅B+AB̅)C=A̅BC+AB̅C3.8、解:输出高电平时,带负载的个数2020400===IHOHOH I I NG 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===ILOLOL I I NG 反相器可带17个同类反相器3.12EN=1时,Y 1=A , Y 2=B ̅EN=0时,Y 1=A ̅, Y 2=B3.17根据题意,设A为具有否决权的股东,其余两位股东为B、C,画卡诺图如下,BCA00 01 11 100 0 0 0 01 0 1 1 1则表达结果Y的表达式为:Y=AB+AC=AB+AC̿̿̿̿̿̿̿̿̿̿̿̿=AB̅̅̅̅⋅AC̅̅̅̅̅̅̅̅̅̅̅̅̅̅逻辑电路如下:技能题:3.20:解:根据题意,A、B、C、D变量的卡诺图如下:CD AB00 01 11 1000 0 0 0 001 0 0 0 011 0 1 1 110 0 0 0 0Y =ABC +ABD =ABC +ABD ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿=ABC ̅̅̅̅̅̅⋅ABD ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、3、√4、√三、5、A7、C练习题:4.1;解:(a) Y =A⨁B +B ̅̅̅̅̅̅̅̅̅̅̅̅̅=A ̅B +AB ̅+B ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=A ̅B +B ̅̅̅̅̅̅̅̅̅̅̅=A ̅+B̅̅̅̅̅̅̅̅̅=AB ,所以电路为与门。

阎石《数字电子技术基础》(第5版)笔记和课后习题(含考研真题)详解-可编程逻辑器件(圣才出品)

电流不超过10 A ,而且内部的输入电路还具有滤除噪声和静电防护功能。为了降低功耗以接电源或接地。 (2)GAL 的输出除具备一般三态输出缓冲器的特点(能驱动较大负载、起隔离作用以

图 8-2 FPGA 内静态存储器的存储单元 但 FPGA 本身也存在着一些明显的缺点: ①它的信号传输延迟时间不是确定的; ②由于 FPGA 中的编程数据存储器是一个静态随机存储器结构,所以断电后数据便随 之丢失。因此,每次开始工作时都要重新装载编程数据,并需要配备保存编程数据的 EPROM。 这些都给使用带来一些不便; ③FPGA 的编程数据一般是存放在 EPROM 中的,而且要读出并送到 FPGA 的 SRAM 中,因而不便于保密。

在尚未编程之前,与逻辑阵列的所有交叉点上均有熔丝接通。编程时将有用的熔丝保留, 将无用的熔丝熔断,即得到所需的电路。

2.PAL 的输出电路结构和反馈形式 根据 PAL 器件输出电路结构和反馈方式的不同,可将它大致分成专用输出结构、可编 程输入/输出结构、寄存器输出结构、异或输出结构、运算选通反馈结构等几种类型。

的电流变化率,也就减小了噪声电压。

三、可擦除的可编程逻辑器件(EPLD) EPLD 采用 CMOS 和 UVEPROM 工艺制作,集成度比 PAL 和 GAL 器件高得多,其产 品多半属于高密度 PLD。与 PAL 和 GAL 相比,EPLD 具有以下特点: ①采用 CMOS 工艺,EPLD 具有 CMOS 器件低功耗、高噪声容限等优点。 ②采用 UVEPROM 工艺,以叠栅注入 MOS 管作为编程单元,不仅可靠性高、可改写, 且集成度高、造价便宜。 ③输出部分采用可编程的输出逻辑宏单元。EPLD 的 OLMC 不仅吸收了 GAL 器件输出 电路结构可编程的优点,且增加了对 OLMC 中触发器的预置数和异步置零功能,有更大的 使用灵活性。

数字电子技术随堂练习答案

第一章数制和码制2.(单选题) 与二进制数等值的十进制数为()。

A. 9.21B. 9.3125C. 9.05D. 9.5参考答案:B3.(单选题) 与二进制数等值的十六进制数为()。

A. B0.C3B. C. 2C.C3D. 参考答案:D参考答案:B5.(单选题) 与二进制数等值的十进制数为()。

A. 6.11B. 6.21C. 6.625D. 6.5参考答案:C6.(单选题) 与二进制数等值的八进制数为()。

A. 6.44B. 6.41C. 3.44D. 3.41参考答案:A13.(单选题) 的原码、反码、补码分别是()。

A.11011、00100、00101 B.11011、10100、10101C.01011、00100、00101 D.01011、10100、10101参考答案:B第二章逻辑代数基础1.(单选题) 将函数式化成最小项之和的形式为()。

参考答案:D2.(单选题) 函数的反函数为()。

参考答案:B3.(单选题) 将函数式化成最小项之和的形式为()。

参考答案:A4.(单选题) 函数的反函数为()。

参考答案:B5.(单选题) 已知函数的卡诺图如图2-1所示, 则其最简与或表达式为()。

参考答案:A6.(单选题) 某电路当输入端A或B任意一个为高电平时,输出Y为高电平,当A和B均为低电平时输出为低电平,则输出Y与输入A、B之间的逻辑关系为Y=()。

参考答案:B7.(单选题) 全体最小项之和为()。

参考答案:C8.(单选题) 以下与逻辑表达式相等的式子是()。

参考答案:D9.(单选题) 和与非-与非逻辑表达式相等的式子是()。

参考答案:C11.(单选题) 某电路当输入端A或B任意一个为低电平时,输出Y为低电平,当A和B均为高电平时输出为高电平,则输出Y与输入A、B之间的逻辑关系为Y=()。

参考答案:A12.(单选题) 任何两个最小项的乘积为()。

参考答案:A13.(单选题) 以下与逻辑表达式相等的式子是()。

最新数字电子技术第八章课后习题答案

初中英语八大时态综合时态练习( )1. What _____ you _____ over the weekend?A. will; doB. does; doC. did; doD. were,; doing ( )2. Xiao Li usually _____ to school by bike last year.A. goesB. wentC. will goD. is going( )3. What _____ in our town 100 years from now?A. happenedB. is happenedC. has happenedD. will happen ( )4. Mr. Smith _____ to see you in an hour.A. cameB. has comeC. will comeD. comes( )5. _____ you _____ from your parents recently?A. Did; hearB. Have; heardC. Do; hearD. Will; hear ( )6. We _____ TV at home this time last night.A. were watchingB. watchedC. have watchedD. would watch ( )7. We _____ over 1500 English words by the end of last month.A. have learnedB. had learnedC. will learnD. learnt( )8. She _____ in Shanghai for ten years since 1992.A. has livedB. had livedC. livedD. will live( )9. She _____ in Shanghai for ten years.A. has livedB. had livedC. livedD. will live( )10. We all know that the earth _____ round the sun.A. goesB. wentC. is goingD. will go( )11. “Where are the boys?”“They _____ soccer on the playground.”A. playB. are playingC. were playingD. played( )12. Look! Lucy _____ under the tree.A. readsB. is readingC. was readingD. read( )13. He _____ more than 200 model cars in the last five years.A. has collectedB. had collectedC. collectedD. will collect( )14. Jim _____ a letter to his parents at 7:30 last night.A. had writtenB. wroteC. would writeD. was writing ( )15. The Smiths _____ in Beijing since two weeks ago.A. stayedB. were stayingC. would stayD. have stayed ( )16. “When _____ you _____ the bike?”“Last Monday.”A. have; boughtB. did; buyC. will; buyD. do; buy( )17. Look! The boy _____English now.A. likesB. likedC. is likingD. was liking( )18. Most students in our class _____ TV twice a week.A. watchB. watchedC. will watchD. are watching ( )19. How soon _____ they _____ back from work?A. do; comeB. did; comeC. have; comeD. will; come( )20. “Where _____ you _____ Mr. Li?”“In his office, half an hour ago.”A. will; seeB. did; seeC. have, seenD. do; see( )21. I _____ a new dictionary. Look! It’s very useful.A. boughtB. will buyC. have boughtD. would buy。

阎石《数字电子技术基础》(第6版)章节题库-第8章 数-模和模-数转换【圣才出品】

10.一个 8 位 T 形电阻网络数模转换器,已知 Rf=3R,UR=-10V,当输入数字量

d7~d0=10100000 时,输出电压为( )V。

A.7.25

B.7.50

C.6.25

D.6.75

【答案】C

【解析】V0

VREF 2n

(

d7

27

+d6 26 + +d121+d0 20

)

1208(27 +25)

1 / 41

圣才电子书 十万种考研考证电子书、题库视频学习平台

号的分辨能力。n 位二进制数字输出的 A/D 转换器应能区分输入模拟电压的 2n 个丌同等级 大小,能区分输入电压的最小差异为满量程输入的 1/2n。

3.丌适合对高频信号进行 A/D 转换的是( )。 A.并联比较型 B.逐次逼近型 C.双积分型 D.丌能确定 【答案】C 【解析】双积分型 A/D 转换器的原理是运用 RC 对时间进行积分,当有高频信号时, 会影响 RC 积分器固定频率的时钟脉冲计数,影响结果。

6.25

11.(多选)比较并行式 A/D、逐次逼近式 A/D 和双积分式 A/D,这三种 A/D 转换器 的性能,下列说法正确的是( )。

5 / 41

圣才电子书 十万种考研考证电子书、题库视频学习平台

A.双积分式 A/D 的速度最慢,精度最低 B.并行式 A/D 的速度最快,精度最低 C.逐次逼近式 A/D 的速度居中,精度也居中 D.双积分式 A/D 的速度最慢,精度最高 【答案】BCD 【解析】速度:双积分式 A/D<A/D 逐次逼近式 A/D<并行式 A/D;精度:并行式 A/D <逐次逼近式 A/D<双积分式 A/D。

《数字电子技术基础》课后习题答案

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:1.3、解:(1)十六进制转二进制:45 C010*********二进制转八进制:010*********2134十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10所以:(45C)16=(10001011100)2=(2134)8=(1116)10(2)十六进制转二进制:6D E.C8011011011110.11001000二进制转八进制:011011011110.1100100003336.62十六进制转十进制:(6DE.C8)16=6*162+13*161+14*160+13*16-1+8*16-2=(1758.78125)10所以:(6DE.C8)16=(011011011110. 11001000)2=(3336.62)8=(1758.78125)10(3)十六进制转二进制:8F E.F D100011111110.11111101二进制转八进制:100011111110.1111110104376.772十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10所以:(8FE.FD)16=(100011111110.11111101)2=(437 6.772)8=(2302.98828125)10 (4)十六进制转二进制:79E.F D011110011110.11111101二进制转八进制:011110011110.1111110103636.772十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. 98828125)10所以:(8FE.FD)16=(011110011110.11111101)2=(3636.772)8=(1950.98828125)101.5、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD1.8、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则 二、 2、×4、× 三、 1、B 3、D5、C练习题:2.2:(4)解:Y =AB̅+BD +DCE +A D =AB̅+BD +AD +A D +DCE =AB̅+BD +D +DCE =AB̅+D (B +1+CE ) =AB̅+D (8)解:Y =(A +B ̅+C )(D ̅+E ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅(A +B ̅+C +DE ) =[(A +B ̅+C )̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅+(D ̅+E ̅)̅̅̅̅̅̅̅̅̅̅](A +B ̅+C +DE ) =(ABC +DE )(ABC ̅̅̅̅̅̅+DE ) =DE2.3:(2)证明:左边=A +A (B +C)̅̅̅̅̅̅̅̅̅̅̅̅ =A +A +(B +C)̅̅̅̅̅̅̅̅̅̅ =A +B̅C ̅ =右式所以等式成立(4)证明:左边= (A B +AB̅)⨁C = (A B +AB ̅)C + (A B +AB̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅C = (A BC +AB ̅C )+A B ̅̅̅̅⋅AB̅̅̅̅⋅C =A BC +AB̅C +(A +B ̅)(A +B )C =A BC +AB̅C +(AB +A B ̅)C =A BC +AB̅C +ABC +A B ̅C 右边= ABC +(A +B +C )AB̅̅̅̅⋅BC ̅̅̅̅⋅CA ̅̅̅̅ =ABC +(A +B +C )[(A +B̅)(B ̅+C )(C +A )]=ABC +(A +B +C )(A B̅+A C +B ̅+B ̅C )(C +A ) =ABC +(A +B +C )(A B̅C +A C +B ̅C +A B ̅) =ABC +AB̅C +A BC +A B ̅C 左边=右边,所以等式成立 2.4(1)Y ′=(A +B̅C )(A +BC) 2.5(3)Y ̅=A B ̅̅̅̅(C +D ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅ C D ̅̅̅̅̅(A +B ̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅ 2.6:(1)Y =AB +AC +BC=AB (C +C̅)+AC (B +B ̅)+BC (A +A ̅) =ABC +ABC̅+AB ̅C +A ̅BC 2.7:(1)Y =A B̅+B ̅C +AC +B ̅C 卡诺图如下:所以,Y =B2.8:(2)画卡诺图如下:Y(A,B,C)=A +B̅+C2.9:(1)画Y (A,B,C,D )=∑m (0,1,2,3,4,6,8)+∑d(10,11,12,13,14)如下:Y (A,B,C,D )=A B̅+D ̅2.10:(3)解:化简最小项式:Y =AB +(A B +C )(A B̅+C ) =AB +(A B A B̅+A BC +A B ̅C +C C ) =AB (C +C )+A BC +A B̅C =ABC +ABC ̅+A BC +A B ̅C =∑m (0,3,6,7)最大项式:Y =∏M(1,2,4,5)2.13:(3)Y =AB̅+BC +AB ̅C +ABC D ̅ =AB̅(1+C )+BC (1+AD ̅) =AB ̅+BC =AB ̅+BC ̿̿̿̿̿̿̿̿̿̿̿̿ = AB ̅̅̅∙BC ̅̅̅̅̅̅̅̅̅̅̅技能题:2.16 解:设三种不同火灾探测器分别为A 、B 、C ,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:Y =AB +AC +BC =AB +AC +BC ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿ =AB ̅̅̅̅⋅AC̅̅̅̅⋅BC ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ =(A +B ̅)(A +C )(B ̅+C )̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ =A +B ̅̅̅̅̅̅̅̅+A +C ̅̅̅̅̅̅̅̅+B ̅+C̅̅̅̅̅̅̅̅第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空; 二、 1、√ 8、√; 三、 1、A 4、D练习题:3.2、解:(a)因为接地电阻4.7k Ω,开门电阻3k Ω,R>R on ,相当于接入高电平1,所以Y =A B 1̅̅̅̅̅̅=A +B +0=A +B (e) 因为接地电阻510Ω,关门电0.8k Ω,R<R off ,相当于接入高电平0,所以、 Y =A +B +0̅̅̅̅̅̅̅̅̅̅̅̅̅=A ̅⋅B ̅∙1̅̅̅̅̅̅̅̅̅̅=A +B +0=A +B3.4、解:(a) Y 1=A +B +0̅̅̅̅̅̅̅̅̅̅̅̅̅=A +B ̅̅̅̅̅̅̅(c) Y 3=A +B +1̅̅̅̅̅̅̅̅̅̅̅̅̅=1̅=0(f) Y 6=A ⋅0+B ⋅1̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=B̅3.7、解:(a) Y 1=A⨁B ⋅C =(A B +AB̅)C =A B C +AB ̅C3.8、解:输出高电平时,带负载的个数2020400===IH OH OH I I N G 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===IL OL OL I I N G 反相器可带17个同类反相器3.12EN=1时,Y 1=A , Y 2=B̅ EN=0时,Y 1=A̅, Y 2=B3.17根据题意,设A 为具有否决权的股东,其余两位股东为B 、C ,画卡诺图如下,则表达结果Y 的表达式为:Y =AB +AC =AB +AC ̿̿̿̿̿̿̿̿̿̿̿=AB ̅̅̅̅⋅AC̅̅̅̅̅̅̅̅̅逻辑电路如下:技能题:3.20:解:根据题意,A 、B 、C 、D 变量的卡诺图如下:Y =ABC +ABD =ABC +ABD ̿̿̿̿̿̿̿̿̿̿̿̿̿̿̿=ABC̅̅̅̅̅̅⋅ABD ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、 3、√ 4、√ 三、 5、A 7、C练习题:4.1;解:(a) Y =A⨁B +B ̅̅̅̅̅̅̅̅̅̅̅̅̅=A B +AB ̅+B ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=A B +B ̅̅̅̅̅̅̅̅̅̅̅=A +B ̅̅̅̅̅̅̅̅=AB ,所以电路为与门。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第8章习题解答

8-1.何谓量化、量化单位、量化误差、四舍五入量化法?

答:将数值连续的模拟量转换为数字量的过程称为量化。

数字量只能是某个最小数量单位Δ的整数倍,这个最小数量单位Δ称为量化单位。

实际被取样模拟量与量化单位之间的差称为量化误差。

四舍五入量化的方式,是把数值在∆+∆-)21(~)21(n n 之间的模拟电压都当作n Δ。

8-2.有一个8位倒T 型电阻网络DAC 中,已知V ERF =10V ,试求输入如下数字量,其输出的模拟电压值。

(1)各位全为1; (2)仅最高位为1;

(3)10011000; (4)01110110

解:模拟电压∑=-=708

22i i i REF

o d V u ,则有 (1)10256255⨯-=o u ;(2)10256128⨯-=o u ;(3)10256152⨯-=o u ;(4)10256

118⨯-=o u 8-3.已知某DAC 电路最小分辨电压为5mV ,最大满值输出电压5V ,试求该电路输入数字量的位数和基准电压各是多少?

答:基准电压为5V ,最小分辨电压mV V u n REF o 52

min ==,所以输入数字量为10位。

8-4.某8位ADC 电路满值输入电压为12V ,当输入电压值分别为63.9 mV 、6.93 mV 、11.7V 时,输出数字量为多少?

解:电路分辨率为12/256=46.9mV ,则输出的数字量分别为:00000001、00000000、11111001。

8-5.一个8位逐次比较型号ADC ,满值输入电压为10V ,时钟频率约2.5MHz ,试求

(1)转换时间是多少?

(2)v I =8.5V ,输出数字量是多少?

(3)v I =2.4V ,输出数字量是多少?

解:(1)完成一次转换需要n+2个周期,所以转换时间10/2500000=4μs 。

(2)量化电平Δ=10×2/511,输出数字量为11011001。

(3)量化电平Δ=10×2/511,输出数字量为00111101。

8-6.在双积分A/D 转换电路中的计数器,若做成十进制的,其最大容量:N =200(10),时钟频率f =10kHz ,V REF =6V 。

(1)试求第一次积分时间T 1;

(2)已知计数器的计数值N 2 =369(10),问此时输入电压v I 为多少?

解:(1)T 1= NT c = 200/10000 = 0.02s (2)V V N N v REF I 07.116200

3692=⨯== 8-7.如果一个四位逐位比较型A/D 转换电路的时钟频率为500kHz ,试计算完成一次A/D 转换所需的时间是多少?如果要求转换时间不得大于10μs ,那么时钟信号频率应选多少?

解:s s T n t μ12000012.0500000/6)2(===+=

KHz Hz s t n f 60010*610/6/)2(55===+=-

所以时钟信号频率应大于600KHz.。