烧写EPCS说明

EDA开发板

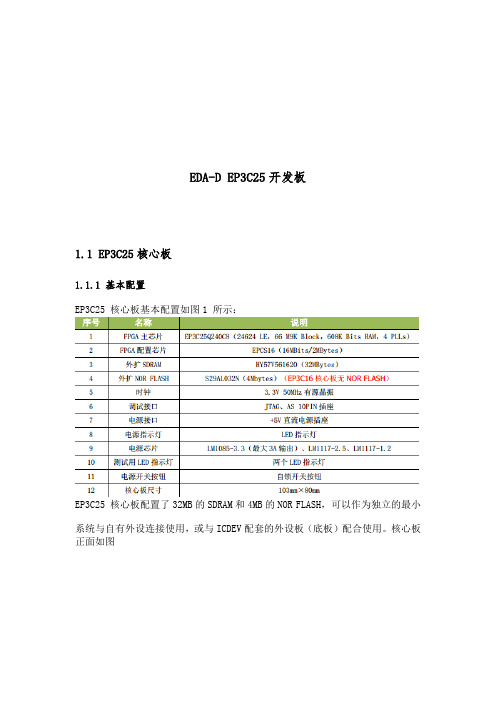

EDA-D EP3C25开发板1.1 EP3C25核心板1.1.1 基本配置EP3C25 核心板基本配置如图1 所示:EP3C25 核心板配置了32MB的SDRAM和4MB的NOR FLASH,可以作为独立的最小系统与自有外设连接使用,或与ICDEV配套的外设板(底板)配合使用。

核心板正面如图2 所示,背面如图3所示。

1.1.2 跳线说明1)BEEP 跳线:该跳线用于连接 ICDEV 外设板的蜂鸣器控制端,在连接外设板的情况下给EP3C25 下载SOF 文件或POF文件时会导致蜂鸣器长鸣,断开跳线可以避免蜂鸣器发声(尤其是下载POF 文件时耗时较长);如果不使用外设板,该跳线的作用仅仅是将该I/O连接到插针。

2)FLASH片选跳线:该跳线用于连接NOR FLASH 片选信号线,在不使用FLASH 的情况下,该跳线的引出针脚可以作为EP3C25的普通 I/O口使用。

3)MSEL1 跳线:该跳线用于连接或断开EP3C25的MSEL1管脚与2.5VA的连接,在通过配置芯片启动时需要用到该跳线。

1.2 外设板(底板)外设板基本配置如图4所示外设板正面如图5所示,背面如图6 所示2.1EDA-D EP3C25结构功能特点:EDA-D系列是深圳市启点时代科技有限公司针对电子竞赛、IP验证、FPGA教学和开发设计的一系列开发板,该系列开发板分为核心板和底板设计,核心板和底板可以分离,核心板可以独立运行,底板设计了大量实验资源,对于实验验证和开发测试都非常有用,配合丰富的实验例程和详细的实验指导,可以在尽可能短的时间内掌握基本的CPLD和FPGA设计方法和思路,所有配套实验均提供源代码和工程文件,用户可以直接使用该代码或者修改后用于自己的设计开发中。

所有底板的器件均分配了独立的IO,不存在IO复用,可以同时使用底板的全部资源!针对CPLD/FPGA入门较难的特点,实验代码在设计上由浅入深,从最基本的基础逻辑门开始,尽量避免一开始就罗列一堆代码,代码设计注重思路与基础,每个实验源码均有功能说明、管脚分配和验证说明,部分综合性实验例程有设计思路分析。

FPGA烧写问题

altera cyclone器件告别AS下载模式,直接用JTAG配置器件进行编程看CYCLONE II的器件手册时,看到一段关于配置器件的描述:可以通过JTAG接口对串行配置器件进行编程,可是里面没有详细的使用方法,在altera的网站上找到了一些关于这个的资料先介绍一下SFL:Serial Flash Loader,它是通过JTAG接口在系统编程(isp)串行配置器件。

这种方法主要是通过FPGA作为一个JTAG与串行配置器件之间的桥梁,优点是能通过一个JTAG接口对器件进行配置,缺点是慢,因为在编程前要对FPGA进行配置。

废话少说,首先编译生成SOF文件,也就是JTAG方式下的下载文件,然后1 在“文件”里选择“Convert Programming Files”,出现对话框后2 在programming file type里选.jic3 在configuration device里选择相应的串行配置器件4 file name选择转换文件5 选sof data,单击add file选择sof文件6 flash loader单击add device选择FPGA器件然后OK生成JIC文件,后面的事情跟JTAG下下载一样,只是将文件类型选为JIC文件,可惜我转换的时候选EPCS1时,老提示容量不够,选EPCS4就没有问题了,大家可以试试。

cyclone器件, jtag和as下载模式JTAG是直接烧到FPGA里面的,由于是SRAM,所以断电后要重烧;AS是烧到FPGA的配置芯片里保存的,每次上电就写到FPGA里;pof文件可以通过as方式下载(保证byteblasterII/usb blaster连接正确);sof文件或者转换的jic可以通过jtag方式下载;这两种下载模式使用的接口外形是完全一样的,要注意区分!使用Flash Loader(JTAG模式)下载EPCS器件一般来说Altera公司Cyclone或者CycloneII系列FPGA相应的配置器件会选择EPCS系列串行FLASH。

NiosII烧写epcs的问题

NIOS烧写epcs_flash关于Nios核的创建的可以参考网络上的文档,我主要是参考了黑金动力社区的两份文档。

列出如下。

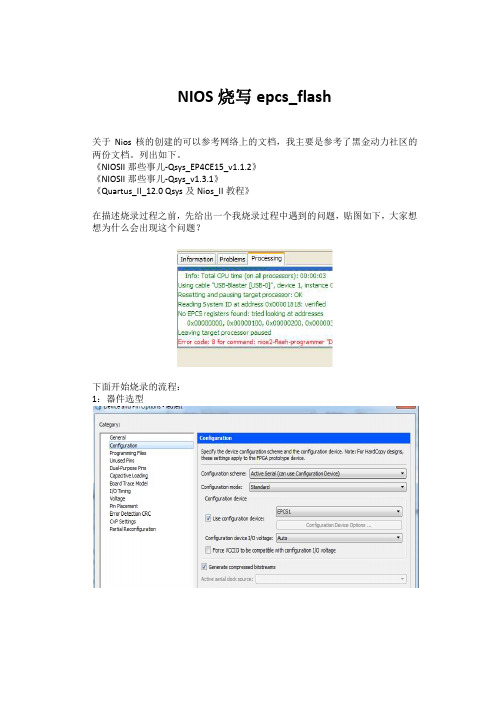

《NIOSII那些事儿-Qsys_EP4CE15_v1.1.2》《NIOSII那些事儿-Qsys_v1.3.1》《Quartus_II_12.0 Qsys及Nios_II教程》在描述烧录过程之前,先给出一个我烧录过程中遇到的问题,贴图如下,大家想想为什么会出现这个问题?下面开始烧录的流程:1:器件选型2:引脚设置,参见下面两张图。

3:epcs_flash_controller的设置,重要哦。

4:连接好四个相关引脚。

5:先将sof文件下载进fpga,以确保fpga内有了nios核。

6:在nios的开发环境里面,选择Nios II -> Flash Programmer7: File -> New,打开如下界面,选择对应的xxxx.sopcinfo文件。

8: 选择Connections 在打开的界面中选好xxxx.qpf文件。

最好打钩以忽略掉system ID的选项。

9:点击Add按钮,一次添加好xxxx.sof文件和xxxx.elf文件。

如图。

10:点击Start按钮,等待烧录完成即可。

恭喜你已经完成了通过nios的Flash Programmer进行epcs的烧写。

以上是在Cyclone IV系列进行的操作,另外本人还遇到一个问题,就是在Cyclone V系列的nios创建过程中无法引出epcs_flash_controller的引出端,导致烧录的时候会报开头贴出的错误。

如果谁在V系列遇到并解决了此问题还请来信。

china_fpga@。

单片机程序烧录的3种方式(ISP、ICP、IAP)是什么

单片机程序烧录的3种方式(ISP、ICP、IAP)是什么说起给单片机烧录程序,大家应该都不陌生吧,我最早接触单片机是从51单片机开始的,型号是STC89C52RC,当时烧录程序就是用的下面这种烧录软件——STC-ISP。

这种方式,通过串口连接单片机,选择一个合适的波特率就可以烧录了。

后来学习STM32,编程时使用KEIL软件自带的下载按钮就能下载程序,方便了不少,但需要额外使用J-Link等下载器。

再后来,接触到产品研发,给已经发布出的产品升级,都是要靠远程无线升级的(想想看,产品已经到客户那里了,当软件需要升级时,要是还使用有线的方式烧录程序,得有多麻烦)既然给单片机烧录程序的方式有多种,那烧录方式具体怎么分类呢?可以分为3种:ISP(In-System Programming)在系统编程,使用引导程序(Bootloader)加上外围UART/SPI等接口进行烧录。

ICP (In-circuit programmer)在电路编程,使用SWD/JTAG接口。

IAP(In-Application Programming)指MCU可以在系统中获取新代码并对自己重新编程,即用程序来改变程序。

这3种烧录方式的原理是什么呢?在分析原理之前,需要先了解一下单片机Flash的访问地址,看看程序是烧录到哪个位置了。

单片机Flash在地址映射表中位置下图是一张STM32F4xx的地址映射表,从0x0000 0000到0xFFFF FFFF,总计4Gbyte。

单片机的片上Flash、片上RAM、片上外设以及外部扩展接口的访问地址,都被映射到这4Gbyte的范围之内。

这张图中,我们需要先注意下半部分Main memory 主存储区通常,我们编写的代码,是放到主存储区的起始位置(0x0800 0000)开始运行的,烧录程序时,直接将程序烧录到这里即可(KEIL 软件给STM32烧录程序的默认烧写地址就是0x0800 0000开始)System memory系统存储区System memory(起始位置0x1FFF 000)是STM32在出厂时,由ST在这个区域内部预置了一段BootLoader,也就是我们常说的ISP程序,这是一块ROM,出厂后无法修改。

Alteraepcs烧写步骤

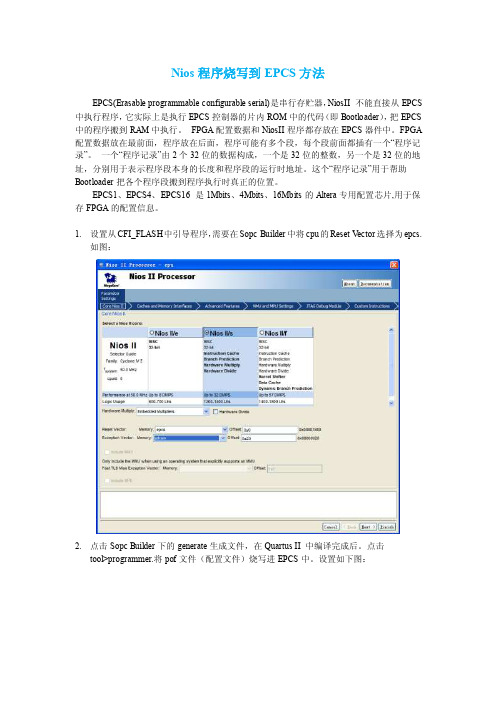

Nios程序烧写到EPCS方法EPCS(Erasable programmable configurable serial)是串行存贮器,NiosII 不能直接从EPCS 中执行程序,它实际上是执行EPCS控制器的片内ROM中的代码(即Bootloader),把EPCS 中的程序搬到RAM中执行。

FPGA配置数据和NiosII程序都存放在EPCS器件中。

FPGA 配置数据放在最前面,程序放在后面,程序可能有多个段,每个段前面都插有一个“程序记录”。

一个“程序记录”由2个32位的数据构成,一个是32位的整数,另一个是32位的地址,分别用于表示程序段本身的长度和程序段的运行时地址。

这个“程序记录”用于帮助Bootloader把各个程序段搬到程序执行时真正的位置。

EPCS1、EPCS4、EPCS16 是1Mbits、4Mbits、16Mbits的Altera专用配置芯片,用于保存FPGA的配置信息。

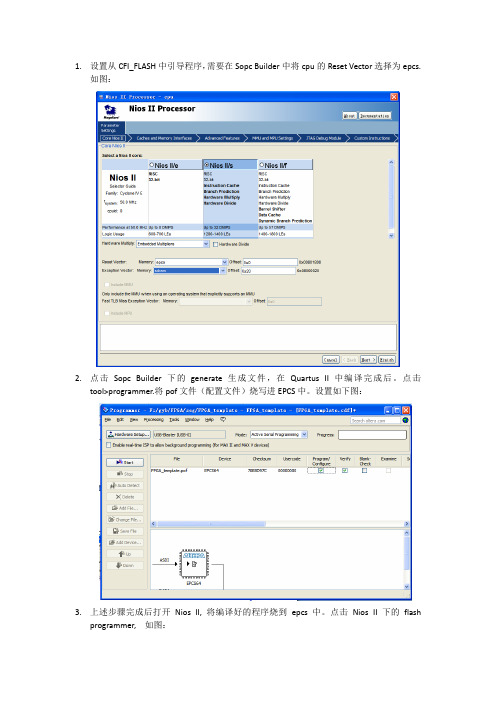

1.设置从CFI_FLASH中引导程序,需要在Sopc Builder中将cpu的Reset V ector选择为epcs.如图:2.点击Sopc Builder下的generate生成文件,在Quartus II 中编译完成后。

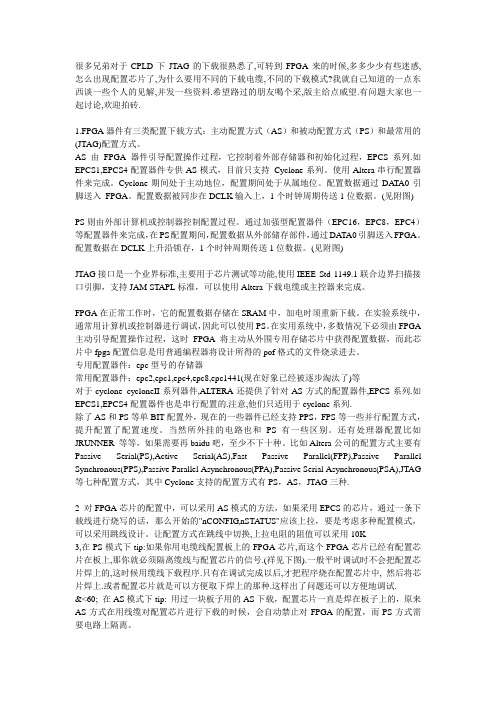

点击tool>programmer.将pof文件(配置文件)烧写进EPCS中。

设置如下图:3.上述步骤完成后打开Nios II, 将编译好的程序烧到epcs中。

点击Nios II下的flashprogrammer, 如图:4.点击file>new, 并添加sopcinfo文件。

如图:5.点击ok后,出现下图(这幅图不是截的全图):6.图中有两个选项Fash:epcs 和Flash:cfi_flash. 选中Flash:epcs,并添加elf文件,点击start就将开始向epcs烧写程序。

说明:向epcs烧写pof文件(配置文件)和软件程序时可以在Nios II中同时进行。

FPGA EPCS烧写及NiosII Flash烧写过程

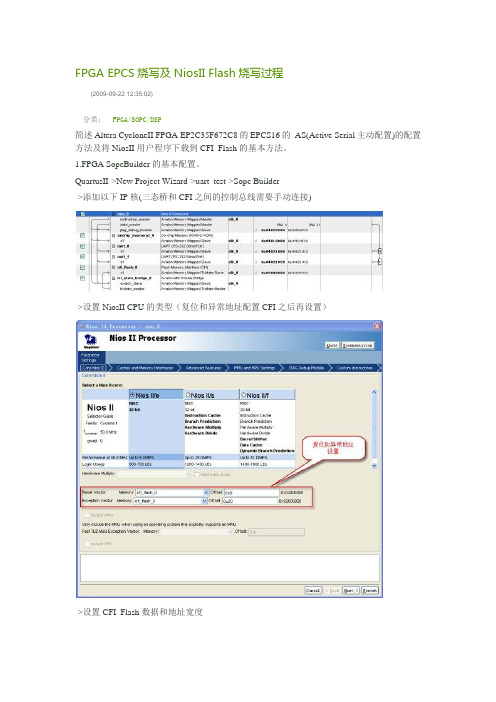

FPGA EPCS烧写及NiosII Flash烧写过程(2009-09-22 12:35:02)分类:FPGA/SOPC/DSP简述Altera CycloneII FPGA EP2C35F672C8的EPCS16的AS(Active Serial主动配置)的配置方法及将NiosII用户程序下载到CFI_Flash的基本方法。

1.FPGA SopcBuilder的基本配置。

QuartusII->New Project Wizard->uart_test->Sopc Builder->添加以下IP核(三态桥和CFI之间的控制总线需要手动连接)->设置NiosII CPU的类型(复位和异常地址配置CFI之后再设置)->设置CFI_Flash数据和地址宽度->设定CFI时序->Generate产生NiosII CPU核运行的硬件环境->关闭Sopc Builder->QuartusII(当前工程)->File->New->Block Diagram->OK ->添加NiosII CPU->定义输入输出引脚->Assignments->Device->->Assignments->Device->Device&Pin Options->unused Pins->As input tri-stated ->Analysis&Synthesis->tools->TclScript->Project->Tcl_script1->Start Compilcation->EDA NetList Writer->Pragram Device->Hardware Setup-> Usb-blaster->Mode->Cautions:将Usb-blaster由FPGA jtag口换到AS口。

四、EPCS控制器的添加及烧写

1.4 EPCS 控制器的添加及烧写1.实验目的(1)进一步熟悉Nios II 系统的构成及开发流程;(2)进一步熟悉SOPC Builder 和Nios II IDE 的使用; (3)掌握EPCS 控制器的添加与使用;2.实验现象8个LED 灯花样闪烁。

3.实验原理原理图如图1.4.1所示图1.4.1由图1.4.1我们可以得到如表1.4.1所示的外设一览表:事实上,EPCS 是一种串行FLASH ,因此EPCS 既可以作为配置芯片单独存储配置文件,这是主要作用,也可以代替之前实验中的并行FLASH 存储程序,但必需使用存储配置文件后的剩余空间。

用EPCS的一个好处是可以节约IO口,因为并行的FLASH需要占用大约40个IO口。

不过EPCS的烧写次有限,因此不建议频繁烧写,只有当程序彻底调试好后再下载进去。

4.实验内容(1)在Quartus II中建立一个工程;(2)使用SOPC Builder建立生成一个具有表1.4.1所示元件的Nios II硬件系统;(3)在Quartus II工程中添加PLL;(4)建立基于Nios II的硬件系统并编译生成配置文件*.sof;(5)在Nios II IDE中建立对应硬件系统的Nios II C/C++ Application,编写程序;(6)将配置文件*.sof和可执行文件*.elf都下载到FPGA进行在线运行。

5.实验步骤上一节实验介绍过的内容不再介绍,这里只介绍EPCS控制器的添加。

完整的Nios II 系统图如图1.4.2所示,把复位地址设置设为EPCS,异常向量地址设为SDRAM。

图1.4.21)在SOPC Builder中添加EPCS控制器在可用元件列表里双击EPCS Serial Flash Controller(图1.4.3),弹出如图1.4.4所示的设置向导,按图所示进行设置。

图1.4.3图1.4.42)在Quartus II中组合所有模块并添加引脚编译EPCS1没有对外的管脚需要添加,Quartus II会自动为其分配。

第四章QuartusII使用方法

3)波形文件存盘。Filesave as将默认名为singt.vwf的波 形文件存入工程文件夹中,

4)将工程CNT10的端口信号节点选入波形编辑器中。 Viewutility windowsnode finder命令,在对话框的filter下 拉列表中选pins:all,然后单击list按钮,在下方的Nodes finder窗口中出现设计中的CNT10工程的所有端口引脚名, 如果list不显示CNT10工程的端口引脚,需要重新编译一次。 最后将重要的端口节点CLK,EN,RST,COUT和输出总线信号 CQ分别拖到波形编辑器窗口后,关闭Nodes Found窗口, 调整波形窗口,使仿真坐标处于适当位置。

2)设置编程器。初次安装QuartusII,在编程前还必须进行编程 器选择操作。单击Hardware Setup按钮可设置下载接口方式, 在对话框中选择Hardware Setting选项卡,双击ByeBlasterMV, 编程方式为: ByeBlasterMV[LPT1]。如果在编程窗口Currently selected hardware右侧显示No Hardware的话必须加入下载方 式。

6)结束设置,下一步弹出工程设置统计窗口,列出相关设置 最后finish,出现设好的工程名的工程管理窗口,显示本工程 项目的层次结构和各层次实体名。

4 烧写软件的使用方法

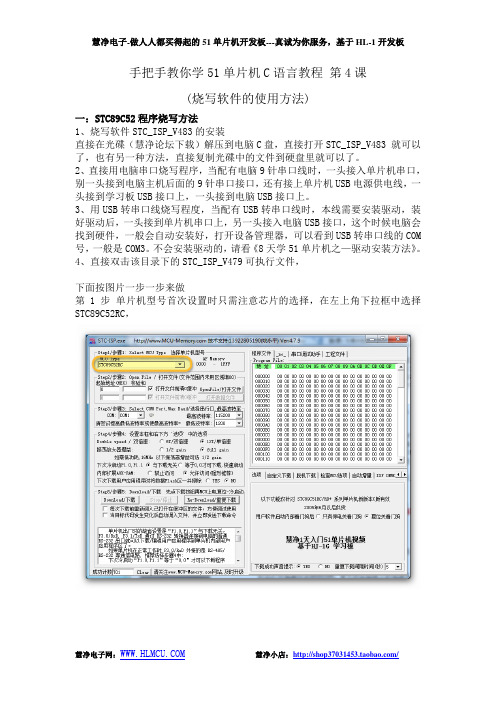

手把手教你学51单片机C语言教程第4课(烧写软件的使用方法)一:STC89C52程序烧写方法1、烧写软件STC_ISP_V483的安装直接在光碟(慧净论坛下载)解压到电脑C盘,直接打开STC_ISP_V483 就可以了,也有另一种方法,直接复制光碟中的文件到硬盘里就可以了。

2、直接用电脑串口烧写程序,当配有电脑9针串口线时,一头接入单片机串口,别一头接到电脑主机后面的9针串口接口,还有接上单片机USB电源供电线,一头接到学习板USB接口上,一头接到电脑USB接口上。

3、用USB转串口线烧写程度,当配有USB转串口线时,本线需要安装驱动,装好驱动后,一头接到单片机串口上,另一头接入电脑USB接口,这个时候电脑会找到硬件,一般会自动安装好,打开设备管理器,可以看到USB转串口线的COM 号,一般是COM3。

不会安装驱动的,请看《8天学51单片机之—驱动安装方法》。

4、直接双击该目录下的STC_ISP_V479可执行文件,下面按图片一步一步来做第1步单片机型号首次设置时只需注意芯片的选择,在左上角下拉框中选择STC89C52RC,第2步打开文件点击软件界面上的Open File 打开对话框,将HJ-1G配套源码里面的LED.hex文件选择,选择好后点击Open 。

第3步 COM口一般的台式机大多只有一个串口,所以COM栏就选择COM1,如果使用别的串口那就选择相应的串口号,USB转串口线一般是COM3。

看设备管理器处COM号是多少号,这里就用多少号。

第5步点击下载注意:在点击之前,一定要关掉单片机电源开关,点击后3秒后打开电源开关,因为STC的单片机内有引导码,在上电的时候会与计算机自动通讯,检测是否要执行下载命令,所以要等点完下载命令后再给单片机上电,然后点击如下图的Download/下载钮,接着按下实验板上电源给单片机上电。

若出现上述图片,则说明已经给单片机成功下载了程序,并且已经加密,成功下载程序后开发板上的八个流水灯中最上方那个会点亮。

FPGA烧写问题

altera cyclone器件告别AS下载模式,直接用JTAG配置器件进行编程看CYCLONE II的器件手册时,看到一段关于配置器件的描述:可以通过JTAG接口对串行配置器件进行编程,可是里面没有详细的使用方法,在altera的网站上找到了一些关于这个的资料先介绍一下SFL:Serial Flash Loader,它是通过JTAG接口在系统编程(isp)串行配置器件。

这种方法主要是通过FPGA作为一个JTAG与串行配置器件之间的桥梁,优点是能通过一个JTAG接口对器件进行配置,缺点是慢,因为在编程前要对FPGA进行配置。

废话少说,首先编译生成SOF文件,也就是JTAG方式下的下载文件,然后1 在“文件”里选择“Convert Programming Files”,出现对话框后2 在programming file type里选.jic3 在configuration device里选择相应的串行配置器件4 file name选择转换文件5 选sof data,单击add file选择sof文件6 flash loader单击add device选择FPGA器件然后OK生成JIC文件,后面的事情跟JTAG下下载一样,只是将文件类型选为JIC文件,可惜我转换的时候选EPCS1时,老提示容量不够,选EPCS4就没有问题了,大家可以试试。

cyclone器件, jtag和as下载模式JTAG是直接烧到FPGA里面的,由于是SRAM,所以断电后要重烧;AS是烧到FPGA的配置芯片里保存的,每次上电就写到FPGA里;pof文件可以通过as方式下载(保证byteblasterII/usb blaster连接正确);sof文件或者转换的jic可以通过jtag方式下载;这两种下载模式使用的接口外形是完全一样的,要注意区分!使用Flash Loader(JTAG模式)下载EPCS器件一般来说Altera公司Cyclone或者CycloneII系列FPGA相应的配置器件会选择EPCS系列串行FLASH。

altera epcs烧写步骤

1.设置从CFI_FLASH中引导程序,需要在Sopc Builder中将cpu的Reset Vector选择为epcs.

如图:

2.点击Sopc Builder下的generate生成文件,在Quartus II 中编译完成后。

点击

tool>programmer.将pof文件(配置文件)烧写进EPCS中。

设置如下图:

3.上述步骤完成后打开Nios II, 将编译好的程序烧到epcs中。

点击Nios II下的flash

programmer, 如图:

4.点击file>new, 并添加sopcinfo文件。

如图:

5.点击ok后,出现下图(这幅图不是截的全图):

6.图中有两个选项Fash:epcs 和Flash:cfi_flash. 选中Flash:epcs,并添加elf文件,点击start

就将开始向epcs烧写程序。

说明:向epcs烧写pof文件(配置文件)和软件程序时可以在Nios II中同时进行。

不过

需要在步骤2中烧写一下sof文件或pof文件。

建议烧写sof文件(快)。

在步骤5中先添加sof文件,然后再添加elf文件。

如图:

注意:中间出现错误自行上网查找原因与解决办法。

这里只是提供步骤流程。

FPGA配置(AS、PS、JTAG)

很多兄弟对于CPLD下JTAG的下载很熟悉了,可转到FPGA来的时候,多多少少有些迷惑,怎么出现配置芯片了,为什么要用不同的下载电缆,不同的下载模式?我就自己知道的一点东西谈一些个人的见解,并发一些资料.希望路过的朋友喝个采,版主给点威望.有问题大家也一起讨论,欢迎拍砖.1.FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone期间处于主动地位,配置期间处于从属地位。

配置数据通过DA TA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

(见附图)PS则由外部计算机或控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

(见附图)JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。

在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。

在实用系统中,多数情况下必须由FPGA 主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

专用配置器件:epc型号的存储器常用配置器件:epc2,epc1,epc4,epc8,epc1441(现在好象已经被逐步淘汰了)等对于cyclone cycloneII系列器件,ALTERA还提供了针对AS方式的配置器件,EPCS系列.如EPCS1,EPCS4配置器件也是串行配置的.注意,他们只适用于cyclone系列.除了AS和PS等单BIT配置外,现在的一些器件已经支持PPS,FPS等一些并行配置方式,提升配置了配置速度。

关于Nios烧写“No EPCS layout data”错误

关于Nios烧写“No EPCS layout data”--------------------------------------------------------------------------------如果在EPCS下载时遇到这个问题:"No EPCS layout data - looking for section [EPCS-EF3013]"这是由于EPCS器件不同版本引起的,解决方法1.在Nios-IDE的安装路径下的bin文件夹中新建一个文件“nios2-flash-override.txt”。

2.输入下述代码,下面描述的器件都是Altera的EPCS器件,sector_size表示sector大小,sector_count表示sector个数;[EPCS-202011] # EPCS1N (lead-free)sector_size = 32768sector_count = 4[EPCS-202013] # EPCS4N (lead-free)sector_size = 65536sector_count = 8[EPCS-202015] # EPCS16N (lead-free)sector_size = 65536sector_count = 32[EPCS-202017] # EPCS64N (lead-free)sector_size = 65536sector_count = 128以上这四段代码分代表四种大小的EPCS,我们根据实际的EPCS大小添加代码。

比如报错为:"No EPCS layout data - looking for section [EPCS-EF3013]",那么应该添加的代码则为[EPCS-EF3013] # EPCS4N (lead-free)sector_size = 65536sector_count = 8前提是用的EPCS4 ,若是其他型号则可选用另外的代码。

FPGA几种下载方式

AS PS JTAG 配置方式的区别AS模式: 烧到FPGA的配置芯片里保存的,FPGA器件每次上电时,作为控制器从配置器件EPCS 主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA的编程;PS模式:EPCS作为控制器件,把FPGA当做存储器,把数据写人到FPGA中,实现对FPGA的编程。

该模式可以实现对FPGA在线可编程;JTAG:直接烧到FPGA里面的,由于是SRAM,断电后要重烧;.pof文件可以通过AS方式下载(保证byteblasterII/usb blaster连接正确);.sof文件或者转换的.jic可以通过JTAG方式下载。

1.FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持 Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone期间处于主动地位,配置期间处于从属地位。

配置数据通过DATA0引脚送入 FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

PS则由外部计算机或控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。

在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。

在实用系统中,多数情况下必须由FPGA 主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

EPCS4中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

(2)串行配置器件不能级联.

(3)连接FPGA 配置手册.

MSEL[] 输入引脚选择AS配置模式.有关详细信息,请参见相应FPGA系列篇章

(4)有关Altera FPGA中AS方案配置引脚I / O要求详细信息,请参见相应FPGA系列手册 配置篇..

该FPGA作为配置师傅在配置流程,并提供

时钟串行配置器件.该FPGA实现串行配置

(4)有关Altera FPGA中AS方案配置引脚I / O要求详细信息,请参见相应FPGA系列手册 配置篇.

芯片中文手册,看全文,戳

图 3-3.

AlteraFPGA配置在AS模式(由APU或第三方编程串行配置器件

程序员) (注1),(4)

须知 图 3-3:

(1)对于在V 值,请参见相应FPGA系列手册配置章节.

AlteraFPGA配置在AS模式(串行配置器件编程为使用下载电缆)

(注1) , (4)

须知 图 3-2:

(1)对于在V 值,请参见相应FPGA系列手册配置章节.

ቤተ መጻሕፍቲ ባይዱ

(2)串行配置器件不能级联.

(3)连接FPGA 配置手册.

MSEL[] 输入引脚选择AS配置模式.有关详细信息,请参见相应FPGA系列篇章

厂商

® 编程单元(APU)和

■ 交付使用擦除存储器阵列(所有位设置为

1)

1

本文档中使用术语"串行配置设备"指Altera EPCS1,

EPCS4,EPCS16,EPCS64和EPCS128.

芯片中文手册,看全文,戳

功能说明

随着支持主动串行配置SRAM为基础设备,配置数据必须每次都重新加载设备上电后 ,系统重新配置,或者在新配置数据是必需.串行配置设备是与可以存储配置数 据为支持主动串行配置和重新加载数据到上电时或重新配置器件FPGA设备串行接 口闪速存储装置.

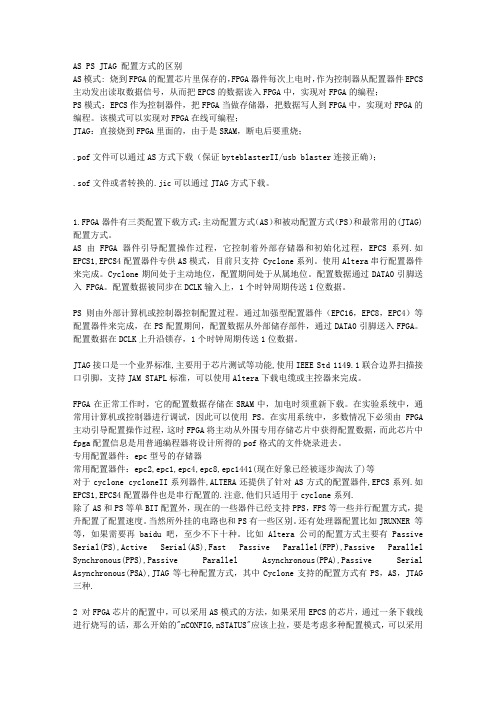

实验08_SOPC_EPCS及FLASH编程S

实验任务: 添加EPCS内核,。

知识点:

1.掌握EPCS内核添加设置方法。 2.掌握时序约束设置的方法。 3.掌握用Flash Programmer下载.sof和.elf文件到EPCS的方 法。 4.掌握生成.jic文件,对EPCS编程的方法。

系统需求:

1.实验之前,请以课件为基础,预习实验内容。 2.在指定的文件夹存储、命名各工程项目和文件。 3.规范实验报告的书写内容和格式。

1.启动QUARTUS II,创建或移动系统设计工程(略)

2.启动Qsys,在原NIOS II系统中添加UART内核并设置

(1)打开 Qsys软件,添加EPCS内核进行设置

1.选择菜单栏,启动Qsys软件。 或直接在文件导航栏上双击 【.qsys】文件,打开Qsys软件, 并自动打开NIOS II系统设置文 件对话框。

(2)完成其他操作及生成NIOS II系统。

6. 在NIOS II处理器内核设置中,修改复 位向量设置。双击NIOS II处理器内核, 在设置框的“Reset Vector”设置中,下 拉,选择【epcs.epcs_control_port】为 复位存储器,其他不做修改。【Finish】 完成NIOSII内核修改。

② 存储非易失性数据:例如串行号,NIC号和其他需要 长久储存的数据。

③ 管理FPGA配置数据:EPCS可存储FPGA的配置数据,并 在上电时自动完成对FPGA的配置。具有网络接口的嵌入 式系统可从网上接收新的FPGA配置数据,并通过EPCS控 制器将新的配置数据下载到EPCS串行配置器件中。

6

EPCS控制器功能

7. 下拉【Tasks】栏至最低层,双击【Write SDC File】,弹出时序约束文件保存对话框。修改名称或 使用默认名称,【OK】确定。退出时序分析对话界面, 提示是否保存SDC文件,前面已保存,故现在选择 【NO】,退出。

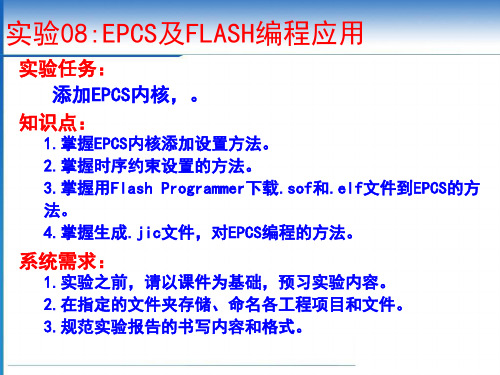

烧写EPCS说明

烧写EPCS说明一:首先在sopc builder中加入epcs flash controller,二:将epcs controller 的clock 设置成与cpu 相同的clock三:双击nios cpu,将reset vector 设置为epcs_flash_controller四:generate sopc builder , 并重新编译quartus 工程,分配引脚五:更改FPGA引脚,将双功能引脚改为user io pin 打开如下菜单点击将所有引脚改为用户引脚七:修改dow.sh的文件中的基地址,将sopc中的epcs的地址付给epcs --base=0x00001000 nios2-flash-programmer --epcs --base=0x00001000 "nios_openMac.flash"# Creating .flash file for the projectelf2flash --epcs --after="nios_openMac.flash" --input="epl.elf" --output="epcs_flash_controller_0.flash"# Programming flash with the projectnios2-flash-programmer --epcs --base=0x00001000 "epcs_flash_controller_0.flash"一:在文件nios2-flash-override.txt中添加相应的EPCS的id 号,是的quartus支持相应的epcs型号[EPCS-010214] # EPCS16N (Spansion lead-free)sector_size = 65536sector_count = 32二:将该文件拷贝到C:\altera\10.0sp1\nios2eds\bin 目录下三:将quartus工程中的.sof 文件(假设为xxx.sof)和nios 工程中的.elf文件(假设为xxx.elf)拷贝到一个目录下。

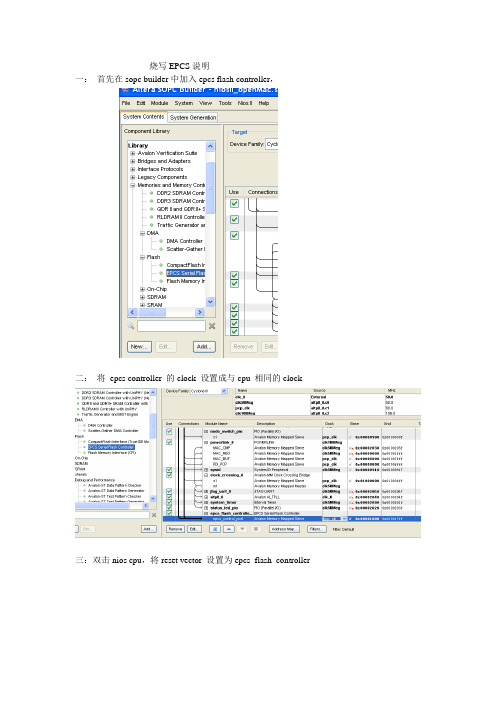

程序烧写说明

程序烧写说明

1.双击图标打开MPLAB IDE;

2.点击File,在下拉菜单中点击Import,如右图所示;

3.点击Import后弹出对话框,找到wuguike.hex并打开

;

4.点击Programmer,在下拉菜单中选择第一个选项Select Programmer,再其弹出的菜单中

选择MPLAB ICD 3,选择成功后MPLAB ICD 3前面会打上勾,如图所示:

5.和第四步骤一样,点击Programmer,在下拉菜单中选择最后一个选项Settings…,弹出对话

框,点击红色圈内的选择,设置成如图所示

即可,然

后点击确定;

6.在设置过程中不能先接上PCB板,只有设置好后才能接,接上PCB板后点击红色圈内图

标进行烧写

,烧完后提示则表示成功烧写,否则需要重烧或捡

出放于不良品处。

备注:第三步wuguike.hex这个文件不能放在有中文名的路径下,否则将打不开。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

烧写EPCS说明

一:首先在sopc builder中加入epcs flash controller,

二:将epcs controller 的clock 设置成与cpu 相同的clock

三:双击nios cpu,将reset vector 设置为epcs_flash_controller

四:generate sopc builder , 并重新编译quartus 工程,分配引脚五:更改FPGA引脚,将双功能引脚改为user io pin 打开如下菜单

点击

将所有引脚改为用户引脚

七:修改dow.sh的文件中的基地址,将sopc中的epcs的地址付给epcs --base=0x00001000 nios2-flash-programmer --epcs --base=0x00001000 "nios_openMac.flash"

# Creating .flash file for the project

elf2flash --epcs --after="nios_openMac.flash" --input="epl.elf" --

output="epcs_flash_controller_0.flash"

# Programming flash with the project

nios2-flash-programmer --epcs --base=0x00001000 "epcs_flash_controller_0.flash"

一:在文件nios2-flash-override.txt中添加相应的EPCS的id 号,是的quartus支持相应的epcs型号

[EPCS-010214] # EPCS16N (Spansion lead-free)

sector_size = 65536

sector_count = 32

二:将该文件拷贝到C:\altera\10.0sp1\nios2eds\bin 目录下

三:将quartus工程中的.sof 文件(假设为xxx.sof)和nios 工程中的.elf文件(假设为xxx.elf)拷贝到一个目录下。

四:创建一个脚本(假设名字为dow.sh),将这两个文件转换为.flash 文件,并下载到epcs 中,dow.sh文件内容如下(将dow.sh文件和.sof,.elf文件放在同一个目录下):

#!/bin/sh

#

# This file was automatically generated by the Nios II IDE Flash Programmer.

#

# It will be overwritten when the flash programmer options change.

#

# Creating .flash file for the FPGA configuration

sof2flash --epcs --input="nios_openMac.sof" --output="nios_openMac.flash"

nios2-flash-programmer --epcs --base=0x00000000 "nios_openMac.flash"

# Creating .flash file for the project

elf2flash --epcs --after="nios_openMac.flash" --input="epl.elf" --output="epcs_flash_controller_0.flash"

# Programming flash with the project

nios2-flash-programmer --epcs --base=0x00000000 "epcs_flash_controller_0.flash"

五:先用quartus 的programer tool 将.sof下载到目标fpga。

六:打开nios command shell

Cd 到dow.sh文件所在的目录(cd “XXX/xxxxx/”),

然后运行dow.sh 脚本(敲入命令./dow.sh)

七:如果显示如下信息:no layout data , 意味着没有epcs信息,需要在nios2-flash-override.txt 中添加该epcs的id 信息,添加如下,修改id信息。