2.2.3译码器解析

332 译码器.

2020/9/25

11

例3-4 试用74LS138译码器实现逻辑函数:

F(A, B,C) m(1,3,5,6,7)

解:因为 Yi mi (i 0,1,2,7)

则 F ( A, B,C) m(1,3,5,6,7)

m1 m3 m5 m6 m7

m1 m3 m5 m6 m7

Y1 Y3 Y5 Y6 Y7

30

(2) LED数码管 LED数码管又称为半导体数码管,它是由多个 LED按分段式封装制成的。LED数码管有两种形式: 共阴型和共阳型。

高电平驱动

低电平驱动

2020/9/25

公共阴极

公共阳极

图3-14 七段显示LED数码管

(a) 外形图 (b) 共阴型 (c) 共阳型

31

2.七段显示译码器

(1)七段字形显示方式 LED数码管通常采用图3-15所示的七段字形

输出5 端

高电平 有效

表3-6 74LS138的功能表

低电平 有效

禁止 译码

译 码 工 作

2020/9/25

译中为0

6

低电平有 效输出

三位二进 制代码

使能端

图3-8 74LS138的逻辑符号

2020/9/25

7

74LS138的逻辑功能

三个译码输入端(又称地址输入端)A2、

A1、A0,八个译码输出端 Y0~Y7,以及三个控制 端(又称使能端)S1、S2 、S3。

十进

制数 LT

01 11 21 31

41 51 61 71

表4.15 74LS47功能表

输入

RBI D C B A

1 0000 × 0001 × 0010 × 0011

译码器的原理及应用

译码器的原理及应用1. 译码器的定义译码器是一种数字电路,用于将输入的数字信号转换为对应的输出信号。

它是一种逻辑电路,根据特定的编码规则将输入的信息解码成对应的输出信号。

译码器通常用于将二进制码转换为十进制数、BCD码、7段LED显示等形式。

2. 译码器的原理译码器的原理基于布尔代数和逻辑门电路。

它通过使用多个逻辑门电路来实现输入信号的解码,并产生对应的输出信号。

具体的原理如下:•输入信号:译码器通常具有多个输入引脚,每个引脚对应一个输入信号。

这些输入信号可以是二进制码、BCD码等。

输入信号经过逻辑门电路的处理后,产生对应的输出信号。

•逻辑门电路:译码器通常使用与门、或门、非门等逻辑门电路来进行信号的处理。

通过组合这些逻辑门电路,可以实现对不同编码方式的解码。

•解码规则:译码器的解码规则是根据具体应用的需求而设计的。

比如,对于二进制码译码器,可以将二进制输入码转换为十进制、BCD码等形式的输出信号。

3. 译码器的应用译码器广泛应用于数字电路和计算机系统中,其主要应用包括但不限于以下几个方面:•数字显示:译码器可将输入的二进制码或BCD码转换为7段LED显示的数字,用于显示数字信息。

这在计算器、计时器、计数器等设备中非常常见。

•键盘扫描:译码器可用于键盘输入的编码和解码。

它可以将按键的信号编码成二进制码,或将二进制码解码成对应的按键信号。

•地址解码:在计算机系统中,译码器用于将CPU发送的地址信号解码成特定的存储单元。

这在内存控制、外设控制等方面非常重要。

•控制信号:译码器还可用于解码CPU生成的控制信号,例如时序信号、使能信号等。

这对于保证计算机系统的正常运行非常关键。

4. 译码器的分类根据其功能和应用场景的不同,译码器可以分为多种类型。

常见的译码器包括但不限于以下几种:•二进制译码器:将二进制码转换为十进制数、BCD码、7段LED数字等。

•BCD译码器:将二进制码转换为BCD码,用于驱动BCD显示器。

译码器说课稿

译码器说课稿一、引言大家好,今天我将为大家分享一篇关于译码器的说课稿。

译码器作为数字电路的重要组成部分,扮演着将数字信号转换为可读信息的关键角色。

本次课程旨在介绍译码器的基本原理、分类以及应用,并通过实例演示加深学生对译码器的理解。

希望通过本课程的学习,学生能够掌握译码器的工作原理和应用场景。

二、课程内容1. 译码器的定义和基本原理译码器是一种数字电路,用于将输入的二进制码转换为相应的输出信号。

其基本原理是根据输入码的不同组合,选择性地激活输出线路。

译码器通常由逻辑门电路组成,如与门、或门等。

2. 译码器的分类2.1 二-四译码器二-四译码器是最基本的译码器之一,其输入为两位二进制码,输出为四个输出信号之一。

通过逻辑门的组合,实现不同输入码对应不同的输出信号。

2.2 三-八译码器三-八译码器是一种更复杂的译码器,其输入为三位二进制码,输出为八个输出信号之一。

通过逻辑门的组合,实现不同输入码对应不同的输出信号。

2.3 优先级译码器优先级译码器是一种特殊的译码器,用于处理具有优先级的输入信号。

当多个输入信号同时激活时,优先级高的输入信号将被优先处理。

3. 译码器的应用3.1 数码管显示译码器常用于数码管显示,将输入的二进制码转换为对应的数码管段选信号。

通过逻辑门的组合,实现不同输入码对应不同的数码管显示。

3.2 键盘扫描译码器也可用于键盘扫描,将键盘输入的二进制码转换为对应的键盘按键信号。

通过逻辑门的组合,实现不同输入码对应不同的按键信号。

3.3 数据传输译码器还可用于数据传输,将输入的二进制码转换为对应的输出信号,实现数据的传输和处理。

4. 实例演示为了更好地理解译码器的工作原理和应用,我们将进行一次实例演示。

以二-四译码器为例,我们将通过逻辑门的组合,实现不同输入码对应不同的输出信号。

通过连接开关和LED灯,我们可以直观地观察到输入码和输出信号之间的对应关系。

五、总结通过本次课程的学习,我们了解了译码器的基本原理、分类以及应用。

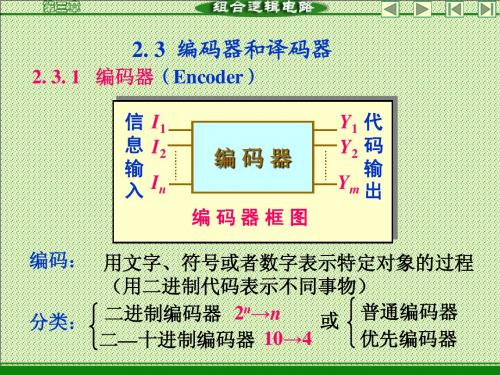

2.3编码和译码器课件

2.3.1 编码器

将信号变换为一一对应的特定代码(一般为二进制数 码)的过程称为编码。实现编码的电路称为编码器。 电路模型框图如图2-16所示。

X0

X1 …

Xn-1

编码器

Y0

… Y1 Ym-1

设有n个待编码的信号X0X1,…,Xi,…,Xn-1,有m位输出代码 Y0Y1,…,Ym-1。为了使输入、输出间建立一一对应的关系,即 一个信号一个代码,则输出的位数m,应满足下式:

1

1

(f) 10

(g)

a A3 A2 A1 A0 A2 A1 A0 A3 A2 A1 A0 A2 A1 A0

b A3 A1A0 A3 A1A0 A3 A1A0 A3 A1A0

g A3 A2 A1 A2 A1A0 A3 A2 A1 A2 A1A0

例2.11 设计一个三位二进制码输入的译码器。

解:该题属于变量译码器。因有三位输入代码,可以译成 八种事件,即经译码器后将最多产生8个控制信号,故该译 码器又称为3-8译码器。假定输出低电平有效,高电平无效, 输入变量为Z2、Z1、Z0,输出变量为X0、X1、…、X7,则做出 译码器真值表见表2-8。

m≥ log2 n

例2.10 设计一个有八个输入信号的二—十进制编码器。

解:由于,则编码位数m应为

取m=3。

m≥ log2 n

Z2 X4 X0 X1 X2 X3 X5 X6 X7 X5 X0 X1 X2 X3 X4 X6 X7

X6 X0 X1 X2 X3 X4 X5 X7 X7 X0 X1 X2 X3 X4 X5 X6

Z0 X1 X3 X5 X7

第四章-译码器

一般LED的工作电流选在5~10mA,但不允许超过最大值(通常为

50mA)。 LED可以直接由门电路驱动。

14

① 半导体发光二极管。

图(a)是输出为低电平时,LED发光,称为低电平驱动; 图(b)是输出为高电平时,LED发光,称为高电平驱动; 采用高电平驱动方式的TTL门最好选用OC门。

R为限流电阻

74HC138的功能表:

输

入

输

出

S1

S

' 2

S3'

0X

A2 A1 A0 Y7' Y6' Y5' Y4' Y3' Y2' Y1' Y0'

X XX 1 1 1 1 1 1 1 1

X 1 X XX 1 1 1 1 1 1 1 1

1 0 0 00 1 1 1 1 1 1 1 0

1 0 0 01 1 1 1 1 1 1 0 1

4

74LS138的逻辑功能 三个译码输入端(又称地址输入端)A2、

A1、A0,八个译码输出端 Y0~Y7,以及三个控制 端(又称使能端)S1、S2 、S3。

S1 、S2 ,S3 是译码器的控制输入端,当 S1 = 1、S2+ S3 = 0 (即 S1 = 1,S2 和S3 均为0)时,S 输出为高电平,译码器处于工作状态。否则,译 码器被禁止,所有的输出端被封锁在高电平。

1 0 0 10 1 1 1 1 1 0 1 1

1 0 0 11 1 1 1 1 0 1 1 1

1 0 1 00 1 1 1 0 1 1 1 1

1 0 1 01 1 1 0 1 1 1 1 1

1 0 1 10 1 0 1 1 1 1 1 1

编码器和译码器实验报告

实验报告: 编码器和译码器1. 背景在信息传输和存储过程中,编码器和译码器是两个关键的组件。

编码器将信息从一个表示形式转换成另一个表示形式,而译码器则将编码的信息还原为原始的表示形式。

编码器和译码器在各种领域中都得到广泛应用,如通信系统、数据压缩、图像处理等。

编码器和译码器可以有不同的实现方式和算法。

在本次实验中,我们将研究和实现一种常见的编码器和译码器:霍夫曼编码器和译码器。

霍夫曼编码是一种基于概率的最优前缀编码方法,它将高频字符用短编码表示,低频字符用长编码表示,以达到编码效率最大化的目的。

2. 分析2.1 霍夫曼编码器霍夫曼编码器的实现包括以下几个步骤:1.统计字符出现频率:遍历待编码的文本,统计所有字符出现的频率。

2.构建霍夫曼树:根据字符频率构建霍夫曼树。

树的叶子节点代表字符,节点的权重为字符频率。

3.生成编码表:从霍夫曼树的根节点出发,遍历树的每个节点,记录每个字符对应的编码路径。

路径的左移表示0,右移表示1。

4.编码文本:遍历待编码的文本,将每个字符根据编码表进行编码,得到编码后的二进制序列。

2.2 霍夫曼译码器霍夫曼译码器的实现包括以下几个步骤:1.构建霍夫曼树:根据编码器生成的编码表,构建霍夫曼树。

2.译码二进制序列:根据霍夫曼树和待译码的二进制序列,从根节点开始遍历每个二进制位。

当遇到叶子节点时,将对应的字符输出,并从根节点重新开始遍历。

3.重建原始文本:将译码得到的字符逐个组合,得到原始的文本。

3. 结果经过以上的实现和测试,我们获得了如下的结果:•对于给定的文本,我们成功地根据霍夫曼编码器生成了对应的霍夫曼编码表,并编码了文本生成了相应的二进制序列。

•对于给定的二进制序列,我们成功地根据霍夫曼译码器进行了译码,并将译码得到的字符逐个组合,得到了原始的文本。

实验结果显示,霍夫曼编码器和译码器能够有效地将文本进行压缩和恢复,达到了编码效率最大化和数据传输压缩的目的。

编码后的文本长度大大减小,而译码后的原始文本与编码前几乎完全一致。

3-2.3编码器 译码器资料

Y3 Y2 Y1 Y0 1 1 1 1 无输入 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0

小结 普通编码器:任何时刻只允许输入 一个编码信号 编码器分 优先编码器:任何时刻允许同时输入 若干个编码信号,但只 对优先权最高的一个进 行编码 要求 掌握两种编码器的特点,会看功能表

G1G2AG2B A2 A1 A0

输出 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0

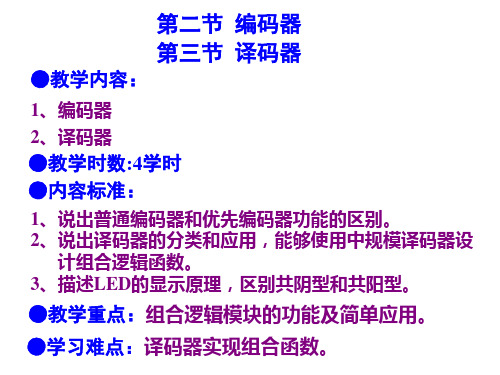

第二节 编码器 第三节 译码器

●教学内容:

1、编码器 2、译码器

●教学时数:4学时 ●内容标准:

1、说出普通编码器和优先编码器功能的区别。 2、说出译码器的分类和应用,能够使用中规模译码器设 计组合逻辑函数。 3、描述LED的显示原理,区别共阴型和共阳型。

●教学重点:组合逻辑模块的功能及简单应用。 ●学习难点:译码器实现组合函数。

Y2 Y1 Y0 1 1 1 1 1 1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

YS 1 0 1 1 1 1 1 1 1 1

YEX 1 无输出 1 无输入 0 0 0 0 0 0 0 0

例3-3 试用两片74LS148接成16线-4线优先编码器, 将A0~A1516个电平输入信号编为0000~111116个四 位二进制代码.其中A15的优先权最高.

含两个2-4译码器的74HC139芯片版图

集成电路课程设计1. 目的与任务本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。

2. 设计题目与要求2.1设计题目及其性能指标要求器件名称:含两个2-4译码器的74HC139芯片 要求电路性能指标:(1) 可驱动10个LSTTL 电路(相当于15pF 电容负载); (2) 输出高电平时,|I OH |≤20μA ,V OH ,min =4.4V ; (3) 输出底电平时,|I OL |≤4mA ,V OL ,man =0.4V ; (4) 输出级充放电时间t r =t f ,t pd <25ns ;(5) 工作电源5V ,常温工作,工作频率f work =30MHz ,总功耗P max =150mW 。

2.2设计要求1. 独立完成设计74HC139芯片的全过程;2. 设计时使用的工艺及设计规则: MOSIS:mhp_n12;3. 根据所用的工艺,选取合理的模型库;4. 选用以lambda(λ)为单位的设计规则;5. 全手工、层次化设计版图;6. 达到指导书提出的设计指标要求。

3. 设计方法与计算 3.1 74HC139芯片简介74HC139是包含两个2线-4线译码器的高速CMOS 数字电路集成芯片,能与TTL 集成电路芯片兼容,它的管脚图如图1所示,其逻辑真值表如表1所示:图1 74HC139芯片管脚图 表1 74HC139真值表计时只需分析其中一个2—4译码器即可,从真值表我们可以得出Cs 为片选端,当其为0时,芯片正常工作,当其为1时,芯片封锁。

A1、A0为输入端,Y0-Y3为输出端,而且是低电平有效。

2—4译码器的逻辑表达式,如下所示:01010A A C A A C Y s s ⋅⋅=++= 01011A A C A A C Y s s ⋅⋅=++=01012A A C A A C Y s s ⋅⋅=++= 01013A A C A A C Y s s ⋅⋅=++=74HC139的逻辑图如图2所示:图2 74HC139逻辑图3.2 电路设计本次设计采用的是m12_20的模型库参数进行各级电路的尺寸计算,其参数如下: NMOS: εox =3.9×8.85×10﹣12F/m μn =605.312×10﹣4㎡/Vst ox =395×10﹣10m V tn =0.81056V PMOS: εox =3.9×8.85×10﹣12F/m μp =219×10﹣4㎡/Vst ox =395×10﹣10m V tp =﹣0.971428V 3.2.1 输出级电路设计根据要求输出级电路等效电路图如图3所示,输入Vi 为前一级的输出,可认为是理想的输出,即V IL =Vss, V IH =V DD 。

CH33-2.3 编码器和译码器

A1

A2

A3

驱动共阳极数码管的电路 — 输出低电平有效 输出低电平 低电平有效

Ya

&

& & &

Yb

&

&

Yc1Biblioteka & &Yd

&

& &

Ye

&

& &

Yf

&

& & &

Yg

&

&

1

1

1

1

A0

A1

A2

A3

五、 用二进制译码器实现组合逻辑函数 1. 基本原理:二进制译码器又叫变量译码器或最小项 基本原理:

译码器,它的输出端提供了其输入变量的 译码器 它的输出端提供了其输入变量的 它的 全部最小项。 全部最小项。

Y0 = I1 + I3 + I5 + I7 = I1 ⋅ I3 ⋅ I5 ⋅ I7

逻辑图 Y2

— 用或门实现 或门实现 Y1 Y0

— 用与非门实现 与非门实现 Y2 Y1 Y0

≥1

≥1

≥1

&

&

&

I7 I6 I5 I4

I3 I2

I1 I0

I7 I6 I5 I4

I3 I2

I1I0

2. 3 位二进制优先编码器 允许几个信号同时输入,但只对优先级别 允许几个信号同时输入, 优先编码: 优先编码: 最高的进行编码。优先顺序:I7 → I0 最高的进行编码。优先顺序:

A2 A 1

A0

1M*8 bit

1111

A0

2-4译码器原理

2-4译码器原理摘要:1.2-4 译码器的概念2.2-4 译码器的工作原理a.二进制到四进制编码b.译码器的设计与实现c.2-4 译码器的应用场景3.2-4 译码器的优缺点分析4.2-4 译码器的发展趋势与展望正文:2-4 译码器是一种将二进制信号转换为四进制信号的设备,它在数字通信、计算机科学等领域具有广泛的应用。

本文将详细介绍2-4 译码器的原理、工作方式以及应用场景,并对其优缺点进行分析,展望未来的发展趋势。

首先,我们需要了解2-4 译码器的概念。

在数字通信中,信息的传输和处理通常采用二进制编码系统,但由于二进制系统只有两种状态,往往不能满足实际应用中的需求。

因此,研究人员提出了将二进制信号转换为四进制信号的方法,即2-4 译码器。

通过使用2-4 译码器,可以有效提高信息传输的效率和可靠性。

接下来,我们来探讨2-4 译码器的工作原理。

首先,二进制到四进制编码是译码器的核心功能。

在这个过程中,需要将二进制信号与特定的编码规则对应起来,从而实现二进制到四进制的转换。

其次,译码器的设计与实现是关键步骤。

为了完成高效的译码任务,需要设计合适的译码器结构,以满足不同应用场景的需求。

目前,已有多种类型的2-4 译码器实现方案,如基于查找表的译码器、基于阵列处理的译码器等。

在了解了2-4 译码器的工作原理之后,我们来探讨一下它的应用场景。

2-4 译码器广泛应用于数字通信、计算机科学等领域,其中最典型的应用是四电平脉冲幅度调制(PAM-4)系统。

在PAM-4 系统中,采用2-4 译码器将二进制信号转换为四进制信号,从而实现更高的传输速率和更长的传输距离。

此外,2-4 译码器还在其他领域发挥着重要作用,如数字信号处理、图像处理等。

当然,2-4 译码器也存在一些优缺点。

优点主要表现在它能提高信息传输的效率和可靠性,使得数字通信系统具有更好的性能。

而缺点则主要体现在设计和实现过程中可能遇到的挑战,如译码器结构的复杂性、译码误差的产生等。

数字电子技术译码器2.

A0

A1 A2 A3

(b) 逻辑功能示意图

输出为反变量,即为低电平有效, 并且采用完全译码方案。

3.5.3 显示译码器

用来驱动各种显示器件,从而将用二进制代码表示 的数字、文字、符号翻译成人们习惯的形式直观地显示 出来的电路,称为显示译码器。

1、数码显示器

ab cd

a

f

b

g

e

c

d

ef gh (a) 外形图

STC

Y7

&

Si

&

Ci

2、用二进制译码器实现码制变换

8

A0

4

A1

1

A2

码

A3

Y0

Y1

Y2

十

Y3 Y4

进

Y5

制

Y6

码

Y7

Y8

Y9

Y10

Y11

Y12

Y13

Y14

Y15

A0

余

A1

3

码

A2

A3

Y0

Y1

Y2

Y3

Y4

Y5

十

Y6 Y7

进

Y8

制

Y9

码

Y10

Y11

Y12

Y13

Y14

Y15

2

A0

4

A1

2

1

A2

码

辅助端功能

由真值表可以看出,为了增强器件的功能,在 74LS48 中还设置了 一些辅助端。这些辅助端的功能如下:

(1)试灯输入端 LT :低电平有效。当LT =0 时,数码管的七段

应全亮,与输入的译码信号无关。本输入端用于测试数码管的好坏。

02-3.3 集成译码器

0100

0101

8

0110

9

10

0111

11 12

1000

13

1001

14

15

1010

1011

1100

1101

1110

1111

用译码器实现组合逻辑函数

2. 显示译码器 LED字形显示器

fg ab

a fb

g e dc

•

ed c•

LED连接方式 七段数字显示器分为共阴极和共阳极两种。

+ + + ++ •

a

b

c

d

e

f

g

注意

共阴极接法

a b c d e f g

共阳极接法

•

+VCC

若采用共阳极LED,显示译码器的输出应为 低电平输出有效;若采用共阴极LED,则高 电平输出有效。

A3 A2 A1 A0

Ya Yb Yc Yd Ye Yf Yg

十进制

字

00 00

11111 1 0

0

0

00 01

01100 0 0

Y 0 B2 B1 B0 Y 1 B2 B1B0 Y 2 B2B1 B0 Y3 B2B1B0

Y 4 B2 B1 B0 Y 5 B2 B1B0 Y 6 B2B1 B0 Y 7 B2 B1B0

Y 7Y 6 Y 5Y 4 Y 3 Y 2 Y1 Y 0

74LS138

B2 B1 B0 S1 S 2 S 3

BCD-七段显示译码器74LS48的逻辑图

常用显示译码器

7447(低电平输出有效) 7449(高电平输出有效) 7448(高电平输出有效

数字逻辑课件——译码器

图3-3-10 4线-7线译码器/驱动 器7448逻辑符号

28

用7448驱动BS201A的基本接法如图3-3-11(a)所 示。当B3B2B1B0 输入0000~1111这16种不同信 号时,相应的显示字形如图3-3-11(b)所示。

图3-3-11 7448驱动BS201A

29

接线时务必防止将+5V直接与a~g段输入短接,否则 会烧毁PN结,用7448的输出Ya~Yg驱动BS201A的段输 入则没有这种危险,这是因为Ya~Yg为集电极开路输

19

常用的半导体数码管、液晶显示器及其BCD – 七段显示 译码器。 4. 半导体数码管 半导体数码管是分段式半导体显示器件,其基本结构为 PN结,一些特殊半导体材料作成的PN结具有这样的性质: 当外加正向偏压时,P区的多数载流子空穴流向N区,N区 的多数载流子电子流向P区,而少数载流子注入PN结与多 数载流子复合,在这个过程中会发出一定波长的光束。

e

c

d

27

配合半导体数码管BS201A工作的4线 — 7线译码 器/驱动器7448 (1)7448的逻辑功能

7448的逻辑符号如图3-3-10所示,其功能如表3-3-7,

它的基本输入信号是 四位二进制数(也可 以是8421BCD码)A3, A2,A1,A0,

基本输出端有7个: Ya,Yb,Yc,Yd,Ye, Yf,Yg。

出结构,并已有上拉电阻2kΩ。

在7448中,除了上述基本输入端和基本输出端 外,还有几个辅助输入、输出端:

(1)灯测试输入(LT ); (2)灭零输入(RBI ); (3)灭灯输入/灭零输出 (BI / RBO) : 这个端钮 比较特殊,它既可作输入用,也可作输出用。

30

4线-7线译码器/驱动器7448功能表

译码器及其应用课件

地址解码

用于计算机内存、外设接口等 地址解码。

显示驱动

用于LED、LCD等显示设备的 驱动控制。

数据分配

用于多路复用、多路选择等数 据分配场景。

扩展接口

用于扩展微控制器、微处理器 等芯片的I/O接口。

02 常见译码器类型介绍

二进制译码器

总结词

二进制译码器是一种常见的数字逻辑 电路,用于将输入的二进制代码转换 为相应的输出信号。

技术标准与规范

由于译码器技术的多样性和复杂性,需要制定统一的技术标准和规 范,以促进技术的普及和发展。

技术人才短缺

随着译码器的快速发展,技术人才短缺问题逐渐凸显。需要加强人才 培养和技术交流,提高技术人员的素质和能力。

THANKS

译码器及其应用课件

目录

CONTENTS

• 译码器概述 • 常见译码器类型介绍 • 译码器在电路设计中的应用 • 译码器的实际应用案例 • 译码器的未来发展趋势与挑战

01 译码器概述

译码器的定义与工作原理

译码器的定义

译码器是一种组合逻辑电路,能 够将输入的二进制代码翻译成相 应的输出信号。

工作原理

语音识别和文本生成等。

智能决策

译码器可以帮助人工智能系统进行 智能决策,通过对大量数据的分析 和处理,快速准确地得出最优解。

智能控制

在智能制造、智能家居等领域,译 码器可以用于实现智能控制,提高 设备的自动化和智能化水平。

译码器面临的挑战与解决方案

数据安全与隐私保护

随着译码器的广泛应用,数据安全和隐私保护成为了一个重要的问 题。需要采取有效的加密和安全措施来保护用户数据和隐私。

应用场景

优先级译码器在计算机、数字通信、 电子测量等领域有广泛应用,例如用 于中断处理、任务调度等。

第二章组合逻辑电路分析-含动画

普通编码器对输入信号的要求是互相排斥,优先编码器无此约束 允许多个信号同时输入,但电路只对优先级别最高的信号进行编码 【例2-6】3位二进制优先编码器的设计。 解:(1)分析设计要求

8个输入信号(I0~I7) 3个输出信号(Y2~Y0) 编码规则:用000、001、010、011、100、101、

2. 4选1数据选择器

【例2-9】4选1数据选择器的设计。 解:(1)分析设计要求 4路数 据输 入信号 (D0、D1、D2、D3) 1路输出信号(Y) 2位选择控制信号(S1、S0) S1S0=00时,Y=D0; S1S0=01时,Y=D1; S1S0=10时,Y=D2; S1S0=11时,Y=D3。

一个N×N的乘法器,有两个N位的乘数输入端及2N位乘积输出。

2.2.6 乘法器

2.乘法器的实现

以 4 × 4 乘 法 器 为 例 , 乘 法 器 的 输 入 信 号 为 被 乘 数 A(A3A2A1A0) 及 乘 数 B (B3B2B1B0),输出为乘积P(P7~P0)。

部分积的计算可通过与门(AND)实现 若要将部分积移位相加,还需要3个4位加法器进行加法运算

2.2 常用的组合逻辑电路

编码器 译码器 数据选择器 数值比较器 加法器 乘法器

2.2.1 编码器

1.编码原理

编码是指用文字、符号或数字表示特定对象的过程 编码器就是实现编码操作的电路 编码器的结构框图:

I0~Im-1对应m个需要编码的输入信号 Yn-1~Y0对应n位的编码输出 为了保证每一个输入信号都对应一个唯一的编码,n和m之间的关系 应满足关系式 2n-1<m≤2n 设计编码器关键在于编码规则,编码规则不同,设计的结果也完全不同

2.2.5 加法器

数字电子技术-译码器-

Y1

Y2

Y3

Y4

Y5

Y6

Y7

m0

m1

m2

m3

m4

m5

m6

m7

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

1

0

0

Yi 0 mi (i 0 0,1,2,

0 7)

7

1. 74LS138的逻辑功

能

内部

电路图

负逻辑

与非门

S为控制端

(又称使能端)

S=1 译码工作

S=0 禁止译码,

ഥ 都与某一个

辑函数的输入变量(ABC),译码器的每个输出端

最小项mi相对应,加上适当的门电路,就可以利用译码器实现组

合逻辑函数。

15

例2-4 试用74LS138译码器实现逻辑函数:

F ( A, B, C) m(1,3,5,6,7)

解:

F ( A, B, C ) m (1,3,5,6,7)

译码器

复习

问(Q):

班里有40名学生,如果编码需要几位二进制数?

A.2

E.40

B.4

C.6

D.10

答:C

25=32<40<26=64

2

问(Q):优先权最高的输入信号是?

复习

输出是

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.二进制译码器

2.二-十进制译码器

3.显示译码器

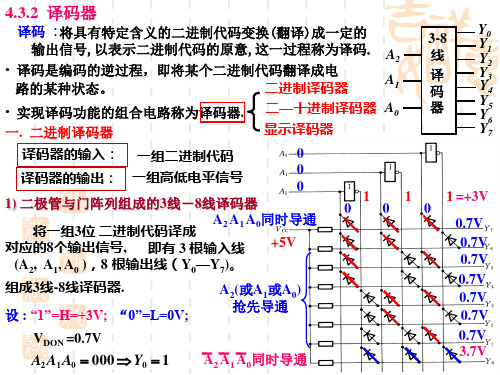

2.2.3译码器

译码是编码的逆过程。将输入的代码翻译成相应的输出信号的 电路就是译码器。常用的译码器有二进制译码器、二-十进制译码 器、显示译码器。 1.二进制译码器 将输入的二进制代码转换成相对应的输出信号的电路,为二 进制译码器。若输入的二进制代码有n个,则输出端的信号为 2n 个。 其主要特点有以下3个: ①二进制译码器一般具有n个输入端、 个输出端和一个(或多个)使能输入端。 ② 在使能输入端为有效电平时,对应每一组输入代码,仅一个输 出端为有效电平,其余输出端为无效电平(与有效电平相反)。 ③有效电平可以是高电平(称为高电平译码),也可以是低电平(称 为低电平译码)。

3.显示译码器

(a)七段数字显示器外形图

(b) 发光段组合图 图2-10 七段数码管字形显示方式

3.显示译码器

按连接方式的不同,LED数码管连接方式有共阳极和共阴 极连接两种方式,如图2-11所示。

(a)共阴极结构图

(b)共阳极结构图

3.显示译码器

LED工作电压较低,工作电流也不大,可以直接用七段显 示译码器来驱动。LED的连接方式不一样,其驱动方式也不 同。对共阴型LED数码管,应采用高电平驱动方式;对共阳 型LED数码管,应采用低电平驱动方式。 2)七段显示译码器74LS48 七段显示译码器74LS48是一种用来驱动共阴型LED数码 管的电路,它把输入的4位二进制代码翻译成驱动七段LED 数码管各对应段所需的电平,其引脚图如图2-12所示。输 入 A3 A2 A1 A0 接收四位二进制码,输出a~g高电平有效,另 外有3个控制端:试灯输入端 LT 、灭零输入端 RBI 、特殊控 制端 BI / RBO 用来增强器件的功能。其逻辑功能表如表2-8所示。

3.显示译码器

从功能表可以看出,对输入代码0000,译码条件是:试 灯输入端 LT 和灭零输入端 RBI ,同时等于1,而对其他输入 代码则仅要求 BI / RBO =1,这时候,译码器各段a~g输出的 电平是由输入代码决定的,并且满足显示字形的要求。

3.显示译码器

3.显示译码器

2.二-十21BCD码,输出端“译中” 时为低电平。8421BCD码以外的称为伪码,当输入伪码 时,所有输出端均为高电平,即拒绝伪码输入。

3.显示译码器

在数字系统中,常常需要将某些数据或运算结果显示出 来,一方面供人们直接读出处理的结果,另一方面用来监视 数字系统的工作情况。这些数字量要先经过译码,才能送到 数字显示器去显示。这种将数字量翻译成数字显示器所能识 别的信号的译码器称为数字显示译码器,数字显示译码器通 常由译码器、驱动器和显示器等部分组成。 数码显示器又称数码管,是用来显示数字、文字或符号 的器件。常见的显示方式有:字形重叠式(如辉光放电管、 边光显示管)、分段式(荧光数码管、LED七段数码管、液 晶数码管)、点矩阵式(场致发光记分牌、大屏幕显示)等。

1.二进制译码器

常见的二进制译码器有2-4线(2输入-4输出)译码器、3-8 线(3输入-8输出)译码器和4-16线(4输入-16输出)译码器等。 图2-87所示分别是T4138型3-8线译码器的管脚排列图和逻 辑符号。

1.二进制译码器

1.二进制译码器

2.二-十进制译码器

二-十进制译码器又称为8421 BCD码译码器,是把二-十 进制代码翻译成10个十进制数字信号的电路。

3.显示译码器

数码显示器有半导体显示器、荧光数字显示器、液体数 字显示器和气体放电显示器多种类型,目前广泛使用的是七 段数码显示器(简称七段数码管),主要包括发光二极管 (LED)数码管和液晶显示(LCD)数码管两种。 1)LED数码管 LED数码管是由7个LED(加小数点为8个)按分段式封 装制成的,亮度较高,颜色多样,应用广泛。七段a,b, c,d,e,f,g(小数点dp)各对应一个发光二极管,利用 发光字段的组合来显示不同的阿拉伯数字,如图2-10所示。