FPGA—MicroBlaze—跑马灯

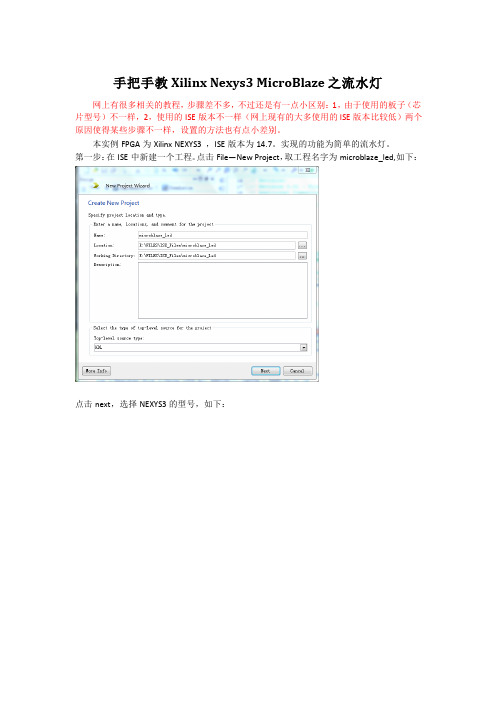

流水灯 microblaze

展开 clock_generator_0,在 CLKIN 一栏右击选择“New Connection”,并再次右击并选择“Make External”,如下:

然后再点击 External Ports 中,需要依次右击 CLK_N,CLK_P 并选择“Delete External Ports”便 可将其删除。结果如下:

return 0; }

接着右键单击 led_application 并选择 Builder Project 对该软件工程进行编译。接着配置产生 可在线烧录的.bit 文件,这个.bit 文件将包括硬件工程生成的.bit 文件和软件工程烧录文件.elf。 在 XPS 的菜单栏选择 Xilinx Tools--Program FPGA,Program FPGA 的配置如下图所示,Bitstream 中选择硬件生成的配置文件 cpu_sys_top.bit,一般就在工程目录下;BMM File 中选择硬件系 统文件 edkBmmFile_bd.bmm,也在工程目录 下;最后在 Software Configuration 下点击 ELF File to Initialize in Block RAM 的下拉条找到 example_application_0.elf 即软件工程的烧录文件。

点击“AddLeabharlann Device…”按钮后出现如下界面,由于是 led,故做如下选择:(分别设置“IO Interface Type”为“GPIO”、“Device”为“LEDS”,完成后点击“OK”。)

点击 OK。最后配置结果如下:

然后点击 finish。稍等一段时间,等待新系统生成。 然后出现如下界面:

接下来就可以用 C 编写代码。 (1) 新建一个工程:点击 Application Project。

MicroBlaze软核的液晶驱动程序设计

基于MicroBlaze软核的液晶驱动程序设计(1)1 MicroBlaze的体系结构MicroBlaze采用功能强大的32位流水线结构,包含32个32位通用寄存器和1个可选的32位移位器,时钟频率可达150 MHz;在Virrex一4 FPGA上运行速率高达120 DMIPS,仅占用Virtex—II Pro FPGA中的950个逻辑单元。

MicroBlaze软核的结构框图如图1所示。

它具有以下基本特征:①32个32位通用寄存器和2个专用寄存器(程序计数器和状态标志寄存器)。

②32位指令系统,支持3个操作数和2种寻址方式。

③分离的32位指令和数据总线,符合IBM的OPB总线规范(与外设相连接的低速总线)。

④通过本地存储器总线(LMB,本地高速总线)直接访问片内块存储器(BRAM)。

⑤具有高速的指令和数据缓存(cache),三级流水线结构(取址、译码、执行)。

⑥具有硬件调试模块(MDM)。

⑦带8个输入和8个输出快速链路接口(FSL)。

图中接口信号说明如下:①DOPB,器件内部的外围设备数据接口总线,用于处理器与片内的设备进行数据交换。

②DLMB,实现数据交换的本地块存储器总线。

该总线为处理器内核与块存储器(BRAM)之间提供专用的高速数据交换通道。

③IOPB,用于实现外部程序存储器的总线接口。

当程序较大时,需要外接大容量的存储器。

该总线提供读取指令的通道。

④ILMB,用于取指令的本地存储器总线。

该总线与器件内部的块存储器(BRAM)相连,实现高速的指令读取。

⑤MFSLO~7,主设备数据接口,提供点对点的通信通道。

⑥SFSLO~7,从设备数据接口,提供点对点的通信通道。

2 MicroBlaze嵌入式开发工具EDKXilinx公司提供了完善的嵌入式开发工具EDK(Em—bedded Development Kit)。

EDK是Xilinx公司于2003年推出的SOPC(System On Programmable Chip)系统开发套件。

利用MicroBlaze除错模块实现FPGA嵌入式处理器的除错

利用MicroBlaze除错模块实现FPGA嵌入式处理器的除错目前,越来越多的FPGA设计开始采用嵌入式处理器,如PowerPC和赛灵思(Xilinx)的MicroBlaze处理器来完成控制任务,采用C语言等软件语言描述这些控制任务,要比使用VHDL或Verilog等硬件语言描述更加容易。

当进行嵌入式系统设计时,绝大部份的设计时间可能花费在除错阶段,因此缩短发现问题并解决问题的时间非常重要。

作为一款整合除错器,Computex公司的F-Sight同时具备硬件和软件除错能力。

一方面,它支持FPGA内部嵌入式处理器的全方位软件除错。

另一方面,它还支持监视FPGA硬件讯号。

本文将介绍如何利用F-Sight提高除错效率。

启动除错器Computex公司的除错器非常适合用来实现FPGA内部嵌入式处理器的除错。

对于MicroBlaze处理器来说,工程师可以利用MicroBlaze除错模块(MDM)控制处理器的执行过程并进行除错,也可以利用赛灵思公司的MicroBlaze追踪核心(XMTC)以非侵入方式监控处理器程序的执行情况。

由于FPGA的接脚限制,减少输出到接脚的讯号数量非常重要。

XMTC提供了编码指令和数据追踪功能,所需要的接脚数量仅为非编码讯号所需的10%。

为了使除错器实现追踪功能,只需要将MDM和XMTC核心分别连接到MicroBlaze处理器的除错和追踪接口,然后将编码后的追踪讯号引到FPGA接脚以便F-Sight收集数据。

完成FPGA设计后,再将F-Sight除错器连接到电路板的Mictor连接器。

如果使用赛灵思不带Mictor连接器的ML400系列、ML500系列或Sparta-3E/3A/3AN FPGA板,那么在Computex F-Sight配接器帮助下仍可以使用F-Sight中的处理器追踪功能。

图1是利用F-Sight配接器将F-Sight连接到Spartan-3板上的照片。

图1:F-Sight透过配接器连接到Spartan-3电路板。

Xilinx FPGA的嵌入式系统开发过程

Xilinx FPGA的嵌入式系统开发过程由创新网小编于星期四, 01/10/2013 - 11:03 发表随着FPGA 技术的迅速发展,可编程片上系统(SOPC)作为一种特殊的嵌入式微处理器系统,融合了SoC和FPGA 各自的优点,并具备软硬件在系统可编程、可裁减、可扩充、可升级的功能,已逐渐成为一个新兴的技术方向。

SOPC的核心是在FPGA上实现的嵌入式微处理器核,目前主要有Xilinx公司集成的32位软核MicroBlaze[1] ,32位PowerPC系列处理器硬核PowerPC405、PowerPC440,ARM公司的CortexA9,以及Altera公司的Nios系列微处理器软核等。

本文主要介绍Xilinx公司的MicroBlaze 软核结构,对其体系结构、设计流程和相关开发工具一一进行介绍,并在实际的无线电监测系统[2]中采用此方案,构建了一个小型化、智能化、网络化的软件无线电处理平台。

1 MicroBlaze处理器结构MicroBlaze软核处理器是可配置的精简指令集(RISC)32位CPU,该RISC核针对Xilinx公司的FPGA芯片进行了优化。

设计人员可以根据设计定制处理器的可选配置,根据版本的不同,配置不同的选项。

该软核处理器具有以下几个方面的特征:◆32个32位通用寄存器;◆32位3个操作数的指令字,指令字有2种寻址模式;◆分离的32位地址总线和数据总线;◆具有高速的指令和数据缓存,3级和5级流水线操作;◆灵活的总线结构,支持LMB、OPB、PLB、XCL、FSL片上总线接口等,新推出的系列还支持AXI总线接口;◆支持MMU存储管理、FPU浮点单元、高速缓存、异常处理和调试逻辑等可根据性能需求和逻辑区域成本任意裁减的高级特性。

MicroBlaze的这些特性极大地扩展了其应用范围,MicroBlaze处理器的内核仍在不断更新之中,目前使用的版本MicroBlaze v7.1,其内部架构如图1所示。

FPGA入门实验教程 适合初学者

艾米电子工作室—让开发变得更简单FPGA 入门系列实验教程——点亮LED1. 实验任务点亮发光二极管。

通过这个实验,熟悉并掌握CPLD/FPGA 开发软件QuartusII 的使用方法和开发流程以及Verilog HDL的编程方法。

2. 实验环境硬件实验环境为艾米电子工作室型号EP2C5T144 开发套件。

软件实验环境为Quartus II 8.1 开发软件。

3. 实验原理FPGA 器件同单片机一样,为用户提供了许多灵活的独立的输入/输出I/O 口(单元)。

FPGA 每个I/O 口可以配置为输入、输出、双向、集电极开路和三态门等各种组态。

作为输出口时,FPGA 的I/O 口可以吸收最大为24mA 的电流,可以直接驱动发光二极管LED 等器件。

图1. 1 为8 个发光二极管硬件原理图,本原理图对应艾米电子工作室型号为EP2C5T144 FPGA 开发板及接口板。

通过原理图可知如果要点亮这八个LED,所以只要正确分配并锁定引脚后,在相应的引脚上输出相应高电平“1”,就可实现点亮该发光二极管的功能。

本工作室开发板均采用输出“1”点亮LED 的模式,以后就不再另作说明。

图1. 1 发光二极管LED 硬件原理图艾米电子工作室—让开发变得更简单FPGA 入门系列实验教程——LED 闪烁灯1. 实验任务让实验板上的8 个LED 周期性的闪烁。

通过这个实验,熟悉并掌握采用计数与判断的方式来实现分频的Verilog HDL 的编程方法以及Quartus II 软件的使用方法和开发流程。

2. 实验环境硬件实验环境为艾米电子工作室型号EP2C8Q208 增强版开发套件。

软件实验环境为Quartus II 8.1 开发软件。

3. 实验原理艾米电子工作室开发套件板载50MHz 的时钟源,假如我们直接把它输入到发光二极管LED,由于人眼的延迟性,我们将无法看到LED 闪烁,认为它一直亮着。

如果我们期望看到闪烁灯,就需要将时钟源的频率降低后再输出。

vivado入门教程-峰哥版

Xilinx zynq 7010clg400-1 sopc 基于zybo开发板之gpio使用Vivado 2015.4SDK 2015.4魏如峰2016年6月7日20:10:33目录Vivado 搭建底层硬件系统 (4)二、sdk使用 (26)三、总结 (38)附录程序 (38)Vivado 搭建底层硬件系统首先使用vivado搭建一个底层硬件系统,具体操作过程如下,用图的方式来说明,直观方便打开vivado 2015.4 如下单击create new project,如下图,单击next继续单击next,如下如,解释一下1:工程的名字2:工程在电脑中的位置,不要中文,不要空格3:打上勾表示在2的位置基础上创建一个子目录,不勾就表示不创建,我一般都是按大类来分,比如米尔的文件夹,zingsk的文件夹,zybo的文件夹,所以我都勾上,我的位置如下图设置好了之后继续单击next,这里是说创建一个什么养的工程一般都是rtl的工程,其他的我还没研究过,直接看官方文档学的,做fpga或者soc,sopc,都是rtl工程。

这里也有个可以勾选的地方,勾上的意思是现在不指定源文件,如果不够上,就进入具体设置,有硬件语言的类型,ip的选择,and so on ,可以自己去看看,建议勾选,这些可以在工程中设置的,没有必要提前设置单击next这里面可选的就很多了,从上到下,从左到右简单的说下Part和board分别指的是单个芯片和官方或者安富利的板子下面的这些是指fpga的类和速度和温度,左后的search,是你之前用过的芯片的记录或者直接收你想要的芯片名字,第一次选好,以后直接到search中选就行这个是zybo的板子的芯片型号,或者在board中直接选zybo,继续单击next,一个summary继续单击next,vivado给咱们创建工程创建好了就是这个样子,一个空的工程接下来我们要建立一个空的图片,用来搭建zynq的底层,单击箭头指的地方会出现下图这样这个表示设计的名字和存储的路径,一般都是系统,我习惯于功能加系统的方式命名,比如这次是对gpio进行操作,我会做gpio_sys,然后单击ok接下来我们来添加zynq的ps,单击,或者单击,再或者crtl + I出现这个图我们在search这输入zynq,选择第一个,单击左键或者回车,都行,下面的那个好像是microblaze,没用过,以后再研究,好像类似于nios(这块我不确定,可以忽略不记)完了是这个样子的双击zynq如图,配置zynq,这里是重点,详细说起来很多,可以参考ug585,我现在也没有全搞明白,也是觉得哪里不对去文档里找,那个文档1800多页,细读完了一定会忘,不如用哪看哪(个人观点)配置完是这样单击run block automtian完了是这样的,把ddr和fix——io引出来了接下来就是本文重点,开始添加gpio的ip双击配置gpio的ip,简单改一下ip的位宽,单击ok然后直接单击如图然后在导航栏,点source右键gpio_sys单击create hdl wapper单击ok上面的那个是手动,后面让eda自动updata,选下面的就好,单击ok在左侧的导航栏中,单击箭头指的位置生成一些ip的约束,单击genrate等一会单击ok,然后编译,等着如果之前忘了保存,这时候会弹出保存的,选save一段漫长的等待之后,分配管教,指定电平水平LMOS33 然后这样,先不要综合,没有分配管教在这点这个然后在这选layout然后选ioplane单击之后如下图分配完了,ctrl + s 点ok设置一个名字可以叫pin_location然后综合然后生成bit文件这个bit文件可以生成,也可以不生成,取决于有没有pl,有的话就要生成bit文件这两个过程很长时间!!!!!!!最后好了单击okVivado的工作要完成了,就剩最后两步File –》export export hardware如下图单击ok最后file –》lanch sdk,vivado的工作就完成了二、sdk使用File—》new—》baord suport package默认选项就行单击finish如下图,再单击finish左边多了一个bsp的文件夹在这里有我们想要用的函数和一些参数信息今天这个是gpio的,主要这个两个函数头文件再建一个应用工程然后起名子,短则刚才建立bsp生成的bsp Next,选helloword工程单击finish多了一个工程接下来就可以写程序了展开这个gpio的工程打开如图接下来我们先写程序,要讲三个函数1.gpio初始化函数2.gpio数据方向设置函数3.gpio写数据函数有关gpio大概有十二三个函数,在bsp→include→xgpio.h下,在crtl+左键,进入xgpio.c 讲的很详细,不过是英语的,如图这是讲初始化函数的我先说这几个参数什么意思,再说怎么用首先int Xgpio_Initialize(Gpio*inr,u16 DeviceID);这个函数是有返回值的,返回一个int型,0和1其中0:XST_SUCCESS,1:XTS_DEVICE_NOT_FOUND写程序的时候可以直接判断一个变量比如if(a == XST_SUCCESS or XTS_DEVICE_NOT_FOUND ){}或者if(a==0 or 1){}前面的指针变量是指向某个gpio的,该gpio在xilinx中被定义为Xgpio类型的变量,后面的device id 表示你要初始化的具体的gpio,这个id在bsp→include→xparameters.h下,比如在这里可以对这些代码进行更改,如果觉得名字太长的话。

EDA实验一:流水灯与跑马灯

准备工作注意事项:先听老师进行讲解,然后才可以进行后面的操作。

①先进行软件破解。

破解方法可参考附件《QuartusII的奇幻漂流_v1.0》的第11-13页。

其中“licence.dat”文件在“C:\altera91\91”下,将“licence.dat”文件用记事本打开,将本电脑的网卡Mac地址去替换“HOSTID”后面的那一段,保存。

然后在quartus II菜单栏“tools”-“license setup”里把修改后的license.dat 挂上,即完成破解。

详细方法请听现场老师讲解。

(在破解之前先不要把USB-blaster数据线接到电脑上)②在插拔JTAG数据线的时候,必须保证实验箱的电源是关闭的。

如果通电时进行插拔JTAG数据线,极易损坏JTAG口。

如果不按要求操作造成设备损坏的,学生本人照价赔偿。

③驱动程序的安装。

将USB-blaster数据线接到电脑上,电脑会提示安装驱动,具体的安装方法可参考附件《QuartusII的奇幻漂流_v1.0》的第14-18页,也可听老师现场讲解。

④驱动安装好后,在保证实验箱电源是关闭的情况下,将USB-blaster数据线的JTAG接口连接到实验箱上的JTAG接口上。

连接无误后,再打开实验箱电源。

至此,准备工作就绪。

实验一流水灯与跑马灯一、实验目的1、通过一个简单的流水灯和跑马灯实验,掌握时序电路的设计方法;2、初步了解QUARTUS II 的使用全过程;3、熟悉实验箱的使用流程。

二、实验原理本实验实现的是让实验箱上的4个LED灯实现流水灯和跑马灯功能。

流水灯,就是让LED灯像流水一样地点亮。

如果把流水做慢动作播放,可以想象到其实就是移动,即:水块不断地向同一方向移动,而原来的水块保持不动,就形成了流水。

同样,如果使得最左边的灯先亮,然后,通过移位,在其右侧的灯,由左向右依次点亮,而已经亮的灯又不灭,便形成了向右的流水灯。

而当4个灯都点亮时,需要一个操作使得所有的灯恢复为初始状态,即灯都不亮。

基于MicroBlaze的FPGA重配置系统设计

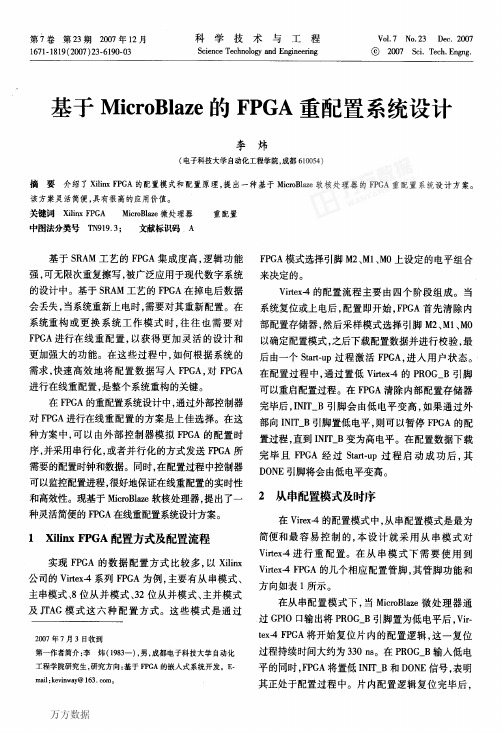

第7卷第23期2007年12月1671—1819(2007)23—6190—03科学技术与工程ScienceTechnologyandEngineeringV01.7No.23Dec.2007⑥2007Sci.Tech.Engng.基于MicroBlaze的FPGA重配置系统设计李炜Jl’(电子科技大学自动化工程学院,成都610054)摘要介绍了XilinxFPGA的配置模式和配置原理,提出一种基于MicroBlaze软核处理器的FPGA重配置系统设计方案。

该方案灵活简便,具有很高的应用价值。

关键词XilinxFPGAMicroBlaze微处理器重配置中图法分类号TN919.3;文献标识码A基于SRAM工艺的FPGA集成度高,逻辑功能强,可无限次重复擦写,被广泛应用于现代数字系统的设计中。

基于SRAM工艺的FPGA在掉电后数据会丢失,当系统重新上电时,需要对其重新配置。

在系统重构或更换系统工作模式时,往往也需要对FPGA进行在线重配置,以获得更加灵活的设计和更加强大的功能。

在这些过程中,如何根据系统的需求,快速高效地将配置数据写入FPGA,对FPGA进行在线重配置,是整个系统重构的关键。

在FPGA的重配置系统设计中,通过外部控制器对FPGA进行在线重配置的方案是上佳选择。

在这种方案中,可以由外部控制器模拟FPGA的配置时序,并采用串行化,或者并行化的方式发送FPGA所需要的配置时钟和数据。

同时,在配置过程中控制器可以监控配置进程,很好地保证在线重配置的实时陛和高效性。

现基于MicroBlaze软核处理器,提出了一种灵活简便的FPGA在线重配置系统设计方案。

1XilinxFPGA配置方式及配置流程实现FPGA的数据配置方式比较多,以Xilinx公司的Virtex-4系列FPGA为例,主要有从串模式、主串模式、8位从并模式、32位从并模式、主并模式及JTAG模式这六种配置方式。

这些模式是通过2007年7月313收到第一作者简介:李炜(1983一),男,成都电子科技大学自动化工程学院研究生,研究方向:基于FPGA的嵌入式系统开发。

FPGA跑马灯实验及程序

信息工程学院实训报告题目:学生姓名:学号:专业:班级:指导教师:实训任务书1.1 设计题目:多开关控制跑马灯1.2 设计要求1.2.1 设计目的(1)掌握开关和LED灯的构成、原理与设计方法;(3)学会使用C语言编写设计逻辑电路;(2)熟悉Xilinx EDK软件的使用方法。

1.2.2 基本要求(1)能用C语言设计多开关控制跑马灯的电路;(2)能进行多开关控制跑马灯检测和仿真;(3)能进行多开关控制跑马灯硬件下载。

1.2.3 发挥部分(1)利用C语言编写多种跑马灯工作方式;(2)硬件显示多种跑马灯功能。

摘要嵌入式系统经历了从单片计算机、工业控制计算机、集中分布式控制系统,发展到嵌入式的平台的几个阶段:从独立单机使用发展到联网设备;从以模拟电路为主发展到以数字电路为主、数/模混合型,进而进入全数字时代。

总的来说,嵌入式系统向着更高性能、更小体积、更低功耗、更廉价、无处不在的方向发展。

嵌入式系统的设计和实现朝着基于芯片,特别是片上可编程系统(SOPC)的方向发展。

嵌入式开发套件(EDK)是用于设计嵌入式可编程系统的全面解决方案。

该套件包括嵌入式软件工具(Platform Studio)以及嵌入式IBM PowerPC硬件处理器核和/或Xilinx MicroBlaze软处理器核进行Xilinx平台FPGA设计时所需的技术文档和IP。

注意,这里的嵌入式软件工具指用来产生、编辑、编译、链接、加载和调试高级编程语言(通常是C或C++)代码的工具,以便在处理器引擎上执行。

由于嵌入式系统涉及了软件和硬件的开发以及两者的综合设计,因此其开发是较为复杂的。

本设计首先通过EDK的XSP搭建一个硬件平台,添加设计需要的IP内核;然后引入SDK,在SDK中用C语言进行程序的编写并进行编译下载,基于XSP、SDK和FPGA 等完成了用四个开关来控制8个LED灯的不同点亮方式及不同的跑马灯,进而完成多开关控制跑马灯。

关键词:嵌入式、XSP、SDK、跑马灯目录实训任务书 (II)1.1 设计题目:多开关控制跑马灯 (II)1.2 设计要求 (II)1.2.1 设计目的 (II)1.2.2 基本要求 (II)1.2.3 发挥部分 (II)摘要 (III)第一章设计原理及分析 (1)1.1 设计原理 (1)1.1.1 LED点亮原理 (1)1.1.2 开关工作原理 (1)1.2 原理分析 (1)1.2.1 设计流程 (2)第二章设计内容及思路 (3)2.1 设计程序及分析 (3)2.1.1 主程序及分析 (3)2.1.2 主程序流程图 (8)2.1.3 波形仿真程序 (8)2.1.4 波形仿真图形 (8)2.1.5 引脚分配 (9)第三章Xilinx EDK12.4软件的应用 (10)3.1 创建硬件平台 (10)3.2 添加IP Core (10)3.3 生成仿真文件 (10)3.4 生成硬件比特流 (10)3.5 开发软件系统 (10)3.6 下载 (10)总结 (11)致谢 (12)参考文献 (13)附录1 程序代码 (14)第一章设计原理及分析1.1 设计原理把四个开关作为选择器,用C语言编写四种不同的跑马灯工作方式;通过四个开关的闭合与开启来选择跑马灯的工作方式,一个开关闭合对应的8个LED灯就进行一种跑马方式。

FPGA入门系列实验教程——跑马灯

FPGA入门系列实验教程——LED跑马灯1.实验任务让实验板上的8个LED实现跑马灯的功能。

通过这个实验,进一步掌握采用计数与判断的方式来实现分频的Verilog HDL的编程方法以及移位运算符的使用。

2.实验环境硬件实验环境为艾米电子工作室型号EP2C8Q208C8增强版开发套件。

软件实验环境为Quartus II8.1开发软件。

3.实验原理从LED[0]到LED[7]依次点亮,第二个灯点亮时第一个熄灭,每个灯交换的时间为0.5S;看上去的效果就象一个亮点从LED[0]跑向LED[7],然后重复此循环,故命名跑马灯。

初始状态时,LED[0]亮,其余熄灭。

每来一个时钟脉冲CLK,计数器就加1。

每当判断出计数器中的数值达到25000000时,就会点亮LED[1],同时LED[0]熄灭,并进行移位。

这样,依次点亮所有的灯,就形成了跑马灯。

而当LED[7]点亮时,需要一个操作使得恢复为初始状态,即:LED[0]亮,其余熄灭。

然后,再进行一次跑马灯,重复此循环。

如果是右移位,就出现向右跑马的现象;反之,向左跑马。

4.实验程序module ledwalk(led,clk);input clk;output[7:0]led;reg[7:0]led_out;reg[25:0]buffer;always@(posedge clk)beginbuffer<=buffer+1'b1;if(buffer==26'd2*******)beginled_out=led_out<<1;if(led_out==8'b00000000)led_out=8'b00000001;endendassign led=led_out;endmodule5.实验步骤(1)建立新工程项目:打开Quartus II软件,进入集成开发环境,点击File→New project wizard建立一个工程项目ledwalk。

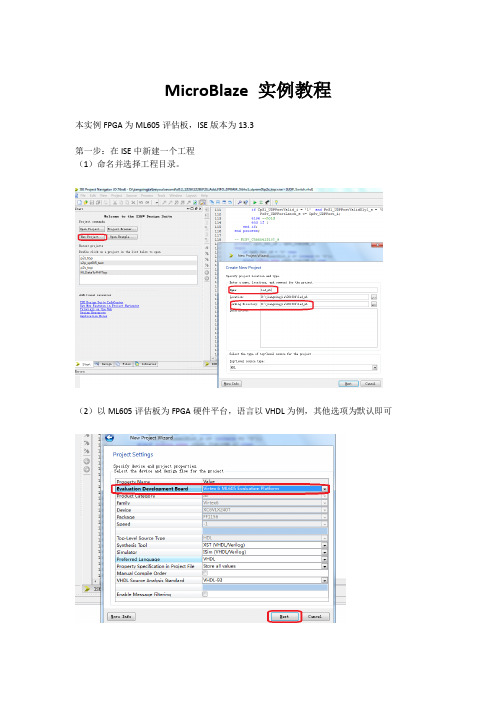

microblaze实例教程

MicroBlaze 实例教程本实例FPGA为ML605评估板,ISE版本为13.3第一步:在ISE中新建一个工程(1)命名并选择工程目录。

(2)以ML605评估板为FPGA硬件平台,语言以VHDL为例,其他选项为默认即可(3)新建一个Embedded Processor,然后命名。

第二步:由向导生成一个CPU_SYS,在下图中点击Yes即可。

(1)选择外围电路,如下图所示(2)点next(3)总线选择AXI,对于之前的器件有时候只支持PLB,则选择PLB (4)生成网表此后,CPU_SYS 生成完成。

第三步:进入软件平台(1)在ISE环境下先生成Top层VHDL代码(2)从ISE环境下导出SDK:如下图选“Export Hardware Design To SDK without Bitstream”,因为此时还没有生成*.bit文件,所以只能选择“without bitstream”或者在XPS环境中导出SDK:先选择XPS环境中Project下的“Export Hardware Design To SDK ...”在弹出的对话框中选择“Export & Launch SDK”(3)选择工作目录,最好在SDK下面新建一个SDK_workspace文件夹(4)在弹出的提示中选择OK即可(5)如下图所示界面,稍等片刻知道导入完成,出现如下界面,此时的CPU_SYS_hw_platform平台为默认的平台,我们可以理解为硬件平台。

现在就完全进入了SDK环境,此后就可以从Windows界面直接进入第四步:用C或者C++语言编写代码(1)新建一个工程,选择Xilinx C Project,点击Next(2)选择Hello World 模板,点Next(3)生成成功,点击Finish 即可此时的模版已经生成,在里面hello_world_0下展开会有src文件夹,其中的helloworld.c可以进行编写,但是此时的程序已经是一个完整的程序,运行即可(4)由于要点亮LED灯,为简单起见,我们类似于上面的模版生成一个Peripheral Tests 模版,如下图,点Next弹出下图所示界面后等待,如下图,完成后点Finish(5)软件平台已经搭建好,而且模版的程序也可以直接用。

microblaze 逻辑 -回复

microblaze 逻辑-回复microblaze 逻辑是什么?MicroBlaze逻辑是一种处理器设计的方法,它是Xilinx公司推出的一种32位快速硬件设计处理器核,主要用于嵌入式系统的设计。

MicroBlaze 处理器可以通过对其适应相关的硬件组件和软件平台来实现所需的定制功能。

它可以在FPGA(可编程逻辑器件)上实现,因此广泛用于嵌入式系统和数字信号处理等领域。

本文将以MicroBlaze逻辑为主题,详细介绍其特点、架构和应用。

第一部分:MicroBlaze的特点(500字)MicroBlaze是一种定制的32位核处理器,具有以下几个主要特点:(1) 可定制化:MicroBlaze处理器可以根据需要进行定制,可以添加或移除特定的硬件组件,以适应不同的应用场景。

这种定制化的能力使得MicroBlaze可以在不同嵌入式系统中满足灵活的要求。

(2) 快速设计:MicroBlaze处理器的设计流程相对简单,只需进行高级综合和门级综合等少量步骤,就可以快速地实现和验证其功能。

这使得MicroBlaze逻辑在硬件设计领域中具有很高的开发效率。

(3) 小型化:MicroBlaze处理器的核心组件相对较小,仅包括基本指令集和寄存器等,这使得其占用的硬件资源较少。

尽管如此,MicroBlaze仍然可以实现高性能和各种应用需求。

(4) 可扩展性:MicroBlaze处理器支持多种外设,包括存储器控制器、通信接口和数字信号处理单元等。

这些外设可以通过高级片上系统(MicroBlaze内部基于AXI总线的外设集成)或外部模块(通过AXI总线进行连接)进行扩展,以满足更多的应用需求。

第二部分:MicroBlaze的架构(600字)MicroBlaze处理器基于Harvard结构,具有五个主要部分:指令存储器、数据存储器、控制单元、运算单元和寄存器文件。

(1) 指令存储器:MicroBlaze使用32位存储器来存储指令,其中包括支持32位、16位和8位指令的指令解码器。

EDA课程设计跑马灯设计

第一章设计内容与设计方案1.1课程设计内容控制8个LED进行花样性显示。

设计4种显示模式:s0,从左到右逐个点亮LED;s1,从右到左逐个点亮LED;s2,从两边到中间逐个点亮LED;s3,从中见到两边逐个点亮LED。

4种模式循环切换,复位键(rst)控制系统的运行停止。

数码管显示模式编号。

可预置彩灯变换速度,4档快、稍快、中速、慢速,默认工作为中速。

1.2设计方案在掌握常用数字电路功能和原理的基础上,根据EDA技术课程所学知识,以及平时实验的具体操作内容,利用硬件描述语言HDL,EDA软件QuartusⅡ和硬件平台cycloneⅡFPGA进行一个简单的电子系统设计,本次课程设计采用Verilog HDL硬件描述语言编写控制程序,应用Quartus Ⅱ软件实现仿真测试。

采用FPGA芯片对LED灯进行控制,使其达到流水跑马灯显示的效果,LED灯采用共阳极接法,当给它一个低电平时,LED点亮,我们利用移位寄存器使各输出口循环输出高低电平,达到控制的目的。

2.1设计原理及设计流程本次试验我所完成的内容是跑马灯的设计,下面我简单的进行一下原理的阐述。

跑马灯课程设计的要求是控制8个LED进行花样显示,设计四种显示模块:第一种显示是从左向右逐个点亮LED。

第二种显示:从右向左逐个点亮LED。

第三种显示:从两边向中间逐个点亮LED。

第四种显示:从中间到两边逐个点亮LED。

四种显示模式循环切换,并带有一位复位键控制系统的运行停止。

为了完成要求的效果显示,由于要求比较简单,所以不用分为很多模块来具体控制,所以我先择利用移位寄存器来完成灯的点亮,我们将LED灯采用共阳极接法,当给于低电平时点亮,那么当我们需要点亮某位LED灯时,只需在该位上赋予低电平即可,比如:如果我们要实现8个数码灯从左到右依次点亮,那么我们就可以给这8个数码灯分别赋值10000000,经过一段时间的延时后再给其赋值01000000,再经过一段时间延时后再给其赋值00100000,依次类推,则最后一种赋值状态为00000001,这样就得到了相应的现象。

FPGA基础教程系列 -- 玩转LED

FPGA基础教程系列电子工程世界 EE_FPGA基础教程系列玩转LEDV1.0作者:xieqiang整理: chenzhuflyQQ: 368860522011‐3‐14电子工程世界 EE_FPGA基础教程系列Revision HistoryVersion Author Description Date1.0 chenzhufly EE_FPGA 基础教程‐‐‐‐ 玩转LEDKeywords:Abstract:本文举例分析点亮LED的Verilog程序,同时讲了计数器和流水灯的概念。

Table of Contents1. 剧情回放 (4)2. 玩转LED (4)2.1 硬件连接 (4)2.2 程序编写 (4)2.3 程序简介 (5)2.4 换个玩法 (7)2.5 点灯进阶 (7)2.6 答疑解惑 (9)3. 总结 (10)1. 剧情回放话说上次在建立的第一个EE_FPGA工程的时候,我们使用了一个点亮LED 的范例,这里我们继续点亮LED这个话题。

2. 玩转LED2.1 硬件连接首先,我们得打开EE_FPGA的硬件手册,找到LED部分的原理图。

如下图所示,我们看到,LED的右端是连着上拉电阻的VDD3.3V高电平,左端则连着FPGA的管脚pin_31-35。

那我们想,假若我们的FPGA管脚输出的是高电平即3.3V,那么左右两端的电压相当,就不会有电流流过LED,也就不会发光了。

如果FPGA管脚输出的是低电平,那就有电流从LED流过,LED就点亮了。

原理就是这么简单。

2.2 程序编写一般FPGA的核心电平是1.2V,管脚电平是3.3V,所以,要想点亮哪个LED,只要给连接的那个管脚赋0,不点亮赋1就可以了。

上次点亮四个LED的程序我们是这样写的:module led (clk,rst_n,led);input clk;input rst_n;output[3:0] led;reg[3:0] led_r;always @(posedge clk or negedge rst_n)beginif(!rst_n)led_r <= 4'b1111;elseled_r <= 4'b0; // led是一端接上拉电阻,输入低电平点亮endassign led = led_r;endmodule2.3 程序简介这里我就讲点Verilog的经验之谈,有不妥的地方还请大家多指正。

FPGA跑马灯

module paoma(mclk,reset,type,ledout);input mclk,reset;input[2:0] type;output [15:0] ledout;reg [15:0] ledout;reg [24:0] count;reg [4:0] state;wire clk;always@(posedge mclk)count=count+1;assign clk=count[23];reg[2:0] type_delay;wire type_change;always @ (posedge clk)type_delay <= type;assign type_change=(type!=type_delay)?1:0;always @ (posedge clk )beginif(reset==0)begin ledout=6'b000000;state<=0;endelseif(type_change)state<=4'b0001;elseif(type==3'b000)begincase (state)4'b0001:ledout <= 16'b0000_0000_0000_0001;4'b0010:ledout <= {ledout[14:0],ledout[15]};default :ledout=16'b0000_0000_0000_0000;endcasestate=state+1;if(state==4'b0011)state=5'b00010;endelseif(type==3'b001)begincase (state)4'b0001:ledout <= 16'b0000_0000_0000_0011;4'b0010:ledout <= {ledout[14:0],ledout[15]};default :ledout=16'b0000_0000_0000_0000;endcasestate=state+1;if(state==4'b0011)state=5'b00010;endelseif(type==3'b010)begincase (state)4'b0001:ledout <= 16'b0000_0000_0000_0111;4'b0010:ledout <= {ledout[14:0],ledout[15]};default :ledout=16'b0000_0000_0000_0000;endcasestate=state+1;if(state==4'b0011)state=5'b00010;endelseif(type==3'b011)begincase (state)4'b0001:ledout <= 16'b1000_0000_0000_0000;4'b0010:ledout <= {ledout[0],ledout[15:1]};default :ledout=16'b0000_0000_0000_0000;endcasestate=state+1;if(state==4'b0011)state=5'b00010;endelseif(type==3'b100)begincase (state)4'b0001:ledout <= 16'b1100_0000_0000_0000;4'b0010:ledout <= {ledout[0],ledout[15:1]};default :ledout=16'b0000_0000_0000_0000;endcasestate=state+1;if(state==4'b0011)state=5'b00010;endelseif(type==3'b101)begincase (state)4'b0001:ledout <= 16'b1110_0000_0000_0000;4'b0010:ledout <= {ledout[0],ledout[15:1]};default :ledout=16'b0000_0000_0000_0000;endcasestate=state+1;if(state==4'b0011)state=5'b00010;endelseif(type==3'b110)begincase(state)4'b0001:ledout=16'b1010_1010_1010_1010;4'b0010:ledout=16'b0101_0101_0101_0101;4'b0011:ledout=6'b0011_0011_0011_0011;4'b0100:ledout=6'b1100_1100_1100_1100;default :ledout=16'b0000_0000_0000_0000;endcasestate=state+1;if(state==4'b0101)state=5'b00001;endelseif(type==3'b111)begincase(state)4'b0001:ledout=16'b1111_0000_0000_1111;4'b0010:ledout=16'b0111_1000_0001_1110;4'b0011:ledout=16'b0011_1100_0011_1100;4'b0100:ledout=16'b0001_1110_0111_1000;4'b0001:ledout=16'b0000_1111_1111_0000;default :ledout=16'b0000_0000_0000_0000;endcasestate=state+1;if(state==4'b0101)state=5'b00001;endendendmodule。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于SOPC 的跑马灯电路设计

一、实验目的

1、认识和了解SOPC 设计技术;

2、熟悉基于MicroBlaze 内核的SOPC 系统设计流程;

二、实验原理

本次实验将完成的设计是一个基于MicroBlaze 的SOPC 系统,其示意图如图1所示。

程序存储器(ROM )

MicroBlaze 处理器核

输入端口

输出端口

FPGA

时钟异步复位多路拨码输入

LED LCD

图1 基于MicroBlaze 的SOPC 系统

MicroBlaze 是基于Xilinx 公司FPGA 的微处理器IP 核,和其它外设IP 核一起,可以完成可编程系统芯片(SOPC )的设计。

MicroBlaze 处理器采用RISC 架构和哈佛结构的32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并访问其的数据。

MicroBlaze 内部有32个32位通用寄存器和2个32位特殊寄存器—PC 指针和MSR 状态标志寄存器。

为了提高性能,MicroBlaze 还具有指令和数据缓存。

所有的指令字长都是32位,有3个操作数和2种寻址模式。

指令按功能划分有逻辑运算、算术运算、分支、存储器读/写和特殊指令等。

指令执行的流水线是并行流水线,它分为3级流水:取指、译码和执行。

MicroBlaze 可以响应软件和硬件中断,进行异常处理,通过外加控制逻辑,可以扩展外部中断。

利用微处理器调试模块(MDM )IP 核,可通过JTAG 接口来调试处理器系统。

多个MicroBlaze 处理器可以用1个MDM 来完成多处理器调试。

MicroBlaze 处理器具有8个输入和8个输出快速单一链路接口(FSL )。

FSL 通道是专用于单一方向的点到点的数据流传输接口。

FSL 和MicroBlaze 的接口宽度是32位。

每一个FSL 通道都可以发送和接收控制或数据字。

MicroBlaze采用32位哈佛RISC 架构,32位独立的地址总线和数据总线。

在采用缓存模式下,独立的指令和数据可以缓存并通过XCL(Xilinx CacheLink)接口连接到内存。

在不采用缓存的机制下,地址和数据总线直接通过PLB46访问内存。

MicroBlaze没有区分数据接口为I/O和存储,所以处理器存储的接口是PLB和LMB,且LMB存储地址空间不和PLB重合。

MicroBlaze还提供最大256K的片上本地内存接口和片上BRAM连接,对于简单的设计,可以将代码直接放入片上BRAM;也可以将复杂设计的BOOTLOADER放在片上的BRAM中。

用户IP可以通过PLB46总线或快速点对点连接(FSL)接入系统。

一般而言:PLB64比较适合基于总线形式的用户IP开发;FSL比较适合基于简单点对点输入输出或协处理器的用户IP开发。

下图是一个MicroBlaze片上系统的内部结构图。

图2

MicroBlaze支持8位(字节)、16位(半字)和32位(字)的数据形式并采用大字序方式. 其具体的形式如下表所示:

图3

三、实验步骤:

1、新建一个工程,命名为Mic_LEDA

图4

2、NEW source 添加embedded processor,命名为Mic_LED

图5

3、之后一直点击next

图6

图7

图8

图9

图10

图11 右上角点击add device添加设备

图12 分别选择GPIO,LEDS

图13

位宽改为8位

图14 一直点击next

图15 点击Finish

图16

右上角点击generate address,分配地址

图17

工具栏点击hardware选择generate netlist 生成网表

图18

回到ISE,双击View HDL instantiation template查看例化文件并复制

图19

新建一个.v文件作为顶层文件,把刚才复制的内容粘贴进来,并完善

图20

添加ucf文件并锁定引脚

图21

双击Configure Target File生成可下载文件,并下载到开发板上

图22

启动SDK软件

图23 新建

图24 工程命名为LED_C,点击next

图25

添加代码

图26

工具栏选择run

图27

再点击run可下载程序到实验板。

四.实验结果

1、下载到实验板上后,LED依次从右向左闪烁然后循环,实现了跑马灯的功能。

图28

五.跑马灯代码

#include "xparameters.h"

#include "xgpio_l.h"

void delay(int cnt)

{

int i, j;

for(i = 0; i < cnt; i++)

for(j = 0; j < 1000; j++)

;

}

int main()

{

while(1)

{

XGpio_mWriteReg(XPAR_LEDS_BASEADDR, 0 , 0xff);

delay(300);

XGpio_mWriteReg(XPAR_LEDS_BASEADDR, 0 , 0xfe);

delay(300);

XGpio_mWriteReg(XPAR_LEDS_BASEADDR, 0 , 0xfd);

delay(300);

XGpio_mWriteReg(XPAR_LEDS_BASEADDR, 0 , 0xfb);

delay(300);

XGpio_mWriteReg(XPAR_LEDS_BASEADDR, 0 , 0xf7);

delay(300);

XGpio_mWriteReg(XPAR_LEDS_BASEADDR, 0 , 0xef);

delay(300);

XGpio_mWriteReg(XPAR_LEDS_BASEADDR, 0 , 0xdf);

delay(300);

}

return 0;

}。