第3章总线与主板

《计算机组成原理》唐朔飞第二版_笔记

《计算机组成原理》唐朔飞第⼆版_笔记第1章概论1,计算机系统的软硬件概念1)硬件:计算机的实体部分,它由看得见摸得着的各种电⼦元器件,各类光、电、机设备的实物组成,如主机、外部设备等。

2)软件:由⼈们事先编制的具有各类特殊功能的程序组成,分为系统软件和应⽤软件。

①系统软件⼜称为系统程序,主要⽤来管理整个计算机系统,监视服务,使系统资源得到合理的调度,⾼效运⾏。

它包括:标准程序库、语⾔处理程序(编译程序)、操作系统、、服务程序(如诊断、调试、连接程序)、数据库管理系统、⽹络软件等。

②应⽤软件⼜称应⽤程序,它是⽤户根据任务需要所编制的各种程序,如科学计算程序、数据处理程序、过程控制程序、实物管理程序。

2、计算机系统的层次结构:1)硬联逻辑级:第零级是硬联逻辑级,这是计算机的内核,由门,触发器等逻辑电路组成。

2)微程序级:第⼀级是微程序级。

这级的机器语⾔是微指令集,程序员⽤微指令编写的微程序,⼀般是直接由硬件执⾏的。

3)传统机器级:第⼆级是传统机器级,这级的机器语⾔是该机的指令集,程序员⽤机器指令编写的程序可以由微程序进⾏解释。

操作4)系统级:第三级是操作系统级,从操作系统的基本功能来看,⼀⽅⾯它要直接管理传统机器中的软硬件资源,另⼀⽅⾯它⼜是传统机器的延伸。

5)汇编语⾔级:第四级是汇编语⾔级,这级的机器语⾔是汇编语⾔,完成汇编语⾔翻译的程序叫做汇编程序。

6)⾼级语⾔级:第五级是⾼级语⾔级,这级的机器语⾔就是各种⾼级语⾔,通常⽤编译程序来完成⾼级语⾔翻译的⼯作。

7)应⽤语⾔级:第六级是应⽤语⾔级,这⼀级是为了使计算机满⾜某种⽤途⽽专门设计的,因此这⼀级语⾔就是各种⾯向问题的应⽤语⾔。

把计算机系统按功能分为多级层次结构,就是有利于正确理解计算机系统的⼯作过程,明确软件,硬件在计算机系统中的地位和作⽤。

3、计算机组成和计算机体系结构1)计算机体系结构:是指那些能够被程序员所见到的计算机系统的属性,即概念性的结构与功能特性。

主板知识

第3章 主 板

图3–1 Slot 架构主板

第3章 主 板

PS/2接口的 键盘和鼠标插座 电源插座 Socket 370 接口的 CPU插座 内存插槽

USB接口

并口(串口在它下面)

软驱接口

IDE接口 可见部分是游戏接 口,下面是声卡接口 接硬盘、光驱等设备

AMR 插槽 北桥芯片 AGP插槽 电池 PCI插槽 南桥芯片 BIOS芯片 一般采用EEPROM

主板集成,而是通过档板片提供,如图 3–25 所示。这

种鼠标接口通常是关闭的,如果系统不认PS/2 MOUSE, 则要在CMOS设置中将PS/2 MOUSE激活。

第3章 主 板

图3–24 串行口鼠标接口

第3章 主 板

图3–25 AT主板上的PS/2 MOUSE接口

第3章 主 板

对于ATX结构主板,PS/2 MOUSE插座都已集成在

电时信息会丢失。CMOS芯片里保存着当前系统的硬

件配置参数和在BIOS程序中设置的各种参数,所以为 了避免关机后CMOS参数丢失,主板上的电池主要用

来给CMOS芯片供电。

第3章 主 板

3.1.7 电池

为了在掉电时保持CMOS内容和主板上系统时钟的 正常运行,每块主板上都有一个电池,如图3–14所示。 现在主板上的电池大多为纽扣电池,在486和586主板 上也有电容电池和集成块电池,如图3–15所示。

第3章 主 板

纽扣电池 CMOS芯片 BIOS芯片

图3–14 电池

第3章 主 板

图3–15 集成块和电容电池

第3章 主 板

3.1.8 主板电源插座

电源是计算机的动力来源。主板电源的插座分为 两种:AT电源插座和ATX电源插座。 1.AT电源插座 AT结构主板电源插座是 12芯单列插座,没有防错

主板的作用、分类及组成

主板

内存插槽:SD、DDR、DDR2、DDR3等

扩展插槽:

AGP插槽、 PCI-E插槽

各类板卡插槽

PCI总线插槽 、 ISA总线插槽

外设接口:键盘、鼠标、显示器、打印机等

接口: 磁盘接口:IDE接口、SATA接口、FDD接口等

USB通用接口:USB1.1、USB2.0、 USB3.0 IEEE 1394接口

❖ 二、主板的作用

❖ 1,将不同电压的电脑配件连接在一起,并提供相应 的电源;

❖ 2,将不同功能的电脑配件连接在一起,使它们相互 传递信息;

❖ 3,接收外来数据,并给其它设备处理;

❖ 4,将内部设备处理的数据集中,并传递给外界;

❖ 5,平衡电脑中的数据、能源、速度、温度、电流等。

❖ 三、主板的分类

❖ 控制芯片组包括北桥芯片和南桥芯片。

❖2.1 北桥芯片

❖ 北桥芯片是主板芯片组中起主导作用的最重要的组 成部分,也称为主桥(Host Bridge)。一般来说, 主板的名称就是以北桥芯片的名称来命名的,例如 英特尔845系列主板的北桥芯片是82845E,AMD770系 列主板的北桥芯片就是AMD 770等等。

第三章 主板

❖ 主板的作用和分类 ❖ 主板的组成 ❖ 主流芯片组介绍 ❖ 主板的选购 ❖ 主板的常见故障分析和维修

第1讲

❖ 主板的定义、作用和分类 ❖ 主板的组成

❖ 一、主板的定义

❖ 主板,又叫主机板(mainboard)、系统板 (systemboard)和母板(motherboard);它安 装在机箱内,是微机最基本的也是最重要的 部件之一。主板一般为矩形电路板,上面安 装了组成计算机的主要电路系统,一般有 BIOS芯片、I/O控制芯片、键盘和面板控制 开关接口、指示灯插接件、扩充插槽、主板 及插卡的直流电源供电接插件等元件。

3.2.2 PCI总线插槽的检测与故障判断_按图索骥学修电脑主板_[共2页]

![3.2.2 PCI总线插槽的检测与故障判断_按图索骥学修电脑主板_[共2页]](https://img.taocdn.com/s3/m/e0c517f8b4daa58da1114ab8.png)

第3章 主板总线插槽的检测与维修

◆ 47 ◆ 4.挂接设备的数量

挂接设备的数量是指总线所能支持同时挂接的最多设备数。

3.2 利用打阻值卡和万用表检修主板总线插槽

3.2.1 打阻值卡简介

打阻值卡(见图3-1)的原理,就是用PCB 板的方式,将欲测量点的位置及名称标在PCB 板上。

在维修主板时,信号的测量是很重要的。

欲测量的各种插槽的引脚很多,其中有电压脚和接地脚,但一般都是测量信号脚。

在没有打阻值卡时,只能对着插槽的引脚定义来找信号脚的所在位置,现在有了打阻值卡这种工具,可以将相应的打阻值卡插到相应的插槽中。

这样就可以不用去记忆复杂的信号定义图,直接对卡上的测试点作测量就可以,从而有效地提高检测和维修的速度,达到事半功倍的效果。

图3-1 打阻值卡实物图

3.2.2 PCI 总线插槽的检测与故障判断

1.PCI 总线插槽简介

PCI 总线是外设部件互连总线,由PCI SIG 在1994年开发出来。

PCI 总线可以提供硬件的即插即用支持,使系统升级比较容易实现。

PCI 总线的数据带宽为32位,可扩展为64位,工作频率为33MHz ,数据传输率为133MB/s 。

图3-2和表3-1所示分别为PCI 总线插槽及其各针脚功能。

计算机组装与维护教程03

机箱面板上的电源开关、重置开关、电源

指示灯、硬盘指示灯等都连接到该插针组 上,接头组的用途见表3-1。

3.2.18 I/O接口背板 主板I/O接口背板如图3-29所示。

1.PS/2接口

主板背板上的PS/2接口插槽,如图3-30所示。 有些主板取消了PS/2键盘、PS/2鼠标接口, 由USB接口代替。

3.2.7 BIOS单元 BIOS芯片常见外观如图3-17所示。

3.2.8 主板电源插座 主板电源插座如图3-18所示。

3.2.9 供电单元

供电单元是指为CPU、内存控制器、集成显 示卡等部件供电的单元。主板供电回路的 主要部分一般都位于主板CPU插座附近,如 图3-19所示。如图3n Board)、系统板 (System Board)或母板(Mother Board),是微机 系统中最基本的也是最重要的部件之一。主板是微 机系统中最大的一块电路板,是整个微机系统的载 体。主板也是与CPU配套最紧密的部件,每推出一 款新型的CPU,都会推出与之配套的主板控制芯片 组。

3.2.12 网卡控制芯片

许多主板上集成了具备网卡功能的芯片 (10/100/1000Mbit/s Fast Ethernet控制器), 在主板上常见的板载网卡控制芯片如图3-22 所示。

3.2.13 I/O及硬件监控芯片

I/O芯片一般位于主板的边缘,如图3-23所 示。

第三章 LCD 主板部分_路分析

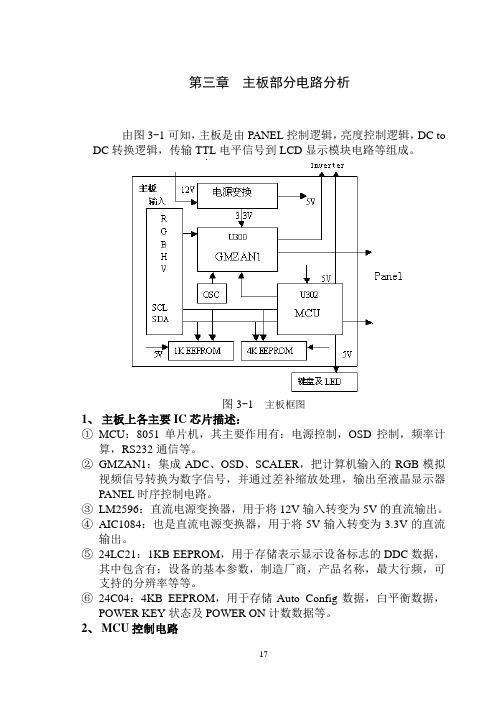

第三章主板部分电路分析由图3-1可知,主板是由PANEL控制逻辑,亮度控制逻辑,DC to DC转换逻辑,传输TTL电平信号到LCD显示模块电路等组成。

图3-1 主板框图1、主板上各主要IC芯片描述:①MCU:8051单片机,其主要作用有:电源控制,OSD控制,频率计算,RS232通信等。

②GMZAN1:集成ADC、OSD、SCALER,把计算机输入的RGB模拟视频信号转换为数字信号,并通过差补缩放处理,输出至液晶显示器PANEL时序控制电路。

③LM2596:直流电源变换器,用于将12V输入转变为5V的直流输出。

④AIC1084:也是直流电源变换器,用于将5V输入转变为3.3V的直流输出。

⑤24LC21:1KB EEPROM,用于存储表示显示设备标志的DDC数据,其中包含有:设备的基本参数,制造厂商,产品名称,最大行频,可支持的分辨率等等。

⑥24C04:4KB EEPROM,用于存储Auto Config数据,白平衡数据,POWER KEY状态及POWER ON计数数据等。

2、MCU控制电路MCU控制接口电路如附图1所示。

其中U302为8051系列单片机,其ROM的容量为64K,RAM容量为512Bytes。

用于计算频率,探测模式切换,RS232通讯,电源控制,屏幕显示菜单控制等,在软件控制下,MCU由P1.6和P1.7脚分别产生一个Backlight_EN和Panel_EN信号用于点亮PANEL上的背光灯和控制PANEL工作。

①MCU各主要引脚功能定义如下表3-1:②MCU项目定义:运行于微控制器上的GMZAN1控制软件,需要完成以下操作:1)初始化LCD控制板元件至用户定义的开机设定:a)把工厂缺省寄存器设定存在ROM中;b)用户设定存在内部EEPROM;c)用户设定初始化时设为工厂缺省值。

2)自动检测模式切换,在模式切换时对相应的元件编程。

3)如果视频模式是未知的,则显示错误信息。

4)检测输入视频线的正确连接,如果没有检测到有效连接,则对应输入视频源显示错误信息。

计算机组成原理——第三章系统总线

计算机组成原理——第三章系统总线3.1 总线的基本概念1. 为什么要⽤总线计算机系统五⼤部件之间的互连⽅式有两种:分散连接——各部件之间使⽤单独的连线总线连接——各部件连到⼀组公共信息传输线上早期的计算机⼤多采⽤分散连接⽅式,内部连线⼗分复杂,尤其当I/O与存储器交换信息时都需要经过运算器,使运算器停⽌运算,严重影响CPU的⼯作效率。

2. 什么是总线总线是连接各个部件的信息传输线,是各个部件共享的传输介质3. 总线上的信息传送串⾏并⾏3.2 总线的分类1. ⽚内总线芯⽚内部的总线CPU芯⽚内部寄存器之间寄存器与算逻单元ALU之间2. 系统总线计算机各部件(CPU、主存、I/O设备)之间的信息传输线按系统总线传输信息不同分为:数据总线——传输各功能部件之间的数据信息双向与机器字长、存储字长有关数据总线宽度——数据总线的位数地址总线——⽤来指出数据总线上的源数据或⽬的数据在主存单元的地址或I/O设备的地址单向(由CPU输出)与存储地址、I/O地址有关地址线位数(2n)与存储单元的个数(n)有关控制总线——⽤来发出各种控制信号的传输线出——中断请求、总线请求⼊——存储器读/写、总线允许、中断确认常见控制信号:时钟:⽤来同步各种操作复位:初始化所有部件总线请求:表⽰某部件需获得总线使⽤权总线允许:表⽰需要获得总线使⽤权的部件已获得了控制权中断请求:表⽰某部件提出中断申请中断响应:表⽰中断请求已被接收存储器写:将数据总线上的数据写⾄存储器的指定地址单元内存储器读:将指定存储单元中的数据读到数据总线上I/O读:从指定的I/O端⼝将数据读到数据总线上I/O写:将数据总线上的数据输出到指定的I/O端⼝内传输响应:表⽰数据已被接收,或已将数据送⾄数据总线上3. 通信总线⽤于计算机系统之间或计算机系统与其它系统(控制仪器、移动通信等)之间的通信通信⽅式:串⾏通信数据在单条1位宽的传输线上,⼀位⼀位地按顺序分时传送。

主板进阶知识

20

PCI规格

电压 ➢ PCI 1.0, 2.0: 5V only ➢ PCI 2.1, 2.2, 2.3: 5V, 3.3V ➢ PCI 3.0: 3.3V only

主板进阶知识

1

主板进阶知识

2

第1章 总线结构

➢ 概述 ➢ Intel平台 ➢ AMD平台 ➢ FSB ➢ DMI ➢ HT ➢ Memory Bus ➢ AGP ➢ PCI ➢ PCI Express ➢ LPC ➢ SPI ➢ SMBus

3

概述

在计算机科学中,总线(BUS)是一组用来在计算机系统的各个部件之间传输 数据的线路。总线实质上是连接系统不同部分的一个共享的高速公路——包括中 央处理器(CPU)、磁盘驱动控制器、内存和输入输出端口——并且使它们能够通 信。引入总线的目的是在一个通道上传输所有通信,从而减少各个部件之间通信 所需要的的路径,这就是有时候总线被比喻为“数据公路”的原因。

DMI

North

South

Bridge

Bridge

8

HT (Hyper Transport)

Hyper Transport技术,以前曾被 称作“闪电数据传输”(Lightning Data Transport, LDT),是一种高速、双向、 低延时、点对点的、串/并行的高带宽 连接,于2001年4月2日开始投入使用。 这种技术被用在AMD平台上连接CPU 和桥。最新版本HT3.1支持 2.8G/3.0/3.2GHz。如果它工作在 32bit/3.2GHz的DDR模式下,最大传输 速率可高达51.2GB/s。

第3章 主板

第3章 主板

100系列将伴随Skylake-S全面爆发,照例有六款型号,分别是入门级H110、主流级 H170、高端级Z170、低端级B150、商务级Q150/Q170,依次取代H81、H97、Z97、 B85、Q85、Q87。 伴随Skylake处理器的升级,Intel还会推出新一代的芯片组,命名直接从之前的8系、 9系跃升到了100系列了。相比9系相对8系主板不痛不痒的升级,100系芯片组总算有 明显升级了,而且多数都非常给力。100系列芯片组 Intel的新接口为LGA1151

第3章 主板

3.1 主板的分类 微机主板的分类方式有以下几种。 1.按主板的结构分类

第3章 主板

2.按主板支持CPU的类型分类 3.按逻辑控制芯片组分类 4.按是否为整合型分类 5.按生产厂家分类

第3章 主板

第3章 主板

3.2 主板的组成结构

第3章 主板

第3章 主板

第3章 主板

3.2.1 PCB基板 PCB(Printed Circuit Board,印制电路板)主要由铜皮(覆铜板)、玻璃纤维,经树 脂材料粘合而成。

第3章 主板

3.2.17 跳线、DIP开关、插针 1.跳线 跳线(Jumper)主要用来设定硬件的工作状态,如CPU的核心(内核)电压、外 频和倍频,主板的资源分配,以及启用或关闭某些主板功能等。

第3章 主板

2.DIP开关 尽管跳线已经使硬件设置变得非常灵活,但是跳线的插拔方式使用起来仍然不太方便。 因此,使用DIP开关,可以更为直观和容易地设置硬件的工作状态。DIP开关与普通 跳线一样,只是把小跳线做成了开关,如图3-22所示。 3.机箱面板指示灯及控制按钮插针 主板上的插针有很多组,有USB插针、CPU风扇插针等,其中最重要的一组是机箱面 板插针,如图3-23所示。机箱面板上的电源开关、重置开关、电源指示灯、硬盘指示 灯等都连接到该插针组上,接头组的用途见表3-1。

计算机组成原理-第3章 总线(4节课)

总线标准的产生

• 总线是在计算机系统模块化的发展过程中产生的,随 着计算及应用领域的不断扩大,计算机系统中各类模 块(特别是I/O设备所带来的各类接口模块),其品种 极其繁杂,往往出现一种模块要配一种总线,很难在 总线上更换、组合各类模块或设备。 • 20世纪70年代末,为了使系统设计简化,模块生产批 量化,确保其性能稳定,质量可靠,便于维护,人们 开始研究如何建立总线标准,完成系统设计和模块制 作。 • 概念:所谓总线标准,可视为系统与各模块、模块与 模块之间的一个互连的标准界面。

processor

memory

• 1970年DEC公司PDP-11 小型计算机首次采用

I/O Interface (adapter) I/O device

I/O Interface (adapter) I/O device

总线

• 定义:是连接多个部件的传输线

– 总线的关键特征是共享传输线。

• 总线的两个特点:

– 任意时刻只能有一个设备向总线发送信息

• 系统瓶颈

– 多个部件可以同时从总线接受相同的信息

• 广播式

主机 processor memory

I/O Interface (adapter) I/O device

I/O Interface (adapter) I/O device

总线分类——按位置

• 片内总线

计算机组成原理 第3章 系统总线

李曦(llxx@)

本章内容

• 3.1 总线的概念和分类

• 3.2 总线特性及性能指标

–总线特性 –性能指标 –总线标准

• 3.3 总线的结构

• 3.4 总线控制

–判优控制 –通信控制

3.1 总线的基本概念和分类

主板的作用、分类及组成

无跳线主板将是主板发展的另一个方向

第五种:按印制电路板的工艺分类:

可以分为双层结构板、四层结构板、六层结 构板等;目前以四层结构板的产品为主。

第六种:按主板的结构分类:

主板结构分为AT、Baby-AT、ATX、Micro ATX、LPX、NLX、 Flex ATX、EATX、WATX以及BTX等结构。其中,AT和Baby-AT是 多年前的老主板结构,现已基本淘汰;而LPX、NLX、Flex ATX 则是ATX的变种,多见于国外的品牌机,国内尚不多见;EATX 和WATX则多用于服务器/工作站主板;ATX是目前市场上最常见 的主板结构,扩展插槽较多,PCI插槽数量在4-6个,大多数主 板都采用此结构;Micro ATX又称Mini ATX,是ATX结构的简化 版,就是常说的“小板”,扩展插槽较少,PCI插槽数量在3个 或3个以下,多用于品牌机并配备小型机箱;而BTX则是英特尔 制定的最新一代主板结构。

❖ AGP插槽通常都是棕色,还有一点需要注意的是它不与PCI、ISA 插槽处于同一水平位置,而是内进一些,这使得PCI、ISA卡不 可能插得进去。当然AGP插槽结构也与PCI、ISA完全不同,根本 不可能插错的。

❖4.4 PCI-E总线及其插槽

❖ PCI Express是新一代的总线接口标准。这个标 准将全面取代现行的PCI和AGP,最终实现总线 标准的统一。它的主要优势就是数据传输速率 高,目前最高可达到10GB/s以上,而且还有相 当大的发展潜力。PCI-E接口根据总线位宽不同 也有多种规格,从PCI-E 1X到PCI-E 16X。 另 外,PCI-E也支持高阶电源管理、热插拔、数据 间同步传输等。

第二种:按主板所用北桥芯片厂商划分: ❖ SIS:矽统 矽统科技于1987年 在台湾的新竹科学 园区成立。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第3章总线与主板总线(Bus)是供多个部件分时共享的公共信息传送线路,一个系统的总线结构决定了该计算机系统的数据通路及系统结构。

它能简化系统设计、便于组织多家厂家进行专业化大规模生产,降低产品成本、提高产品的性能和质量,便于产品的更新换代、满足不同用户需求以及提高可维修性等,因而得以迅速发展。

自1970年美国DEC公司在其PDP-11/20小型计算机上采用Unibus以来,各种标准的、非标准的总线纷纷面世。

如今,几乎所有的计算机系统中都采用了总线结构。

在微型计算机中,总线以及所连接的部件都安放在主板(Main Board)上。

计算机在运行中对于系统内的部件和外部设备的控制都通过主板实现,主板的组成与布局也影响着系统的运行速度、稳定性和可扩展性。

3.1 总线的概念3.1.1 总线及其规范总线是由导线组成的传输线束,用来作为在计算机各种功能部件之间传送信息的公共通信干线。

共享、分时和规范是总线的3个基本特点。

共享是指多个部件连接在同一组总线上,各部件之间相互交换的信息都可以通过这组总线传送。

分时是指同一时刻总线只能在一对部件之间传送信息。

总线是计算机系统模块化的产物,相同的指令系统,相同的功能,不同厂家生产的各功能部件在实现方法上不尽相同,但希望相同的功能部件可以互换使用,这要求各厂家的产品必须遵循一定的规范。

这些规范包括如下4个方面。

1. 机械规范机械规范又称为物理规范,指总线在机械上的连接方式,如插头与插座所使用的标准,包括接插件尺寸、形状、引脚根数及排列顺序等,以便能正确无误地连接。

图3.1为计算机中常用的一些总线接插件。

2. 电气规范电气规范指总线的每一根线上信号的传递方向及有效电平范围、动态转换时间、负载能力等。

一般规定送入CPU的信号称为输入信号(IN),从CPU发出的信号称为输出信号(OUT)。

例如,地址总线是输出线,数据总线是双向传送,这两类信号线都是高电平有效;·154··155·控制总线一般是单向的,有输出的也有输入的,有高电平有效也有低电平有效。

总线的电平都符合TTL 电平的定义。

例如RS-232C 的电气规范规定,用低电平表示逻辑1,并且要求电平低于–3V ;用高电平表示逻辑0,并且要求电平高于+4V ,通常额定信号电平为–10V ~+10V 。

图3.1 计算机中常用的一些总线接插件 3. 功能规范按功能总线可分为地址总线、数据总线和控制总线。

在控制总线中,各条线的功能也不相同,有CPU 发出的各种控制命令(如存储器读写、I/O 读写等),也有外设与主机的同步匹配信号,还有中断信号、DMA 控制信号等。

4. 时间规范时间规范又称为逻辑规范,指在总线操作过程中每一根信号线上信号什么时候有效,通过这种信号有效的时序关系约定,确保了总线操作的正确进行。

3.1.2 总线分类总线应用很广,形态多样,从不同的角度可以有不同的分类方法。

下面列举几种。

1. 按照总线传递的信号性质分类按照总线传递的信号性质,可将其分为3种。

(1)地址总线(Address Bus ,AB ),用来传递地址信息。

(2)数据总线(Data Bus ,DB ),用来传递数据信息。

(3)控制总线(Control Bus ,CB ),用来传递各种控制信号。

2. 按照总线所处的位置分类按照总线所处的位置分为机内总线和机外总线。

机内总线分为片内总线和片外总线。

片内总线指CPU 芯片内部用于在寄存器、ALU 以及控制部件之间传输信号的总线;片外总线指CPU 芯片之外,用于连接CPU 、内存以及I/O 设备的总线。

机外总线指与外围设备接口的总线,实际上是一种外设的接口标准。

目前在微型计算机上流行的接口标准有IDE 、SCSI 、USB 和IEEE 1394等。

·156·3. 按照总线在系统中连接的主要部件分类按照总线在系统中连接的主要部件,可以将总线分为5种。

(1)存储总线:连接存储器。

(2)DMA 总线:连接DMA 控制器。

(3)系统总线:连接I/O 通道总线和各扩展槽。

(4)I/O (设备)总线:连接外部设备控制芯片。

(5)局部总线:通常是一种实现高速数据传送的高性能总线,用来在高度集成的外设控制器器件、扩展板和处理器/存储器系统之间提供一种内部连接机制。

4. 按照总线传输的数据单位分类按照总线传输的数据单位分为串行总线和并行总线。

图3.2为两者示意图。

图3.2 串行总线与并行总线(1)串行总线按位进行传输,每次传输一个位的数据。

串行总线按照所传输数据的方向性,又可分为3种:单工、半双工和双工。

① 单工传输只支持数据在一个方向上传输,除控制信号和电源之外,一般只用一根数据线就够了。

② 半双工数据传输允许数据在两个方向上传输,但两个方向的传输不可同时进行,故除控制信号和电源之外,一般也只用一根数据线就够了。

③ 双工数据传输允许数据同时在两个方向上传输,因此全双工通信是两个单工通信方式的结合。

(2)并行数据每次传输多位,通常有8b 、16b 、32b 和64b 等几种。

所以,并行传输除了控制信号、电源等之外,要传输多少位数据,就需要多少根数据线。

5. 按照发送端与接收端有无共同的时钟分类按照发送端与接收端有无共同的时钟,总线可以分为同步总线与异步总线等类型。

具体将在第3.2节中深入讨论。

6. 按照系统中使用的总线数量分类大多数总线都是以相同方式构成的,其不同之处仅在于总线中数据线和地址线的数目,·157·以及控制线的多少及功能。

按照系统中使用的总线的条数可以分为单总线结构、双总线结构和多总线结构。

如图1.74所示,单总线结构使用一组单一的系统总线来连接CPU 、主存和I/O 设备。

在这类系统中,同一类信息在不同部件间传递时,通过同一组总线,或者说,所有的模块都挂在同一组总线上。

这种总线结构连接灵活、易于扩充。

单总线结构容易扩展成多CPU 系统,这只要在总线上挂接多个CPU 即可。

因所有信息都在一组系统总线上传送,故信息传输的吞吐量受到限制。

双总线结构保持了单总线结构简单、易于扩充的优点,又在CPU 和主存之间有一组专门高速总线,使CPU 可与主存迅速交换信息,而主存不必经过CPU 仍可通过总线与外设之间实现DMA 操作。

这样,缓解了对系统总线和CPU 的压力,提高了系统的效率。

如图1.81所介绍的以存储器为中心的双总线结构。

由于各种设备对于总线的要求不同,在设备不断增加的形势下,总线趋向于分级的总线结构。

图3.3是一种三级总线结构。

图3.3 分级三总线结构这种三级总线结构一般用于I/O 设备性能相差不大的情况。

在高速的视频设备、网络、硬盘等大量涌现的情况下,将它们与低速设备(如打印机、低速串口设备)接在同一条总线上,非常影响系统的效率。

进一步的改进是为这些高速设备设立一条单独的高速总线,形成如图3.4所示的由系统总线、局部总线、高速总线和扩展总线组成的四级总线结构。

图3.4 四级总线结构计算机总线是计算机模块间传递信息的通路。

计算机总线技术包括通路控制性能、使用方法、仲裁方法和传输方式等。

总线技术在整个计算机系统中占有十分重要的位置。

任何系统的研制和外围模块的开发,都必须服从一定的总线规范。

总线的结构不同,性能差别很大。

由于计算机总线的主要职能是负责计算机各模块间的信息传输,所以,对总线性能的衡量,也是围绕着这一职能而定义、测试和比较的。

3.1.3 总线的性能指标总线的主要性能指标有如下几方面。

1. 总线位宽总线位宽也称传送宽度,指总线能同时传送的二进制数据的位数,主要指数据总线的位数,用b(位)表示,如总线宽度有8b、16b、32b、64b之分。

总线的位宽越宽,每秒钟数据传输率越大,总线的带宽越宽。

2. 总线工作的时钟频率总线的工作时钟频率越高,总线的传输率越高。

3. 总线带宽总线带宽即总线标准传输率,指的是单位时间内总线上传送的数据量,即每钞传送兆字节的最大稳态数据传输率。

与总线密切相关的两个因素是总线的位宽和总线的工作频率,它们之间的关系如下:总线带宽 = 总线的工作频率 × 总线的位宽 / 8或者总线的带宽=(总线的位宽 / 8 )/ 总线周期例如,总线工作频率为33MHz,总线宽度为32位,则最大传输率为D r = 4B × 33 × 106 / s = 132MB/s4. 寻址能力寻址能力取决于地址总线的根数。

例如,PCI总线的地址总线为32位,寻址能力达4GB。

5. 是否支持突发传送总线上数据传送方式分为两种。

(1)正常传送——每个传送周期先传送数据的地址,再传送数据。

(2)突发传送——支持成块连续数据的传送,只需给出数据块的首地址,后续数据地址自动生成。

PCI总线支持突发传送,ISA总线不支持。

6. 负载能力负载能力即总线上能够连接的设备数。

·158·7. 总线控制方式总线控制含有突发传输、并发工作、自动配置、仲裁方式、逻辑方式、计数方式等内容。

8. PnP能力PnP(Plug-and-Play,即插即用,也称为热插拔)是由微软公司提出的,意思是系统自动侦测周边设备和板卡并自动安装设备驱动程序,做到插上就能用,无须人工干预,是Windows自带的一项技术。

即插即用是指将符合PnP标准的PC插卡等外围设备安装到计算机时,操作系统自动设定系统结构的技术。

当用户安装新的硬件时,不必再设置任何跳线器开关,也不必用软件配置中断请求(IRQ)、内存地址或直接存储器存取(DMA)通道,Windows会向应用程序通知硬件设备的新变化,并会自动协调IRQ、内存地址和DMA通道之间的冲突。

9. 其他指标除了以上几项指标外,还有如下一些。

(1)传输距离(这一点对I/O总线很重要)。

(2)传输差错率(这一点对I/O总线很重要)。

(3)抗干扰力。

(4)确定性延迟。

(5)同步方式。

(6)信号线数。

(7)是否支持多路复用。

(8)电源电压高低。

(9)能否扩展64位宽度等。

3.1.4标准系统总线表3.1为在微型计算机发展过程中形成的一些主要标准系统总线。

表3.1在微型计算机发展过程中形成的一些主要标准系统总线总线名称开发者推出时间总线位宽/b 工作频率/Hz 带宽/(B/s)负载能力PC-XT IBM 1981年8 4M 4M 8 ISA IBM 1984年16 8M 16M 8 MCA IBM 1987年32 10M 40M 无限制EISA Compaq等 1988年9月32 8.33M 33M 6 PCI Intel\IBM等 1991年32 20~33.3M 133M/528M 3 VESA VESA 1992年32 66M 266M 6 AGP Intel1996年7月32 66.7M/133M 266M/2.133GPCI-E Intel\IBM等 2002年7月串行 2.5G/5G/10G 点对点:4G/16G双向:8G/32G·159·上述这些标准中有些已经被淘汰,有些正在被应用,有些即将被应用。