Cadence 实验系列12_数模混合电路设计_spetreVerilog

20120523-数模混合电路设计流程

数模混合电路设计流程马昭鑫 2012/5/23本文主要面向模拟电路设计者,讲解了从行为级代码形式的数字电路到数模混合版图之间的流程,默认模拟版图和数字电路的行为级代码、testbench已经完成。

阅读者需确定自己会编写Verilog或Spice格式的网表,熟悉Linux的文件操作,了解Spectre、Virtuoso、Calibre、Modelsim、Design Compiler(dc)、Astro等EDA工具的使用方法。

由于本人才疏学浅,经验不足,难免会在文中出现一些错误,恳请高手给予指正。

数模混合电路的仿真方法一般的设计流程中数字电路和模拟电路是分开进行设计的,但有些时候希望能将数字电路和模拟电路放在一起仿真来验证设计,这就需要用到混合电路的仿真方法。

在Cadence 工具中有专门用作混合电路仿真的仿真器spectreVerilog,其实现方法是首先将模拟模块与数字模块区分开并设置接口电平,然后在ADE中设置数字电路的测试代码,调用不同的仿真器分别对数字模块和模拟模块进行仿真,最后将结果汇总显示或输出。

下面将以一个简单实例的形式讲解混合电路的仿真方法。

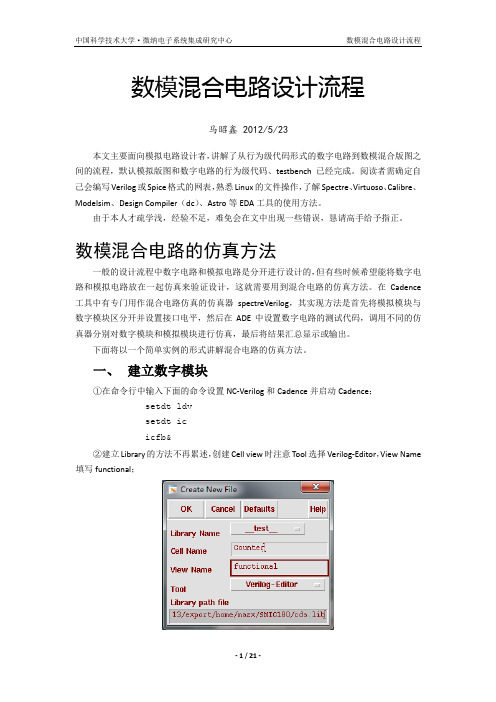

一、建立数字模块①在命令行中输入下面的命令设置NC-Verilog和Cadence并启动Cadence;setdt ldvsetdt icicfb&②建立Library的方法不再累述,创建Cell view时注意Tool选择Verilog-Editor,View Name 填写functional;③点击OK后会弹出有模块代码框架的vi窗口,将设计需要的代码输入或粘贴进去;④保存并关闭后如果没有错误会弹出创建Symbol View的询问对话框,确定后会进入Symbol编辑器,并自动生成了Symbol(注意在Cadence中总线用尖括号<>表示);⑤保存并关闭Symbol编辑器。

至此已经完成了数字模块的创建。

二、建立模拟模块模拟电路的创建方法无需赘述,这里搭建了一个输出频率为10MHz的环形振荡器。

数模混合信号电路设计-第一讲

华侨大学IC设计中心

建立层次文件

1.建立config文件 2.链接顶层文件

Mixed Signal Processing & RF/Analog IC TRx architectures Signal IC Digital ASIC

Multi-band Multimode Antenna Interface

AD

90º

AD

Baseband processing

DA

TRx calibration

数模混合信号仿真华侨大学IC设计中心

3.仿真提速

A:用作信 号发生器。 仿真的时候,需要不少的激励信号,而且有着严格的时序关 系,要是用pulse电源或是别的什么电源来做的话,可要累死 人的。用verilog写模块的foundational,就 可以比较方便快 捷的构成一个信号发生器。

B:节约模拟的时间。 对于一些成熟的已经知道电路输入输出特性的电路,可以用 verilog写出其特性,这样的话,模拟的时间可以大大的缩短。 当然,还有就是verilog 的老本家--数字电路,也可以用 verilog写出foundational,节约模拟的时间。

Ch.1概述5

华侨大学IC设计中心

SIP与SOC是两项平行发展的系统集成技术, 它们都顺应了电子产品高性能、多功能、小型 化、轻量化和高可靠性的发展趋势。从发展的 历程来看,SOC与SIP是极为相似的,两者均 希望将逻辑组件、数字、模拟、无源器件整合 在一个单元中。然而就发展方向而言,两者有 很大的不同:SOC是从设计的角度出发,目的 是将一个系统整合到一块IC芯片上去;而SIP 则是由封装的角度出发,将不同功能的芯片整 合于一个电子封装结构体内。

symbo

Cadence数模混合电路设计_spetreVerilog

Cadence sp芯et片re级v电e路ril验o证g

模拟信号仿真

射频信号仿真

1-2 数模混合信号模拟的应用

混合信号模拟简介

混合模拟的定义 混合模拟的应用

2

1

3

4

1-2 数模混合信号模拟的应用

1. 数模混合电路的设计 2. 大型数字集成电路设计 3. 仿真提速

1-2 数模混合信号模拟的应用

混合信号模拟简介

混合模拟的定义 混合模拟的应用 Cadence中的实现

2

1

3

4

1-3 Cadence 中的Spetreverilog

1. cadence中数模混合仿真的环境 2. cadence中数模混合仿真的数据流

1-3 Cadence 中的Spetreverilog

1. 数模混合仿真的环境

层次编辑器

用高斯消去法 求解线性方程

1-1 数模混合信号模拟定义

2.数字信号模拟

是指基于松弛算法的由事件驱动的:一t种es仿tb真en模ch拟方式。

1

2

3

4

1-1 数模混合模拟的定义

3. 混合信号模拟

以特定的组合方式处理电路中的模拟数字信号的仿真过程

单仿真器架构

模拟 信号

数字 简化信号 模拟 信号

双仿真器架构

模拟 信号

数字 信号

模拟信号 仿真器

模拟信号 仿真器

数字信号 仿真器

1-1 数模混合模拟的定义

3. 混合信号模拟

双仿真器的混合信号模拟

A_D仿真方法组合 A_D仿真器结合度

手工型

顺序型

偶合型

+ 配对型

= spetreverilog

基于Verilog的数字电路设计与仿真实验

基于Verilog的数字电路设计与仿真实验数字电路设计与仿真是数字电子技术领域中非常重要的一部分,Verilog作为一种硬件描述语言,在数字电路设计中扮演着至关重要的角色。

本文将介绍基于Verilog的数字电路设计与仿真实验,包括Verilog语言基础、数字电路设计流程、仿真工具的选择以及实验案例分析等内容。

Verilog语言基础Verilog是一种硬件描述语言,广泛应用于数字电路设计领域。

它具有类似于C语言的语法结构,包括模块化设计、行为建模和结构建模等特点。

在Verilog中,最基本的单元是模块(module),一个模块可以包含输入端口(input)、输出端口(output)和内部信号(wire)。

通过组合这些模块,可以构建复杂的数字电路系统。

Verilog语言中常用的建模方式包括行为建模和结构建模。

行为建模主要描述数字电路的功能行为,而结构建模则描述数字电路的物理结构。

Verilog语言还支持时序描述和并发描述,可以方便地对数字电路进行精确描述和仿真。

数字电路设计流程数字电路设计流程通常包括需求分析、概念设计、详细设计、验证和实现等阶段。

在Verilog中进行数字电路设计时,首先需要明确设计需求,然后进行概念设计,确定整体架构和模块划分。

接下来是详细设计阶段,根据功能需求编写Verilog代码,并进行仿真验证。

最后是实现阶段,将Verilog代码综合成目标设备可实现的逻辑电路。

在数字电路设计流程中,仿真验证是非常关键的一步。

通过仿真可以验证设计的正确性和功能是否符合预期。

Verilog提供了丰富的仿真工具和方法,如ModelSim、Xilinx ISE等,可以对设计进行全面的仿真测试。

仿真工具的选择在进行基于Verilog的数字电路设计与仿真实验时,选择合适的仿真工具至关重要。

ModelSim是一款常用的Verilog仿真工具,它提供了直观的图形界面和强大的仿真功能,能够帮助设计人员快速验证设计的正确性。

SpectreVerilog软件做数模混合仿真简单教程

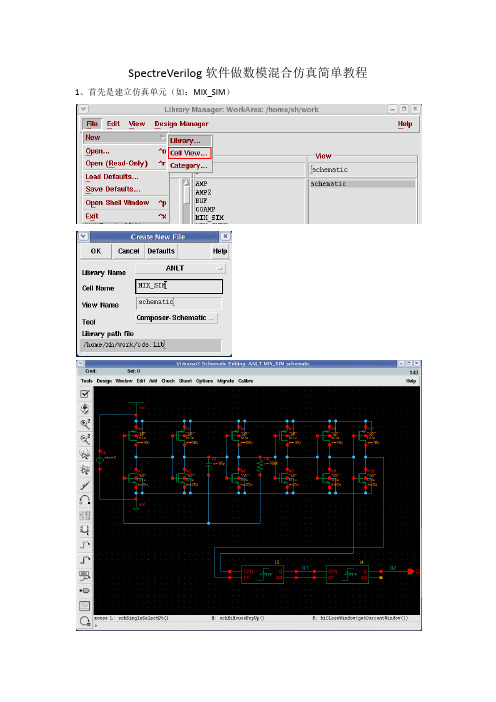

SpectreVerilog软件做数模混合仿真简单教程1、首先是建立仿真单元(如:MIX_SIM)

2、建立config文件,如下图所示,点击OK。

在出现下图表中点击Browse,选择好cell的View=schematic,然后点击OK

然后分别按下面图示操作。

3、打开MIX_SIM的config文件,如下图所示。

4、设置模数转换以及数模转换接口,注意下图所示的设置方法要求数模模数转换接口处用的是functional,设置才有效。

5、打开模拟仿真器,选择模拟软件工具为SpectreVerilog,并填好用于仿真的目录。

6、选择仿真模型库

7、如果需要添加仿真激励信号,按下图操作,加入激励信号,保存退出。

8、选择仿真模式,瞬态仿真的话填入仿真时间以及步长设定。

9、选择探测信号,接着选择出网表并运行仿真。

spectraverilog数模混合仿真

Cadence 的数模混合仿真工具spectraverilog能够实现数字模拟电路联仿的功能,对于模拟电路的输入信号可以利用数字接口很方便的进行设置。

主要用来进行功能仿真。

步骤:

1.准备schematic,如电路单元mix

2.从库管理器中建立mix单元的config view.

在use template中选择spectraverilog,然后ok

将top cell中的myview改为实际的schemtic,然后ok

正确的结果如下图

保存,点击open打开config后的schematic,在tools中选择mix signal opts.

在mix-signal菜单中,尝试第二项的每一个小项,可以看到模拟和数字的相关划分。

由于数字部分默认的电压为5V,转换电平为1.5V和3.5V,因此,如果电路的电源电压不同的与5V,需要对于数模混合接口部分进行设置,在mix-signal菜单中的第三项中进行设置。

对于模拟部分来讲,其按照模型进行计算,无需在数模接口部分进行端口设置,对于数字接口来讲,需要将默认的5V电平以及1.5V,3.5V转换电平变为与模拟部分相符的电压

值,比如电源3V,转换电平为1.5V和3.5V。

设置如下,

对于与模拟器件相连接的数字输出端,将高电平由5V改为3V

对于与模拟器件相连接的数字输入端,将转换电平由1.5V改为3.5V改为1V和2V

所有数模混合接口的相关的数字端口都需要改动,如下图所示的数模接口部分

3.调出analog仿真工具,并设置为spectreverilog

4.编写端口的输入激励文件

设置传输分析的时间长度

5.其余步骤同模拟信号仿真一样,run。

Cadence中Verilog 的一些使用方法

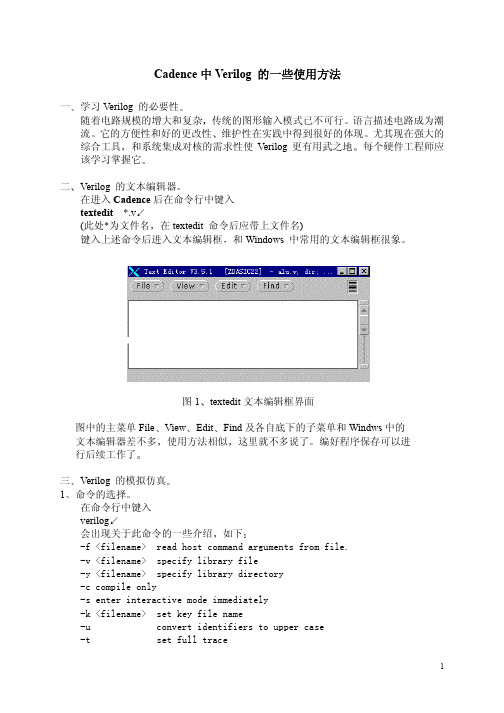

Cadence中Verilog的一些使用方法一学习Verilog 的必要性随着电路规模的增大和复杂传统的图形输入模式已不可行语言描述电路成为潮流它的方便性和好的更改性维护性在实践中得到很好的体现尤其现在强大的综合工具和系统集成对核的需求性使Verilog更有用武之地每个硬件工程师应该学习掌握它二Verilog 的文本编辑器在进入Cadence后在命令行中键入textedit *.v↙(此处*为文件名在textedit 命令后应带上文件名)键入上述命令后进入文本编辑框和Windows 中常用的文本编辑框很象图1textedit文本编辑框界面图中的主菜单File View Edit Find及各自底下的子菜单和Windws中的文本编辑器差不多使用方法相似这里就不多说了编好程序保存可以进行后续工作了三Verilog 的模拟仿真1命令的选择在命令行中键入verilog↙会出现关于此命令的一些介绍如下-f <filename> read host command arguments from file.-v <filename> specify library file-y <filename> specify library directory-c compile only-s enter interactive mode immediately-k <filename> set key file name-u convert identifiers to upper case-t set full trace-q quiet-d decompile data structureSpecial behavioral performance options (if licensed):+turbo speed up behavioral simulation.+turbo+2 +turbo with second level optimizations.+turbo+3 +turbo+2 with third level optimizations.+listcounts generate code for maintaining information for $listcounts +no_turbo don't use a VXL-TURBO license.+noxl disable XL acceleration of gates in all modulesSpecial environment invocation options (if licensed):+gui invoke the verilog graphical environment在上面的参数选择中简单介绍几个常用的:(1)-c首先应该保证所编程序的语法正确性先进行语法的检查选择参数- c键入如下命令verilog –c *.v↙根据Cadence的报告查找错误信息的性质和位置然后进入文本编辑器进 行修改再编译这是个反复的过程直到没有语法错误为止(2)-s进入交互式的环境人机交互运行和下面的参数联合使用(3)+gui &verilog 仿真有命令和图形界面两种方式图形界面友好和windows使用很象很好掌握一般都使用图形方式&”符号是后台操作的意思不影响前台工作如此时你可以在命令行输入其它的命令其它的命令参数选择比较复杂这里就不介绍了故我们这里常用的命令是verilog –s *.v +gui &↙ (*代表文件名)进入图形交互界面$附命令行输入!!↙是执行上一条命令命令行输入!* ↙ (*代表字母)是执行最近的以*开头的命令上述附注对命令输入速度提高有所帮助2SimVision 图形环境SimVision是Verilog-XL的图形环境 主要有SimControl NavigatorSignal Flow Browswer Wactch Objects Window SimWave 等窗口(1)SimControl 窗口此窗口是主要的仿真控制窗口让用户和机器进行交互式操作执行各种Verilog-XL 命令(菜单)进行仿真分析调试你的设计该窗口可以显示设计的模块和模块显示和设置断点强制信号等创建用户自己的按钮和执行经常使用的操作Source Browser2SimControl 窗口界面图I/O RegionMessage Region各部分简介Menu Bar有许多的子菜单让你执行各种模拟仿真命令这里就不一一介绍到使用时在指明其功能和所在位置Tool Bar各种按钮代表最常用的操作和功能能快速对选中的物体执行各种命令你可以在工具条中加入自己定义的按钮来代表常用的操作命令使用Option-UserButtons-Create 菜单项用Options-User Buttons-Edit 菜单项修改修改按钮工具条还显示当前模拟时间当处于交互式的模拟状态时会随模拟更新时间因为工具条按钮的操作为常用操作下面各功能详细介绍一下运行模拟按钮 设置模块按钮 对对象执行操作按钮 调用其它显示窗口按钮放用户自定义按钮 是否显示程序代码 图3SimControl窗口中的工具条a Run Simulation按钮运行模拟若无断点直至完成图标变为停止模拟图标若有断点则运行到断点对应信号再改变的位置b Single Step按钮再任何模块每按一下执行到下一个可执行行即使在子程序中也是单步运行c Step Over 按钮在当前的模块中执行到下一个可执行行在子程序中步单步执行而是一步执行完 子程序d Set Scope 按钮由当前的调试模块转到被选中的模块e Scope Up 按钮由当前模块转到它的上一级模块但若有对象被选中不执行f Show Execution 按钮模拟时更新当前模块显示正在模拟的模块在当前刚执行完的代码行左边有一个箭头g Set Breakpoint 按钮设置断点当模拟过程中被选信号变化时发生代码左边的行号为高亮的可设为断 点灰色则不可以h Set Force 按钮弹出一个窗口里面有当前选中信号的名字和数值用户可以强制信号为一个希望 值i Show Value 按钮n程序代码是否显示的切换按钮显示当前被选信号的数值以下j k l m调用其它调试窗口具体介绍放到后面j打开Navigator窗口k打开Watch Objects 窗口显示被选中的对象l打开Singal Flow Browser窗口把被选中的对象放到浏览器中m打开SimWave窗口显示被选中对象的模拟波形Source Browser显示被调试的程序代码每行左边有行号你可以在其间选择信号和模块这种选择会影响其它工具的操作对象反过来其他工具操作对象的选择也会作用于SourceBrowser信号和对象的选择可在其间设置断点如前所说的在行号为高亮的行可设为断点灰色则不可以可在Source Browser中点鼠标的右键选择菜单进行操作另一个对选择对象的操作是双击该对象如双击信号得到它的数值双击模块则调 到 该模块描述处如图3中的n字母代表的按钮Source Browser可被关掉不显示Scope Region包含scope field 和subscopes field从下拉按钮选择不同的项跳不同的模块对应的Source Browser显示该模块的代码I/O Region显示执行的命令和模拟输出的结果你也可以直接在此键入命令执行操作I/ORegion 也可以被关掉不显示当点击Message Region右边的三角按钮可切换显示与否Message Region显示模拟状态3Navigator 窗口按下图3中j字母所代表的按钮(2)SimControl 窗口Tools-Navigator菜单项(3图8中按下和图3中j字母所代表的按钮一样的按钮打开Navigator窗口此窗口用图形在Scope Tree 中采用树的形式显示设计中各模块的层次关系在Objects List中显出Scope Tree中被选模块的当前模拟数值和描述图4Navigator窗口Menu Bar提供各种命令和操作有下拉菜单(如下面的图5)和右键弹出菜单两种选中对象点击右键可选择对对象操作所需的命令如下面的图6图5 Navigator窗口的菜单图6Navigator中的PoP-Up菜单Tool Bara设置模块 b对选择对象操作 c调用其他显示窗口图7Navigator中的工具条a b c同SimControl窗口中的工具条对应按钮的功能一样都是对选择对象进行相应的操作只是对象可以在SimControl窗口选择也可以在Navigator窗口中 选择互相影响Hierarchy Path显示当前模块的直接路径其他路径不显示可选择其间的模块点击右键弹出菜单进行操作Scope Tree对被选中的模块用树的形式表示出来在图5中Options-Scope Tree…菜单项中有 关于对象显示的的性质有Filters Formatting Layout三栏各有一些选项供 选择影响当前Scope Tree显示的内容Objects List显示当前调试模块里的信号和当前数值在在图5中Options-Objects List…菜单 选项有Filters Formatting两栏会影响Objects List中的显示内容在Selcet 子菜单中的选项(如图5)能选取某一类别的信号如都是Wires型或是Registers 型4Singal Flow Browser窗口该窗口跟踪可疑信号的值进入有三个方法(1) 按下图3中j字母所代表的按钮(2)SimControl 窗口Tools- Singal Flow Browser菜单项 (3) 图7Navigato中 的工具条中字母c的第二个按钮打开窗口(4) Wactch Objects Window中按下图 3中j字母所代表的按钮的一样的按钮界面如下图(没选信号时)8Singal Flow Browser窗口界面Tool Bar Trace fieldMenu对对象的操作命令可查看信号或输入的细节显示信号的驱动可用四种进制显示信号的数值见下图后面会阐述菜单项的功能图8Singal Flow Browser窗口菜单Tool Bar 中的按钮和前面出现的相同的按钮的功能一样这里就不重复了Trace field显示图2 SimControl 窗口Source Browser或者图4Navigator窗口中Objects List所选的信号也可在Trace field输入信号名Driver Frame显示被选的信号和数值以及所有影响该信号的信号及它们的数值假设某个时候的Driver和Value 如下图图9Driver 信号举例如果在上图中选中Driver信号选图8中 View-Driver info…的菜单项将弹出 Driver Details窗口显示信号的详细信息如下图图10Driver 信号Driver Details窗口当选中图9中的Driver 信号选图8中Trace-show inputs菜单项或者双击信 号将得到影响Driver 信号的有关信号的信息如下图图11Driver 信号的inputs信息图再次双击Driver 信号会隐去这些信息5Watch Objects 窗口显示所选信号及其数值当模拟中断时更新数值进入有三个方法(1) 按下图3中k字母所代表的按钮(2)SimControl 窗口Tools- Watch Objects菜单项 (3) 图7Navigator中的工具条中字母c的第一个按钮打开窗口(4) Singal Flow Browser 窗口中按下和图3中k字母所代表的按钮的一样的按钮界面如下图(没选信号时)图12Watch Objects 窗口你可以在打开Watch Objects窗口前选择观察信号如在Source Browser 中点选择信号或在SimControl窗口中(图2)的Select菜单下的菜单项选择或在图4中Navigator窗口的Objects List中选择也可以在打开Watch Objects窗口后 再选择信号如前选择好信号然后点击图12中工具条上的加号图标把选好信号加到窗口中窗口的菜单如下图菜单项的含义都比较明了就不多说了提一下Options-Heighlight Activity项使最新变化的信号项用高亮条表示Options-ContinousUpdate 项使信号随时变化即使按图3中的a Run Simulation按钮也会显示最后的结果否则不显示最后结果图13Watch Objects 窗口的菜单SimWave 窗口显示选择信号的波形和数值图14SimWave 窗口界面四一个示例这里举一个实际工作中编的例子演示前面所讲的内容但不一定面面俱到程序的清单见附录(alu.v)在命令行中敲textedit alu.v↙ 用textedit 编好程序的文本在命令行中敲verilog –c alu.v↙ 编译通过程序.在命令行中敲verilog –s alu.v +gui&↙ 进入交互式图形界面SimControl窗口(见图2)在Scope中选择test.talu在SimControl 窗口中的选中Select-Ports项选择端口按下图3SimControl窗口中的工具条中的k键打开Watch Objects 窗口并如图13选中Options-Continuous ,Highlight Activity两项按下图3SimControl窗口中的工具条中的m键,打开 SimWave 窗口按下图3SimControl窗口中的工具条中的a键,图15Watch Objects 窗口图16SimWave 窗口波形附alu.v源程序module alu(sum,c_out,a,b,c_in,m);output [3:0]sum;output c_out;input [3:0]a,b;input c_in,m;wire c4,cn,cout1;wire [3:0]sum1,a2;assign a2[0]=(b[0]&~m)|(~b[0]&m);assign a2[1]=b[1];assign a2[2]=(b[2]&~m)|(((~b[2]&b[1])|(b[2]&~b[1]))&m);assign a2[3]=(b[3]&~m)|(~b[3]&~b[2]&~b[1]&m);assign {c4,sum1}=a+a2+c_in;assign cn=c4|(sum1[3]&sum1[2])|(sum1[3]&sum1[1]);assign {cout1,sum}=sum1+{1'b0,cn,cn,1'b0}+1'b0;assign c_out=cn;endmodulemodule test;reg [3:0]ta,tb;reg tc,tm;wire [3:0]tsum;wire tcout;alu talu(tsum,tcout,ta,tb,tc,tm);initial$monitor($time,"c_out=%d,sum %d=%d+%d+%d,m=%d",tcout,tsum,ta,tb,tc,tm); initialbeginta=4'b1001;tb=4'b1000;tc=1'b0;tm=1'b0;#10 ta=4'b1001;tb=4'b1001;tc=1'b1;#10 ta=4'b0111;tb=4'b0010;tc=1'b0;#10 tm=1'b1;ta=4'b0111;tb=4'b0010;tc=1'b1;#10 ta=4'b0111;tb=4'b0100;tc=1'b1;#10 ta=4'b0101;tb=4'b0010;tc=1'b1;#10 $finish;endendmodule下图1718是程序对应的电路图图17 BCD码加法器图18 ALU原理图几个打开相关帮助的命令,在命令行中敲入openbook vlogtut&↙ (Verilog-XL Tutorial)openbook vlogref&↙ (Verilog-XL Reference)openbook vloguser&↙ (simwave user guide)openbook simwaveuser&↙ (open the Verilog-XL guide)校内网站ftp10.12.41.35有PC机版Verilog仿真工具如Modelshim,Active HDL4.2版Xilinx的FPGA等等还有Cadence 的一些资料如Verilog-XL Referenceuser_guide等等。

以DAC为例介绍SpectreVerilog数模混合电路仿真方法

以DAC为例介绍SpectreVerilog数模混合电路仿真方法来源:EETOP BBS 作者:真我个性(eetop id名)1.先谈下cadence IUS 和cadence ic,nc-verilog,spectre的关系cadence ic用于模拟仿真的软件,cadence IUS用于数字仿真的软件。

如果只做模拟,那用ic就够了。

同理,如果只做数字,那用IUS 也就够了。

但如果做数模混合,既有数字又有模拟,那两个软件都需要安装。

cadence ic cadence IUS如同spectre是cadence ic的模拟仿真器,nc-verilog是IUS的数字仿真器。

因此,如同装上cadence ic就能用spectre一样,装上cadence IUS就能用nc-verilog。

2. 数模混合电路中数字和模拟的实现数模混合电路中的模拟部分包括运放,开关电容等,数字部分包括开关电容中的控制信号等。

本文模拟部分就是DAC,但是例程中的DAC并不是用实际的电路实现的,而是采用verilog A代码来描述其行为模型的。

代码如下:数字部分就是给DAC提供一些列的数字输入信号,采用的是数字语言verilog实现的,代码如下:所有代码,其中DAC8bit_spectreverilog.tar.gz是cadencelibrary,解压后可直接在cadence中仿真运行。

DAC8bit_spectreverilog.zip (24.61 KB) (本文最后的压缩包中也有该文件)数模混合电路仿真时数字电路采用nc-verilog仿真器,模拟电路用spectre仿真器,最后把结果合在一起。

具体的设置步骤参考下文:VerilogA_Creating & simulating an 8-bit D-A Converter (DAC)_spectreverilog.pdf (605.61 KB) (本文最后的压缩包中也有该文件)总电路仿真结果3. 参考资料“数模混合电路设计流程_中科大”:介绍很完整,很严谨。

数模混合仿真设计流程详解

数模混合仿真设计流程详解

数模很合仿真可以提高cadence仿真的速度,使用spectreverilog进行仿真。

首先需要安装IUS9.2数字电路的仿真器,verilogXL。

否则不会启动的!!!!!我一开始用的是ic514后来发现我没有安装IUS,同时虚拟机没有空间了,于是我就把IUS装到了ic615上,所以前面的界面是514后边会有615的界面,大同小异。

按照步骤来,我相信大家都会学会的。

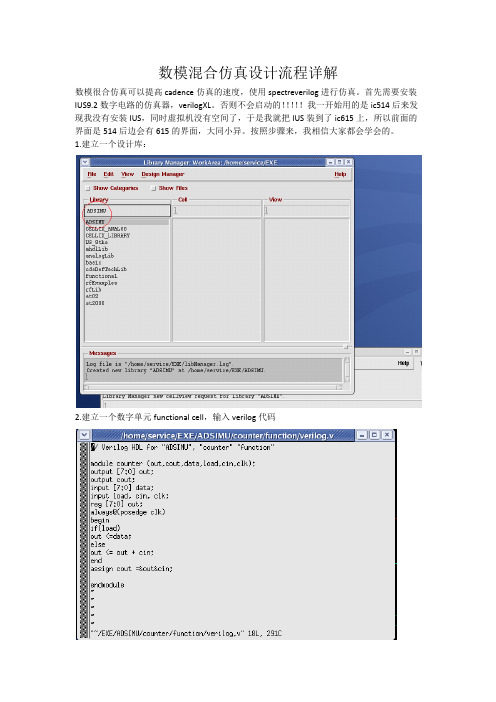

1.建立一个设计库:

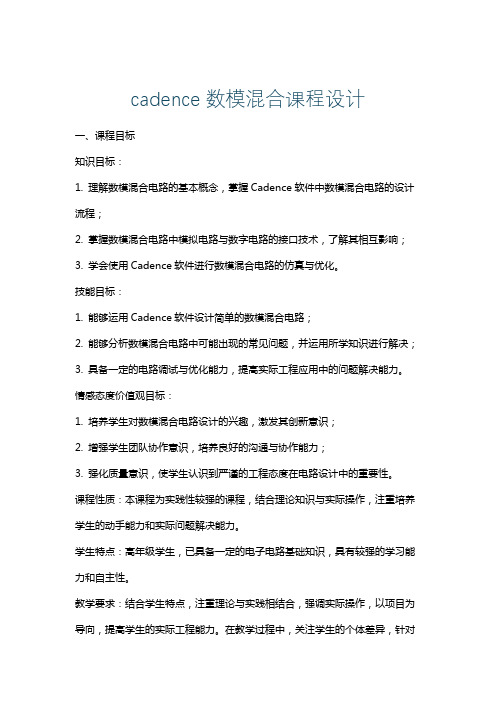

2.建立一个数字单元functional cell,输入verilog代码

输入代码完成后创建符号图

3.创建模拟电路

5.建立config文件

6.建立spectreverilog模板

进入mix模式,打开simu的config文件后再进入mix模式

ic6151

仿真器改成spectreVerilog

设置数字电路和模拟电路的仿真激励

编辑测试激励语句

设置仿真时长与步长

仿真结果如下

需要注意的是数字和模拟电路的接口电平设置,何为1何为0。

需要在下图所示中设置

输入输出都需要设置,高电平何为1低电平何为0。

一般情况下是默认值,如果默认值不太合适的话,会导致逻辑错误。

所以需要手工设置一下。

这个地方我还没有研究明白,应该会

选择 一下针对CELL或者lib或者pin。

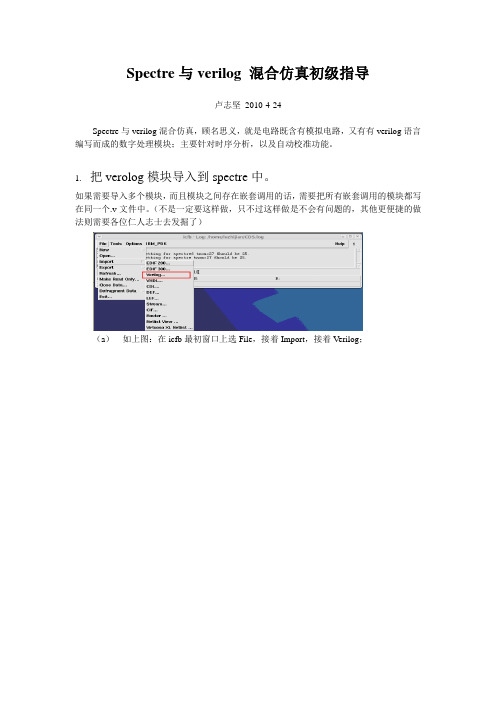

cadence数模混合课程设计

cadence数模混合课程设计一、课程目标知识目标:1. 理解数模混合电路的基本概念,掌握Cadence软件中数模混合电路的设计流程;2. 掌握数模混合电路中模拟电路与数字电路的接口技术,了解其相互影响;3. 学会使用Cadence软件进行数模混合电路的仿真与优化。

技能目标:1. 能够运用Cadence软件设计简单的数模混合电路;2. 能够分析数模混合电路中可能出现的常见问题,并运用所学知识进行解决;3. 具备一定的电路调试与优化能力,提高实际工程应用中的问题解决能力。

情感态度价值观目标:1. 培养学生对数模混合电路设计的兴趣,激发其创新意识;2. 增强学生团队协作意识,培养良好的沟通与协作能力;3. 强化质量意识,使学生认识到严谨的工程态度在电路设计中的重要性。

课程性质:本课程为实践性较强的课程,结合理论知识与实际操作,注重培养学生的动手能力和实际问题解决能力。

学生特点:高年级学生,已具备一定的电子电路基础知识,具有较强的学习能力和自主性。

教学要求:结合学生特点,注重理论与实践相结合,强调实际操作,以项目为导向,提高学生的实际工程能力。

在教学过程中,关注学生的个体差异,针对性地进行指导,确保课程目标的实现。

通过课程学习,使学生能够独立完成数模混合电路的设计与优化,为后续相关课程和实际工作打下坚实基础。

二、教学内容1. 数模混合电路基本概念:包括模拟电路、数字电路特点,数模混合电路的定义及其在电子系统中的应用。

教材章节:第二章 数模混合电路基础2. Cadence软件操作:介绍Cadence软件的基本操作,原理图绘制,电路仿真等。

教材章节:第三章 Cadence软件操作3. 数模混合电路设计流程:讲解从电路设计、原理图绘制、仿真测试到PCB 设计的完整流程。

教材章节:第四章 数模混合电路设计流程4. 接口技术:分析模拟电路与数字电路之间的接口技术,包括信号转换、阻抗匹配等。

教材章节:第五章 接口技术5. 电路仿真与优化:介绍仿真方法,参数设置,优化策略等,提高电路性能。

数模混合电路设计

Mixed Analog and Digital IC Design

ADC

DAC

Vout

Spectrum Analyzer

© 2008 H. K. Page 54

Data Converter Basics

Data Converter Performance Metrics

Mixed Analog and Digital IC Design

© 2008 H. K. Page 50

Data Converter Basics

Static Measurement

Example: Hiding Problems in the Noise

DNL/INL Measurement – Histogram Testing

Input with known PDF; amplitude & offset don’t matter Ramp: uniform pdf, difficult with high purity generation Sine: ”bath-tub” shape PDF, IEEE standard

Data Converter Basics

Dynamic Performance

Discrete Fourier Transform (DFT) Properties

• DFT of N samples spaced Ts=1/fs seconds:

– N frequency bins from DC to fs – Bin m represents frequencies at m * fs /N [Hz]

模拟数字混合仿真指导(DOC)

Spectre与verilog 混合仿真初级指导卢志坚2010-4-24Spectre与verilog混合仿真,顾名思义,就是电路既含有模拟电路,又有有verilog语言编写而成的数字处理模块;主要针对时序分析,以及自动校准功能。

1.把verolog模块导入到spectre中。

如果需要导入多个模块,而且模块之间存在嵌套调用的话,需要把所有嵌套调用的模块都写在同一个.v文件中。

(不是一定要这样做,只不过这样做是不会有问题的,其他更便捷的做法则需要各位仁人志士去发掘了)(a)如上图:在icfb最初窗口上选File,接着Import,接着Verilog;(b)接着在弹出的窗口“Verilog In”中,如上图,只关心红框标注的4个地方,在第2个红框处,可以浏览到需要把文件导入的目标库“test_lu”;在第一个大框中,可以浏览到逆需要导入的try.v,选中后,点击第3各红框“Verilog Files To Import”右边的“Add”;在第4个红框中“Import Structural Modules As”选“functional”;其他可以不用管吧,不过尽量与截图一致的话会比较顺利的。

最后点击“OK”,然后等一会,会提示导入完成,提示逆查看以下信息,如果导入不成功,很可能是你的.v文件没有写好,需要修正以下,然后再做导入工作。

(c)如上图,导入成功以后,在“Library Manager”中的库“test_lu”中,“Cell”一栏下就会出现所导入的所有模块,每个模块都有“functional”与“symbol”两个View。

2.把数字模块添加到schematic中(a)如上图,Cell“test_dft”只有schematic View,打开之,如下图(b)按照一般的添加instance的步骤,把数字模块“digital_3”加进来,如下图(c)保存好,然后关掉schematic View“config”,然后回车,就会弹出下图(e)“Library Name”与“Cell Name”明显是不用改的,而“Tool”需要选到“Hierarchy-Editor”,之后“View Name”自动变为“config”,然后“OK”,则继续弹出下图的两个窗口“New Configuration”和“hierarchy-editor”(f)如上图,在“New Configuration”窗口中,在View处浏览,弹出下图浏览窗口(g)选中test_dft中的schematic,之后“OK”,然后又回到“New Configuration”窗口,点击“Use Template…”, 如下图(h)之后会弹出“Use Template”窗口,如下图,在“Name”中选中“spectreV erilog”,之后“OK”;(i)然后“New Configuration”窗口中的有关信息被填好,如下图,然后“OK”(j)然后刚才空着的“hierarchy-editor”窗口,会被填满信息,该信息都是关于schematic View中的信息,如下图(k)然后可以保存,则完成该config View的设置,然后关闭该窗口。

集成电路设计CAD_EDA工具实用教程1-Spectre_Verilog数模混合仿真

共27页

26

THANK YOU!

共27页

27

同时包含模拟和数字两个仿真核

处理速度快,能处理的电路规模极大,但需要解决模拟仿真核和数字 仿真核之间的通信问题;另外,由于数字逻辑仿真器和模拟仿真器的输 入、输出数据是不一样的,还必须在模拟仿真核和数字仿真核之间实现 模拟信号和数字信号的相互转换。

共27页

Q&A

9

Creating Analog Block

共27页

8

Mixed-Signal Simulator 的基本结构

以模拟电路仿真器为核心

在处理数模混合电路时将数字部分等效为相应的简化的模拟电路、或 者采用解析函数来表示逻辑模块的行为,然后对整个系统采用模拟电路 的方法进行模拟。优点:模拟结果精确、能处理的电路规模比较大,模 拟速度也有显著提高。缺点:比逻辑模拟器还是慢很多。

共27页

24

Submit the Simulation

Execute the simulation job with Run, or create the netlist with Netlist

start simulation

共27页

25

Results

数 字 输 出 数字 /模 拟输 入

模 拟 输 出

选择SpectreVerilog

共27页 23

Choose Analysis Type

Invoke the analysis setting window

For Mixed-Signal simulation, only tran is meaningful Set the simulation time Check this box to enable this simulation

SpectreVerilog仿真使用方法

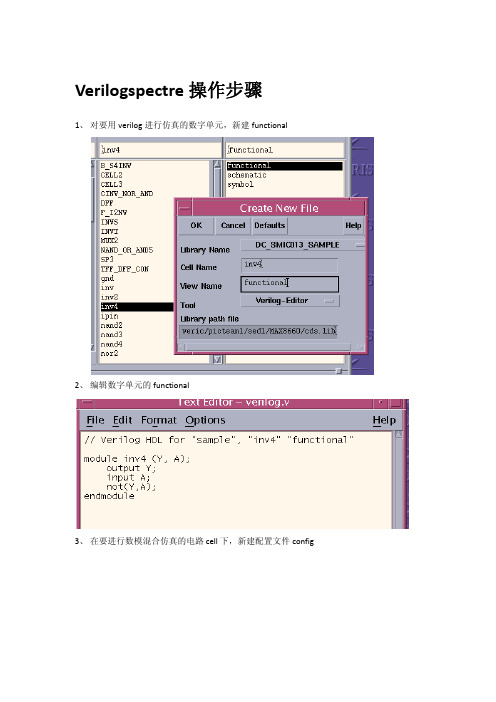

Verilogspectre操作步骤

1、对要用verilog进行仿真的数字单元,新建functional

2、编辑数字单元的functional

3、在要进行数模混合仿真的电路cell下,新建配置文件config

4、配置文件config建立后,自动弹出初始化配置窗口。

单击Browse,将config文件链接到

要数模混合仿真的电路原理图文件,点击OK保存。

5、点击Use Template… 选择要数模混合仿真的模板,这里选择spectreVerilog。

单击OK完

成初始化。

6、对要数模混合仿真的电路进行配置。

如下,将sample库内的数字单元设置用verilog仿

真,在view found栏内显示functional,表示其已经设置成数字仿真。

如果需要用模拟仿真,右击此栏,弹出如下子窗口,选择用schematic。

7、配置完成后单击保存,退出配置窗口。

双击config弹出如下窗口,上面表示打开配置文

件,下面表示打开原理图文件,这里已经配置完成,只打开原理图文件。

8、打开电路原理图后,点击tools‐> analog enviroment,弹出仿真对话框,点击setup,选

择simulator/Directory/Host…

9、弹出选择仿真器窗口,在simulator栏内选择spectreverilog作为仿真工具,点击OK。

自

动载入数模混合仿真环境。

接下来设置和spectre仿真相同,不再赘述。

数模混合仿真详细文档.

用 SpectreVerilog 进行模数混仿,以 Sigma-Delta ADC为例SpectreVerilog 模数混仿 , 模拟部分用 Spectre, 数字部分用 Verilog-XL. 所以还需要安装 Cadence LDV软件 , 其内含 Verilog-XL 仿真器 .这里以自行设计的二阶全差分 Sigma-Delta ADC为例 , 详细介绍用SpectreVerilog 的仿真过程 . 所用工艺库为 TSMC 0.18u,电源电压:1.8V.1. 准备Sigma-Delta ADC分模拟和数字部分两块 , 其中模拟部分为调制器 , 数字部分为数字滤波器 . 如下图 . 其中 out 为调制器的输出 , 这里是 1位 0, 1数据流 . 数字滤波器为 Verilog RTL级代码 .Schematic :Symbol :Verilog Code:module DigitalFilter (in2out, out, clk, clr, in;output in2out;output [`wordsize-1:0] out;input clk;input clr;input in;reg in2out;wire clk_half1, clk_half2;……Endmodule同时为了直观的观看输出结果,因此把输出的数字字转化为模拟量,这里用Verilog-A 做一个理想的 DA 转换器。

因此最好事先用 Spectre 仿真模拟部分 , 用 ModelSim 或 Verilog-XL 等仿真数字部分 . 这里假定我们已有 :1 模拟部分的原理图 (包括 Symbol;2 数字部分的 Verilog 代码 ,DigitalFilter.v, 模块名 :DigitalFilter(in2out,out,clk, clr,in;3 数字部分的 TestBench 代码 , DigitalFilter_TB.v, 模块名 : DigitalFilter_TB. 下图为最终的系统图:2. 创建数字模块的 Symbol1 新建一个 Cell, View Name为symbol, Tool: Composer-Symbol.2 画 Symbol. 简单地 , 画一个矩形框 , 添加几个 Lable, 然后添加 Pin.3 添加 Pin. 左边输入 , 右边输出 . 对于多位的 pin 可以用如 out<7:0>的样式作为 pin 的名字 . 注意 : 与模拟部分相连的多位 Pin 最好不要用一个 pin, 而要用多个 . 如下图 .4 创建对应的 Verilog 文件 . 在 symbol 编辑器中 , Design菜单 ->CreatCellView->FromCellView.会弹出的对话框 , Tool/Data Type一栏选择 Verilog-Editor, 则 To View Name会变为functional.点击 OK, 会弹出错误对话框 , 点 No. 自动弹出 VI 编辑器 , 可以看到已经生成Verilog 代码的空壳 .代码文件的路径在 VI 编辑器的标题栏上 . 下面要做的就是把我们的数字模块(不是 TestBench 的代码填进去 . 如果不想用 VI 编辑器 , 也可以用其他文本编辑器 . 复制代码时最好不要动自动生成的代码 . 经测试 , 所有代码最好放在一个文件中 .这一步之后,数字部分就会有 functional 和 symbol 两个 View 。

由Cadence开发的电路仿真器

演示

单击此工处具编栏辑介母绍版标题样 式

背景

Spectre

Ultrasim

24/105

Spectre-Verilog

演示

单击此A处na编ly辑se母s菜版单标题样 式

选择仿真类型。Spectre 的分析有很多种,如右图 所示,最基本的有: tran(瞬态分析) dc(直流分析) ac(交流分析)

• Spectre:由Cadence开发的电路仿真器,在SPICE的基 础上进行了改进,使得计算的速度更快,收敛性更好。

背景

Spectre

Ultrasim

5/105

Spectre-Verilog

演示

单击C此ad处en编c辑e软母件版简标介题样 式

Cadence 提供了一个大型的EDA软件包,它包括: • ASIC设计

• 启动Cadence • 建立可进行Spectre仿真的单元文件 • 编辑可进行Spectre仿真的单元文件 • 仿真环境的设置(重点) • 仿真结果的显示以及处理 • 分模块仿真(建立子模块) • 仿真实例

背景

Spectre

Ultrasim

7/105

Spectre-Verilog

演示

单击C此ad处en编c辑e软母件版启标动题样 式

背景

Spectre

Ultrasim

20/105

Spectre-Verilog

演示

单击此处附编加辑功母能版标题样 式

快捷键:F3

背景

Spectre

Ultrasim

21/105

Spectre-Verilog

演示

单仿击真此环处境编的辑设母置版(标 重题 点样 ) 式

Composer-schematic界面中的Tools->Analog Environment

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1-1 数模混合模拟的定义

3. 混合信号模拟 Cadence spetreverilog解决方案 混合仿真环境

Verilog-XL Spetre IPC = interprocess communication

仿真输出数据库

1-1 数模混合信号模拟定义

4. 商用混合信号仿真技术 Cadence Muti-Mode仿真(MMSIM)解决方案

2-1 数字-模拟电路设计

3.模拟电路设计 1.建立一个schemetic元件

2-1 数字-模拟电路设计

3.模拟电路设计 2.绘制schemetic原理图

2-1 数字-模拟电路设计

3.模拟电路设计 2.绘制schemetic原理图

元件规格: Pmos Nmos W 2.5u W 2.5u L 500n L 500n

1.数-模电路设计 1.建立一个verilog元件

2-1 数字-模拟电路设计

2.数字电路设计 2.输入verilog代码

2-1 数字-模拟电路设计

2.数字电路设计 3.生成symbol视图

verilog

symbo

2-1 数字-模拟电路设计

2.数字电路设计 3.生成symbol视图

2-1 数字-模拟电路设计

Res

Cap Vdc

200k

10p 5

2-2 制作顶层文件

混合信号模拟的实现

数字设计 模拟设计

数字-模拟电路设计

制作顶层文件

制作顶层文件

建立层次化文件

配置仿真环境 仿真验证

2-2 制作顶层文件

1 实际操作中,我们把clk_01 schematic作为顶层文件,直 接导入counter_01.

2-3 建立层次文件

层次编辑器

Hierarchy-Editor

屏幕输出

Spetreverilog 仿真器

波形文件

顶层原理图

SchematicWindow 用户定义文件

1-3 Cadence 中的Spetreverilog

2. 数模混合仿真的数据流

2-1 数字-模拟电路设计

混合信号模拟简介

数字设计 模拟设计

2 1

混合信号模拟的实现

2. 配置仿真环境 4.设置数字仿真器激励

2-4 设置仿真环境

2. 配置仿真环境 5.设置仿真的时长与步长

2-4 设置仿真环境

2. 配置仿真环境 6.设置绘图节点

3-1 混合信号的模拟的特点

混合信号模拟简介

混合信号模拟的实现

1

2 3 4

混合信号模拟的特点

操作示例

3-1 混合信号的模拟的特点

1 仿真的文件 2 仿真器的工作模式 3 仿真器的激励

时钟发生器 Verilog-editor

计数器

2-1 数字-模拟电路设计

1.数-模电路设计

Lib

Counter_1

Verilog symbo

Clk_1

schem

2-1 数字-模拟电路设计

1.数-模电路设计

1 建立自己的设计库 名字 design_101

2-1 数字-模拟电路设计

1.数-模电路设计 1.建立一个设计库

操作示例

1-1 数模混合信号模拟定义

1.模拟信号模拟仿真

2.数字信号模拟仿真 3. 混合信号模拟仿真 4. 商用混合信号模拟仿真

1-1 数模混合信号模拟定义

1.模拟信号模拟

指基于节点积分分析的瞬态模拟仿真方法

f1(x1, x2,…) =0 f2(x1, x2,…) =0 …

…

…

用高斯消去法 求解线性方程

3-1 混合信号的模拟的特点

1.仿真的文件

混合信号 模拟信号

config

schematic

3-1 混合信号的模拟的特点

2.仿真器的工作模式

混合信号 模拟信号

spectreVerilog

spectre

3-1 混合信号的模拟的特点

3.仿真器的激励

混合信号 模拟信号

Analog & Digital

Analog

2.数字电路设计 3.生成symbol视图

2-1 数字-模拟电路设计

2.数字电路设计 3.生成symbol视图

2-1 数字-模拟电路设计

3.模拟电路设计

1 在设计库中使用Composer-Schemetic建立一个元件 名字 clk_01 视图 schematic

2 编辑 schematic文件,输入clk_01的电路图

1-2 数模混合信号模拟的应用

2.大型数字系统仿真

大部分电路使用verilog仿真器仿真; 指定的关键部分电路使用模拟仿真器以达到高精度.

1-2 数模混合信号模拟的应用

3.仿真提速

A:用作信 号发生器。 仿真的时候,需要不少的激励信号,而且有着严格的时序关 系,要是用pulse电源或是别的什么电源来做的话,可要累死 人的。用verilog写模块的foundational,就 可以比较方便快 捷的构成一个信号发生器。

Cadence 实验系列12_ 数模混合电路设计_spetreVerilog

数模混合电路设计流程

算法设计

数字设计

模拟设计

数模混合验证

数字版图

模拟版图 数模混合验证 Tape-out

目录

混合信号模拟简介

2 1 4 3

混合信号模拟的实现

混合模拟的应用

混合模拟的定义

混合信号模拟的特点

Cadence中的实现

混合信号模拟的实现

数字设计 模拟设计

数字-模拟电路设计

制作顶层文件

制作顶层文件

建立层次化文件

建立层次文件

配置仿真环境 仿真验证

2-3 建立层次文件

1 建立config文件 元件名 clk_01 视图 工具 config Hierarchy Editor

2 把config文件链接到顶层文件 3 把模板选为spetreVerilog 4 把相应的单元分别设置为verilog仿真和spetre仿真

制作顶层文件

数字-模拟电路设计

制作顶层文件

4

3

建立层次化文件

混合信号模拟的特点

建立层次文件

配置仿真环境

设置仿真环境 操作示例 仿真

仿真验证

2-1 数字-模拟电路设计

1.数-模电路设计

2.数字电路设计 3. 模拟电路设计

2-1 数字-模拟电路设计

1.数-模电路设计

schemetic

schemetic

混合信号仿真

Cadence 芯片级电路验证 spetreverilog

模拟信号仿真

射频信号仿真

1-2 数模混合信号模拟的应用

混合信号模拟简介

2 1 4 3

混合模拟的定义

混合模拟的应用

1-2 数模混合信号模拟的应用

1. 数模混合电路的设计

2. 大型数字集成电路设计 3. 仿真提速

1-2 数模混合信号模拟的应用

双仿真真器

模拟信号 仿真器

数字信号 仿真器

1-1 数模混合模拟的定义

3. 混合信号模拟

双仿真器的混合信号模拟

A_D仿真方法组合

A_D仿真器结合度 顺序型

手工型

偶合型 扩展型

+

配对型 单模式

=

spetreverilog

巢套型 偶合型--配对型--锁步” (lock-step)同步法 集成型 = Cadence spetreverilog 框架型

2-1 数字-模拟电路设计

2.数字电路设计

1 在设计库中使用Verilog-editor建立一个元件 名字 counter_01 视图 functional 2 编辑 verilog文件,输入counter_1代码 3 符号化counter_01, 生成symbol视图

2-1 数字-模拟电路设计

B:节约模拟的时间。 对于一些成熟的已经知道电路输入输出特性的电路,可以用 verilog写出其特性,这样的话,模拟的时间可以大大的缩短。 当然,还有就是verilog 的老本家--数字电路,也可以用 verilog写出foundational,节约模拟的时间。

1-3 Cadence 中的Spetreverilog

1-1 数模混合信号模拟定义

2.数字信号模拟

是指基于松弛算法的由事件驱动的一种仿真模拟方式。 松弛算法 事件驱动 : testbench

1

2

3

4

1-1 数模混合模拟的定义

3. 混合信号模拟

以特定的组合方式处理电路中的模拟数字信号的仿真过程

单仿真器架构

模拟

信号 数字 简化 信号 模拟 信号 模拟 信号

混合信号模拟简介

混合信号模拟的实现

2 1 4 3

混合信号模拟的特点

操作示例

Thank you!

1. 数模混合设计

1-2 数模混合信号模拟的应用

1. 数模混合设计

数模IC

传感器

滤波器

A/D

信号处理器

D/A

放大器

接收器

1-2 数模混合信号模拟的应用

1. 数模混合设计

算法设计

数字设计

模拟设计

数字设计

模拟设计

混合原理图 数模混合验证 建立层次化文件

数字版图

模拟版图 配置仿真环境 数模混合验证 仿真验证 Tape-out

2-3 设置仿真环境

1.进入Mixed signal模式

2-4 设置仿真环境

2.设置模式层次显示

2-4 设置仿真环境

2.设置Analog环境 1.设置仿真器工作模式

2-4 设置仿真环境

2. 配置仿真环境 2.设置引用工艺库