Cadence数模混合电路设计

数模混合仿真详细文档.

用 SpectreVerilog 进行模数混仿,以 Sigma-Delta ADC为例SpectreVerilog 模数混仿 , 模拟部分用 Spectre, 数字部分用 Verilog-XL. 所以还需要安装 Cadence LDV软件 , 其内含 Verilog-XL 仿真器 .这里以自行设计的二阶全差分 Sigma-Delta ADC为例 , 详细介绍用SpectreVerilog 的仿真过程 . 所用工艺库为 TSMC 0.18u,电源电压:1.8V.1. 准备Sigma-Delta ADC分模拟和数字部分两块 , 其中模拟部分为调制器 , 数字部分为数字滤波器 . 如下图 . 其中 out 为调制器的输出 , 这里是 1位 0, 1数据流 . 数字滤波器为 Verilog RTL级代码 .Schematic :Symbol :Verilog Code:module DigitalFilter (in2out, out, clk, clr, in;output in2out;output [`wordsize-1:0] out;input clk;input clr;input in;reg in2out;wire clk_half1, clk_half2;……Endmodule同时为了直观的观看输出结果,因此把输出的数字字转化为模拟量,这里用Verilog-A 做一个理想的 DA 转换器。

因此最好事先用 Spectre 仿真模拟部分 , 用 ModelSim 或 Verilog-XL 等仿真数字部分 . 这里假定我们已有 :1 模拟部分的原理图 (包括 Symbol;2 数字部分的 Verilog 代码 ,DigitalFilter.v, 模块名 :DigitalFilter(in2out,out,clk, clr,in;3 数字部分的 TestBench 代码 , DigitalFilter_TB.v, 模块名 : DigitalFilter_TB. 下图为最终的系统图:2. 创建数字模块的 Symbol1 新建一个 Cell, View Name为symbol, Tool: Composer-Symbol.2 画 Symbol. 简单地 , 画一个矩形框 , 添加几个 Lable, 然后添加 Pin.3 添加 Pin. 左边输入 , 右边输出 . 对于多位的 pin 可以用如 out<7:0>的样式作为 pin 的名字 . 注意 : 与模拟部分相连的多位 Pin 最好不要用一个 pin, 而要用多个 . 如下图 .4 创建对应的 Verilog 文件 . 在 symbol 编辑器中 , Design菜单 ->CreatCellView->FromCellView.会弹出的对话框 , Tool/Data Type一栏选择 Verilog-Editor, 则 To View Name会变为functional.点击 OK, 会弹出错误对话框 , 点 No. 自动弹出 VI 编辑器 , 可以看到已经生成Verilog 代码的空壳 .代码文件的路径在 VI 编辑器的标题栏上 . 下面要做的就是把我们的数字模块(不是 TestBench 的代码填进去 . 如果不想用 VI 编辑器 , 也可以用其他文本编辑器 . 复制代码时最好不要动自动生成的代码 . 经测试 , 所有代码最好放在一个文件中 .这一步之后,数字部分就会有 functional 和 symbol 两个 View 。

推荐-数模混合信号电路设计数字电路设计流程 精品 精

行为综合:是指从系统算法级的行为描述到寄存 器传输级(RTL)结构描述的转换

逻辑综合:是从RTL级描述到门级逻辑级的转换 版图综合:是从门级描述到产生相应版图的综合

综合方法

二、行为综合

行为综合是一种高层次的综合,它的任务是实 现从系统算法级的行为描述到寄存传输级结构描 述的转换。这里所说的行为是数字系统或其部件 与外界环境的相互关系与作用;而结构是指组成 系统RTL级的各个部件及其相互之间的连接关系。

Top-Down 设计步骤

4、物理实现(版图设计)

逻辑综合生成门级网表,可以有两种硬件实现 选择。第一种是由自动布局布线工具,如 Silicon Enemble, 生成ASIC版图。第二种是将 网表转换成FPGA(现场可编程门阵列)映射文件, 由FPGA硬件实现。

Top-Down设计与Bottom-Up设计相比,

2.版图设计(后端设计)

版图设计就是根据逻辑网表进一步设计集成电路的物 理版图,也就是制造工艺所需的掩膜版的版图。

设计方法

1、Bottom-Up(之下而上) 2、Top-Down (之上而下)

设计方法

1、Bottom-Up

自底向上(Bottom-Up)设计是集成电路和PCB 板的传统设计方法,该方法盛行于七、八十年

采用Verilog/VHDL语言描述电路时,我们 将电路的描述分为行为(Behavioral)和 寄存器传输级(Register Transfer Level) 和门级描述(Gate Level)三个层次。这 样的划分是根据寄存器辑都不明确

RTL级:寄存器明确,组合逻辑不明确。

综合过程是将HDL描述转换成非优化的布尔等式的描述, 也就是门级描述,该转换过程是综合软件自动完成的, 其过程不受用户控制。采用一定的算法和规则,在约束 条件控制下使非优化的布尔等式进一步转换成优化的布 尔描述,这就是逻辑优化的过程。

cadence工具介绍

标签:cadence工具介绍cadence工具介绍主要是cadence的常用工具:(一)System & Logic Design & Verification 1、SPW:系统仿真工具,与matlab相似,但是比其专业,用于系统建模,常用于通信系统2、Incisive:就是大家最常用的nc_verilog, nc_sim, nc_lauch,以及ABV,TBV的集合,仿真和验证功能很强大(二)Synthesis & Place & Route 1、BuildGates:与DC同期推出的综合工具,但是在国内基本上没有什么市场,偶尔有几家公司用2、RTL Complil er:继BuildGates之后的一个综合工具,号称时序,面积和功耗都优于DC,但是仍然无法取代人们耳熟能详的DC 3、Silicon Ensemble & PKS: 硅谷早期做物理设计的工程师,几乎都用它。

是第一个布局布线工具4、First Encount er & SoC Encounter: 继SE以后的很好的P&R工具,但是盗版太少,所以也只有大公司能用且都用,但是目前astro在国内有赶超之意5、Cetlic :噪声分析工具,权威6、Fire&Ice: 分布参数提取工具,国内很多人用synopsys的StarRC 7、VoltageStrom:静态功耗和动态功耗分析的很不错的工具,与s 的Power Complier相同。

8、SingnalStrom:时序分析工具,唯一一个能建库的工具9、nanoroute : 很强大的布线器喔,但是不是一般人能用的到的。

我也是在cadence实习的时候爽过的,比astro快十倍不止。

(三)custom IC Design 1、Virtoso:版图编辑工具,没有人不知道吧,太常用了,现在还有一个公司的laker 2、diva, dracula, assura: 物理验证工具,用的比较普遍,但是calibre是标准,很多公司都是用其中的一个和calibre同时验证,我好可怜,现在只能用herculus (四)数模混合信号设计这部分太多了,但是一个ADE的环境基本上都能包括,不细说了,打字都打累了(五)PCB A llego最为典型了,很多大公司都用的。

Cadence数模混合电路设计_spetreVerilog

Cadence sp芯et片re级v电e路ril验o证g

模拟信号仿真

射频信号仿真

1-2 数模混合信号模拟的应用

混合信号模拟简介

混合模拟的定义 混合模拟的应用

2

1

3

4

1-2 数模混合信号模拟的应用

1. 数模混合电路的设计 2. 大型数字集成电路设计 3. 仿真提速

1-2 数模混合信号模拟的应用

混合信号模拟简介

混合模拟的定义 混合模拟的应用 Cadence中的实现

2

1

3

4

1-3 Cadence 中的Spetreverilog

1. cadence中数模混合仿真的环境 2. cadence中数模混合仿真的数据流

1-3 Cadence 中的Spetreverilog

1. 数模混合仿真的环境

层次编辑器

用高斯消去法 求解线性方程

1-1 数模混合信号模拟定义

2.数字信号模拟

是指基于松弛算法的由事件驱动的:一t种es仿tb真en模ch拟方式。

1

2

3

4

1-1 数模混合模拟的定义

3. 混合信号模拟

以特定的组合方式处理电路中的模拟数字信号的仿真过程

单仿真器架构

模拟 信号

数字 简化信号 模拟 信号

双仿真器架构

模拟 信号

数字 信号

模拟信号 仿真器

模拟信号 仿真器

数字信号 仿真器

1-1 数模混合模拟的定义

3. 混合信号模拟

双仿真器的混合信号模拟

A_D仿真方法组合 A_D仿真器结合度

手工型

顺序型

偶合型

+ 配对型

= spetreverilog

基于Cadence的模拟集成电路设计

2.1

Cadence初次启动之前需要如下一些配置文件:

.cshrc文件:有关一些Cadence必需的环境变量,如Cadence软件的路径及license。

.cdsenv文件:包含Cadence各种工具的一些初始设置。

.cds.lib文件:用户库的管理文件,在第一次运行Cadence时自动生成。

.cdsinit文件:包含Cadence的一些初始化设置以及快捷键设置。

进入连线命令后,于起点单击左键,再于终点单击左键。画完一段导线后,此时并没有退出画线命令,可以继续画连接线,直到画完所所有的连接线后,按ESC退出画线命令。连好线的电路图如图3.7所示,其中左右两条水平导线是后在连连接端口用的。

还可以对画好的线进行命名,键入快捷键L(小写),在弹出的对话框中输入线名,比如a,点击Hide,然后将字母a移动到要命令的线附近点击左键放下,如果名字离线较远,则要求再单击所要命名的线。

如图1.1Cadence模拟集成电路设计流程

本实验指导书针对以上流程,通过设计一个简单的缓冲器的原理图到最终的版图,对Cadence的Composer,Analog Desing Environment,Virtuoso,Assura等各大功能模块逐一做个简单介绍。此外还包括一些Cadence平台的知识介绍。Cadence开发了自己的编程语言skill以及相应的编译器,整个Cadence可以理解为一个搭建在skill语言平台上的可执行文件集。初学者对此可以不用理会,当用户深入后,可以用skill语言对Cadence设计工具进行扩展。

图3.5选择了元件后的添加器件窗口

可以发现Library,Cell,View等都自动填上了相应的信息。同时多出了一些参数列表(拖动滚动条可以看到更多)。点击Hide隐藏当前窗口,此时鼠标对应有一个PMOS的symbol,此时按r键,可以旋转PMOS,继续点击鼠标左键,否则按ESC取消当前的放置器件命令。

电路仿真快速仿真数模混合仿真

3、View则包含多种类型,常用的有schemetic,symbol, layout,verilog,extracted等等 ,新建Cellview要注意选 择View的类型。

浙大微电子

16/105

Tools菜单

在Tools菜单下,比较常 用的菜单项有 Library Manager Library Path Editor Technology File Manager

Library Manager项打开的是库管 理器。在窗口的各部分中,分别 显示的是Library、Cell、View相应 的内容。

浙大微电子 17/105

Library Path Editor & Technology File Manager

Library Path Editor 可以对本用户的文件 路径进行修改

浙大微电子

13/105

二、建立可进行SPECTRE模拟 的单元文件

主窗口分为信息窗口 (command interpreter window,CIW)、命令行 以及主菜单。信息窗口 会给出一些系统信息 (如出错信息,程序运 行情况等)。在命令行 中可以输入某些命令。 主菜单包括: 1、File菜单 2、Tools菜单 3、Options菜单

浙大微电子

9/105

一、进入Cadence软件包

步骤一

下载安装putty软件 (http://www.isee.zju.ed /ic/datas/news/0308/ new_120213/putty-0.60installer.exe ),在Host name处填工作站地址, 端口默认,协议 (protocol)选SSH,如 图所示,在putty进行设 置;然后登录工作站。

cadence详细教程(模拟电路)

cadence详细教程(模拟电路)⽬录1.Cadence系统编辑环境 (2)实验1:Cadence系统编辑环境设置与基本操作 (2)2.电路图设计⼯具-Schematic (8)实验2:⼆与⾮门电路原理图设计 (8)实验3:数、模混合集成电路原理图设计 (14)3.电路仿真⼯具-ADE (18)实验4:ADE环境设置 (18)实验5:差分放⼤器电路仿真 (23)4.版图设计⼯具-Layout Editor (30)实验6:Layout Editor环境设置 (30)实验7:MOS管版图设计 (35)实验8:BJT管版图设计 (38)实验9:CMOS反相器版图设计 (42)实验10:Pcells版图设计 (46)实验11:pk44chip芯⽚版图综合设计 (53)5.版图验证⼯具-Diva (57)实验12:版图验证 (57)实验13:版图识别 (66)实验14:版图改错 (71)6.设计性实验 (73)实验15:RS触发器设计 (73)实验16:静态存储器设计 (76)实验17:三态与⾮门设计 (79)实验18:基准电压源设计 (81)实验19:CMOS放⼤器设计 (83)实验20:异或门设计 (84)Lab 1 Cadence系统环境设置与基本操作1.实验⽬的熟悉Cadence系统环境了解CIW窗⼝的功能掌握基本操作⽅法2.实验原理系统启动Cadence系统包含有许多⼯具(或模块),不同⼯具在启动时所需的License 不同,故⽽启动⽅法各异。

⼀般情况下涉及到的启动⽅式主要有以下⼏种,本实验系统所⽤到的有icms、icfb、layoutPlus等。

①前端启动命令:表1.1 前端启动命令命令规模功能icde s 基本数字模拟设计输⼊icds s icde以及数字设计环境icms s 前端模拟、混合、微波设计icca xl 前端设计加布局规划②版图⼯具启动命令表1.2 版图⼯具启动命令命令规模功能Layout s 基本版图设计(具有交互DRC功能)layoutPlus m 版图设计(具有⾃动化设计⼯具和交互验证功能)③系统级启动命令表1.3 系统级启动命令命令规模功能swb s PCB设计msfb l 混合型号IC设计icfb xl 前端到后端⼤多数⼯具CIW窗⼝Cadence系统启动后,⾃动弹出“what’s New…”窗⼝和命令解释窗⼝CIW (Command Interpreter Window)。

Candence集成电路版图设计报告

目录一、实验目的: (2)二、实验工具: (2)三、设计规则: (2)1. 版图设计的内容: (2)2. 设计规则(Design Rule ): (2)四、实验原理: (5)1.CMOS反相器工作原理 (5)2.三级反相器工作原理 (5)3.电流镜工作原理 (6)4.差分放大电路 (6)5.基准电压源电路 (7)五、实验内容: (7)1.CMOS反相器 (7)2.三级反相器 (8)3.电流镜 (8)4.差分放大电路 (8)5.基准电压源电路 (8)六、原理图和版图绘制结果: (9)七、版图设计与绘制的总结: (9)1.设计方法、技巧以及要注意的问题 (9)2.心得体会 (9)参考文献 (10)附录 ................................................................................................................... 错误!未定义书签。

一、一、实验目的:1.在Linux系统下熟悉IC设计软件Cadence Virtuoso的使用方法。

2.掌握集成电路基本单元的原理图设计、版图设计的流程方法以及技巧。

然后对其进行基本的DRC检查和LVS检查。

二、实验工具:3.Virtuoso三、设计规则:1. 版图设计的内容:①布局:安排各个晶体管、基本单元、复杂单元在芯片上的位置。

②布线:设计走线,实现管间、门间、单元间的互连。

③尺寸确定:确定晶体管尺寸(W、L)、互连尺寸(连线宽度)以及晶体管与互连之间的相对尺寸等。

④版图编辑(Layout Editor ):规定各个工艺层上图形的形状、尺寸和位置。

⑤布局布线(Place and route ):给出版图的整体规划和各图形间的连接。

⑥版图检查(Layout Check ):设计规则检验(DRC,Design Rule Check)、电气规则检查(ERC,Electrical Rule Check)、版图与电路图一致性检验(LVS,Layout Versus Schematic )。

cadence共模电路设计要点

国家集成电路人才培养基地培训资料(4)共源放大器实验2006-7-19目录1. 启动cadence,创建个人工作库 (3)2. 电路图输入 (3)3. 设置元件参数 (3)4. 对电路进行仿真 (4)4.1 DC扫描 (4)4.2 AC扫描 (7)4.3 tran扫描 (8)5. 对二极管负载的电路进行仿真 (9)5.1 仿真前设置 (9)5.2 电路仿真 (10)6. 对电流源负载的电路进行仿真 (13)6.1仿真前设置 (13)6.2 电路仿真 (14)7. 三种不同放大器性能的比较 (16)mos晶体管共源级放大器对共源放大器(包括纯电阻负载和有源负载)做DC、AC和Tran分析,验证它的输入图2.1 纯电阻负载共源放大器电路图3. 设置元件参数电源电压vdd取1.8v,V1的DC V oltage设为参数v1,AC magnitude为1v(用于看增益)。

电阻R0的阻值设为参数r1,输出电容C0的大小为1pf。

nmos管的模型为n18,沟道宽度w 为3.6um,栅长l为0.6u m 。

设置完毕后点击工具栏上的进行保存。

4. 对电路进行仿真图4.1 直流仿真参数设置然后在工具栏中点击Outputs->To Be Plotted->Select On Schematic,用鼠标点击放大器输出端所在支路作为output。

最终设置好的ADE环境如图4.2所示:图4.2 ADE环境点击图4.3 直流仿真结果图4.4 参数化扫描设置点击工具栏中的Analysis->Start,便可观察到如图4.5所示的结果:图4.5 参数化扫描结果4.2 AC仿真根据DC 分析的结果,重新设置v1和r1的值,以使增益尽量提高。

v1=0.55v ,r1=50k Ω。

点击Analysis->Choose ,选中AC 项,频率扫描范围为1k →200M 。

设置好后点击就可以看到仿真结果。

如图4.7所示:图4.6 查看参数图4.6 查看参数图4.7 AC仿真结果图4.7 瞬态信号源vsin的设置结果可以看出此时在直流电压0.55v上叠加了一个幅度为0.1mv频率为1kHz正弦信号。

cadence模拟电路板图设计

实验名称:模拟电路板图设计实验者:赵静怡学号:1028401083指导老师:顾江敏实验目的:1、根据已知电路图了解模拟电路设计要求2、完成模拟电路仿真,学会加载已知数据3、绘制模拟电路板图,通过DRC以及LVS检查。

进一步熟悉和掌握cadence软件的使用实验操作介绍:一、进入操作界面1、双击“VMware Workststion”,进入虚拟机。

选择用户名“icl2012”,键入密码“Su64zhouicl”进入cadence界面。

右击“Open in Terminal”进入输入指令界面。

2、部分指令说明:ls(回车)——查找当前目录下所有文件,绿色是可执行文件、蓝色为文件夹ls—l(回车)——给出文家属性、建立时间等信息cd ..(回车)——回到icl2012./ic【Tab】(回车)——打开界面二、库管理器1、点击“library manager”,打开库管理器。

认识Schematic、layout、Symbol等每一项内容。

点击左上角“show Categories”即可看到library中的具体分类。

2、点击“File—New—library”,新建一个库。

选择“Attach to an existing techfile”与pdk一致。

“Technology Library”中选择与之匹配的库。

3、建立cell,注意名字中不要有空格、只能有字母、数字、下划线。

三、绘制Schematic1、快捷键“i”:Add Instance2、快捷键“m”:移动元器件3、快捷键“w”:连线4、快捷键“l”:标注网络名5、快捷键“p”:加port6、电路仿真四、生成Symbol1、点击“Design—Create Cell view—From Cell view”生成Symbol2、绘制完成之后“Design—Check and Save”五、绘制layout1、快捷键说明:Shift+z:缩小Ctrl+z:缩小NPLUS+NV:是指只看NPLUS这一层F:刷新Q:设置参数Ctrl+d:取消所有选中Ctrl+a:全部选中Shift+k:删除标尺K:进行标尺P:布置金属线Shift+c:删除2、从电路图生成layout(1)Tools—Design—Layout XL(2)Connectivity—Update—Components and Nets从电路图更新到layout(3)将I/O Pins修改为金属1,将Pin Label Shape修改为Label,修改Pin Label Options的参量。

数模混合电路的设计(很详细规范)

目录:前言一、数模混合设计的难点二、提高数模混合电路性能的关键三、仿真工具在数模混合设计中的应用四、小结五、混合信号PCB设计基础问答前言:数模混合电路的设计,一直是困扰硬件电路设计师提高性能的瓶颈。

众所周知,现实的世界都是模拟的,只有将模拟的信号转变成数字信号,才方便做进一步的处理。

模拟信号和数字信号的转变是否实时、精确,是电路设计的重要指标。

除了器件工艺,算法的进步会影响系统数模变换的精度外,现实世界中众多干扰,噪声也是困扰数模电路性能的主要因素。

本文通过Ansoft公司的“AD-Mix Si gnal Noise Design Suites” 数模混合噪声仿真设计软件的对数模混合设计PC B的仿真,探索分析数模混合电路的噪声干扰和优化设计的途径,以达到改善系统性能目的。

一、数模混合设计的难点数模混合电路设计当中,干扰源、干扰对象和干扰途径的辨别是分析数模混合设计干扰的基础。

通常的电路中,模拟信号上由于存在随时间变化的连续变化的电压和电流有效成分,在设计和调试过程中,需要同时控制这两个变量,而且他们对于外部的干扰更敏感,因而通常作为被干扰对象做分析;数字信号上只有随时间变化的门限量化后的电压成分,相比模拟信号对干扰有较高的承受能力,但是这类信号变化快,特别是变化沿速度快,还有较高的高频谐波成分,对外释放能量,通常作为干扰源。

作为干扰源的数字电路部分多采用CMOS工艺,从而导致数字信号输入端极高的输入电阻,通常在几十k欧到上兆欧姆。

这样高的内阻导致数字信号上的电流非常微弱,因而只有电压有效信号在起作用,在数模混合干扰分析中,这类信号可以作为电压型干扰源,如CLK信号,Reset等信号。

除了快速交变的数字信号,数字信号的电源管脚上,由于引脚电感和互感引起的同步开关噪声(SSN),也是数模混合电路中存在的重要一类电压型干扰源。

此外,电路中还存在一些电流信号,特别是直流电源到器件负载之间的电源信号上有较大的电流,根据右手螺旋定理,电流信号周围会感应出磁场,进而引起变化的电场,在分析时,直流电源作为电流型干扰源。

cadence原理图设计实例教程

器件放置

• 也可以按下步骤放置uA741:

➢ 执行P1ace/Part命令 ➢ 在 Part中输“ *741* ” , ➢ 点击Part Search, ➢ 点击Begin Search, ➢ 在Library 库中寻找到

uA741/opamp.olb ➢ 单击“OK” ➢ 执行前面的步骤,单击

“OK”,放置器件,断开放 置

放置电容符号

➢ 执行P1ace/Part命令 ➢ 在 “Libraries”列表框中选

择“ANALOG” ➢ 在 “Part”列表框中选择

“ C” ➢ 单击“OK” ➢ 将电阻C移至合适位置,

(按键盘中的R键,器件旋 转)按鼠标左键放置 ➢ 按ESC键(或鼠标右键点 end mode)结束绘制元器

器件封装调用

在Link Footprint to Component 栏内点OK,对于没有 定义的管脚封装图,出现MAXECO提示说明,确定

器件封装调用

在Link Footprint to Component 栏内点OK,对于没有定义的管脚封 装图, 点Link existing footprint to component来查找连接封装。

Place net name

放置分页图纸间的接口

原理图绘制

(二) 原理图绘制

以声控开关为例(电源是直流12V,负载为发光二极管)见下 图:

放置集成块运放uA741

• 执行P1ace/Part命令 • 在 “Libraries”列表

框中选择“OPAMP” 库 • 在 “Part”列表框中 选择“uA741” • 单击“OK” • 将集成块移至合适位 置,按鼠标左键 • 按ESC键或鼠标右键点 end mode以结束绘 制元器件状态

cadence数模混合课程设计

cadence数模混合课程设计一、课程目标知识目标:1. 理解数模混合电路的基本概念,掌握Cadence软件中数模混合电路的设计流程;2. 掌握数模混合电路中模拟电路与数字电路的接口技术,了解其相互影响;3. 学会使用Cadence软件进行数模混合电路的仿真与优化。

技能目标:1. 能够运用Cadence软件设计简单的数模混合电路;2. 能够分析数模混合电路中可能出现的常见问题,并运用所学知识进行解决;3. 具备一定的电路调试与优化能力,提高实际工程应用中的问题解决能力。

情感态度价值观目标:1. 培养学生对数模混合电路设计的兴趣,激发其创新意识;2. 增强学生团队协作意识,培养良好的沟通与协作能力;3. 强化质量意识,使学生认识到严谨的工程态度在电路设计中的重要性。

课程性质:本课程为实践性较强的课程,结合理论知识与实际操作,注重培养学生的动手能力和实际问题解决能力。

学生特点:高年级学生,已具备一定的电子电路基础知识,具有较强的学习能力和自主性。

教学要求:结合学生特点,注重理论与实践相结合,强调实际操作,以项目为导向,提高学生的实际工程能力。

在教学过程中,关注学生的个体差异,针对性地进行指导,确保课程目标的实现。

通过课程学习,使学生能够独立完成数模混合电路的设计与优化,为后续相关课程和实际工作打下坚实基础。

二、教学内容1. 数模混合电路基本概念:包括模拟电路、数字电路特点,数模混合电路的定义及其在电子系统中的应用。

教材章节:第二章 数模混合电路基础2. Cadence软件操作:介绍Cadence软件的基本操作,原理图绘制,电路仿真等。

教材章节:第三章 Cadence软件操作3. 数模混合电路设计流程:讲解从电路设计、原理图绘制、仿真测试到PCB 设计的完整流程。

教材章节:第四章 数模混合电路设计流程4. 接口技术:分析模拟电路与数字电路之间的接口技术,包括信号转换、阻抗匹配等。

教材章节:第五章 接口技术5. 电路仿真与优化:介绍仿真方法,参数设置,优化策略等,提高电路性能。

集成电路设计CAD_EDA工具实用教程1-Spectre_Verilog数模混合仿真

共27页

26

THANK YOU!

共27页

27

同时包含模拟和数字两个仿真核

处理速度快,能处理的电路规模极大,但需要解决模拟仿真核和数字 仿真核之间的通信问题;另外,由于数字逻辑仿真器和模拟仿真器的输 入、输出数据是不一样的,还必须在模拟仿真核和数字仿真核之间实现 模拟信号和数字信号的相互转换。

共27页

Q&A

9

Creating Analog Block

共27页

8

Mixed-Signal Simulator 的基本结构

以模拟电路仿真器为核心

在处理数模混合电路时将数字部分等效为相应的简化的模拟电路、或 者采用解析函数来表示逻辑模块的行为,然后对整个系统采用模拟电路 的方法进行模拟。优点:模拟结果精确、能处理的电路规模比较大,模 拟速度也有显著提高。缺点:比逻辑模拟器还是慢很多。

共27页

24

Submit the Simulation

Execute the simulation job with Run, or create the netlist with Netlist

start simulation

共27页

25

Results

数 字 输 出 数字 /模 拟输 入

模 拟 输 出

选择SpectreVerilog

共27页 23

Choose Analysis Type

Invoke the analysis setting window

For Mixed-Signal simulation, only tran is meaningful Set the simulation time Check this box to enable this simulation

数模混合IC设计流程

数模混合IC设计流程1.数模混合IC设计近十年来,随着深亚微米及纳米技术的发展,促使芯片设计与制造由分离IC、ASIC 向SoC转变,现在SoC芯片也由数字SoC全面转向混合SoC,成为真正意义上的系统级芯片。

如今人们可以在一块芯片上集成数亿只晶体管和多种类型的电路结构。

此时芯片的制造工艺已经超越了传统制造理论的界限,对电路的物理实现具有不可忽略的影响。

因此,片上系统所依赖的半导体物理实现方式,面临着多样化和复杂化的趋势,设计周期也越来越长。

目前越来越多的设计正向混合信号发展。

最近,IBS Corp做过的一个研究预测,到2006年,所有的集成电路设计中,有73%将为混合信号设计。

目前混合信号技术正是EDA业内最为热门的话题。

设计师在最近才开始注意到混合信号设计并严肃对待,在他们意识到这一领域成为热点之前,EDA公司已经先行多年。

EDA业内领头的三大供应商Mentor Graphics、Synopsys和Cadence在几年前即开始合并或研发模拟和混合信号工具和技术。

其中Mentor Graphics是第一个意识到这一点,并投入力量发展混合信号技术的EDA供应商。

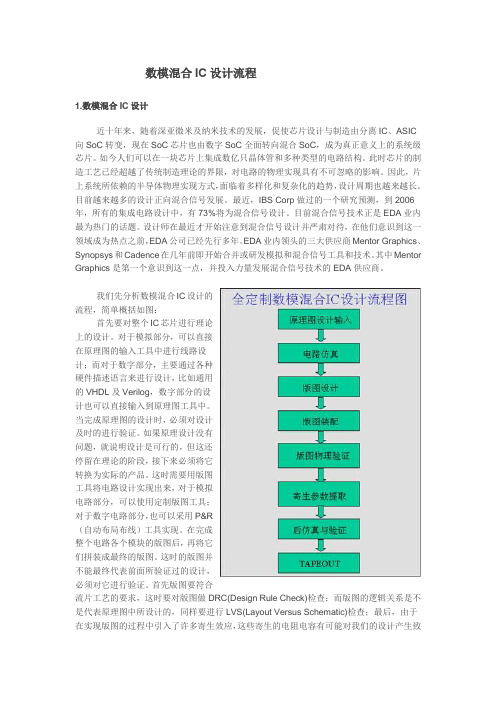

我们先分析数模混合IC设计的流程,简单概括如图:首先要对整个IC芯片进行理论上的设计。

对于模拟部分,可以直接在原理图的输入工具中进行线路设计;而对于数字部分,主要通过各种硬件描述语言来进行设计,比如通用的VHDL及Verilog,数字部分的设计也可以直接输入到原理图工具中。

当完成原理图的设计时,必须对设计及时的进行验证。

如果原理设计没有问题,就说明设计是可行的,但这还停留在理论的阶段,接下来必须将它转换为实际的产品。

这时需要用版图工具将电路设计实现出来,对于模拟电路部分,可以使用定制版图工具;对于数字电路部分,也可以采用P&R(自动布局布线)工具实现。

在完成整个电路各个模块的版图后,再将它们拼装成最终的版图。

这时的版图并不能最终代表前面所验证过的设计,必须对它进行验证。

数模混合电路设计

6 5 4

2Iref

I4on ,I2off ,I1off . . . . . I2on ,I1on I2on ,I1off I1on

Digital Input

• DNL depends on transition – Example: 0 to 1 ÆσDNL2 =

3 2

σ(dΙref/Ιref)2 1 to 2 Æ σDNL2 = 3σ(dΙref/Ιref)2

EECS 247- Lecture 14

Mixed Analog and Digital IC Design

Data Converters: DAC Design

© 2008 H.K. Page 45

Digital-to-Analog Converters

Static DAC Errors

DAC INL

DNL Unit Element DAC

E.g. Resistor string DAC: Assumption: No systematic error- only random error

2B −1

Vref Iref

Δ = Rmedi an Iref Δi = Ri Iref D N Li = Δi − Δmedian Δmedian Ri − R R

Current Based DAC

R-2R ladder: binary weighted output impedance Output impedance: EF/SF & opamp compensation INL/DNL error due to opamp offset Unit-element current DAC: monotonic, 2N -1 current & switches Binary-weighted: monotonicity not guranteed, 2N -1 current & N switches

电子设计中的数模混合设计方法

电子设计中的数模混合设计方法

在电子设计中,数模混合设计方法是一种常用的技术,用于将数字信号与模拟

信号相结合,以实现复杂的电路功能。

数模混合设计方法在各种领域中广泛应用,包括通信、控制系统、传感器等。

数模混合设计方法的核心是将模拟信号转换为数字信号(ADC),或者将数字信号转换为模拟信号(DAC)。

ADC和DAC是电子系统中常用的器件,用于实现信号的数字化和模拟化处理。

在设计中,需要考虑信号的精度、速度、功耗等因素,以确保电路性能的稳定和可靠。

在数模混合设计中,一般会使用模拟电路和数字电路相结合的方式来实现功能。

模拟电路主要负责信号处理和滤波等功能,数字电路则用于控制逻辑和数据处理。

通过合理的设计,可以实现更复杂的功能,提高系统的性能和稳定性。

另外,在数模混合设计中,还需要考虑布局和布线的问题。

良好的布局和布线

可以减少信号的干扰和损耗,提高系统的可靠性和性能。

通常会使用仿真工具来辅助设计和优化布局,以确保电路的稳定和可靠。

总的来说,数模混合设计方法是一种复杂而重要的技术,在电子系统中发挥着

重要作用。

通过合理的设计和优化,可以实现更高性能和更可靠的电子系统,满足各种应用需求。

在未来的发展中,数模混合设计方法将继续发挥重要作用,推动电子技术领域的发展。

cadence共模电路设计教学内容

c ade n c e共模电路设计国家集成电路人才培养基地培训资料(4)共源放大器实验2006-7-19目录1. 启动cadence,创建个人工作库 (3)2. 电路图输入 (3)3. 设置元件参数 (4)4. 对电路进行仿真 (4)4.1 DC扫描 (4)4.2 AC扫描 (8)4.3 tran扫描 (9)5. 对二极管负载的电路进行仿真 (11)5.1 仿真前设置 (11)5.2 电路仿真 (11)6. 对电流源负载的电路进行仿真 (14)6.1仿真前设置 (14)6.2 电路仿真 (15)7. 三种不同放大器性能的比较 (18)mos晶体管共源级放大器对共源放大器(包括纯电阻负载和有源负载)做DC、AC和Tran分析,验证它的输入输出特性曲线,学习如何在cadence软件中观察放大器的增益和各种波形,学习在Results Displaying Window中查看各种电路参数,以及对放大器做参数化扫描。

1. 启动cadence,创建个人工作库开机进入solaris9系统,输入cds.setup后再输入icfb&,启动candence。

建立一个命名为common_source_stage的工作库。

在此工作库下建立一个cellview 命名为resistive_load。

2. 电路图输入在schematic中编辑以纯电阻为负载的共源放大器,图中用到的元件nmos4、res、gnd、cap、vdc和vdd从analogLib库中选取。

编辑好的电路如图2.1所示:图2.1 纯电阻负载共源放大器电路图3. 设置元件参数电源电压vdd取1.8v,V1的DC Voltage设为参数v1,AC magnitude为1v(用于看增益)。

电阻R0的阻值设为参数r1,输出电容C0的大小为1pf。

nmos管的模型为n18,沟道宽度w为3.6um,栅长l为0.6u m。

设置完毕后点击工具栏上的进行保存。

4. 对电路进行仿真4.1 DC仿真选择菜单Tools->Anolog Environment,进入ADE环境,首先对model文件进行设置, 在ADE工具栏中点击Setup->Model Libraries添加Model Library。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1-2 数模混合信号模拟的应用

2.大型数字系统仿真

大部分电路使用verilog仿真器仿真; 指定的关键部分电路使用模拟仿真器以达到高精度.

1-2 数模混合信号模拟的应用

3.仿真提速

A:用作信 号发生器。 仿真的时候,需要不少的激励信号,而且有着严格的时序关 系,要是用pulse电源或是别的什么电源来做的话,可要累死 人的。用verilog写模块的foundational,就 可以比较方便快 捷的构成一个信号发生器。

数字仿真

➢ 步骤:

➢ 1.在icfb中建立verilog 的view,(包括 模块和testbench,testbench的view名也 是verilog

➢ 2.右键点击testbench的verilog view, 选择“open(read-only)”在verilog阅读窗 的菜单上选择tools=>verilog-xl

模拟 信号

数字 信号

模拟信号 仿真器

模拟信号 仿真器

数字信号 仿真器

1-1 数模混合模拟的定义

3. 混合信号模拟

双仿真器的混合信号模拟

A_D仿真方法组合 A_D仿真器结合度

手工型

顺序型

偶合型

+

配对型

= spetreverilog

单模式

扩展型

偶合型--配对型--锁步”巢(套l型ock-step)同步法 集成型 = Cadence spetreverilog

Cadence 实验系列12_ 数模混合电路设计_spetreVerilog

设置

➢ 路径设置 ➢ 首先要设置路径,可以这样设置(icfb 和

ius和在一起了):

➢ setenv ic50 /tools/cadence/ic5141 setenv ius58 /opt/cadence/ius58 set LD_LIBRARY_PATH = ( $ic50/tools/lib $ic50/tools/dfII/li b $ic50/tools/tcltk/tcl8.0/lib $ic50/tools/tcltk/tk8.0/lib ${ius58 }/tools/verilog/lib $ius58/tools/lib $LD_LIBRARY_PATH) set path = ( ${ius58}/tools/verilog/bin $ius58/tools/bin $ic50/t ools/bin $ic50/tools/dfII/bin $ic50/tools/dracula/bin $path )

框架型

1-1 数模混合模拟的定义

3. 混合信号模拟 Cadence spetreverilog解决方案

混合仿真环境

Verilog-XL

IPC = interproceSspsectoremmunication

仿真输出数据库

1-1 数模混合信号模拟定义

4. 商用混合信号仿真技术 Cadence Muti-Mode仿真(MMSIM)解决方案

制作顶层文件

混合信号模拟的特点

建立层次文件

操设作置示仿例真环境

仿真

数字设计

模拟设计

2

1制作顶层文件 3

4

建立层次化文件

混合信号仿真

Cadence sp芯et片re级v电e路ril验o证g

模拟信号仿真

射频信号仿真

1-2 数模混合信号模拟的应用

混合信号模拟简介

混合模拟的定义 混合模拟的应用

2

1

3

4

1-2 数模混合信号模拟的应用

1. 数模混合电路的设计 2. 大型数字集成电路设计 3. 仿真提速

1-2 数模混合信号模拟的应用

用高斯消去法 求解线性方程

1-1 数模混合信号模拟定义

2.数字信号模拟

是指基于松弛算法的由事件驱动的:一t种es仿tb真en模ch拟方式。

1

2

3

4

1-1 数模混合模拟的定义

3. 混合信号模拟

以特定的组合方式处理电路中的模拟数字信号的仿真过程

单仿真器架构

模拟 信号

数字 简化信号 模拟 信号

双仿真器架构

混合信号模拟的特点Cadenc Nhomakorabea中的实现

操作示例

2

1

3

4

1-1 数模混合信号模拟定义

1.模拟信号模拟仿真 2.数字信号模拟仿真 3. 混合信号模拟仿真 4. 商用混合信号模拟仿真

1-1 数模混合信号模拟定义

1.模拟信号模拟

指基于节点积分分析的瞬态模拟仿真方法

f1(x1, x2,…) =0 f2(x1, x2,…) =0 … … …

1. 数模混合设计

1-2 数模混合信号模拟的应用

1. 数模混合设计

数模IC

传感器 滤波器

A/D

信号处理器

D/A

放大器 接收器

1-2 数模混合信号模拟的应用

1. 数模混合设计

算法设计

数字设计

模拟设计

数字设计

模拟设计

数模混合验证

数字版图

模拟版图

数模混合验证 Tape-out

混合原理图 建立层次化文件

Hierarchy-Editor

仿真器 工作环境

Spetreverilog 仿真器

屏幕输出 波形文件

顶层原理图

SchematicWindow

用户定义文件

1-3 Cadence 中的Spetreverilog

2. 数模混合仿真的数据流

2-1 数字-模拟电路设计

混合信号模拟简介

混合数信字-号模拟模电拟路的设实计现

混合信号模拟简介

混合模拟的定义 混合模拟的应用 Cadence中的实现

2

1

3

4

1-3 Cadence 中的Spetreverilog

1. cadence中数模混合仿真的环境 2. cadence中数模混合仿真的数据流

1-3 Cadence 中的Spetreverilog

1. 数模混合仿真的环境

层次编辑器

➢ 3.用verilog-xl仿真,试一试就会用了仿 真完成后View Waveform的按钮会被激活 按这个按钮,simvision打开

数模混合电路设计流程

算法设计

数字设计

模拟设计

数模混合验证

数字版图

模拟版图

数模混合验证 Tape-out

目录

混合信号模拟简介

混合模拟的定义

混合信号模拟的实现

混合模拟的应用

B:节约模拟的时间。 对于一些成熟的已经知道电路输入输出特性的电路,可以用 verilog写出其特性,这样的话,模拟的时间可以大大的缩短。 当然,还有就是verilog 的老本家--数字电路,也可以用 verilog写出foundational,节约模拟的时间。

1-3 Cadence 中的Spetreverilog