数字逻辑第七章

《数字电路与数字逻辑》第七章

ppt课件

15

③放电阶段:

u C 1 3 V C , CR 0 则 (或 1 ) , S 0 , u o 0 ;第二暂稳态

u C 1 3 V C, CR 则 0 , S 1 , u o 1 ;第一暂稳态

ppt课件

ppt课件

8

(3) 3脚—输出端

(4) 4脚—直接置0端

(5) 5脚—电压控制端UIC ①接UREF ,则高触发电平、低触发电平分别为

UREF 、12UREF ②不接UREF ,则高、低触发电平分别为

32VCC 、13VCC

ppt课件

9

(6) 6脚—高触发输入端(阈值输入端) (7) 7脚—放电端 (8) 8脚—电源端

当ui为高电平时,uo为低电平; 当ui变为低电平时,uo变为高电平;

tr

tf

Um

tW

T

ppt课件

4

P1

△U

P2

图 7.1.2Βιβλιοθήκη 矩形脉冲的参数ppt课件5

第二节 集成定时器

一、555定时器的结构

1.组成 分压器,电压比较器,基本SREF,集电极开 路输出的放电三极管。

2.各引脚功能 (1) 1脚—接地端 (2) 2脚—低触发输入端(触发输入端)

ppt课件

6

V CC

16

3.矩形波参数

T P H 0 .7 (R A R B )C ;H (R A R B )C

T PL 0.7R BC

;LRBC

T T P T H P 0 L . 7 ( R A 2 R B ) C

qtW T PH R AR B T T PH T PLR A2R B

(整理)《数字逻辑电路》试题2.

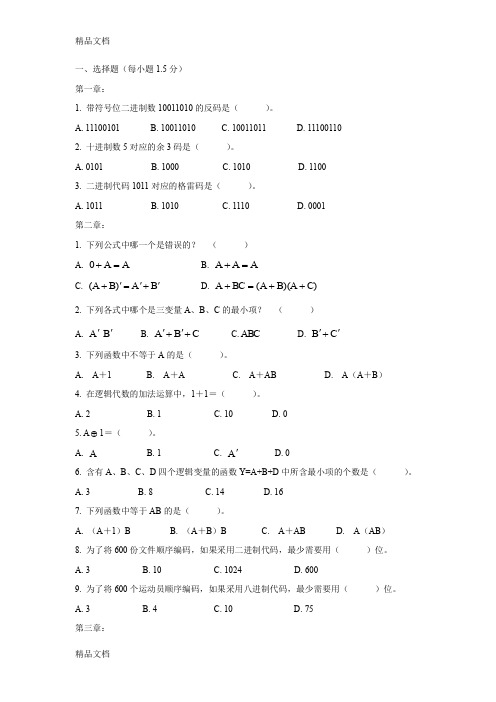

一、选择题(每小题1.5分)第一章:1. 带符号位二进制数10011010的反码是( )。

A. 11100101B. 10011010C. 10011011D. 111001102. 十进制数5对应的余3码是( )。

A. 0101B. 1000C. 1010D. 11003. 二进制代码1011对应的格雷码是( )。

A. 1011B. 1010C. 1110D. 0001第二章:1. 下列公式中哪一个是错误的? ( )A. A A 0=+B. A A A =+C. B A )B A ('+'='+D. )C A )(B A (BC A ++=+2. 下列各式中哪个是三变量A 、B 、C 的最小项? ( )A. B A ''B. C B A +'+'C.ABCD. C B '+'3. 下列函数中不等于A 的是( )。

A. A +1B. A +AC. A +ABD. A (A +B )4. 在逻辑代数的加法运算中,1+1=( )。

A. 2B. 1C. 10D. 05. A ⊕1=( )。

A. AB. 1C. A 'D. 06. 含有A 、B 、C 、D 四个逻辑变量的函数Y=A+B+D 中所含最小项的个数是()。

A. 3 B. 8 C. 14 D. 167. 下列函数中等于AB 的是( )。

A. (A +1)BB. (A +B )BC. A +ABD. A (AB )8. 为了将600份文件顺序编码,如果采用二进制代码,最少需要用( )位。

A. 3B. 10C. 1024D. 6009. 为了将600个运动员顺序编码,如果采用八进制代码,最少需要用( )位。

A. 3B. 4C. 10D. 75第三章:1. 采用漏极开路输出门电路(OD 门)主要解决了( )。

A. CMOS 门不能相“与”的问题B. CMOS 门的输出端不能“线与”的问题C. CMOS 门的输出端不能相“或”的问题2. 下列哪个特点不属于CMOS 传输门?( )A. CMOS 传输门属于双向器件。

精品课件-数字电子技术-第7章

第7章 集成逻辑门电路简介

7.4 已知电路和输入信号的波形如图7.12所示,信号 的重复频率为1 MHz,每个门的平均延迟时间tpd=20 ns,试 画出:(1) 不考虑tpd影响时的波形;(2) 考虑tpd影响

第7章 集成逻辑门电路简介

图7.12 题7.4图

第7章 集成逻辑门电路简介

7.5 电路如图7.13所示。(1) 分别写出Y1、Y2、Y3、 Y4的逻辑函数表达式;(2) 若已知A、B、C的波形,试分别 画出Y1、Y2、Y3、Y4

(4) DE段。当UI≥1.4 V时,V2、V5饱和,V4截止,输 出为低电平, 与非门处于饱和状态, 所以把DE段称为饱和

第7章 集成逻辑门电路简介

4. (1) 输出高电平UOH和输出低电平UOL。电压传输特性 曲线截止区的输出电压为UOH,饱和区的输出电压为UOL。 一般产品规定UOH≥2.4 V,UOL<0.4 V (2) 阈值电压Uth。电压传输特性曲线转折区中点所 对应的输入电压为Uth,也称门槛电压。一般TTL与非门的 Uth≈1.4 V

Y=Y1·Y2

第7章 集成逻辑门电路简介

图7.4 实现“线与”功能的电路

第7章 集成逻辑门电路简介

但是普通TTL逻辑门的输出端是不允许直接相连的,如 图7.5所示电路:设门1的输出为高电平(Y1=1), 门2的输 出为低电平(Y2=0),此时门1的V4管和门2的V5管均饱和导通, 这样在电源UCC的作用下将产生很大的电流流过V4、V5管使V4、 V5

第7章 集成逻辑门电路简介

(3) 关门电平UOFF和开门电平UON。保证输出电平为 额定高电平(2.7 V左右)时,允许输入低电平的最大值, 称为关门电平UOFF。通常UOFF≈1 V , 一般产品要求 UOFF≥0.8 V。 保证输出电平达到额定低电平(0.3 V)时, 允许输入高电平的最小值,称为开门电平UON。通常 UON≈1.4 V,一般产品要求UON≤1.8 V

数字逻辑欧阳星明第四版华科出版1~7全答案ppt课件

Y= XYXY= XYXY= XY ,

所以,X=Y。

.

18

习题课

2.6 用逻辑代数的公理、定理和规则将下列逻辑函数化简为 最简“与-或”表达式 。

(1) FAB ABCBC

(2) FABBBCD

(3) F (A B C )A ( B )A ( B C )

(4) FB C D D (B C )A ( C B )

.

2

习题课

1.3 数字逻辑电路可分为哪两种类型?主要区别是什么?

解答: 根据一个电路有无记忆功能,可将数字逻辑电路分为组

合逻辑电路和时序逻辑电路。如果一个逻辑电路在任何时刻 的稳定输出仅取决于该时刻的输入,而与电路过去的输入无 关,则称为组合逻辑电路。由于这类电路的输出与过去的输 入信号无关,所以不需要有记忆功能。如果一个逻辑电路在 任何时刻的稳定输出不仅取决于该时刻的输入,而与电路过 去的输入相关,则称为时序逻辑电路。由于这类电路的输出 与过去的输入信号相关,所以要有记忆功能,要用电路中的 记忆元件的状态来反映过去的输入信号。

解答:

8421码: 十进制: 2421码:

0110 1000 0011 0011 0101 0000 350 0011 1011 0000

0100 0101.1001 0001 0010.0110 12.6 0001 0010.1100

.

10

习题课

1.12 试用8421码和Gray码分别表示下列各数。

4×8-3

(4)(785.4AF)16=7×162+8×161+5×160+4×16-1+

10×8-2

+15×16-3

.

5

习题课

1.6 将下列二进制数转换成十进制数、八进制数和十六进制 数。

数字逻辑课后答案第七章

D80 D20

D20 D4

D10 D10

D8 D2

D1

图2

3. 用4位二进制并行加法器设计一个用8421码表示的1位十进制加法

器。

解答

分析:由于十进制数采用8421码,因此,二进制并行加法器输入被加数和 加数的取值范围为0000~1001(0~9),输出端输出的和是一个二进制数,数的 范围为0000~10011(0~19,19=9+9+最低位的进位)。因为题目要求运算的结果也

0

0000000000

0

1

0000100001

0

2

0001000010

0

3

0001100011

0

4

0010000100

0

5

0010100101

0

6

0011000110

0

7

0011100111

0

8

0100001000

0

9

0100101001

0

10

0101010000

1

11

0101110001

1

12

0110010010

设计出该序列发生器的逻辑电路图如图8所示。

图8

11. 在图9所示电路中,若取R1=2R2 ,请问输出矩形波的占空比为多 少?

图9 解答

2R2 + R2 = 3R2 = 3 2R2 + 2R2 4R2 4

12. 分析图10所示由定时器5G555构成的多谐振荡器。

图10

(1)计算其振荡周期;

(2)若要产生占空比为50%的方波,R1和R2的取值关系如何?

路较复杂,一般分辨率较低;逐次比较型速度较快,精度高;双积 分型精度高、抗干扰能力强,但速度较慢。 18. ADC0809如何实现对8路模拟量输入的选择?当它与微机连接时是

数字逻辑第七章作业答案

H’·L’·R’

1

IDLE

R R·H’ 1 H’

R1

H

R2

L2

H’(L’+R’) 1

L3 1 H+LR L L·H’·R’ IDLE 1 R3 1 H’(L’+R’) R R·H’·L’ H+LR

H’(L’+R’) 1 L1 H+LR 1 H+L·R H H+LR R1 1H’(L’+R’) LR3

R

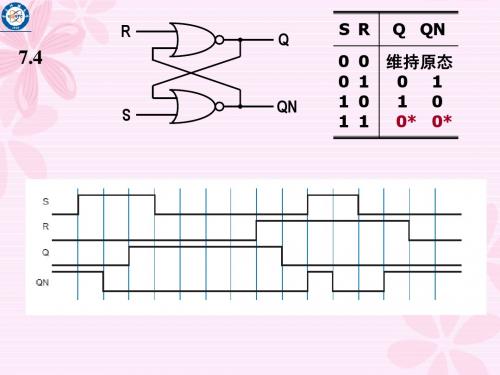

7.4

S

Q

S R 0 0 1 1 0 1 0 1

Q QN 维持原态 0 1 1 0 0* 0*

QN

R

Q

7.5

S QN

7.6 利用带有使能端的T触发器和组合逻辑构造D触发 器

D触发器:Q* = D (转移方程) T触发器的特征方程:Q*= EN·Q’ + EN’·Q=ENQ 所以,激励方程:EN = DQ

W’Y’

X’YZ

X’Z’

对A状态,不满足完备性,少了(X+YZ)’ 对B状态,不满足互斥性,多了W’Y’ 对C状态,满足二义性 对D状态,不满足互斥性,多了XY,并且不满足完备性, 少了(X+Y’)’

L2

7.24修改状态图

L3

H’ 1

H’ 1

H

L1

1 L L·H’·R’ H 1 H+L·R H H

H’·L’·R’

R2

Transition list

Q2Q1Q0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 S 转移表达式 S* Q2*Q1*Q0* 0 0 1 1 0 0 0 0 0 0 1 0 0 1 1 0 1 0 H’·L’·R’ IDLE L1 IDLE L·H’·R’ R·H’·L’ R1 H+L·R LR3 H’·(L’+R’) L2 L1 H+LR LR3

第7章数字逻辑基础

AB Y 00 1 01 0 10 0 11 1

三、逻辑函数及其表示方法

1.逻辑变量和逻辑函数 在数字系统中,开关的接通与断开,电压的高和低 ,信号的有和无,晶体管的导通与截止等两种稳定的物理 状态,均可用1和0这两种不同的逻辑值来表征,这种仅有 两个取值的自变量称为逻辑变量,通常用字母A、B、 C…来表示。 如果对应于输入逻辑变量A、B、C、…的每一组确 定值,输出逻辑变量Y就有唯一确定的值,则称Y是A、B 、C、…的逻辑函数。记为:

YA BA BA B

异或运算

AB Y 00 0 01 1 10 1 11 0

异或逻辑运算的规则:相同为0,相异为1。

5.同或运算

所谓同或运算,是指两个输入变量取值相同时输出为1, 取值不相同时输出为0。 逻辑表达式:

式中,符号“⊙”表示同或运算,读作“同或”。 同或运算

同或逻辑运算的规则:相同 为1,相异为0

起来的逻辑代数式。它是数字电路输入量与输出量 之间逻辑函数关系的表达式,也称函数式或代数式。 优点:形式简洁,书写方便,直接反映了变量间 的运算关系,便于用逻辑图实现该函数。

例7-4 写出如图所示逻辑图的函数表达式。

解:根据门电路的逻辑符号和对应的逻辑运算, 由前向后逐级推算,即可写出输出函数Y的表达式

(128)8=(1×82+2×81+8×80)10 =(64+16+8)10 =(88)10

(5D)16=(5×161+13×160)10 =(80+13)10 =(93)10

2.十进制数转换二进制

例7-2 求[29]10=[

]2。“除2取余法”

2

29

…余1

底位

2

14

数字逻辑第7章

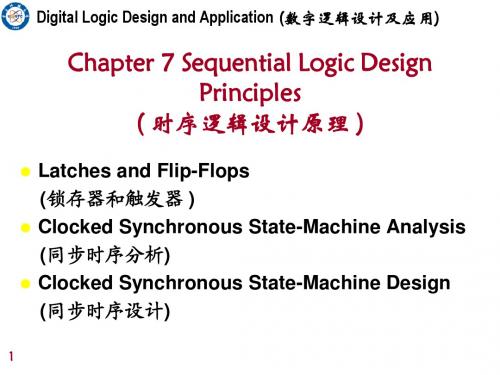

Digital Logic Design and Application (数字逻辑设计及应用)

Review of Last Class (内容回顾)

锁存器与触发器

R Q

S-R锁存器 S-R锁存器

具有使能端的S-R锁存器

有约束条件

S S_L

QL

D

C C

S

Q

D锁存器

2

QL

R R_L

Digital Logic Design and Application (数字逻辑设计及应用)

6

Digital Logic Design and Application (数字逻辑设计及应用)

Scan Flip-Flop (扫描触发器)

Logic Symbol (逻辑符号)

TE = 0 正常操作 Q=D TE = 1 进入测试模式

D 测试使能端 TE 测试输入端 TI CLK

思考:同样是主从结构, 为什么由D锁存器构成的可以称为边沿D触发器, 而由S-R锁存器构成的不能称为边沿S-R触发器?

D D Q C Q D Q C Q

Dynamic-Input Indicator Q (动态输入指示 D Q QN 边沿触发) CLK Q S C R

CLK S S C R Q S C R Q Q Q Q Postponed-Output

D Flip-Flops (D触发器)

—— 主从结构

D

Master(主) Slave (从) Qm Q D Q D Q C Q QL C Q

CLK

CLK=0时, 主锁存器工作,接收输入信号 Qm = D

从锁存器不工作,输出 Q 保持不变 CLK=1时, 主锁存器不工作,Qm 保持不变

数字逻辑(第二版) 华中科技大学出版社(欧阳星明)版数字逻辑答案第七章

习 题 七1. 用4位二进制并行加法器设计一个实现8421码对9求补的逻辑电路。

解答设8421码为B 8B 4B 2B 1 ,其对9的补数为C 8C 4C 2C 1 ,关系如下:相应逻辑电路图如图1所示。

图 12. 用两个4位二进制并行加法器实现2位十进制数8421码到二进制码解答设两位十进制数的8421码为D 80D 40D 20D 10D 8D 4D 2D 1 ,相应二进制数为B 6B 5B 4B 3B 2B 1B 0,则应有B 6B 5B 4B 3B 2B 1B 0 = D 80D 40D 20D 10×1010+D 8D 4D 2D 1,运算如下:× D 80 1D 40 0 D 20 1 D 10 0 + D 80 D 40 D 80 D 20D 40 D 10 D 8D 20D 4 D 10D 2 D 1B 6B 5B 4 B 3B 2B 1B 0据此,可得到实现预定功能的逻辑电路如图2所示。

图 23. 用4位二进制并行加法器设计一个用8421码表示的1位十进制加法解答分析:由于十进制数采用8421码,因此,二进制并行加法器输入被加数和加数的取值范围为0000~1001(0~9),输出端输出的和是一个二进制数,数的范围为0000~10011(0~19,19=9+9+最低位的进位)。

因为题目要求运算的结果也是D 8 D 10D 2D 10 D 18421码,因此需要将二进制并行加法器输出的二进制数修正为8421码。

设输出的二进制数为FC 4 F 4 F 3 F 2 F 1,修正后的结果为'1'2'3'4'4F F F F FC ,可列出修正函数真值表如表1所示。

根据表1写出控制函数表达式,经简化后可得:据此,可画出逻辑电路图如图3所示。

图34. 用一片3-8线译码器和必要的逻辑门实现下列逻辑函数表达式。

解答假定采用T4138和与非门实现给定函数功能,可将逻辑表达式变换如下:逻辑电路图如图4所示。

数字逻辑第7章 触发器

《数字逻辑》 假设门传输延时时间为t pd

四、最高时钟频率

2S

VCC 4S 4R 4Q 3SA 3SB 3R 3Q

VDD 4S 4R 1Q 2R 2S 3Q 2Q

16 15 14 13 12 11 10 9 74LS279

12345678

16 15 14 13 12 11 10 9 CC4044

12345678

1R 1SA 1SB 1Q 2R 2S 2Q GND (a) 74LS279 的引脚图

···

《数字逻辑》

一、电路结构和工作原理 1、用两个电平触发D触发器组成的边沿触发器

利用CMOS传输门的边沿触发器

《数字逻辑》

(4)列出真值表

CLK D Q Q *

XXXQ 0 X0 1 X1

(1)clk

0时,T

TG1通,TG2断 G3断,TG4通

Q Q保持,

D, Q随着D而变化 反馈通路接通,自锁

Q’

SR

Q*

《数字逻辑》

10

0

01

1

1 1 保持

0 0 不定

置1 保持 置1 置0 置1 不允许 置1

二、动作特点 在任何时刻,输入都能直接改变输出的状态。

《数字逻辑》

例:

SD和RD同时为0 Q,Q同为1

三、由或非门构成的锁存器

《数字逻辑》

《数字逻辑》

1.工作原理

SD RD Q Q *

两个或非门接成反馈,引出输入端用来置0,1 0 0 0 0

R

Q’m

Q’

CLK

Q 0时,只允许J 1的信号进入主触发器

Q 1时,只允许K 1的信号进入主触发器

《数字逻辑》

《数字逻辑设计》第7章 数据选择器及译码器

P1

P2

P9

P3

P8

Gnd P4

P7 P6

P5

扩展

W=(P8•P9)’ Y=(P2•P3•P6•P7)’

X=(P4•P5•P6•P7)’ Z=(P1•P3•P5•P7•P9)’

X

Y

Z

&

&

&

&

1. 二进制编码器——例:4线-2线编码器

Example

4:2编码器

计算机配有四个外部设备:声卡(A0),硬盘驱动器 (A1),鼠标(A2),网卡(A3),B0、B1为编码输出。

g

CD

AB 00 01 11 10 00 1 1 0 0 01 0 0 1 0 11 × × × × 10 0 0 × ×

g=A+CD+BC+BC

编码器(Encoders)

编码器——

♦ 特点:多输入、多输出的组合逻辑电路 ♦ 功能:将二进制码按照一定规律编排,使其具有特定含义

(如:8421BCD码用1000 代表数字8),与译码器互逆。

0 1 0 0 0 1 1 001 1 4

0 1 0 1 1 0 1 101 1 5

0 1 1 0 1 0 1 111 1 6

0 1 1 1 1 1 1 000 0 7

1 0 0 0 1 1 1 111 1 8

1 0 0 1 1 1 1 101 1 9

七段数码管

f g COM a b

a

f

b

g

e

c

d

e d COM c

A1

A0

典型应用——实现常规逻辑函数

A

D0

D1

D2

数字逻辑设计习题(7、8章)答案

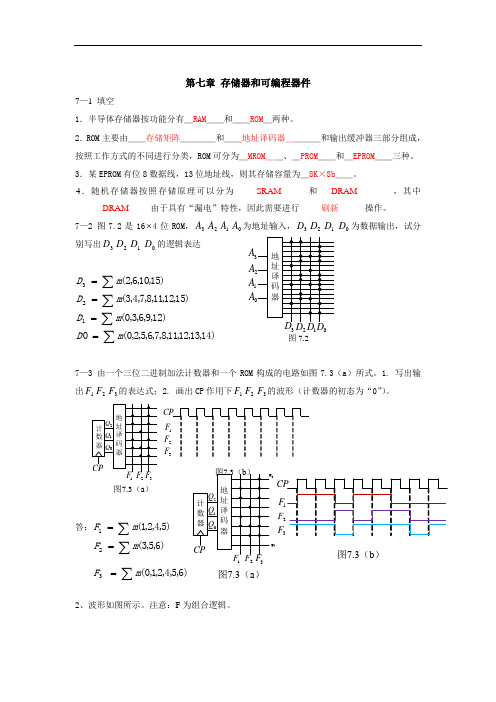

第七章 存储器和可编程器件7—1 填空1.半导体存储器按功能分有_RAM __和__ROM _两种。

2.ROM 主要由__存储矩阵____和__地址译码器____和输出缓冲器三部分组成,按照工作方式的不同进行分类,ROM 可分为_MROM __、_PROM __和_EPROM __三种。

3.某EPROM 有位8数据线,13位地址线,则其存储容量为_8K ×8b __。

4.随机存储器按照存储原理可以分为_____SRAM ______和___DRAM ________,其中______DRAM_____由于具有“漏电”特性,因此需要进行_____刷新______操作。

7—2 图7.2是16⨯4位ROM ,3A 2A 1A 0A 为地址输入,3D 2D 1D 0D 为数据输出,试分别写出3D 2D 1D 0D 的逻辑表达∑=)15,10,6,2(3m D ∑=)15,12,11,8,7,4,3(2m D ∑=)12,9,6,3,0(1m D ∑=)14,13,12,11,8,7,6,5,2,0(0m D7—3 由一个三位二进制加法计数器和一个ROM 构成的电路如图7.3(a )所式。

1. 写出输出1F 2F 3F 的表达式;2. 画出CP 作用下1F 2F 3F 的波形(计数器的初态为“0”)。

答:∑=)5,4,2,1(1m F ∑=)6,5,3(2m F∑=)6,5,4,2,1,0(3m F2、波形如图所示。

注意:F 为组合逻辑。

A A A A 3210图7.2123F F F 图7.3(a )123F F F 图7.3(a )图7.3(b )W 7第8章 脉冲波形的产生及整形8-1 图8.1(a )为由555定时器和D 触发器构成的电路,请问: 1. 555定时器构成的是哪种脉冲电路? 2. 在图(b )中画出C U O1U O2U 的波形; 3. 计算O1U O2U 的频率;4. 如果在555定时器的第5脚接入4V 的电压源,则O1U 的频率将为多少?答:1、该电路为多谐振荡器。

数字逻辑课件 07

A2 A1 A0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 0 0 0 1 0 1 0 。。。 1 1 1

Y0 0 1 1 1 1 1 1 1 1 1 1 1

Y1 1 0 1 1 1 1 1 1 1 1 1 1

Y2 Y3 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

junfu@

输 出 低 电 平 有 效

C

ollege of Computer Science & Information Engineering

数字逻辑

Digital Logic

利用4 利用4线-10线扩展为5线-32线译码器 10线扩展为5 线扩展为 32线译码器 1 0 1 0 1

14

Vcc f

g

a

b

c

Hale Waihona Puke de74LS48

1

A1 A2

LT

RBI

A3 A0 GND

BI / RBO LT : 灯测试端,低电平有效。检查笔段是否正常发光。 灯测试端,低电平有效。检查笔段是否正常发光。

junfu@

C

ollege of Computer Science & Information Engineering

数值比较器逻辑符号

junfu@

C

ollege of Computer Science & Information Engineering

数字逻辑

Digital Logic

4位数值比较器逻辑符号 位数值比较器逻辑符号

junfu@

C

数字逻辑

数字逻辑各章节重要知识考点

For personal use only in study and research; not forcommercial use第一章绪论知识点1:编码、无权代码、有权代码知识点2:数制、进制变换知识点3:定点数、浮点数知识点4:模拟信号、数字信号、模拟电路、数字电路一、选择题1、以下代码中为无权码的为( CD )。

A、8421BCD码B、5421BCD码C、余三码D、格雷码2、一位十六进制数可以用( C )位二进制数来表示。

A、1B、2C、4D、163、十进制数25用8421BCD码表示为( B )。

A、10 101B、0010 0101C、100101D、101014、在一个8位的存储单元中,能够存储的最大无符号整数是( CD )。

A、(256)10B、(127)10C、(FF)16D、(255)105、常用的BCD码有( CD )。

A、奇偶校验码B、格雷码C、8421码D、余三码6、与模拟电路相比,数字电路主要的优点有( BCD )。

A、容易设计B、通用性强C、保密性好D、抗干扰能力强二、判断题(正确打√,错误的打×)1、数字电路中用“1”和“0”分别表示两种状态,二者无大小之分。

(√)2、格雷码具有任何相邻码只有一位码元不同的特性。

(√)3、八进制数(18)8比十进制数(18)10小。

(×)4、在时间和幅度上都离散的信号是数字信号,语音信号不是数字信号。

(√)三、填空题1、数字信号的特点是在幅度上和时间上都是离散,其高电平和低电平常用 1和 0 来表示。

2、分析数字电路的主要工具是逻辑代数,数字电路又称作逻辑电路。

3、常用的BCD码有 8421BCD码、2421BCD码、5421BCD码、余三码等。

常用的可靠性代码有格雷码、奇偶校验码等。

4、(10110010.1011)2=( 262.54 )8=( B2.B )165、 ( 35.4)8 =(11101.1 )2 =(29.5)10=(1D.8)16=(0010 100.0101)8421BCD6、(39.75 )10=(100111.11)2=(47.6)8=(27.C)167、 ( 5E.C)16=(1011110.11)2=(136.6)8=(94.75)10= (1001 0100.0111 0101)8421BCD8、( 0111 1000)8421BCD =(1001110)2=(116)8=(78)10=(4E)16第二章 逻辑代数基础知识点1:逻辑函数、逻辑函数的六种表示方式知识点2:基本的逻辑运算(与、或、非、与非、或非、与或非、异或)、逻辑运算规则 知识点3:三个定理:代入定理、反演定理、对偶定理知识点4:逻辑函数两种标准形式、逻辑函数的变换(与非-与非、或非-或非、与或非式) 知识点5:逻辑函数的公式法化简、卡若图表示和卡诺图法化简、具有无关项的卡诺图化简一、选择题1、当逻辑函数有n 个变量时,共有( D )个变量取值组合。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

习 题 七

1. 用4位二进制并行加法器设计一个实现8421码对9求补的逻辑电

路。

解答

设8421码为B 8B 4B 2B 1 ,其对9的补数为C 8C 4C 2C 1 ,关系如下:

1

B B B B 1001B B B B 1001

C C C C 12481

2481248+-=-=

相应逻辑电路图如图1所示。

图 1

2. 用两个4位二进制并行加法器实现2位十进制数8421码到二进制码的转换。

解答

设两位十进制数的8421码为D 80D 40D 20D 10D 8D 4D 2D 1 ,相应二进制数为B 6B 5B 4B 3B 2B 1B 0,则应有B 6B 5B 4B 3B 2B 1B 0 = D 80D 40D 20D 10×1010+D 8D 4D 2D 1,运算如下:

× D 80 1

D 40 0 D 20 1 D 10 0 + D 80 D 40 D 80 D 20

D 40 D 10 D 8

D 20

D 4 D 10

D 2 D 1

B 6

B 5

B 4 B 3

B 2

B 1

B 0

据此,可得到实现预定功能的逻辑电路如图2所示。

图 2

3. 用4位二进制并行加法器设计一个用8421码表示的1位十进制加法器。

解答

分析:由于十进制数采用8421码,因此,二进制并行加法器输入被加数和

加数的取值范围为0000~1001(0~9),输出端输出的和是一个二进制数,数的范围为0000~10011(0~19,19=9+9+最低位的进位)。

因为题目要求运算的结果也

B 6

B 5 B 4 B 3

B 2 B 1 B 0

D 80 D 8 D 20 D 10

D 2

D 4

D 10 D 1

D 20 D 40 D 40 D 80 0

T693

T693

是8421码,因此需要将二进制并行加法器输出的二进制数修正为8421码。

设输出的二进制数为FC 4 F 4 F 3 F 2 F 1,修正后的结果为'

1'

2'3'

4'

4F F F F FC ,可列出修正函数真值表如表1所示。

根据表1写出控制函数表达式,经简化后可得:

据此,可画出逻辑电路图如图3所示。

图3

4. 用一片3-8线译码器和必要的逻辑门实现下列逻辑函数表达式。

B

A A

B F B A F C

AB C A F 321+=+=+=

解答

假定采用T4138和与非门实现给定函数功能,可将逻辑表达式变换如下:

7

610376321026

201m m m m )7,6,1,0(B A AB F m m m m m m 6,7)m(0,1,2,3,

B A F m m m )6,2,0(

C AB C A F ⋅⋅⋅==+=⋅⋅⋅⋅⋅==+=⋅⋅==+=∑∑∑m m 逻辑电路图如图4所示。

图4

5. 用一片4-16线译码器和适当的逻辑门设计一个1位十进制数2421

码的奇偶位产生电路(假定采用奇检验)。

解答

设2421码为ABCD, 奇偶检验位为P,根据题意可列出真值表如表2所示。

ABCD P ABCD P

0000 0001 0010 0011 0100 1

1

1011

1100

1101

1110

1111

1

1

由真值表可得:

∑

=5)

m(0,3,12,1

D)

C,

B,

P(A,

假定采用74LS154和与非门实现给定函数功能,可画出逻辑电路图如图5

所示。

图5

6. 当优先编码器74LS148的Is接0,输入I7I6I5I4I3I2I1I0 =11010001

时,输出为什么状态?

解答

Q C Q B Q A=010(编码I5), Q EX=0(编码群输出端,允许编码且有信号输入时为0), Q S=1(允许输出端,允许编码且有信号输入时为1)。

7.试用4路数据选择器实现余3码到8421码的转换。

解答

假定用ABCD表示余3码,WXYZ表示8421码,并选择A、B作为选择变量,可求出各4路数据选择器的数据输入端分别为:

1

D ,D D D 0,D :Z 0D D,C D D 0,D :Y 0D ,CD D CD,D 0,D :X 1D CD,D 0,D D :W 3210321032103210=====⊕===========

用4个四路数据选择器和4个逻辑门构造出该代码转换电路,逻辑图如图6所

示。

图6

8. 当4路选择器的选择控制变量A 1、A 0接变量A 、B ,数据输入端D 0、

D 1、D 2、D 3依次接C 、0、0、C 时,电路实现何功能? 解答

输出函数表达式如下:

ABC C B A W +⋅⋅=

电路实现三变量“一致性”检测功能。

9. 用4位二进制同步可逆计数器T4193和必要的逻辑门实现模12加

法计数器。

解答

根据T4193的逻辑功能,可画出模12加法计数器的逻辑电路图如图7所示。

图7

10. 用T1194双向移位寄存器和必要的逻辑门设计一个00011101序列 信号发生器。

解答

设寄存器初始状态Q 0Q 1Q 2=101,从Q 2产生输出,可列出反馈函数真值表如表3

所示。

CP

Q 0Q 1Q 2

F(D R )

0 1 2 3 4 5 6 7

101 110 111 011 001 000 100 010

1 1 0 0 0 1 0 1

由表3可写出反馈函数表达式:

2

102102102102

1021021021202

10210210210R Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q )Q Q (Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q )F(D ⊕=⊕=⋅+⋅=++=++=+++=

设计出该序列发生器的逻辑电路图如图8所示。

图8

11. 在图9所示电路中,若取R 1=2R 2 ,请问输出矩形波的占空比为多少?

图9 解答

43432222

22222==++R R R R R R

12. 分析图10所示由定时器5G555构成的多谐振荡器。

图10 (1)计算其振荡周期;

(2)若要产生占空比为50%的方波,R 1和R 2的取值关系如何?

解答

(1) 振荡周期:

)C

R 0.7(R C 0.7R C 0.7R t t T 2121L

H W +=+=+=

(2) 占空比: 2

11

211W H R R R )C R 0.7(R C 0.7R T t Q +=+==

要产生占空比为50%的方波,应有R 1=R 2 。

13. 将5G555定时器按图11(a)所示连接,输入波形如图11(b)所示。

请画出定时器输出波形,并说明该电路相当于什么器件。

图11 5G555连线图和有关波形图

解答

假定电路的初始输出为高,可画出输出波形如图12所示。

图12

由输入输出波形图可知,该电路的功能相当于一个基本R-S触发器。

14. D/A转换器有哪些主要参数?通常用什么参数来衡量转换精度?

解答

D/A转换器的主要参数有分辨率、非线性误差、绝对精度、建立

时间。

通常用分辨率衡量转换精度。

15. DAC1210是12位D/A 芯片,请问其分辨率为多少?(用百分数表示)解答

分辨率=%02.04095112112112≈=-=-n 16. DAC0832由哪几部分组成?可以构成哪几种工作方式?每种方式如

何控制?

解答

DAC0832由两个8位数据缓冲寄存器、一个8位D/A 转换器和三个控制逻辑门组成,可以构成双缓冲、单缓冲和直通三种工作方式。

工作方式选择受控制信号XFER 、 WR 、 WR 、 、ILE CS 21的控制。

双缓冲方式:首先在1WR 、 、ILE CS 控制下将数据锁存到输入寄

存器,然后在 2WR ,XFER 控制下将输入寄存器中数

据锁存到DAC 寄存器。

单缓冲方式:令输入寄存器和DAC 寄存器中的一个处于受控状态,

另一个处于直通状态。

直通方式:令输入寄存器和DAC 寄存器中均处于直通状态。

17. 常见集成A/D 转换器按转换方法的不同可分成哪几种类型?各有

何特点?

解答

集成A/D 转换器按转换方法的不同可分成并行比较型、逐次比较型和双积分型几种类型。

并行比较型转换速度高,但由于内部线

路较复杂,一般分辨率较低;逐次比较型速度较快,精度高;双积分型精度高、抗干扰能力强,但速度较慢。

18. ADC0809如何实现对8路模拟量输入的选择?当它与微机连接时是

否要外加三态缓冲器?

解答

ADC0809由3根地址选择线实现对8路模拟量输入的选择。

由于ADC0809内部带有三态输出缓冲器,所以当它与微机连接时不需要外加三态缓冲器。