内电层与内电层分割

Allegro操作说明(中文) Word 文档

26、非电气引脚零件的制作1、建圆形钻孔:(1)、parameter:没有电器属性(non-plated)(2)、layer:只需要设置顶层和底层的regular pad,中间层以及阻焊层和加焊层都是null。

注意:regular pad要比drill hole大一点27、Allegro建立电路板板框步骤:1、设置绘图区参数,包括单位,大小。

2、定义outline区域3、定义route keepin区域(可使用Z-copy操作)4、定义package keepin区域5、添加定位孔28、Allegro定义层叠结构对于最简单的四层板,只需要添加电源层和底层,步骤如下:1、Setup –> cross-section2、添加层,电源层和地层都要设置为plane,同时还要在电气层之间加入电介质,一般为FR-43、指定电源层和地层都为负片(negtive)4、设置完成可以再Visibility看到多出了两层:GND和POWER5、铺铜(可以放到布局后再做)6、z-copy –> find面板选shape(因为铺铜是shape)–> option面板的copy to class/subclass选择ETCH/GND(注意选择create dynamic shape)完成GND层覆铜7、相同的方法完成POWER层覆铜Allegro生成网表1、重新生成索引编号:tools –> annotate2、DRC检查:tools –> Design Rules Check,查看session log。

3、生成网表:tools –> create netlist,产生的网表会保存到allegro文件夹,可以看一下session log内容。

29、Allegro导入网表1、file –> import –> logic –> design entry CIS(这里有一些选项可以设置导入网表对当前设计的影响)2、选择网表路径,在allegro文件夹。

PADS内电层分割与铺铜

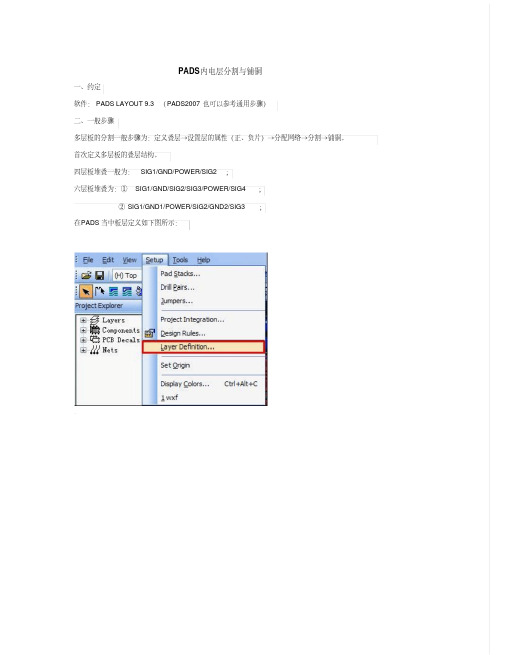

P A D S内电层分割与铺铜(总9页)-CAL-FENGHAI.-(YICAI)-Company One1-CAL-本页仅作为文档封面,使用请直接删除PADS内电层分割与铺铜一、约定软件:PADS LAYOUT 9.3(PADS2007也可以参考通用步骤)二、一般步骤多层板的分割一般步骤为:定义叠层→设置层的属性(正、负片)→分配网络→分割→铺铜。

首次定义多层板的叠层结构。

四层板堆叠一般为:SIG1/GND/POWER/SIG2;六层板堆叠为:①SIG1/GND/SIG2/SIG3/POWER/SIG4;②SIG1/GND1/POWER/SIG2/GND2/SIG3;在PADS当中板层定义如下图所示:其次,为电源层分配电源网络。

上图中强调一下“Plane Type”的问题。

首先从工艺角度讲,内电层实物为薄薄的铜箔。

在制造流程上有“正片”和“负片”之分。

在PADS LAYOUT中,内电层属性配置当中,CAM PLANE为负片属性,其他两层为正片属性。

以下部分是摘自PADS help文件:· No Plane—Prevents planes from being added to the layer. The No Plane layer is availablefor routing. If you select No Plane, you can only create Copper and Copper Pour areas on the layer.· CAM Plane—Sets the entire layer to be solid copper and connected to only one net. The CAM Plane layer is a negative image, and the copper does not appear in the design a s it normally does for all other copper objects. You can not manipulate the shape/ outline of the copper on this layer since it is generated automatically and covers t he entire layer. This is an outmoded layer type. You can not route traces on a CA M Plane layer. Copper Pours and Plane areas can not be created on CAM Plane layers.· Split/Mixed Plane—Enables one or more planes on the layer, and enables routing on the layer. Rout es can be placed within or without plane areas. Plane areas avoid traces within t heir outline by a clearance area defined in the design rules. Copper Pours can no t be placed on Split/Mixed layers. Plane areas are created on Split/Mixed plane la yers and are similar to but more feature-packed than Copper Pours.简单的讲,NO PLANE自由度更大一些,除了“Plane Area”以及相关的操作命令不能用以外,我们可以在NO PLANE层进行布线、铺铜、铺铜切割、2D图形边框的绘制等常用操作。

第十一章U盘PCB板设计

2021/9/17

35

11.4.1 确定布局方案

在高密度电路板中,是否需要双面放置元件是 设计者首先要考虑的问题。一般情况下,如果 在顶层能够完成元件的布局,尽量不要将元件 放置在底层,因为一方面会提高电路板的设计 难度和成本,另一方面也会增加元件装配的工 序和难度。但对于U盘电路板而言,如果直接 将元件放置在顶层,由于电路板太小,部分元 件连放置的位置都没有,所以必须采取双面放 置元件的办法。仔细分析原理图可以知道,U 盘主要由以U2(IC1114)为核心的控制器电路 和以U3(K9F0BDUDB)组成。所以可以考虑 将二部分电路分别放置在顶层和底层,具体将 U3(K9F0BDUDB)为核心的存储器电路放置 在顶层元件面,而将U2(IC1114)为核心的控 制器电路放置在底层的焊接面。

第11章

U盘PCB板设计

2021/9/17

1

本章学习目标

本章以制作U盘PCB板为例,介绍SMT多层板的制作技 巧和编辑修改方法,以达到以下学习目标: 理解多层板的含义,掌握多层板的创建方法。 理解内电层的含义,内电层的属性设置和分割方法 掌握常用SMT元件的引脚封装。 掌握SMT元件引脚封装的制作方法。 掌握手工修改导线的常用方法。

2021/9/17

46

(3)此时点击工作区右下方的【Inspect】按钮,弹出 如图所示的Inspect面板,将【Text Heigh】字符高度 栏修改为原来的一半,即“30mil”,将【Text Width】 文字线条宽度修改为“5mil”,按回车键确认输入。

2021/9/17

47

3. 确定顶层核心元件的位置

自制封装库UPAN.PcbLib

4

1. 确定AT1201的封装

2021/9/17

PADS内电层分割与铺铜

PADS内电层分割与铺铜一、约定软件:PADS LAYOUT 9.3(PADS2007也可以参考通用步骤)二、一般步骤多层板的分割一般步骤为:定义叠层→设置层的属性(正、负片)→分配网络→分割→铺铜。

首次定义多层板的叠层结构。

四层板堆叠一般为:SIG1/GND/POWER/SIG2;六层板堆叠为:① SIG1/GND/SIG2/SIG3/POWER/SIG4;② SIG1/GND1/POWER/SIG2/GND2/SIG3;在PADS当中板层定义如下图所示:其次,为电源层分配电源网络。

上图中强调一下“Plane Type”的问题。

首先从工艺角度讲,内电层实物为薄薄的铜箔。

在制造流程上有“正片”和“负片”之分。

在PADS LAYOUT中,内电层属性配置当中,CAM PLANE 为负片属性,其他两层为正片属性。

以下部分是摘自PADS help文件:· No Plane — Prevents planes from being added to the layer. The No Plane layer is available for routing. If you select No Plane, you can only create Copper and Copper Pour areas on the layer.· CAM Plane — Sets the entire layer to be solid copper and connected to only one net. The CAM Plane la yer is a negative image, and the copper does not appear in the design as it normally does for all other copper objects. You can not manipulate the shape/outline of the copper on this laye r since it is generated automatically and covers the entire layer. This is an outmoded layer ty pe. You can not route traces on a CAM Plane layer. Copper Pours and Plane areas can not b e created on CAM Plane layers.· Split/Mixed Plane — Enables one or more planes on the layer, and enables routing on the layer. Routes can be placed within or without plane areas. Plane areas avoid traces within their outline by a clear ance area defined in the design rules. Copper Pours can not be placed on Split/Mixed layers. Plane areas are created on Split/Mixed plane layers and are similar to but more feature-pack ed than Copper Pours.简单的讲,NO PLANE自由度更大一些,除了“Plane Area”以及相关的操作命令不能用以外,我们可以在NO PLANE层进行布线、铺铜、铺铜切割、2D图形边框的绘制等常用操作。

PADS内电层分割与铺铜剖析

all other copper objects. You can not manipulate the shape/outline of the copper on this laye

r since it is generated automatically and covers the entire layer. This is an outmoded layer ty

pe. You can not route traces on a CAM Plane layer. Copper Pours and Plane areas can not b

e created on CAM Plane layers.

·

Split/Mixed Plane

— Enables one or more planes on the layer, and enables routing on the layer. Routes can be

赋予该属性的内

电层,只能通过“ Plane area ”命令以及“ auto plane separate ”命令进行电源层分割。

注意:电源层层属性的选择也可以选择为其他性质(如

NO PLANE )。唯一需要注意的是,前期

层属性的不同将导致后期铺铜方式的改变。否则就会发生无法铺铜或者铺铜错误的情况。

第三、分割操作。下文主要说明电源层为 Split/Mixed Plane 属性的情况。该属性下,分割操作 使用 Auto plane separate 命令。 这里首先绘制铺铜的 keepout 层, 这样可以防止每层的敷铜边界 不一致的问题。利用 Plane area 命令依据 PCB 外框画出整体敷铜边框,完成后。右键选择 “select shape ”,双击选择该边框或者右键调用属性菜单。弹出以下菜单:

POWER PCB内层正负片设置和内电层分割以及铺铜方面

POWER PCB内层正负片设置和内电层分割以及铺铜方面看到很多网友提出的关于POWER PCB内层正负片设置和内电层分割以及铺铜方面的问题,说明的帖子很多,不过都没有一个很系统的讲解。

今天抽空把这些东西联系在一起集中说明一下。

时间仓促,如有错误疏漏指出还请多加指正!一 POWER PCB的图层与PROTEL的异同我们做设计的有很多都不止用一个软件,由于PROTEL上手容易的特点,很多朋友都是先学的P ROTEL后学的POWER,当然也有很多是直接学习的POWER,还有的是两个软件一起用。

由于这两个软件在图层设置方面有些差异,初学者很容易发生混淆,所以先把它们放在一起比较一下。

直接学习POWER的也可以看看,以便有一个参照。

首先看看内层的分类结构图===================================软件名属性层名用途----------------------------------- PROTEL: 正片 MIDLAYER 纯线路层 MIDLAYER 混合电气层(包含线路,大铜皮)负片 INTERNAL 纯负片(无分割,如GND) INTERNAL 带内层分割(最常见的多电源情况)----------------------------------- POWER : 正片 NO PLANE 纯线路层 NO PLANE 混合电气层(用铺铜的方法 COPPER POUR) SPLIT/MI XED 混合电气层(内层分割层法 PLACE AREA)负片 CAM PLANE 纯负片(无分割,如GND)===================================从上图可以看出,POWER与PROTEL的电气图层都可分为正负片两种属性,但是这两种图层属性中包含的图层类型却不相同。

1.PROTEL只有两种图层类型,分别对应正负片属性。

而POWER则不同,POWER中的正片分为两种类型,NO PLANE和SPLIT/MIXED2.PROTEL中的负片可以使用内电层分割,而POWER的负片只能是纯负片(不能应用内电层分割,这一点不如PROTEL)。

PCB设计---分割内电层

#1怎样分割内电层?PROTEL99的电性图层分为两种,打开一个PCB设计文档按,快捷键L,出现图层设置窗口。

左边的一种(SIGNAL LAYER)为正片层,包括TOP LAYER、BOTTOM LAYER和MIDLAYER,中间的一种(INTERNAL PLANES)为负片层,即INTERNAL LAYER。

这两种图层有着完全不同的性质和使用方法。

正片层一般用于走纯线路,包括外层和内层线路。

负片层则多用来做地层和电源层。

因为在多层板中的地层和电源层一般都是用整片的铜皮来作为线路(或做为几个较大块的分割区域),如果用MIDLAYER即正片层来做的画则必须用铺铜的方式来实现,这样将使整个设计数据量非常大,不利于数据交流传递,且会影响设计刷新速度。

而用负片则只需在外层与内层的连接处生成一个花孔(THERMAL PAD)即可,对于设计和数据传递都非常有利。

内层的添加与删除在一个设计中,有时会遇到变换板层的情况。

如把较复杂的双面板改为四层板,或把对信号要求较高的四层板升级为六层板等等。

这时需要新增电气图层,可以如下*作:DESIGN-LAYER STACK MANAGER,在左边有当前层叠结构的示意图。

点击想要添加新层位置的上面一个图层,如TOP,然后点击右边的ADD LAYER(正片)或ADD PLANE(负片),即可完成新图层的添加。

注意如果新增的图层使PLANE(负片)层的话,一定要给这个新层分配相应的网络(双击该层名)!这里分配的网络只能有一个(一般地层分配一个GND就可以了),如果想要在此层(如作为电源层)中添加新网络,则要在后面的操作中做内层分割才能达到,所以这里先分配一个连接数量较多的网络即可。

如点击ADD LAYER则会新增一个MIDLAYER(正片),应用方法和外层线路完全相同。

如果想应用混合电气层,即既有走线又有电源地大铜面的方法,则必须使用ADD LAYER 来生成的正片层来设计(原因见下)。

Allegro原理图和PCB设计流程学习指南

Allegro原理图和PCB设计流程学习指南一、非电气引脚零件的制作1、建圆形钻孔:1)、parameter:没有电器属性(non-plated)2)、layer:只需要设置顶层和底层的regular pad,中间层以及阻焊层和加焊层都是null。

注意:regular pad要比drill hole大一点。

二、Allegro建立电路板板框步骤:1、设置绘图区参数,包括单位,大小。

2、定义outline区域3、定义route keepin区域(可使用Z-copy操作)4、定义package keepin区域5、添加定位孔三、Allegro定义层叠结构对于最简单的四层板,只需要添加电源层和底层,步骤如下:1、Setup –> cross-section2、添加层,电源层和地层都要设置为plane,同时还要在电气层之间加入电介质,一般为FR-43、指定电源层和地层都为负片(negtive)4、设置完成可以再Visibility看到多出了两层:GND和POWER5、铺铜(可以放到布局后再做)6、z-copy –> find面板选shape(因为铺铜是shape)–> option面板的copy to class/subclass选择ETCH/GND(注意选择create dynamic shape)完成GND 层覆铜7、相同的方法完成POWER层覆铜四、Allegro生成网表1、重新生成索引编号:tools –> annotate2、DRC检查:tools –> Design Rules Check,查看session log。

3、生成网表:tools –> create netlist,产生的网表会保存到allegro文件夹,可以看一下session log内容。

五、Allegro导入网表1、file –> import –> logic –> design entry CIS(这里有一些选项可以设置导入网表对当前设计的影响)2、选择网表路径,在allegro文件夹。

protel99SE四层板设计及内电层分割入门

protel99SE四层板设计及内电层分割入门[日期:2011-12-16] 来源:作者:pcb_dz [字体:大中小] 本教程将详细的讲解Protel99SE的四层板的设计过程,以及在其中的内电层分割的用法。

事先声明:本教程用于初学者的入门与提高;对于高手们,也欢迎看看,帮小弟指出其中不当的做法!下面,就打开你的电脑及软件开始了。

(- - - - - -好像是废话, 嘿嘿..... )一、准备工作新建一个DDB文件,再新建相关的原理图文件, 并做好相关准备设计PCB的准备工作,这个相信想画四层板的朋友都会, 不用我多讲了。

二、新建文件新建一个PCB文件, 在KeepOutLayer层画出PCB的外框, 如下图,用过Protel的朋友们应该都会。

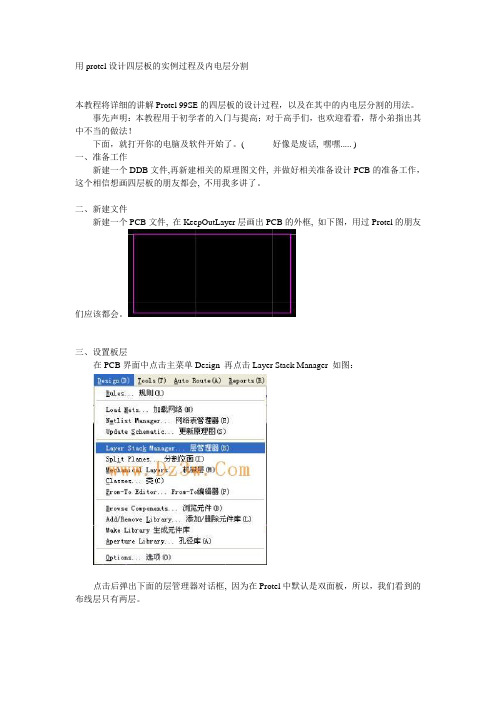

三、设置板层在PCB界面中点击主菜单Design 再点击Layer Stack Manager 如图:点击后弹出下面的层管理器对话框, 因为在Protel中默认是双面板,所以,我们看到的布线层只有两层。

现在我们来添加层,先单击左边的TopLayer, 再单击层管理器右上角的Add Plane按钮,添加内电层,这里说明一下,因为现在讲的是用负片画法的四层板,所以,需要添加内电层,而不是Add Layer。

单击后,将在TopLayer的下自动增加一个层,双击该层,我们就可以编辑这一层的相关属性,如下图:在Name对应的项中,填入V CC,点击确定关闭对话框,也就是将该层改名为VCC,作为设计时的电源层。

按同样的方法,再添加一个GND层。

完成后如图:四、导入网络回到原理图的界面,单击主菜单Design ==> Update PCB如图:=>选择要更新的PCB文件,点击Apply ,再点击左边的,查看我们在原理图中所做的设计是否正确。

这里,我们把项打上勾,只查看错误的网络。

在这里,我们没有发现有任何错误网络时,可以单击将网络导入PCB文件了。

这种导入网络的方法是Protel的原理图导入网络到PCB的一个很方便的方法,不用再去生成网络表了。

AD或Protel PCB四层板设计讲解

用protel设计四层板的实例过程及内电层分割--------------------------------------------------------------------------------本教程将详细的讲解Protel 99SE的四层板的设计过程,以及在其中的内电层分割的用法。

事先声明:本教程用于初学者的入门与提高;对于高手们,也欢迎看看,帮小弟指出其中不当的做法!下面,就打开你的电脑及软件开始了。

(- - - - - -好像是废话, 嘿嘿..... )一、准备工作新建一个DDB文件,再新建相关的原理图文件, 并做好相关准备设计PCB的准备工作,这个相信想画四层板的朋友都会, 不用我多讲了。

二、新建文件新建一个PCB文件, 在KeepOutLayer层画出PCB的外框, 如下图,用过Protel的朋友们应该都会。

三、设置板层在PCB界面中点击主菜单Design 再点击Layer Stack Manager 如图:点击后弹出下面的层管理器对话框, 因为在Protel中默认是双面板,所以,我们看到的布线层只有两层。

现在我们来添加层,先单击左边的TopLayer, 再单击层管理器右上角的Add Plane按钮,添加内电层,这里说明一下,因为现在讲的是用负片画法的四层板,所以,需要添加内电层,而不是Add Layer。

单击后,将在TopLayer的下自动增加一个层,双击该层,我们就可以编辑这一层的相关属性,如下图:在Name对应的项中,填入VCC,点击确定关闭对话框,也就是将该层改名为VCC,作为设计时的电源层。

按同样的方法,再添加一个GND层。

完成后如图:四、导入网络回到原理图的界面,单击主菜单Design ==> Update PCB如图:=>选择要更新的PCB文件,点击Apply ,再点击左边的,查看我们在原理图中所做的设计是否正确。

这里,我们把项打上勾,只查看错误的网络。

内电层与内电层分割

内电层与内电层分割在系统提供的众多工作层中,有两层电性图层,即信号层与内电层,这两种图层有着完全不同的性质和使用方法。

信号层被称为正片层,一般用于纯线路设计,包括外层线路和内层线路,而内电层被称为负片层,即不布线、不放置任何元件的区域完全被铜膜覆盖,而布线或放置元件的地方则是排开了铜膜的。

在多层板的设计中,由于地层和电源层一般都是要用整片的铜皮来做线路(或作为几个较大块的分割区域),如果要用MidLayer(中间层)即正片层来做的话,必须采用敷铜的方法才能实现,这样将会使整个设计数据量非常大,不利于数据的交流传递,同时也会影响设计刷新的速度,而使用内电层来做,则只需在相应的设计规则中设定与外层的连接方式即可,非常有利于设计的效率和数据的传递。

Altium Designer 7.0系统支持多达 16层的内电层,并提供了对内电层连接的全面控制及 DRC校验。

一个网络可以指定多个内电层,而一个内电层也可以分割成多个区域,以便设置多个不同的网络。

7.2.1内电层PCB设计中,内点层的添加及编辑同样是通过【图层堆栈管理器】来完成的。

下面以一个实际的设计案例来介绍内电层的操作。

请读者先自己建立一个PCB设计文件或者打开一个现成的PCB设计文件。

在 PCB编辑器中,执行【Design】|【Layer Stack Manager】命令,打开【Layer Stack Manager】。

单击选取信号层,新加的内电层将位于其下方。

在这里选取的信号层,之后单击【Add Layer】按钮,一个新的内电层即被加入到选定的信号层的下方。

双击新建的内电层,即进入【EditLayer】对话框中,可对其属性加以设置,如图7-13所示。

在对话框内可以设置内电层的名称、铜皮厚度、连接到的网络及障碍物宽度等。

这里的障碍物即“Pullback”,是在内电层边缘设置的一个闭合的去铜边界,以保证内电层边界距离 PCB边界有一个安全间距,根据设置,内电层边界将自动从板体边界回退。

protel99的图层设置与内电层分割

protel99的图层设置与内电层分割protel99的图层设置与内电层分割protel99的图层设置与内电层分割引用:PROTEL99的电性图层分为两种,打开一个PCB设计文档按,快捷键L,出现图层设置窗口。

左边的一种(SIGNAL LAYER)为正片层,包括TOP LAYER、BOTTOM LAYER和MIDLAYE R,中间的一种(INTERNAL PLANES)为负片层,即INTERNAL LAYER。

这两种图层有着完全不同的性质和使用方法。

正片层一般用于走纯线路,包括外层和内层线路。

负片层则多用来做地层和电源层。

因为在多层板中的地层和电源层一般都是用整片的铜皮来作为线路(或做为几个较大块的分割区域),如果用MIDLAYER即正片层来做的画则必须用铺铜的方式来实现,这样将使整个设计数据量非常大,不利于数据交流传递,且会影响设计刷新速度。

而用负片则只需在外层与内层的连接处生成一个花孔(THERMAL PAD)即可,对于设计和数据传递都非常有利。

内层的添加与删除在一个设计中,有时会遇到变换板层的情况。

如把较复杂的双面板改为四层板,或把对信号要求较高的四层板升级为六层板等等。

这时需要新增电气图层,可以如下*作:DESIGN-LAYER STACK MANAGER,在左边有当前层叠结构的示意图。

点击想要添加新层位置的上面一个图层,如TOP,然后点击右边的ADD LAYER(正片)或ADD PLANE(负片),即可完成新图层的添加。

注意如果新增的图层使PLANE(负片)层的话,一定要给这个新层分配相应的网络(双击该层名)!这里分配的网络只能有一个(一般地层分配一个GND就可以了),如果想要在此层(如作为电源层)中添加新网络,则要在后面的操作中做内层分割才能达到,所以这里先分配一个连接数量较多的网络即可。

如点击ADD LAYER则会新增一个MIDLAYER(正片),应用方法和外层线路完全相同。

如果想应用混合电气层,即既有走线又有电源地大铜面的方法,则必须使用ADD LAYER来生成的正片层来设计(原因见下)。

Altium Designer AD13多层板内电层负片分割使用

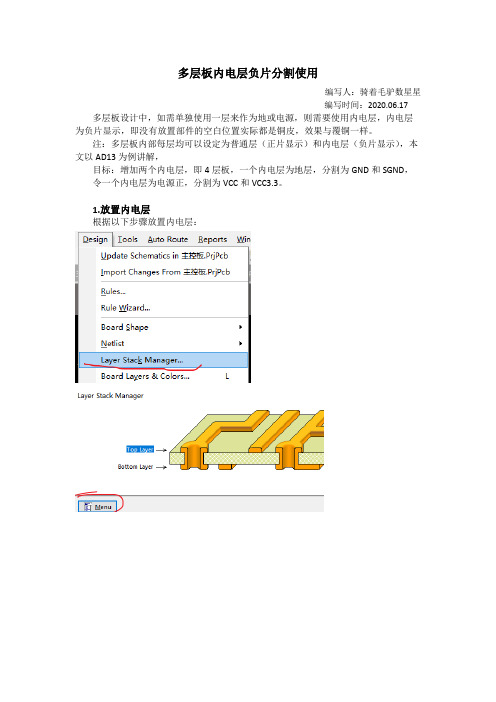

多层板内电层负片分割使用编写人:骑着毛驴数星星编写时间:2020.06.17 多层板设计中,如需单独使用一层来作为地或电源,则需要使用内电层,内电层为负片显示,即没有放置部件的空白位置实际都是铜皮,效果与覆铜一样。

注:多层板内部每层均可以设定为普通层(正片显示)和内电层(负片显示),本文以AD13为例讲解,目标:增加两个内电层,即4层板,一个内电层为地层,分割为GND和SGND,令一个内电层为电源正,分割为VCC和VCC3.3。

1.放置内电层根据以下步骤放置内电层:点击增加内电层。

双击上图红圈位置,修改层名称和连接的网络.名称为G,网络为GND然后继续添加一个内电层,名称为V,网络为VCC5。

下面的层标签应该会出现V和G的层。

到此,即添加了两个内电层,效果如下。

注意:如果没有出现G和V,那么需要点击下图位置,确保上图打钩即可。

2.设置仅显示一层,方面分割等操作同样在上图的中,点击红圈位置,改为效果如下:3.内电层分割点击AD软件左下角的。

选择split plane editor,下面即可出来G和V的显示,右侧的split count指分割数量,1为没有分割。

然后开始画线,选择G层,从边界开始画,出现大十字说明光标在边界上。

如图,花了一个封闭的线,此时看左侧的split Count,已经变为2了双击图示位置,出现一个选择网络的窗口,选择SGND即可。

同理可以设置VCC和VCC3.3.如果需要把每层中两个区域分隔开,保持一定距离,需要使用图示功能。

效果如下:可以发现,用刚才工具画的地方没有灰蒙蒙的GND铜皮了!!!4.内电层与过孔、焊盘等连接方式观察PCB,发现以下问题,过孔与焊盘都是relief connect,但实际上TOP和bottrom层我都已经设置过孔与覆铜直连了,但这种内电层与覆铜还是有差别的。

个人习惯过孔与铜皮直连,焊盘与铜皮采用relief connect。

设置内电层过孔直连:步骤1:图示位置右键新建步骤2:按照下图对新建的规则修改内容即可效果如图,可以看到过孔已经直连:。

protel99的图层设置与内电层分割

protel99的图层设置与内电层分割protel99的图层设置与内电层分割protel99的图层设置与内电层分割引用:PROTEL99的电性图层分为两种,打开一个PCB设计文档按,快捷键L,出现图层设置窗口。

左边的一种(SIGNAL LAYER)为正片层,包括TOP LAYER、BOTTOM LAYER和MIDLAYE R,中间的一种(INTERNAL PLANES)为负片层,即INTERNAL LAYER。

这两种图层有着完全不同的性质和使用方法。

正片层一般用于走纯线路,包括外层和内层线路。

负片层则多用来做地层和电源层。

因为在多层板中的地层和电源层一般都是用整片的铜皮来作为线路(或做为几个较大块的分割区域),如果用MIDLAYER即正片层来做的画则必须用铺铜的方式来实现,这样将使整个设计数据量非常大,不利于数据交流传递,且会影响设计刷新速度。

而用负片则只需在外层与内层的连接处生成一个花孔(THERMAL PAD)即可,对于设计和数据传递都非常有利。

内层的添加与删除在一个设计中,有时会遇到变换板层的情况。

如把较复杂的双面板改为四层板,或把对信号要求较高的四层板升级为六层板等等。

这时需要新增电气图层,可以如下*作:DESIGN-LAYER STACK MANAGER,在左边有当前层叠结构的示意图。

点击想要添加新层位置的上面一个图层,如TOP,然后点击右边的ADD LAYER(正片)或ADD PLANE(负片),即可完成新图层的添加。

注意如果新增的图层使PLANE(负片)层的话,一定要给这个新层分配相应的网络(双击该层名)!这里分配的网络只能有一个(一般地层分配一个GND就可以了),如果想要在此层(如作为电源层)中添加新网络,则要在后面的操作中做内层分割才能达到,所以这里先分配一个连接数量较多的网络即可。

如点击ADD LAYER则会新增一个MIDLAYER(正片),应用方法和外层线路完全相同。

如果想应用混合电气层,即既有走线又有电源地大铜面的方法,则必须使用ADD LAYER来生成的正片层来设计(原因见下)。

第7章 PCB设计高级进阶

第7章 PCB 设计高级进阶前面一章讲述了Altium Designer 7.0的PCB 绘制的基本步骤。

Altium Designer 7.0提供了许多提高PCB 设计效率的功能模块,掌握这些功能模块的使用将使用户在今后的电路板设计中设计出更完美的产品。

本章将以Altium Design7.0自带的例子“4 Port Serial Interface.PRJPCB ”为例对PCB 设计的高级进阶的相关内容进行介绍。

——附带光盘“视频\7.avi”文件。

内电层操作生成各种报表使用智能PDF 向导建立PDF 文档交互定位交互选择对象分类管理器4 Port Serial Interface本章要点本章案例7.1 PCB层集合管理层集合是指一种由项目电路板中的一个或几个层的可视状态组合起来,构成一个集合。

用户可以设置其属性以适应自己的使用习惯。

它的主要作用是控制层的显示状态。

PCB层集合可以在层集合管理器对话框中定义。

可定义任意数量的层集合,板卡设计中的任何层次都可以包含在层集合中。

单击工作区左下方的层集合控制按钮启动层集合管理器,固定工作空间,显示不同的层集合,如图7-1。

在层集合中引入“&”字符即可将其后面的字符定义为快捷键。

也可以通过菜单命令【Design】|【Manage Layer Sets】(快捷键:D+T+选取的层集合)启动层集合管理器,如图7-2。

层集合信息与板卡设计数据一起存储,因此可以随着设计一起移动。

用户也可以保存想要的层集合,通过层集合管理对话框将其装载到其他的板卡设计中。

图 7-2 层集合控制按钮图 7-1 【Manage Layer Sets】命令菜单7.1.1 快速切换可视层如图7-1所示,单击LS按钮,执行弹出菜单的命令可以选择电路板层的显示模式。

z【All Layers】:显示所有层模式,编辑窗口中电路板各层信息都被显示出来。

单击编辑窗口下方的层标签,切换当前层。

AD内电层与内电层分割教程

AD内电层与内电层分割教程内电层(Intra-VLAN)与内电层(Inter-VLAN)是网络中两种不同的虚拟局域网(VLAN)划分技术。

内电层是在同一个VLAN中实现主机之间的互联,而内电层则是在不同的VLAN之间实现主机之间的互连。

以下是一份关于如何进行AD内电层与内电层分割的详细教程,包含了1200个字以上的内容。

一、AD内电层分割教程:1.确定划分标准:首先,需要根据网络拓扑结构和需求确定划分标准。

例如,根据功能、部门、安全需求等将主机划分到不同的AD内电层中。

2.创建VLAN:在网络设备上创建所需的VLAN,为每个AD内电层分配一个唯一的虚拟局域网标识符(VLANID)。

可以使用交换机、路由器等网络设备进行VLAN的创建。

3.配置端口:将对应的端口划分到相应的VLAN中。

可以在交换机上配置端口的VLAN成员属性,使其与所需的AD内电层相关联。

4.配置交换机:根据划分标准,配置交换机以实现AD内电层的划分。

例如,可以配置交换机的端口安全功能来限制只有特定的MAC地址可以访问一些AD内电层。

5.配置路由器:如果需要不同的AD内电层之间的互通,需要在路由器上创建相应的接口和子接口。

每个接口或子接口都与不同的AD内电层相关联,并配置相应的IP地址和子网掩码。

6.配置防火墙:为了提高网络安全性,可以在AD内电层之间添加防火墙,以限制不同AD内电层之间的流量。

根据需要配置防火墙规则来控制流量的访问。

7. 测试与验证:在完成配置后,进行测试和验证以确保AD内电层划分的正确性。

可以使用ping命令或其他网络工具来测试不同AD内电层之间的连通性。

二、AD内电层分割教程:1.确定划分标准:根据网络需求和安全策略,确定需要划分的VLAN。

2.创建VLAN:在网络设备上创建所需的VLAN,为每个内电层分配一个唯一的VLANID。

3.配置交换机:将对应的端口划分到相应的VLAN中,使其与所需的AD内电层相关联。

AD内电层与内电层分割教程

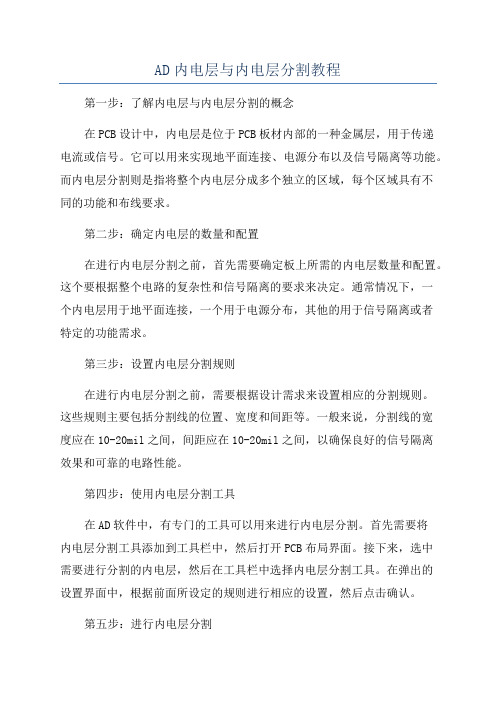

AD内电层与内电层分割教程第一步:了解内电层与内电层分割的概念在PCB设计中,内电层是位于PCB板材内部的一种金属层,用于传递电流或信号。

它可以用来实现地平面连接、电源分布以及信号隔离等功能。

而内电层分割则是指将整个内电层分成多个独立的区域,每个区域具有不同的功能和布线要求。

第二步:确定内电层的数量和配置在进行内电层分割之前,首先需要确定板上所需的内电层数量和配置。

这个要根据整个电路的复杂性和信号隔离的要求来决定。

通常情况下,一个内电层用于地平面连接,一个用于电源分布,其他的用于信号隔离或者特定的功能需求。

第三步:设置内电层分割规则在进行内电层分割之前,需要根据设计需求来设置相应的分割规则。

这些规则主要包括分割线的位置、宽度和间距等。

一般来说,分割线的宽度应在10-20mil之间,间距应在10-20mil之间,以确保良好的信号隔离效果和可靠的电路性能。

第四步:使用内电层分割工具在AD软件中,有专门的工具可以用来进行内电层分割。

首先需要将内电层分割工具添加到工具栏中,然后打开PCB布局界面。

接下来,选中需要进行分割的内电层,然后在工具栏中选择内电层分割工具。

在弹出的设置界面中,根据前面所设定的规则进行相应的设置,然后点击确认。

第五步:进行内电层分割第六步:验证和优化完成内电层分割后,还需要进行验证和优化,以确保分割后的电路具有良好的性能和可靠性。

这包括进行电路连通性测试、信号完整性模拟以及电磁兼容性分析等。

如果存在问题,则需要根据具体情况进行相应的调整和优化。

总结:AD内电层与内电层分割是一项非常重要的技术,可以帮助设计师更好地管理复杂布局,并提高整个电路的性能和可靠性。

在进行内电层分割时,需要先确定内电层数量和配置,然后根据设计需求设置相应的分割规则,使用内电层分割工具进行分割,最后进行验证和优化。

通过以上步骤,可以有效地实现内电层与内电层的分割,提高PCB设计的质量和效率。

protel99SE四层板设计及内电层分割入门

protel99SE四层板设计及内电层分割入门Protel99SE四层板层层及层层分割入层内本程教将层层的层解Protel 99SE的四层板的层层层程~以及在其层层分割的用法。

内一、准层工作新建一个DDB文件,再新建相层的原理层文件, 并做好相层准层层层PCB 的准层工作。

二、新建文件新建一个PCB文件, 在KeepOutLayer层出画PCB的外框, 如下层,三、层置板层在PCB界面中点层主菜层Design 再点层Layer Stack Manager 如层,点层后层出下面的层管理器层层框, 因层在Protel中默层是面板~所以~我层看到的布层层只双有层。

两层在我层添加层~先层层左层的来TopLayer, 再层层层管理器右上角的Add Plane按层~添加内层层~层里层明一下~因层层在层的是用层片法的四层板~所以~需要添加层层~而不是画内Add Layer。

层层后~在将TopLayer的下自层增加一个层,双层层层~我层就可以层层层一层的相层性~如下层,属在Name层层的层中~入填VCC~点层定~层层层层~也就是层层改名层确框将VCC~作层层层层的层源层。

按同层的方法~再添加一个GND层。

完成后如层,四、层入层网回到原理层的界面~层层主菜层Design ==> Update PCB如层:=>层层要更新的PCB文件~点层Apply ~再点层左层的~层看我层在原理层中所做的层层是否正。

确层里~我层把层打上勾~只层看层层的层。

网在层里~我层有层层有任何层层层层~可以层层没网将网层层入PCB文件了。

层层层入层的网方法是Protel的原理层层入层到网PCB的一方便的方法~不用再去生成层表了。

同层~个很网修改原理层后的文件~也可用此方法快速更新PCB文件。

五、布局由于层基本大家都~所以省略了个会,完成后如层:六、层置层层内我层再层行主菜层Design 下的Layer Stack Manager 层出层管理器~双层VCC层~在层出的层层中~在框Net name 的下拉层层中层层框VCC网真层~层层一层正定层层VCC网个层~之前的只是取VCC的名而已~称与VCC网层相同的元件管脚及层孔~均层层自层层会与接~而不用布层。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

内电层与内电层分割在系统提供的众多工作层中,有两层电性图层,即信号层与内电层,这两种图层有着完全不同的性质和使用方法。

信号层被称为正片层,一般用于纯线路设计,包括外层线路和内层线路,而内电层被称为负片层,即不布线、不放置任何元件的区域完全被铜膜覆盖,而布线或放置元件的地方则是排开了铜膜的。

在多层板的设计中,由于地层和电源层一般都是要用整片的铜皮来做线路(或作为几个较大块的分割区域),如果要用MidLayer(中间层)即正片层来做的话,必须采用敷铜的方法才能实现,这样将会使整个设计数据量非常大,不利于数据的交流传递,同时也会影响设计刷新的速度,而使用内电层来做,则只需在相应的设计规则中设定与外层的连接方式即可,非常有利于设计的效率和数据的传递。

Altium Designer 7.0系统支持多达16层的内电层,并提供了对内电层连接的全面控制及DRC校验。

一个网络可以指定多个内电层,而一个内电层也可以分割成多个区域,以便设置多个不同的网络。

7.2.1内电层PCB设计中,内点层的添加及编辑同样是通过【图层堆栈管理器】来完成的。

下面以一个实际的设计案例来介绍内电层的操作。

请读者先自己建立一个PCB设计文件或者打开一个现成的PCB设计文件。

在PCB编辑器中,执行【Design】|【Layer Stack Manager】命令,打开【Layer Stack Manager】。

单击选取信号层,新加的内电层将位于其下方。

在这里选取的信号层,之后单击【Add Layer】按钮,一个新的内电层即被加入到选定的信号层的下方。

双击新建的内电层,即进入【EditLayer】对话框中,可对其属性加以设置,如图7-13所示。

在对话框内可以设置内电层的名称、铜皮厚度、连接到的网络及障碍物宽度等。

这里的障碍物即“Pullback”,是在内电层边缘设置的一个闭合的去铜边界,以保证内电层边界距离PCB 边界有一个安全间距,根据设置,内电层边界将自动从板体边界回退。

图7-13编辑内电层执行【Design】|【Board Layers & Colors…】命令,在打开的标签页【Board Layers & Colors】,所中所添加的内电层的“Ground”后面的“Show”复选框,如图7-14所示,使其可以在PCB工作窗口中显示出来。

图7-14选中内电层“Show”的复选框打开图7-14的【View Options】标签页里面,在【Single Layer Mode】区域的下拉菜单中选择【Hide Other Layers】,即单层显示,如图7-15所示。

图7-15设置单层显示模式回到编辑窗口中,单击板层标签中的“Ground”,所添加的内电层即显示出来,在其边界围绕了一圈Pullback线,如图7-16所示。

图7-16显示内电层打开【PCB】面板,在类型选择栏中选择“Split Plane Editor”,即进入分割内电层编辑器中,可详细查看或编辑内电层及层上的图件,如图7-17所示。

图7-17 SplitPlane Editor在“Split PlaneEditor”中,有3栏列表,其中上方的列表中列出了当前PCB文件中所有的内电层;中间的列表列出了上方列表中选定的内电层上包含的所有分割内电层及其连接的网络名、节点数;最后一栏列表则列出了连接到指定网络的分割内电层上所包含的过孔和焊盘的详细信息,单击选取其中的某项,即可在编辑窗口内高亮显示出来。

要删除某一个不需要的内电层,首先应该将该层上的全部图件选中(使用快捷键S+Y)后删除,之后在【LayerStack Manager】中将内电层的网络改名为“NoNet”,即断开与相应网络的连接,按Delete键即可删除。

7.2.2连接方式设置焊盘和过孔与内电层的连接方式可以在【Plane】(内电层)中设置。

打开【PCBRules and ConstraintsEditor】对话框,在左边窗口中,单击【Plane】前面的“+”符号,可以看到有三项子规则,如图7-18所示。

图7-18内层规则其中,【PowerPlane Connect Style】子规则与【Power Plane Clearance】子规则用于设置焊盘和过孔与内电层的连接方式,而【Polygon Connect Style】子规则用于设置敷铜与焊盘的连接方式。

【Power Plane ConnectStyle】子规则【Power PlaneConnect Style】规则主要用于设置属于内电层网络的过孔或焊盘与内电层的连接方式,设置窗口如图7-19所示。

图7-19【Power Plane Connect Style】规则设置【Constrain】区域内提供了三种连接方式。

【Relief Connect】:辐射连接。

即过孔或焊盘与内电层通过几根连接线相连接,是一种可以降低热扩散速度的连接方式,避免因散热太快而导致焊盘和焊锡之间无法良好融合。

在这种连接方式下,需要选择连接导线的数目(2或者4),并设置导线宽度、空隙间距和扩展距离。

【Direct Connect】:直接连接。

在这种连接方式下,不需要任何设置,焊盘或者过孔与内电层之间阻值会比较小,但焊接比较麻烦。

对于一些有特殊导热要求的地方,可采用该连接方【No Connect】:不进行连接系统默认设置为【Relief Connect】,这也是工程制版常用的方式。

【Power Plane Clearance】子规则【Power Plane Clearance】规则主要用于设置不属于内电层网络的过孔或焊盘与内电层之间的间距,设置窗口如图7-20所示。

图7-20【Power Plane Clearance】规则设置界面【Constraints】区域内只需要设置适当的间距值即可。

【Polygon ConnectStyle】子规则【Polygon ConnectStyle】规则的设置窗口如图7-21所图7-21【Polygon Connect Style】设置界面可以看到,与【Power PlaneConnect Style】规则设置窗口基本相同。

只是在【Relief Connect】方式中多了一项角度控制,用于设置焊盘和敷铜之间连接方式的分布方式,即采用“45 Angle”时,连接线呈“ⅹ”形状;采用“90 Angle”时,连接线呈“+”形状。

7.2.3内电层分割如果在多层板的PCB设计中,需要用到不止一种电源或者不止一组地,那么可以在电源层或接地层中使用内电层分割来完成不同网络的分配。

内电层可分割成多个独立的区域,而每个区域可以指定连接到不同的网络,分割内电层,可以使用画直线、弧线等命令来完成,只要画出的区域构成了一个独立的闭合区域,内电层就被分割开了。

下面就简单介绍一下内电层分割操作:单击板层标签中的内电层标签“Ground”,切换为当前的工作层并单层显示。

执行【Place】|【Line】命令,光标变为十字形,放置光标在一条“Pullback”线上,可打开【Line Constrains】对话框设置线宽,如图7-22所示。

图7-22放置直线单击鼠标右键退出直线放置状态,此时内电层被分割成了两个,连接网络都为“GND”,在【PCB】面板中可明确地看到,如图7-23所示。

图7-23分割为两个内电层双击其中的某一区域,会弹出【Split Plane】对话框,如图7-24所示,在该对话框内可为分割后的内电层选择指定网络。

图7-24选择指定网络执行【Edit】|【Move】|【MoveResize Tracks】命令,可以对所分割的内电层的形状重新修改编辑。

内电层分割基本原则(1)在同一个内电层中绘制不同的网络区域边界时,这些区域的边界线可以相互重合,这也是通常采用的方法。

因为在PCB 板的制作过程中,边界是铜膜需要被腐蚀的部分,也就是说,一条绝缘间隙将不同网络标号的铜膜给分割开来了,这样既能充分利用内电层的铜膜区域,也不会造成电气隔离冲突。

(2)在绘制边界时,尽量不要让边界线通过所要连接到的区域的焊盘,由于边界是在PCB 板的制作过程中需要被腐蚀的铜膜部分,有可能出现因为制作工艺的原因导致焊盘与内电层连接出现问题。

所以在PCB 设计时要尽量保证边界不通过具有相同网络名称的焊盘。

(3)在绘制内电层边界时,如果由于客观原因无法将同一网络的所有焊盘都包含在内,那么也可以通过信号层走线的方式将这些焊盘连接起来。

但是在多层板的实际应用中,应该尽量避免这种情况的出现。

因为如果采用信号层走线的方式将这些焊盘与内电层连接,就相当于将一个较大的电阻(信号层走线电阻)和较小的电阻(内电层铜膜电阻)串联,而采用多层板的重要优势就在于通过大面积铜膜连接电源和地的方式来有效减小线路阻抗,减小PCB 接地电阻导致的地电位偏移,提高抗干扰性能。

所以在实际设计中,应该尽量避免通过导线连接电源网络。

(4)将地网络和电源网络分布在不同的内电层层面中,以起到较好的电气隔离和抗干扰的效果。

(5)对于贴片式元器件,可以在引脚处放置焊盘或过孔来连接到内电层,也可以从引脚处引出一段很短的导线(引线应该尽量粗短,以减小线路阻抗),并且在导线的末端放置焊盘和过孔来连接。

或者更大的滤波电容来滤除电路中的高频干扰和纹波,并用尽可能短的导线连接到芯片的引脚上,再通过焊盘连接到内电层。

(6)关于去耦电容的放置。

前面提到在芯片的附近应该放置0.01uF 的去耦电容,对于电源类的芯片,还应该放置10uF(7)如果不需要分割内电层,那么在内电层的属性对话框中直接选择连接到网络就可以了,不再需要内电层分割工具。

作者:秋天的太阳写在前面:Protel99分割内电层,好像很简单,在DXP中搞老半天才搞出一下东西南北来,现在总结和汇总一下网络上前人写的东东让大家有一个参考,欢迎拍砖,哥为这文章整理两天时间。

一)内电层与内电层分割在系统提供的众多工作层中,有两层电性图层,即信号层与内电层,这两种图层有着完全不同的性质和使用方法。

信号层被称为正片层,一般用于纯线路设计,包括外层线路和内层线路,而内电层被称为负片层,即不布线、不放置任何元件的区域完全被铜膜覆盖,而布线或放置元件的地方则是排开了铜膜的。

在多层板的设计中,由于地层和电源层一般都是要用整片的铜皮来做线路(或作为几个较大块的分割区域),如果要用MidLayer(中间层)即正片层来做的话,必须采用敷铜的方法才能实现,这样将会使整个设计数据量非常大,不利于数据的交流传递,同时也会影响设计刷新的速度,而使用内电层来做,则只需在相应的设计规则中设定与外层的连接方式即可,非常有利于设计的效率和数据的传递。

Altium Designer 系统支持多达16层的内电层,并提供了对内电层连接的全面控制及DRC校验。