基于bandgap版图设计毕业论文

版图设计论文15篇

版图设计论文15篇版图设计论文摘要:集成电路版图设计教学应面向企业,按照企业对设计工程师的要求来安排教学,做到教学与实践的紧密结合。

从教学开始就向学生灌输IC行业知识,定位准确,学生明确自己应该掌握哪些相关知识。

从集成电路数字版图、模拟版图和逆向设计版图这三个方面就如何开展教学可以满足企业对版图工程师的要求展开探讨,安排教学有针对性。

在教学方法与内容上做了分析探讨,力求让学生在毕业后可以顺利进入IC行业做出努力。

关键词版图设计设计论文设计版图设计论文:一种基于厚膜工艺的电路版图设计摘要:在电子线路版图设计中,通常采用印刷线路板技术。

如果结合厚膜工艺技术,可以实现元器件数目繁多,电路连接复杂,且安装空间狭小的电路版图设计。

通过对3种不同电路版图设计方案的理论分析,确定了惟一能满足要求的设计方案。

基于外形尺寸的要求,综合考虑电路的性能和元件的封装形式,通过合理的电路分割和布局设计,验证了设计方案的合理性和可实现性。

体现了厚膜工艺技术在电路版图设计中强大的优越性,使一个按常规的方法无法实现的电路版图设计问题迎刃而解。

关键词:电路版图设计;电路分割设计;厚膜混合集成电路;厚膜工艺0 引言随着电子技术的飞速发展,对电子设备、系统的组装密度的要求越来越高,对电路功能的集成度、可靠性等都提出了更高的要求。

电子产品不断地小型化、轻量化、多功能化。

除了集成电路芯片的集成度越来越高外,电路结构合理的版图设计在体积小型化方面也起着举足轻重的作用。

1 厚膜工艺技术简述厚膜工艺技术是将导电带和电阻通过丝网漏印、烧结到陶瓷基板上的一种工艺技术[1]。

厚膜混合集成电路是在厚膜工艺技术的基础上,将电阻通过激光精调后,再将贴片元器件或裸芯片装配到陶瓷基板上的混合集成电路[2]。

厚膜混合集成电路基本工艺流程图见图1。

图1 厚膜工艺流程图厚膜工艺与印制板工艺比较见表1。

2 电路版图设计2.1 设计要求将电路原理图(图2,图3)平面化设计在直径为34 mm的PCB板上(对电路进行分析后无需考虑相互干扰),外形尺寸图见图4。

版图设计毕业论文

版图设计毕业论文近年来,随着科技和经济的不断发展,版图设计在各个领域都有着广泛的应用,尤其是在城市规划和建筑设计中有着非常重要的作用。

本论文旨在探讨版图设计在城市规划中的应用,并通过实例分析,探索版图设计在城市规划中的实践价值。

一、版图设计的基本概念和意义版图设计是指根据规划目标和要求,在地理信息系统的支持下,通过对空间数据进行搜集、整理、分析和加工等一系列工作,实现对空间关系的综合研究与表达,从而形成新的地图和空间布局方案的技术和方法。

作为城市规划中的一项关键技术,版图设计可以为城市的长远发展提供支持和保障,同时也可以为政府制定空间规划和部门决策提供科学依据。

版图设计主要包含空间数据处理、空间分析和方案设计三个主要阶段。

空间数据处理是指通过多种手段搜集和整理地理信息,形成规范化、统一标准的数据表,并把数据转换成适合软件处理的格式。

空间分析是指基于地理信息分析的基础上,进行空间关系、特性和规律的研究,主要包括时空关系、空间密度和土地利用等。

方案设计是指结合政策、规划要求、社会需求以及市场需求,针对不同的目标和要求,提出合理的空间布局和设计方案。

版图设计在城市规划中的作用是不可替代的。

首先,版图设计可以为城市规划提供重要数据和信息支持,为市政部门、规划部门制定政策和规划提供空间数据分析、研究和预测。

其次,版图设计可以为城市规划提供合理化、系统化的规划方案,优化城市的空间结构和布局,提高城市的空间利用率和效益。

最后,版图设计可以为公众提供信息和参与平台,加强公众对城市规划的监督和参与,有助于提高城市规划的透明度和公正性。

二、版图设计在城市规划中的实践价值版图设计在城市规划中有着广泛的应用和实践价值,主要包括以下方面:1.优化城市空间结构和布局城市规划的基本目标是优化城市的空间结构和布局,提高城市的空间利用率和效益。

版图设计可以通过空间数据的分析和加工,提出合理的空间规划和布局方案,从而达到优化城市空间结构和布局的目的。

bandgap电路设计报告

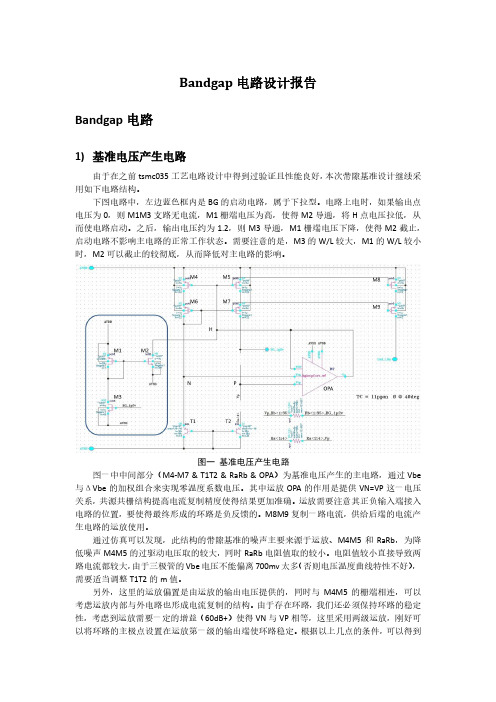

Bandgap电路设计报告Bandgap电路1)基准电压产生电路由于在之前tsmc035工艺电路设计中得到过验证且性能良好,本次带隙基准设计继续采用如下电路结构。

下图电路中,左边蓝色框内是BG的启动电路,属于下拉型。

电路上电时,如果输出点电压为0,则M1M3支路无电流,M1栅端电压为高,使得M2导通,将H点电压拉低,从而使电路启动。

之后,输出电压约为1.2,则M3导通,M1栅端电压下降,使得M2截止,启动电路不影响主电路的正常工作状态。

需要注意的是,M3的W/L较大,M1的W/L较小时,M2可以截止的较彻底,从而降低对主电路的影响。

图一基准电压产生电路图一中中间部分(M4-M7 & T1T2 & RaRb & OPA)为基准电压产生的主电路,通过Vbe 与ΔVbe的加权组合来实现零温度系数电压。

其中运放OPA的作用是提供VN=VP这一电压关系,共源共栅结构提高电流复制精度使得结果更加准确。

运放需要注意其正负输入端接入电路的位置,要使得最终形成的环路是负反馈的。

M8M9复制一路电流,供给后端的电流产生电路的运放使用。

通过仿真可以发现,此结构的带隙基准的噪声主要来源于运放、M4M5和RaRb,为降低噪声M4M5的过驱动电压取的较大,同时RaRb电阻值取的较小。

电阻值较小直接导致两路电流都较大,由于三极管的Vbe电压不能偏离700mv太多(否则电压温度曲线特性不好),需要适当调整T1T2的m值。

另外,这里的运放偏置是由运放的输出电压提供的,同时与M4M5的栅端相连,可以考虑运放内部与外电路也形成电流复制的结构。

由于存在环路,我们还必须保持环路的稳定性,考虑到运放需要一定的增益(60dB+)使得VN与VP相等,这里采用两级运放,刚好可以将环路的主极点设置在运放第一级的输出端使环路稳定。

根据以上几点的条件,可以得到运放的结构如下图二所示。

其中的两个P管电流源可以看成是与图一中M4和M5成电流复制结构。

bandgap设计及仿真介绍

5.温度补偿结构

R3

R2

I1

I2

V R1

R

1

Q2

V REF

Q1

此结构是在一个负反馈运 算放大器的两个输入端各 接一个稳压电路。两路稳 压电路并联。它们并联的 总电压作为我们所要的参 考电压,连接到运放的输 出端输出。电源电压包含 在运放里。下面分析一下 它的工作原理。

R

3

R

2

I I

2

1

V

R 1

R

> 0

6.关于K的两点讨论

R3

R2

I1

I2

VR1

• 1.K必须独立于温度(用电阻之 比) • 2.K必须独立于电源电压

VREF = VEB 2 + KT

VREF

R k R A K = 2 ln 2 E 1 R q R A 1 3 E 2 > 0

1

V

Q

R E F

2

Q

1

V REF = V BE 2 + V R 3

(VR3即是我们要构造的KT项)

VR 3

R2 = I 2 R3 = I 1 R2 = VR1 ∗ R1

VR1 = VEB 2 − VEB1

kT J 2 kT J 1 k I 2 AE1 = ln J − q ln J = q ln I A ∗ T q I

∆V

V

这种结构的稳压性能虽好,但是它的温度特 性仍然没有得到改善。VBE具有负的温度系数,在 室温时大约是-2.2mV/℃。我们可以通过补偿的 方法来改善参考电压源的温度特性。我们期望构 造出具有正温度系数的KT项,其中K为正常数, T T为热力学温标,使

bandgap设计教程

1 : 1V REF∂V 考虑版图,N可取8R3=R0, R4=R2, M3=M2,R3R0R4R2M3M2运放的失调必须控制好具体设计请参考基准电压与电流201R R V V V BEBE REF ⋅Δ+=Ref:sansen 0ln 21R R N q kT V V BE REF ⋅⋅+=−~m1156mVchapter 16()T C T V V g BE +=λ00For I DS T ln qR N kT I BG⋅=Is PTAT0qVBG 通常在1.2左右结合电阻的温度系数,IBG 在高温与低温下其值变化可能较大,若用它直接去偏置其他电路,这一点须特别注意IBG~T 注意到:IBG T 时,gm constant二次补偿:VBG 的温度特性包含抛物线型非线性项,设计中令顶点位于常温附近,更高精度要求可采用二次补偿电路(例sansen ppt 1626)简单的电阻补偿:ln NkT I BG ⋅=若采用负温度系数的电阻,有可能降低非线性,实现更小的温度系数qR 例:设置不同的电阻温度系数,并在每个系数下调整电阻比例至最佳输出状态Tr1 = 1m Tr1 = ‐2m Tr1 = ‐3m温度系数——不同的Corner下,会有不同的温度系数,希望通过调整电阻比例,将温度系数调整至最佳状态调整至最佳状态;输出电压值:由于失配,或工艺起伏,输出电压会在一个范围内变化,系统通过调整电阻比例,将变化的范围控制得小一些。

电路设计:将电阻分段,并加开关控制;校准策略:批校准;每个校准校准策略批校准每个校准启动与稳定性启动:这个电路有两个稳定工作点,其中一个是两个支正反馈负反馈启动电路回路回路静态损耗:VDD/RESOpa RC VBG MOSCAPVREF ‐Vos +抑制/噪声采1/f噪声还可采用chopping技术V/I转换V/V转换R1=R2VBG的大小可通过整, 不影响温度系数IBG=VBG/R3,由IBG温漂较小,主要取决于电阻温度系数最低电源电压可正反馈环负反馈环MOSResistor正常输出下VBG>VTn, 否则应采用其他形式的启动电路MOSCAPPMOS采用folded结构采用PMOS输入差分对, 减少1/f噪声, 并适合于低输入共模的情况VGS‐VT小, 其他电流镜VGS‐VT大, 晶体管的L要大一些, 减输入差分对GS GS要大些少失调, 1/f噪声, 以及沟道调制效应自便置设计启动时,vb1若为高,则无法启动,故需增加拉低vb1低压设计将R1, R2由两个电阻串联,取中间点接运放输入,可降低输共模步降低压压入共模,进一步降低电压电压要求运放采用PMOS输入的folded‐cascode结构或symmetrical结构可进一步采用电路设计技术来降低运放对电源电压的要求‐BandgapSub1V ExampleRef: Ka Nang Leung, JSSC2002采用symmetrical结构和电平移位(level shifting)来降低输入共模要求ip inPhase 1in ipPhase 2。

毕设正文

前言过去人们用的是反向击穿齐纳二极管来获得参考的基准电压源,但是对于电源电压在5V以下的电路设计并不合适。

1971年,RobertWidlar 提出了一种带隙参考电压源技术。

带隙基准源电路由于具有低温度系数,低电源电压以及可以与标准CMOS工艺兼容等优点获得了广泛的研究和应用。

随着IC集成电路设计技术的发展,基准电压源已成为大规模、超大规模集成电路和几乎所有数字模拟系统中不可缺少的基本电路模块。

基准电源不仅应用于A/D,D/A模块中,而且应用于锁相环,分频器和其它需要基准源的模块。

其应用范围非常广泛,基准源的稳定性和精确度直接影响整个锁相环中分频器的设计,即影响输出时钟的准确性和稳定性。

现今模拟市场CMOS占主要地位的动力是尺寸的不断缩小提高了MOSFET器件的速度。

CMOS技术不断向先进工艺发展,从微米到深亚微米,目前已发展到纳米工艺技术阶段。

晶成电路上集成的晶体管数量每18个月将增加一倍,性能将提高一倍,而价格却不相应的增加,这就是所谓的摩尔定律。

据权威机构预测到2016年,器件的最小特征尺寸应在13nm[1]。

纳米工艺所造芯片上管子密度大大增加,极大改善了芯片性能,但成本的提高使得一次性流片成功成为设计者的基本要求。

在0.18um及以上的工艺中,电路设计规则简单,但是先进工艺,电路的设计规则便得复杂,在65nm和28nm工艺节点下情形便得更加复杂。

随着尺寸的缩小,晶体管表现出与微米尺度工艺下不同的电学特性。

纳米工艺的探索还处在基础研究阶段。

本设计采用的是全定制设计。

全定制设计的特点是针对每个元件进行电路参数和版图参数的优化,它采用自由的版图设计规则进行设计,以使每个元件及内连接安排的紧凑,合适[2]。

本文所设计的28nm工艺的带隙基准源还是处在仿真的阶段,如果有流片后的测试结果,该文章将更加具有参考价值和研究价值。

一 带隙基准源的电路设计(一)基本原理这里是本设计根据双极型晶体管的基极-发射极即PN 结二极管的Vbe 的温度系数本身与温度有关的特性,将两个具有相反温度系数的量加以适当加权结果就会显示零温度系数。

gaibande 版图设计讲稿 河北科技大学 安胜彪

CMOS放大器的版图

特殊尺寸器件的版图设计

特殊尺寸器件是指: ① 大尺寸——MOS管宽长比(W/L)很大; ② 小尺寸——W/L<1(倒比管)。

大尺寸器件

1. CMOS电路的缓冲输出 缓冲输出是指在内部电路输出端串联二级反相器,改善输出驱动能力。各级器件 尺寸(W/L): I0为小尺寸,I1为中等尺寸,I2为大尺寸。I2的尺寸根据输出电流的 大小和输出波形参数的要求进行设计。

(a)金属导线跨过两个扩散区

(b)场反型形成场区寄生MOS管

寄生MOS管示意图

2)场开启电压 影响场开启电压的因素: ① 场氧化层厚度——场氧化层越厚,场开启电压就越高。 ② 衬底掺杂浓度——衬底浓度越高,场开启电压也越高。 要求场开启电压足够高,至少应大于电路的电源电压,使每个MOS管之间具有 良好的隔离特性 版图设计中增加沟道隔离环提高场开启电压。

5) P阱硅栅CMOS反相器输出级与压焊块(PAD)的连接 特点:① P管和N管都由多管并联而成。 ② P管和N管放在两个隔离环内。 ③ 考虑到电子迁移率比空穴约大2.5倍,所以P管的尺寸比N管大,使反相器 的输出波形对称。

(a) 无铝层的版图

(b) 完整的版图

4. CMOS放大器

电路图 五个器件的布局

图8.2 由注入倾斜造成栅阴影区

考虑栅阴影后,图(a)的结构更好一些。

栅阴影效应 (a)两个MOS管的栅在同一直线上; (b)两个栅相互平行

3) 增加虚拟器件提高对称性

注意器件周围保持相同的环境。

(a)M2管旁边的的金属线引起不对称;(b)在M1管相对称位置安排同样一条线来消除不对称性

4) 共中心(四方交叉)

(a)合并前

(b)合并后

(c) Vdd和Vss采用叉指结构

基于bandgap版图设计毕业论文

摘要近年来随着IC设计要求的不断开展,集成电路幅员设计是实现集成电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是否正确,而且也会极大程度地影响集成电路的性能、本钱。

而集成电路中的bandgap可以在温度和电压不稳定的环境中保持稳定的参考电压,被广泛运用于比拟器、A/D转换器等模拟电路及数模混合信号集成电路中,其性能直接影响整个系统的精度和性能。

因此,bandgap幅员设计的研究非常有意义。

本文基于Cadence 幅员设计软件平台,采用XFAB0.6µm CMOS 工艺设计。

设计的幅员元件包括PMOS、NMOS、PNP三极管、电阻、电容。

其中对差分放大器、电流镜、电阻等重要元件采用了匹配和对称的设计方法,考虑电气特性的幅员设计技术;为防止闩锁效应,本设计还运用了保护环保护整个电路,提高了bandgap 电路的可靠性。

本设计对最终设计出的幅员使用calibre验证工具进展LVS和DRC验证,并顺利通过验证。

关键字:幅员;带隙基准电压源;Cadence;匹配;验证ABSTRACTIn recent years, along with IC design request of continuously development, IC layout are essential to achieve the design of integrated circuit manufacturing sectors, it is not only related to the IC's functions are correct, but also great extent affect IC performance and cost.But bandgap reference voltage of integrated circuit can keep stability in the unsteady environment of the temperature and the electric voltage of reference electric voltage, used extensively in comparison machine, A/D conversion machine etc. analog electric circuit and some mixture signal integrated circuit. Its function is directly influence the whole accuracy and function of system. Therefore, the research which take the layout design of the bandgap reference voltage is very meaningful.This text ,according to the design software of the Cadence about layout design, adopts XFAB0.6µm CMOS of design rule.The component of layout design include PMOS, NMOS, PNP, electric resistance, electric capacity. To the OP、current and resistance which are importance components adopt layout design technique of consideration electricity characteristic; To reduce latch-up, this design still uses guard ring to protect the whole electric circuit, improving the credibility of bandgap reference voltage.In the end, this design carried LVS and DRC of verification to the landscape used calibre verification tool that finally designs and passed a verification smoothly.Key Words: Layout; Bandgap reference voltage; Cadence; matching; Symmetry目录第1章引言11.1选题背景及意义11.2国内微电子开展状况1第2章Bandgap简介32.1 什么是Bandgap32.2 Bandgap的原理32.3 Bandgap的应用6第3章 Virtuoso工具及幅员绘制7 3.1 Cadence 软件介绍73.2 Virtuoso工具的使用8建立幅员库8层选择窗的设置11幅员编辑窗的设置13的常用快捷键15第4章Bandgap的幅员设计18 4.1幅员设计中的相关主题18器件的匹配规那么18匹配管子的幅员设计22电阻幅员设计25倒比管幅员设计26双极型晶体管幅员设计27电容幅员设计284.2全局规划〔floor plan〕294.2.1模块摆放294.3整体布线30第5章Bandgap电路幅员验证32 5.1幅员验证的概述325.2幅员的DRC验证335.3 幅员的LVS验证37完毕语42参考文献43致谢44附录46外文资料原文50第1章引言1.1选题背景及意义随着IC工艺的开展,在模拟电路和数模混合电路中,片内集成的基准源电路已被普遍采用,它是集成电路中的一个重要模块。

BandGap设计心得

Bandgap也算模拟电路里的重要角色了,差不多可以说有模拟电路的地方就有Bandgap。

从原理上说,目前用的bandgap都离不开两个东西,一个是deltaVbe,一个是Vbe。

前者产生的是一个kt/q形式电压,后者产生的是一个随温度准线性的电压。

而bandgap的输出就则由这两个电压线性组合决定。

至于为什么有温度系数,从最大的因素上说,就来自于Vbe,VBe只是随温度准线性,而另一个电压则是线性度很好的。

原理上知道了,在实际中怎么设计?Vbe好说,就是给二极管(或者说三极管)一个电流。

deltaVbe则离不开一定形式的反馈。

从大的角度讲,一种是用opa设计的,一种是用镜像电流镜设计的,从反馈的角度看,这两种电路是完全不同的。

用opa设计的是一个负反馈,更严格的说,是有两个反馈支路,一正一负,而一定要负反馈强于正反馈,保证整个系统是负反馈。

另一种上面一个电流镜,下面一个电流镜,只是下面电流镜加了diode做degeneration。

这个从系统的角度讲是正反馈,正反馈如果用在电路里,就一定要保证环路增益小于1才能稳定.由于稳定性的要求,所以这两种电路都不能随便把左右互换。

至于仿真稳定性,对于用opa设计的负反馈电路,我的观点很明确,必须把正负反馈两个支路合起来仿真稳定性,否则仿真结果没有任何意义(如果有人争辩说,不是已经理论分析得出了正反馈弱于负反馈吗?那我就要反问仿真的意义是什么?)。

对于正反馈,我不是很清楚稳定的判据,所以一般都是看看增益是否会超过1.在实际的应用中,我很少碰到有很强调温度系数的设计,这似乎和学校里的要求刚好相反。

这也许是因为我设计的电路中ADC和DAC很多都不是测量用的。

偶尔碰到那么几个,其指标也在10bit左右,看了看别人产品的datasheet,也只要求30-60ppm。

与其强调温度系数,反倒不如强调随工艺变化造成的静态输出变化。

所以对于如何在工程上实现一个很好温度系数的bandgap我很感兴趣。

bandgap设计流程

bandgap设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!1. 确定设计目标明确 bandgap 的性能要求,如温度系数、输出电压精度、功耗等。

高精度电流偏置电路的设计

高精度电流偏置电路的设计蒋本福;杨骁【摘要】A high accuracy current bias circuit is presented in this paper, which can be used in RF wireless transceiver chip. This paper designs a practical application of the bandgap reference circuit, with consideration of the power, area and offset voltage. This paper adopts the bandgap reference circuit and a voltage to current converter structure to design a high power supply rejection ratio design (PSRR) of the reference current. Current mirror with auxiliary operational amplifier (gainboost) is to improve the output impedance, and to reduce the influence of modulation effect on the reference current, so as to improve the precision of output current reference.The reference current bias is simulated based on 0.35 μm technology standard CMOS process. The layout area is 0.18 mm2. Planning parameters extraction (PEX)simulation results show that the reference voltage is 1.203 5 V, temperature coefficient in the range of -55℃~+90℃ is 15.5 ppm/℃, the power supply rejection ratio in low frequenc y is 90 dB, when the outside resistor is from 1 kΩ~400 kΩ, the output reference current error range is 0.000 1μA.%提出了一款应用于 RF 无线收发芯片的高精度电流偏置电路。

bandgap设计教程.

1 : 1V REF∂V 考虑版图,N可取8R3=R0, R4=R2, M3=M2,R3R0R4R2M3M2运放的失调必须控制好具体设计请参考基准电压与电流201R R V V V BEBE REF ⋅Δ+=Ref:sansen 0ln 21R R N q kT V V BE REF ⋅⋅+=−~m1156mVchapter 16()T C T V V g BE +=λ00For I DS T ln qR N kT I BG⋅=Is PTAT0qVBG 通常在1.2左右结合电阻的温度系数,IBG 在高温与低温下其值变化可能较大,若用它直接去偏置其他电路,这一点须特别注意IBG~T 注意到:IBG T 时,gm constant二次补偿:VBG 的温度特性包含抛物线型非线性项,设计中令顶点位于常温附近,更高精度要求可采用二次补偿电路(例sansen ppt 1626)简单的电阻补偿:ln NkT I BG ⋅=若采用负温度系数的电阻,有可能降低非线性,实现更小的温度系数qR 例:设置不同的电阻温度系数,并在每个系数下调整电阻比例至最佳输出状态Tr1 = 1m Tr1 = ‐2m Tr1 = ‐3m温度系数——不同的Corner下,会有不同的温度系数,希望通过调整电阻比例,将温度系数调整至最佳状态调整至最佳状态;输出电压值:由于失配,或工艺起伏,输出电压会在一个范围内变化,系统通过调整电阻比例,将变化的范围控制得小一些。

电路设计:将电阻分段,并加开关控制;校准策略:批校准;每个校准校准策略批校准每个校准启动与稳定性启动:这个电路有两个稳定工作点,其中一个是两个支正反馈负反馈启动电路回路回路静态损耗:VDD/RESOpa RC VBG MOSCAPVREF ‐Vos +抑制/噪声采1/f噪声还可采用chopping技术V/I转换V/V转换R1=R2VBG的大小可通过整, 不影响温度系数IBG=VBG/R3,由IBG温漂较小,主要取决于电阻温度系数最低电源电压可正反馈环负反馈环MOSResistor正常输出下VBG>VTn, 否则应采用其他形式的启动电路MOSCAPPMOS采用folded结构采用PMOS输入差分对, 减少1/f噪声, 并适合于低输入共模的情况VGS‐VT小, 其他电流镜VGS‐VT大, 晶体管的L要大一些, 减输入差分对GS GS要大些少失调, 1/f噪声, 以及沟道调制效应自便置设计启动时,vb1若为高,则无法启动,故需增加拉低vb1低压设计将R1, R2由两个电阻串联,取中间点接运放输入,可降低输共模步降低压压入共模,进一步降低电压电压要求运放采用PMOS输入的folded‐cascode结构或symmetrical结构可进一步采用电路设计技术来降低运放对电源电压的要求‐BandgapSub1V ExampleRef: Ka Nang Leung, JSSC2002采用symmetrical结构和电平移位(level shifting)来降低输入共模要求ip inPhase 1in ipPhase 2。

(毕业论文)版图设计开发1组3

随着IC技术的不断发展,芯片的品质不仅要依靠前端设计的优劣,在某些情况下,同版图设计联系的更加紧密,尤其在an alog/mix-sig nal/RF circuit design中。

所谓版图,就是一组相互套合的图形,各层版图对应于不同的工艺步骤,每一层都用不同的图案来表示。

版图与所采用的制备工艺紧密相关,会根据性能要求以及工艺水平要求来设计光刻用的掩膜版图,实现IC设计的最终输出振荡器是一种用来产生高、中、低频信号的频率源,一般会使用在锁相环中,高精度振荡器在无线电广播,卫星通信、电视机、开关电源、收音机等电子设备中都要广泛用到。

关键词:振荡器、高精度、版图ABSTRACTWith the con ti nu ous developme nt of IC tech no logy, the quality of the chip must not only rely on the merits of fron t-e nd desig n, and in some cases, associated with thelayout more closely, particularly in the an alog / mix-sig nal / RF circuit desig n in. The territory of the so-called, is a set of mutually nested graphics, all levels of the map correspond to different process steps, each layer are expressed in different patterns. Used in the territory and is closely related to the preparati on process will be based on performa nee requireme nts and process requireme nts desig ned to mask layout used in lithography, IC desig n to achieve the final output. Oscillator is used to gen erate a high, medium and low-freque ncy sig nals in the freque ncy of the source, gen erally in use in phase-locked loop, high-precision oscillator in the radio broadcasting, satellite com muni catio ns, televisi on, switch ing power supplies, radios and other electro nic equipme nt are to be widely used.Key words: oscillator, accuracy, layout目录第一章引言 (1)1.1本课题的研究背景 (1)1.2研究本课题的价值及意义 (1)1.3 本课题的主要工作 (1)第二章设计工具、流程及规则简介 (3)2.1 Cadenee工具简介 (3)2.2设计流程简介 (8)2.3 标准单元设计技术 (11)2.4版图设计规则简介 (14)第三章版图设计 (16)3.1 基本制造工艺 (16)3.2分立器件设计 (18)3.3单元模块设计 (21)第四章版图验证 (30)4.1 设计规则检查(DRC) (30)4.2 电路与版图一致性验证(LVS ) (32)4.3 完成验证 (33)第五章版图总拼、优化 (34)第六章结论 (36)参考文献 (37)致谢 (38)外文资料原文 (39)外文资料译文 (46)第一章引言1.1 本课题的研究背景随着振荡器在电子工业、医疗、科学研究等方面的广泛应用。

布图设计结构、技术、功能简要说明

OSC01简要说明

本版图是石英晶体振荡器电路的版图设计。

本版图采用最新的CMOS 0.18um工艺制程,可以为SOC芯片内部作为基准电压源使用。

电路由inv、schmitt触发器、bandgap基准源、ldo和level shift 5个部分组成,如图1所示。

图1 电路框图

其核心部分inv的电路图,如图2所示:

电路的整体版图如图3所示:

本版图对于match要求非常高。

以下设计可达到良好的match。

Bandgap core中三极管的版图如图4.1所示。

图4.1 Bandgap core中三极管的结构设计Bandgap core中电阻的版图如图4.2所示。

图4.2 Bandgag core中电阻的结构设计

LDO中电阻的版图如图4.3所示。

图4.3 LDO中电阻的结构设计

为了减少电源噪声的干扰,模拟电源与数字电源分开,如图5所示。

图5 模拟、数字电源线分开。

画图板的设计与实现学士学位论文

北京邮电大学毕业设计(论文)任务书第1页第2页第3页画图板的设计与实现摘要本文的主要内容是记述同题课程设计中的一些关键技术和辅助文档。

本文的目标是设计一款基于Qt编程语言的简易画图板,使其具有涂鸦,绘制基本图形等功能。

本程序具有一定的实用意义和价值。

功能分装良好可以方便的根据需求进行扩充。

本文运用材料综述的方法,首先记述了编程环境的搭建,介绍了Qt的优点,Qt编码规范和Qt的双缓冲机制在绘图中的运用。

着重分析了Qt在软件开发中的编程机制,并根据应用特点进行了设计的构件与算法的需求分析。

其次在需求分析中给出是可行性分析,然后放入功能分析图和流程图帮助梳理设计思路。

最后在详细设计阶段完成编码,实现程序功能,得到一个功能健全的画图板应用程序。

在本文中将设计并实现画图板的一些基本功能,例如:新建,打开,保存,清空,放大,缩小,还原,基本图形绘制,转换画笔颜色等功能。

最后运行结果符合设计要求,方案可行。

经过测试后程序功能实现良好。

关键词嵌入式Linux QT;图形用户界面;电子画板;双缓冲机制The Realization of Drawing Board FunctionAbstractThe main content of this paper is described with the course in the design of so me key technologies and supporting documents.The goal of this article is to design a simple drawing board based on Qt programming language, make its have graffiti, dr aw up the basic graph, and other functions.This program has a certain practical signif icance and value.Function according to the requirements of good packaging can easily expanded.This article applies the method of material review, the construction of the first d escribes the programming environment, this paper introduces the advantages of Qt Qt code conventions and Qt double-buffering mechanism used in the drawing.Qt program ming in the software development mechanism is analyzed emphatically, and the desig n based on the application of artifacts and requirements analysis of the algorithm.Seco nd is feasibility analysis is given in the requirements analysis, and then into the com b function analysis diagram and flowchart to help design thinking.Program is realized by encoding the detailed design phase is complete, the function, get a functioning dr awing board application.Designed and implemented in this paper some basic function of drawing board, f or example: the new, open, save, empty, enlarge, shrink, reduction, basic graphics ren dering, convert the brush color, and other functions.Finally run results conform to the requirements of the design, the scheme is feasible.Program function is good.Key words Linux QT ; graphical user interface (GUI);electronic drawing board; double buffering mechanism目录摘要 (i)Abstract (ii)1 引言 (1)1.1 研究背景 (1)1.2 研究的目的和意义 (2)1.3 程序设计的环境选择 (2)2 画图板设计的技术背景 (3)2.1 Qt的主要特征 (3)2.2 QT creator简介 (3)2.3 Qt creator环境搭建 (4)2.4 QT编程机制信号与槽机制简介 (5)2.5 Qt编码规范 (7)2.6 GDI绘图理论基础 (9)2.7 双缓冲机制 (9)2.8 双缓冲技术绘图 (10)3 画图板项目需求分析 (12)3.1 可行性研究 (12)3.1.1 经济可行性 (12)3.1.2 技术可行性 (12)3.1.3 运行可行性 (12)3.1.4 时间可行性 (12)3.1.5 法律可行性 (12)3.2 功能分析 (13)3.3 系统用例分 (13)3.4 性能需求 (13)3.4.1 应用需求分析 (14)3.4.2 运行需求分析 (14)3.4.3 其他需求分析 (14)4 画图板概要设计 (15)4.1 画图板功能模块关系与划分 (15)4.2 画图板总体设计流程图 (16)5 画图板详细设计 (17)5.1 画图板界面设计 (18)5.1.1 画图板的界面元素声明 (18)5.1.2 图板界面布局实现 (19)5.2 画图板功能详细设计 (20)5.2.1 画图板的文件编辑功能实现 (20)5.2.2 画图板的图片编辑功能实现 (23)5.3 画图板绘图功能实现 (26)5.3.1 绘图板的基本图形绘制功能实现 (26)5.3.2 绘图板自由绘图功能实现 (30)5.3.3 画图板画图辅助选项实现 (33)6 画图板程序测试 (35)6.1 测试的重要性及目的 (35)6.2 测试的方法 (36)6.3 测试用例 (36)6.4 测试结果 (36)结论 (38)参考文献 (39)致谢 (40)外文原文 (41)中文翻译 (49)1 引言随着操作系统不断的更新换代,其自带的画图板界面及功能也是不断变化着,像是xp、vista、win7,它们的画图板的界面布局风格以及功能都有所不同。

bandgap电路设计报告

Bandgap电路设计报告Bandgap电路1)基准电压产生电路由于在之前tsmc035工艺电路设计中得到过验证且性能良好,本次带隙基准设计继续采用如下电路结构。

下图电路中,左边蓝色框内是BG的启动电路,属于下拉型。

电路上电时,如果输出点电压为0,则M1M3支路无电流,M1栅端电压为高,使得M2导通,将H点电压拉低,从而使电路启动。

之后,输出电压约为1.2,则M3导通,M1栅端电压下降,使得M2截止,启动电路不影响主电路的正常工作状态。

需要注意的是,M3的W/L较大,M1的W/L较小时,M2可以截止的较彻底,从而降低对主电路的影响。

图一基准电压产生电路图一中中间部分(M4-M7 & T1T2 & RaRb & OPA)为基准电压产生的主电路,通过Vbe 与ΔVbe的加权组合来实现零温度系数电压。

其中运放OPA的作用是提供VN=VP这一电压关系,共源共栅结构提高电流复制精度使得结果更加准确。

运放需要注意其正负输入端接入电路的位置,要使得最终形成的环路是负反馈的。

M8M9复制一路电流,供给后端的电流产生电路的运放使用。

通过仿真可以发现,此结构的带隙基准的噪声主要来源于运放、M4M5和RaRb,为降低噪声M4M5的过驱动电压取的较大,同时RaRb电阻值取的较小。

电阻值较小直接导致两路电流都较大,由于三极管的Vbe电压不能偏离700mv太多(否则电压温度曲线特性不好),需要适当调整T1T2的m值。

另外,这里的运放偏置是由运放的输出电压提供的,同时与M4M5的栅端相连,可以考虑运放内部与外电路也形成电流复制的结构。

由于存在环路,我们还必须保持环路的稳定性,考虑到运放需要一定的增益(60dB+)使得VN与VP相等,这里采用两级运放,刚好可以将环路的主极点设置在运放第一级的输出端使环路稳定。

根据以上几点的条件,可以得到运放的结构如下图二所示。

其中的两个P管电流源可以看成是与图一中M4和M5成电流复制结构。

模拟电路版图设计方法与框架结构毕业论文【范本模板】

上海城市管理职业技术学院毕业设计(论文)分院人文与信息技术学院专业应用电子班级 11应用电子(1)姓名胡穆学号 110502003指导教师崔玉美设计(论文)题目模拟电路版图设计方法与框架结构二○一三年三摘要集成电路的出现与发展彻底改变了人类的文明和人们的日常生活面目,比如:手机、U盘、麦克风、等等。

集成电路是电子电路,它不不同于一般意义上的电子电路,它是把成千上万的电子元件包括晶体管,电阻,电容甚至电感集成在微小的芯片上面,正是这种奇妙的设计和制造方式使它为人类社会的进步创造了空前绝后的奇迹,而使这种奇迹变为现实的是集成电路掩膜版图设计。

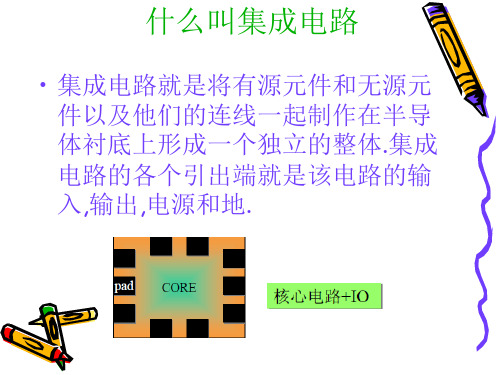

集成电路或称微电路(microcircuit)、微芯片(microchip)、芯片(chip)在电子学中是一种把电路(主要包括半导体装置,也包括被动元件等)小型化的方式,并通常制造在半导体晶圆表面上。

集成电路是相对分立器件组成的电路而言、把组成电路的元件、器件以及相互间的连线放在单个芯片上,整个电路就在这个芯片上,把这个芯片放到管壳中进行封装,电路与外部的连接靠引脚完成。

根据电路功能和性能的要求,在正确选择系统配置、电路形式、器件结构、工艺方案和设计规则的情况下,尽量减小芯片面积,降低设计成本,缩短设计周期,以保证全局优化,设计出满足要求的集成电路。

关键词:版图设计;设计规则;版图验证;电阻,电容,二极管;目录摘要------------------------------------------------------------ 2前言-------------------------------------------------------------- 4 第一章了解版图-------------------------------------------------- 5 1。

1 版图意义----------------------------------------------------- 5 1.2 版图定义-------------------------------------------------------- 5 1。

版图设计论文15篇

版图设计论文15篇版图设计论文摘要:集成电路版图设计教学应面向企业,按照企业对设计工程师的要求来安排教学,做到教学与实践的紧密结合。

从教学开始就向学生灌输IC行业知识,定位准确,学生明确自己应该掌握哪些相关知识。

从集成电路数字版图、模拟版图和逆向设计版图这三个方面就如何开展教学可以满足企业对版图工程师的要求展开探讨,安排教学有针对性。

在教学方法与内容上做了分析探讨,力求让学生在毕业后可以顺利进入IC行业做出努力。

关键词版图设计设计论文设计版图设计论文:一种基于厚膜工艺的电路版图设计摘要:在电子线路版图设计中,通常采用印刷线路板技术。

如果结合厚膜工艺技术,可以实现元器件数目繁多,电路连接复杂,且安装空间狭小的电路版图设计。

通过对3种不同电路版图设计方案的理论分析,确定了惟一能满足要求的设计方案。

基于外形尺寸的要求,综合考虑电路的性能和元件的封装形式,通过合理的电路分割和布局设计,验证了设计方案的合理性和可实现性。

体现了厚膜工艺技术在电路版图设计中强大的优越性,使一个按常规的方法无法实现的电路版图设计问题迎刃而解。

关键词:电路版图设计;电路分割设计;厚膜混合集成电路;厚膜工艺0 引言随着电子技术的飞速发展,对电子设备、系统的组装密度的要求越来越高,对电路功能的集成度、可靠性等都提出了更高的要求。

电子产品不断地小型化、轻量化、多功能化。

除了集成电路芯片的集成度越来越高外,电路结构合理的版图设计在体积小型化方面也起着举足轻重的作用。

1 厚膜工艺技术简述厚膜工艺技术是将导电带和电阻通过丝网漏印、烧结到陶瓷基板上的一种工艺技术[1]。

厚膜混合集成电路是在厚膜工艺技术的基础上,将电阻通过激光精调后,再将贴片元器件或裸芯片装配到陶瓷基板上的混合集成电路[2]。

厚膜混合集成电路基本工艺流程图见图1。

图1 厚膜工艺流程图厚膜工艺与印制板工艺比较见表1。

2 电路版图设计2.1 设计要求将电路原理图(图2,图3)平面化设计在直径为34 mm的PCB板上(对电路进行分析后无需考虑相互干扰),外形尺寸图见图4。

版图设计毕业设计

摘要摘要进入21世纪以来,我国信息产业在生产和科研方面都大大加快了发展速度,并已成为国民经济发展的支柱产业之一。

但是,与世界上其他信息产业发达的国家相比,我过在技术开发、教育培训等方面都还存在这较大的差距。

集成电路已经发展到了系统级芯片(SOC)的阶段。

随着CMOS 工艺阶段的进步,由于CMOS 电路的低成本,低功耗、以及速度的不断提高,由于CMOS模拟电路设计的技术不断进步,CMOS技术已被证明是实现SOC的最好选择。

模拟电路是SOC中不可缺少的部分。

由于器件尺寸不不断缩小和低电源电压,低功耗等要求,模拟CMOS集成电路设计在不断的发展,在SOC中变得越来越重要。

作为设计与制造的纽带,版图的地位至关重要。

在各类集成电路中,模拟集成电路由于对器件的依赖性更强,所以起性能更大程度上受到版图因素的影响。

关键字:集成电路设计,版图设计ABSTRACT ABSTRACT Since the 21st century, China's information industry in production and research research aspects aspects aspects are are are much much much faster faster faster development development development speed, speed, speed, and and and has has has become become become a a a pillar pillar industry industry of of of the the the national national national economy economy economy development. development. development. However, However, However, with with with the the the world world world of of information industry developed countries other than, I live in technical development, development, education education education training training training etc etc etc are are are still still still exist exist exist in in in the the the larger larger larger gap gap gap Integrated Integrated circuit circuit has has has developed developed into into system system system level level level chip chip chip (SOC) (SOC) (SOC) stage. stage. stage. Along Along with with the the progress of stage of CMOS technology, due to the low cost, CMOS circuit, and low consumption rate rise ceaselessly, because the CMOS analog circuit design technology progress, CMOS technology has been proved to be the best choice of SOC SOC realization. realization. realization. Analog Analog Analog circuit circuit circuit is is is an an an indispensable indispensable indispensable part part part of of of SOC. SOC. SOC. Due Due Due to to to the the device device size size size and and and low low low voltage voltage voltage shrinking, shrinking, shrinking, low low low power power power consumption, consumption, consumption, analog analog analog CMOS CMOS integrated circuit design in the unceasing development, in the SOC of becomes more more and and and more more more important. important. important. As As As the the the design design design and and and manufacture manufacture manufacture of of of the the the link, link, link, the the position is very important. In all kinds of integrated circuits, analog circuits due to to the the the dependence dependence dependence of of of the the the device, device, device, so so so its its its stronger stronger stronger performance performance performance greater greater greater extent extent extent by by the factors which influence the territory. Key Words: integrated circuit design, layout design目录目录目 录第1章 引言引言引言 ........................................................ 1 .. (1)1.1 1.1 选题背景选题背景选题背景 ........................................................ 1 .. (1)1.2 1.2 研究目标和意义研究目标和意义研究目标和意义 .................................................. 1 .. (1)1.3 1.3 研究思路研究思路研究思路 ........................................................ 1 .. (1)第2 2 章章 版图设计理论基础版图设计理论基础............................................. 2 2.1版图概念版图概念......................................................... 2 2.2 2.2 版图设计过程版图设计过程版图设计过程 .................................................... 2 . (2)2.3 2.3 版图验证与检查:版图验证与检查:版图验证与检查: ................................................ 3 (3)2.4 2.4 版图设计注意事项版图设计注意事项版图设计注意事项 ................................................ 3 ................................................ 3 第 3 3 章章 Cadence Cadence 工具使用工具使用工具使用 ............................................ 5 .. (5)3.1 Cadence 3.1 Cadence 软件简介软件简介软件简介 ................................................ 5 (5)3.2. 3.2. 建立新库和新文件建立新库和新文件建立新库和新文件 ............................................... 6 .. (6)3.3 3.3 版图的验证版图的验证版图的验证 ...................................................... 8 (8)3.4 3.4 布局相关布局相关布局相关 ....................................................... 11 ....................................................... 11 第 4 4 章章 模拟版图设计匹配模拟版图设计匹配 ........................................... 13 . (13)4.1 4.1 匹配的概述匹配的概述匹配的概述 ..................................................... 13 .. (13)4.2模拟电路版图设计中的匹配艺术模拟电路版图设计中的匹配艺术.................................... 13 4.2.1 4.2.1 根器件法根器件法根器件法(Root Device Method) ................................. 13 (Root Device Method) (13)4.2.2 4.2.2 交叉法交叉法交叉法(Interdigitating Devices) .............................. 14 (Interdigitating Devices) (14)4.2.3 4.2.3 虚拟器件法虚拟器件法虚拟器件法 ................................................... 14 (14)4.2.4 4.2.4 共心法共心法共心法(Common Centroid) ...................................... 15 (Common Centroid) .. (15)4.2.5 4.2.5 匹配信号路径匹配信号路径匹配信号路径 ................................................. 16 . (16)4.2.6 4.2.6 尽量采用较大尺寸的器件尽量采用较大尺寸的器件尽量采用较大尺寸的器件 ....................................... 16 (16)4.3 4.3 结论结论结论 ........................................................... 17 .. (17)第5章 应用于USB 通道检测器版图设计通道检测器版图设计 ................................ 18 .. (18)5.1 USB 通道检测器的电路图:通道检测器的电路图:........................................ 18 5.2 5.2 版图电路的分析:版图电路的分析:版图电路的分析: ............................................... 18 .. (18)5.3 5.3 画版图步骤画版图步骤画版图步骤 ..................................................... 19 .. (19)目录目录5.4 5.4 电路中所画的版图电路中所画的版图电路中所画的版图 ............................................... 21 .. (21)5.4.1 5.4.1 以下将列举出画的版图中的部分版图以下将列举出画的版图中的部分版图以下将列举出画的版图中的部分版图 ............................. 21 .. (21)5.5 5.5 版图布局版图布局版图布局 ...................................................... 21 (21)5.6 5.6 版图连线版图连线版图连线 ....................................................... 22 ....................................................... 22 第 6 6 章章 结论结论结论 ...................................................... 23 (23)参考文献参考文献 ........................................................... 24 ........................................................... 24 致 谢谢 . (25)附录一:附录一:5V 5V 版图设计规则版图设计规则............................................. 26 附录二:附录二:USB USB 通道检测器网表通道检测器网表.......................................... 28 附录三:附录三:USB USB 通道检测器LVS 检测报告图检测报告图................................ 30 外文资料原文外文资料原文 ....................................................... 34 . (34)译文译文 ............................................................... 37 (37)第1章 引言引言1 第1章 引言1.1 选题背景集成电路已经发展到了系统芯片(SOC )的阶段,随着CMOS 工艺的进步,由于CMOS 电路的低成本、低功耗,以及速度的不断提高,由于CMOS 模拟电路设计技术的不断提高和进步,CMOS 技术已被证明是实现SOC 的最好选择。

一种电流求和型的低功耗Bandgap电压基准源

一种电流求和型的低功耗Bandgap电压基准源

朱卓娅;魏同立

【期刊名称】《东南大学学报(自然科学版)》

【年(卷),期】2003(033)006

【摘要】为满足标准P阱CMOS工艺要求,设计了一种新的电流求和型Bandgap 电压基准电路,实现了相对于地的稳定电压输出,并且能提供多电压基准输出.电路采用0.6μm UMC P阱CMOS工艺验证,HSPICE模拟结果表明:电路输出基准电压为800mV;在-40~85℃的温度变化范围内,电路温度系数仅为14×10-6/℃;电源电压为3.5V时,电路功耗低,消耗电流仅为1.5μA.该电路不需改变现有工艺,输出灵活,有望在多基准电压的低功耗系统中获得较广泛的应用.

【总页数】4页(P717-720)

【作者】朱卓娅;魏同立

【作者单位】东南大学微电子中心,南京,210096;东南大学微电子中心,南

京,210096

【正文语种】中文

【中图分类】TN432

【相关文献】

1.一种低功耗多输出带隙电压基准源电路的设计 [J], 张珂铭;

2.一种新型偏置电路的CMOS亚阈型电压基准源 [J], 蔡立达;常昌远

3.一种全MOS管结构低压低功耗电压基准源的设计 [J], 张昌璇;解光军

4.一种低功耗多输出带隙电压基准源电路的设计 [J], 张珂铭

5.一种用于锂电池保护芯片的低功耗电压基准源 [J], 马绍宇;韩雁;洪慧;周海峰因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要近年来随着IC设计要求的不断发展,集成电路版图设计是实现集成电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是否正确,而且也会极大程度地影响集成电路的性能、成本。

而集成电路中的bandgap可以在温度和电压不稳定的环境中保持稳定的参考电压,被广泛运用于比较器、A/D转换器等模拟电路及数模混合信号集成电路中,其性能直接影响整个系统的精度和性能。

因此,bandgap版图设计的研究非常有意义。

本文基于Cadence 版图设计软件平台,采用XFAB0.6µm CMOS 工艺设计。

设计的版图元件包括PMOS、NMOS、PNP三极管、电阻、电容。

其中对差分放大器、电流镜、电阻等重要元件采用了匹配和对称的设计方法,考虑电气特性的版图设计技术;为防止闩锁效应,本设计还运用了保护环保护整个电路,提高了bandgap 电路的可靠性。

本设计对最终设计出的版图使用calibre验证工具进行LVS和DRC验证,并顺利通过验证。

关键字:版图;带隙基准电压源;Cadence;匹配;验证ABSTRACTIn recent years, along with IC design request of continuously development, IC layout are essential to achieve the design of integrated circuit manufacturing sectors, it is not only related to the IC's functions are correct, but also great extent affect IC performance and cost.But bandgap reference voltage of integrated circuit can keep stability in the unsteady environment of the temperature and the electric voltage of reference electric voltage, used extensively in comparison machine, A/D conversion machine etc. analog electric circuit and some mixture signal integrated circuit. Its function is directly influence the whole accuracy and function of system. Therefore, the research which take the layout design of the bandgap reference voltage is very meaningful.This text ,according to the design software of the Cadence about layout design, adopts XFAB0.6µm CMOS of design rule.The component of layout design include PMOS, NMOS, PNP, electric resistance, electric capacity. To the OP、current and resistance which are importance components adopt layout design technique of consideration electricity characteristic; To reduce latch-up, this design still uses guard ring to protect the whole electric circuit, improving the credibility of bandgap reference voltage. In the end, this design carried LVS and DRC of verification to the landscape used calibre verification tool that finally designs and passed a verification smoothly.Key Words: Layout; Bandgap reference voltage; Cadence; matching; Symmetry目录第1章引言 (1)1.1选题背景及意义 (1)1.2国微电子发展状况 (1)第2章 Bandgap简介 (3)2.1 什么是Bandgap (3)2.2 Bandgap的原理 (3)2.3 Bandgap的应用 (5)第3章 Virtuoso工具及版图绘制 (7)3.1 Cadence 软件介绍 (7)3.2 Virtuoso工具的使用 (8)3.2.1建立版图库 (8)3.2.2层选择窗的设置 (11)3.2.3版图编辑窗的设置 (13)3.2.4Virtuoso的常用快捷键 (14)第4章 Bandgap的版图设计 (17)4.1版图设计中的相关主题 (17)4.1.1器件的匹配规则 (17)4.1.2匹配管子的版图设计 (21)4.1.3电阻版图设计 (24)4.1.4倒比管版图设计 (25)4.1.5双极型晶体管版图设计 (26)4.1.6电容版图设计 (27)4.2全局规划(floor plan) (28)4.2.1模块摆放 (28)4.3整体布线 (29)第5章 Bandgap电路版图验证 (31)5.1版图验证的概述 (31)5.2版图的DRC验证 (32)5.3 版图的LVS验证 (35)结束语 (40)参考文献 (41)致42附录 (44)外文资料原文 (48)第1章引言1.1选题背景及意义随着IC工艺的发展,在模拟电路和数模混合电路中,片集成的基准源电路已被普遍采用,它是集成电路中的一个重要模块。

产生基准的目的是建立一个与电源波动和工艺无关、具有确定温度特性的直流电压或电流。

为了提高电路的性能对基准源的要求越来越高。

而相应的版图设计也是至关重要的,它直接关系到基准源性能的好坏。

集成电路版图设计是连接集成电路工艺的桥梁,它在集成电路发展过程中起着重要作用。

随着特征尺寸的不断减小,使得版图设计中需要考虑的问题越来越多,对版图设计人员的要求也越来越高。

研究本课题从基础入手,一方面是电路和版图理论知识的学习,另一方面是EDA工具的应用实践,理论与实践相结合能够帮助我轻松了解IC后端设计的全过程,熟练运用Cadence工具进行版图设计和验证以及掌握版图设计的基本方法和技巧。

这将对所学知识的巩固和今后从事相关工作有很大帮助。

1.2国微电子发展状况随着全球信息化、网络化和知识化经济浪潮的到来,集成电路产业的战略地位越来越重要,它已成为事关国民经济、国防建设、人民生活和信息安全的基础性、战略性产业。

特别是近几年来,在世界半导体产业环境不断改善,集成电路的性能以惊人的速度向快速和微型方面发展,其发展潜力、高技术含量和广阔的市场都令人叹为观止。

与此同时,中国集成电路产业也已经开始快速发展,正在努力向世界技术前沿靠拢。

也就是说,我们中国的IC产业已经初具规模,并且正处在一个摆脱一味只是集中在制造和消费方面而向核心技术领域转型的一个关键阶段,所有的IC精英们正在齐心协力打造中国自己的“中国芯”,争取早日扭转在核技术上受制于人的局面,这是每一个IC精英义不容辞的责任,同时也是产业调研的最大目的。

随着我国国民经济的持续高速增长,蓄势多年的我国IC产业出现了勃勃生机,呈现群体发展态势。

我国在2002年底前,共有3条8英寸生产线,6条6英寸线,6条5英寸线,10条4英寸线。

2003年正在建设的有5条8英寸线,2条6英寸线。

正在筹建的有1条12英寸线,8条8英寸线,6条6英寸线,1条5英寸线。

这些生产线的建立将有助于缩小我国与世界先进水平的差距。

目前我国 IC 芯片制造企业有49家,其中综合制造企业40家,委托加工6家,相对集中在长江三角洲地区、京津地区和珠江三角洲地区。

近几年我国IC产业取得了一定的进步,2001 年国产IC的产我国的集成电路(IC)产业近年来发展非常迅速,对IC设计人才的需求日益趋膨胀,尤其在版图设计方面的人才更是紧缺,因此,版图设计的培养就越来越迫切。

第2章 Bandgap简介本章主要介绍Bandgap的基本知识。

首先给出Bandgap的定义;然后对其原理及运用进行说明,重点讲述带隙基准源的原理;最后用具体例子阐述基准源的实际应用。

本章是本课题的一个理论基础,具有一定的电路知识将对后面的版图设计有较大帮助。

2.1 什么是BandgapBandgap voltage reference中文翻译为带隙基准电压源,也常常有人简单地称它为Bandgap。

是利用一个与温度成正比的电压与二极管压降之和,二者温度系数相互抵消,实现与温度无关的电压基准。

因为其基准电压与硅的带隙电压差不多,因而称为带隙基准。

实际上利用的不是带隙电压。

现在有些Bandgap结构输出电压与带隙电压也不一致。

模拟电路广泛的包含电压基准和电流基准。

这种基准是直流量,它与电源和工艺参数的关系很小,但与温度的关系是确定的。

产生基准的目的是建立一个与电源和工艺无关,具有确定温度特性的直流电压或电流。

在大多数应用中,所要求的温度关系采取下面三种形式中的一种:1)与绝对温度成正比;2)常数Gm特性,也就是,一些晶体管的跨导保持常数;3)与温度无关。

要实现基准电压源所需解决的主要问题是如何提高其温度抑制与电源抑制,即如何实现与温度有确定关系且与电源基本无关的结构。

由于在现实中半导体几乎没有与温度无关的参数,因此只有找到一些具有正温度系数和负温度系数的参数,通过合适的组合,可以得到与温度无关的量,且这些参数与电源无关。

2.2 Bandgap的原理Bandgap广泛应用于电源调节器、A/D和D/A转换器、数据采集系统,以及各种测量设备中。

它的原理是通过合理的电路设计,设法利用正、负温度系数相互抵消来补偿Vbe随温度变化对输出电压的影响,以获得接近零温度系数的基准源。

它可以在温度和电压不稳定的环境中保持稳定的参考电压,被广泛运用于模拟电路及数模混合信号集成电路中。

图2-1为带隙基准电压源的原理示意图。

双极性晶体管的基极-发射极电压VBE,具有负的温度系数,其温度系数一般为-2.2 mV/K。