ModelsimSE仿真步骤

如何在ISE环境中使用ModelSim仿真

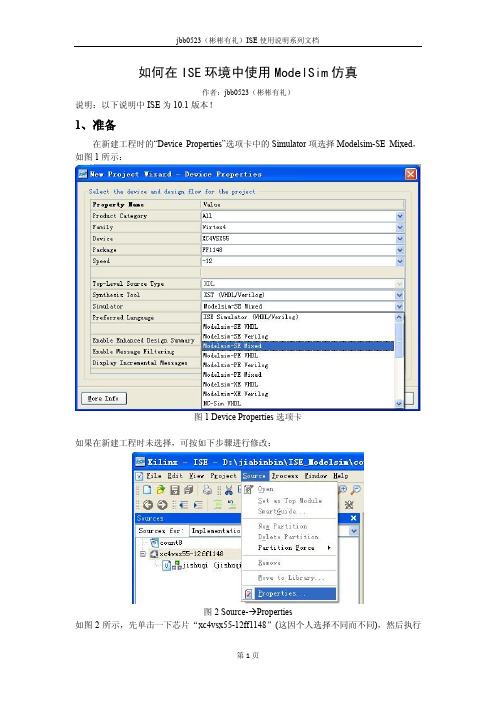

如何在ISE环境中使用ModelSim仿真作者:jbb0523(彬彬有礼)说明:以下说明中ISE为10.1版本!1、准备在新建工程时的“Device Properties”选项卡中的Simulator项选择Modelsim-SE Mixed,如图1所示:图1 Device Properties选项卡如果在新建工程时未选择,可按如下步骤进行修改:图2 Source- Properties如图2所示,先单击一下芯片“xc4vsx55-12ff1148”(这因个人选择不同而不同),然后执行Source——Properties,修改即可。

2、仿真步骤1)如图3所示,在需要仿真的源文件上右击,选择“New Source…”图3 右击---New Source2)如图4所示,在Select Source Type选项卡中选择“Verilog Test Fixture”,输入File name,单周next,直到完成。

图4 Select Source Type3)将source for选择为“Behavioral Simulation”,打开刚刚新建的文件,编辑该文件,输入仿真需要的代码(其实就是对输入信号进行配置)。

然后双击过程管理区的“Simulate Behavioral Model”,即可自动打开ModelSim进行仿真(此时ModelSim不能处于打开状态,否则会出错的),如图5所示(注意图中每一处用红线标记的部分)。

4)如果是首次仿真,ModelSim会出现如下错误:图6 ModelSim error这是一个很普遍的错误,百度此错误中的关键字“Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver".”即可找到解决办法。

如图7所示,Source for中重新选择Implementation,其它按照图中的红线标识单击或选择,然后双击“Compile HDL Simulation Libraries”,等待编译成功结束后,重新执行步骤3)即可。

ModelsimSE的使用方法 简单易懂

2020/10/13

西安邮电学院计算机系

9

图2.3

2020/10/13

西安邮电学院计算机系

10

编译: 编译(包括原代码和库文件的编译),编译可点击Comlile > Comlile All来完成。

2020/10/13

西安邮电学院计算机系

11

装载文件: 如图2.4,点击Simulate -> Simulate..后,如图 2.5所示,选定顶层文件(激励文件),ADD加入,然后 点击load,装载。

2020/10/13西安邮电学Fra bibliotek计算机系3

2.1代码仿真需要的文件

设计HDL源代码:可以使用VHDL语言或Verilog HDL语言。(这里以附录用Verilog语言编写的4位计数器 为例进行说明)

测试激励代码:根据设计要求编写输入/输出的激励程序, 由于不需要进行综合,书写具有很大的灵活性。

2020/10/13

西安邮电学院计算机系

21

图3.1

2020/10/13

西安邮电学院计算机系

22

图3.2

2020/10/13

西安邮电学院计算机系

23

用Qusrtus产生仿真所需要的网表与sdf文件: 在作了第一步的正确设置后,每当你完成一次编译, Quartus会自动在你的当前Project 目录下生成一个 simulation目录,在该目录下,就有我们所需要的文件。如 果使用VHDL语言,网表文件是.VHO,SDF文件.SDO;如果 使用Verilog语言,网表文件是.VO,SDF文件也是.SDO。

2020/10/13

西安邮电学院计算机系

5

图2.1

2020/10/13

用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)

用ModelSimSE进行 功能仿真和时序仿真的方法 (ALTERA篇)黄俊April 2007用ModelSim SE进行功能仿真和时序仿真的方法 (ALTERA篇)软件准备(1) QuartusII,本文截图是QuartusII 6.1界面的。

我个人认为,如果是开发StratixII或CycloneII或MAXII,用QuartusII6.0+SP1+SP2比较稳定。

(2) ModelSim SE. ALTERA仿真库要已经装好,安装仿真库的笔记已记录于《在ModelSimSE中添加ALTERA仿真库的详细步骤》中。

我电脑上装的是ModelSim SE6.1b。

例子程序的制作先在Quartus II里生成一个例子程序,以方便介绍三种仿真的方法。

步骤如下:1、新建一个工程(Project),工程名取lpm_shift, 器件选CycloneII EP2C5Q208C, 第三方的工具暂时都不选。

2、菜单栏上ToolsÆMegaWizard Plug-In Manager, 点Next,在storage中选LPM_SHIFTREG,输出文件格式根据习惯选一种语言,在这里以Verilog的为例,在右边的output file名字中加上lpm_shift。

点Next。

3、这个例子是做一个移位寄存器,调用lpm库,和cycloneII元件库,也正好可以作为对前面建好的ALTERA库的一个验证。

点可以查到该模块的使用说明和详细介绍。

移位寄存器比较简单,就不用细看了。

如下图设置.点Next.4、加上一个异步清零端,点Next,再点Next,最后点Finish.Add/Remove Files in Project…,6、点图标,选中生成的lpm_shift,点打开再点Add都加到项目中去。

7、在这里直接把lpm_shift.v当成顶层文件,就不需要再例化它了。

8、下面写一个简单的TestBench.a)Quartus II工具栏上点图标,选Verilog HDL;b)点,设文件名为top_tb;c)如下所述写一个简单的TestBench.(例子见附件)开始仿真z ModelSim仿真有很多种流程,下面我采用个人感觉比较好一个流程进行仿真验证:基于工程(Project)的流程Step1 新建一个工程Step2 添加文件到工程中去Step3 编译设计文件Step4 启动仿真器,指定顶层设计单元Step5 查看和调试结果z对的设计有三个阶段的仿真。

Modelsim仿真新手入门最详细教程

Modelsim仿真新⼿⼊门最详细教程2021年11⽉15⽇00 安装包/版本我是提前在⽹上下好的(但这⼀点也给我的实验造成了“⿇烦”),⽤的是Modelsim SE-64 2020.4版本的,学校实验室的似乎不同。

但最终没有太⼤影响。

01 配置环境步骤学校有⼀个⽂档,在机房电脑照做就⾏。

我因为是⾃⼰下载的,配置与机房软件有所不同,所以⼜平添了很多⿇烦。

01-0 verilog⽂件这个代码可以在很多地⽅编写:Visual Studio Code⾥有Verilog的插件;还可以有更强⼤的语⾔编辑器:Nodepad++。

这⾥我使⽤的是Nodepad++,因为看上去专业⼀点。

Nodepad++的页⾯效果如图:其实第⼀次上机,⽼师会给⼤家⽰例⽂件(包括设计代码与测试代码),跑出来⽰例波形就⾏。

01-1 具体步骤1. 新建⼀个⽤于安放project的⽂档,放在哪⾥都⾏。

把前⾯做出的.v⽂件添加到这个⽂档。

留意⼀下路径。

2. 打开modelsim,在jumpstart中create a new project。

3. 在弹出的提⽰框⾥browse,找到刚才的⽂件夹。

选中。

填写project 名,注意要与.v⽂件⾥的module名保持⼀致。

点击ok。

4. 进⼊页⾯后会是这样⼦:注意此处两个⽂件后⾯应当都有问号,代表没有编译。

先逐个右击⽂件add to this project确保加⼊。

5. 在上⽅提⽰栏中complie->compile all。

稍等些许会看到⽂件后问号全部变为对勾,表⽰代码编译通过,没有问题。

如果此步出错则代表代码有bug。

在下⾯的Transcript中上翻查找错误。

6. 点击上⽅Simulate->start simulation。

由于注意与实验室不同的,选中下⾯的Enable optimization,再在右侧Optimization Options中的Visibility中选中Apply full visibility....7. 接着在work⾥找到测试代码的⽂件,选中。

ModelSim+SE+6.5仿真软件下载及安装步骤

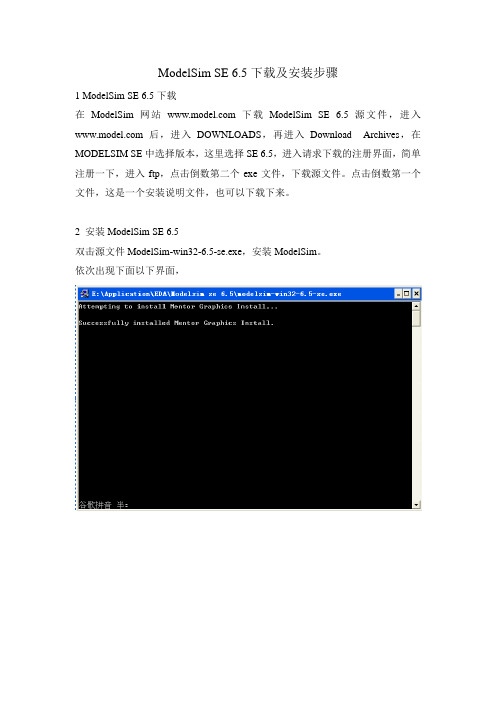

ModelSim SE 6.5下载及安装步骤1 ModelSim SE 6.5下载在ModelSim网站下载ModelSim SE 6.5源文件,进入后,进入DOWNLOADS,再进入Download Archives,在MODELSIM SE中选择版本,这里选择SE 6.5,进入请求下载的注册界面,简单注册一下,进入ftp,点击倒数第二个exe文件,下载源文件。

点击倒数第一个文件,这是一个安装说明文件,也可以下载下来。

2 安装ModelSim SE 6.5双击源文件ModelSim-win32-6.5-se.exe,安装ModelSim。

依次出现下面以下界面,点击【Next>>】,点击【Agree】点击【Browse】,选择安装路径,此处安装在E:\Eapp\EDA\ModelSim下,点击【Next>>】,正在安装,单击【Y es】,建立桌面快捷方式,单击【Y es】,单击【Y es】,单击【Y es】,重启计算机。

3 ModelSim SE 6.5破解3.1 生成LECENSE.dat文件到网上下载一个ModelSim SE 6.5的破解文件,我下载的是ModelSim6.5_KeyGen 文件夹,里面有个MentorKG.exe文件,双击它产生LECENSE.txt文件,将文件后缀txt改成dat。

复制LECENSE.dat到Modelsim SE 6.5\win32下,此处为E:\Eapp\EDA\Modelsim SE 6.5\win32。

3.2 右击桌面上的“我的电脑”,打开“属性”/“高级”/“环境变量”,在系统变量中新建LM_LICENSE_FILE,编辑中输入上一步LIECENSE.dat所在的路径,E:\Eapp\EDA\Modelsim SE 6.5\win32\ LICENSE.dat,确定即可。

重启计算机。

(这一步在下载的安装说明文件中有详细说明)。

在ModelSimSE中添加ALTERA仿真库的详细步骤

ModelSim学习笔记(二)在ModelSimSE中添加ALTERA仿真库的详细步骤黄俊April 2007以前用的是LATTICE的,ispLEVER有自带了一个OEM版的ModelSim。

要仿真时,不需要添加库,用起来比较方便,自己有点懒,所以就一直凑合着用。

现在转向用ALTERA 了,ALTERA也有OEM版的ModelSim,也不用添加库。

后来听说ModelSim SE的功能更强大,速度更快,所以就决定把ModelSim SE好好摸索一下,再多学习一点关于TestBench 技巧方面的知识。

我的学习资料主要是ModelSim SE自带的教程、ALTERA提供的资料以及edacn上面ModelSim专栏由网友们上传的资料。

因为是初学,加上看到英文资料一大堆,烦都烦死,而有些中文文档可能是有些步骤没有讲清楚,我实际按照文档上面说的一步一步做下来也老是完成不了,花了不少时间。

我于是就想自己摸清楚后,把步骤截图下来,整理清楚,做成笔记。

一方面加深自己的认识,另一方面对初学者也许会有些许用处。

我近期计划陆续整理出以下几个方面的学习笔记:初学ModelSimSE时被迷糊了几天的若干概念在ModelSimSE中添加ALTERA仿真库的详细步骤用ModelSimSE进行功能仿真和时序仿真的方法(ALTERA篇)ModelSimSE中常用到的几个命令及DO文件的学习笔记近来学到的几招TestBench的技巧MSN: paulhuang_sz@E-mail: huangjun5927@Blog: /index.php/2599在ModelSimSE中添加ALTERA仿真库的详细步骤装仿真库前要先了解几个概念1、装ModelSim之前,要先装QuartusII。

安装好QuartusII后,在其安装目录下…\quartus\eda\sim_lib里面存放了所有的仿真原型文件(simulation modelfiles)。

modelsim+ISE后仿真流程

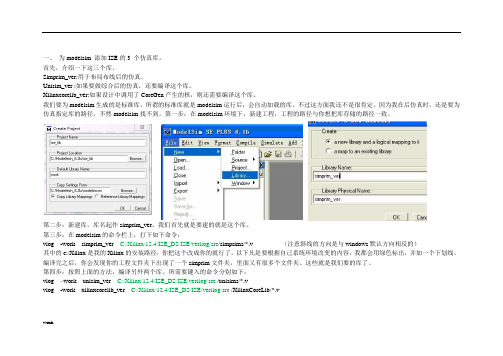

一、为modelsim 添加ISE的3 个仿真库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src/simprims/*.v (注意斜线的方向是与windows默认方向相反的)其中的c:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

以下凡是要根据自己系统环境改变的内容,我都会用绿色标出,并加一个下划线。

编译完之后,你会发现你的工程文件夹下出现了一个simprim文件夹,里面又有很多个文件夹。

这些就是我们要的库了。

第四步:按照上面的方法,编译另外两个库。

所需要键入的命令分别如下:vlog –work unisim_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src /unisims/*.vvlog -work xilinxcorelib_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src /XilinxCoreLib/*.v第五步:把库建好后,接下来的事情就是使它成为modelsim的标准库。

这只要修改modelsim安装目录下的modelsim.ini文件就可以了。

Quartus II调用ModelsimSE进行功能仿真

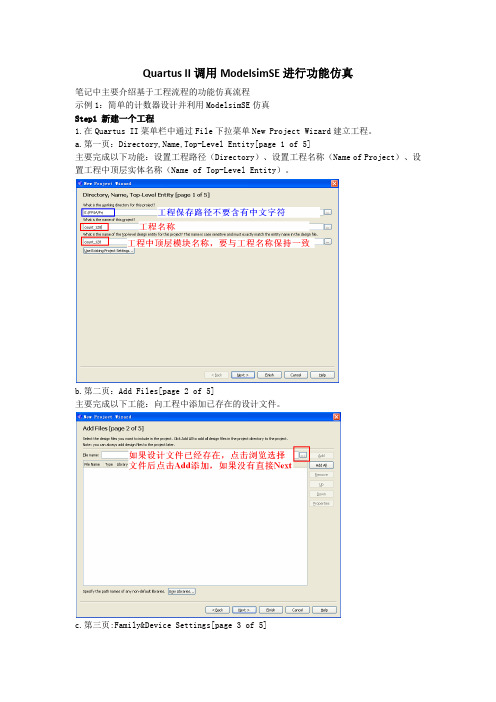

Quartus II调用ModelsimSE进行功能仿真笔记中主要介绍基于工程流程的功能仿真流程示例1:简单的计数器设计并利用ModelsimSE仿真Step1 新建一个工程1.在Quartus II菜单栏中通过File下拉菜单New Project Wizard建立工程。

a.第一页:Directory,Name,Top-Level Entity[page 1 of 5]主要完成以下功能:设置工程路径(Directory)、设置工程名称(Name of Project)、设置工程中顶层实体名称(Name of Top-Level Entity)。

b.第二页:Add Files[page 2 of 5]主要完成以下工能:向工程中添加已存在的设计文件。

c.第三页:Family&Device Settings[page 3 of 5]主要实现完成功能:选择自己所使用的FPGA芯片。

d.第四页:EDA Tool Settings[page 4 of 5]主要完成功能:根据需要选择使用哪种EDA工具Design Entry/Synthesis:设计输入/综合工具Simulation:仿真工具Timing Analysis:时序分析工具Format Verification:格式验证工具Board –Level:板级工具e.第五页:Summary[page 5 of 5]主要完成功能:生成建立工程的总结报告,包含了前面设置的内容。

根据报告查看新建工程是否与自己要建立的工程要求一致,如果不一致返回(<Back)上一层或多层进行修改,直到满足要求为止。

f.Finish:通过工程向导完成新建工程。

2.向新建工程中添加设计文件。

根据自己使用的HDL语言添加设计文件,Finish完成。

本示例中设计文件代码如下所示:完成一个简单的计数器,使计数器计数满128后重新计数。

module count_128(clk,rst_n,count);//工程模块及端口声明input clk,rst_n;//输入信号:时钟信号和复位output reg[7:0] count;//定义count位宽和数据类型always@(posedge clk or negedge rst_n)if(!rst_n)count<=8'd0;//复位置零else if(count[7])//当count最高位为1,也就是计数到128时,count置0count<=1'd0;else //否则继续计数count<=count+1'd1;endmodule/*计数模块实现128计数,当coun计数满128重新计数*/3.将设计文件保存在工程目录下并对设计文件进行语法分析。

Modelsim仿真流程-经验总结

Modelsim仿真流程-经验总结1.Modelsim简介略。

2.modelsim仿真流程:modelsim基本的仿真流程包括建立库、建立工程并编译、仿真、调试、但在libero环境中运行modelsim时,软件自动映射库和生成工程文件。

其中功能仿真、综合仿真以及后仿真分别映射presynth、postsynth和postlayout库。

基本流程是:建立工作库→编译源代码→启动仿真→分析、调试。

2.1建立库并映射在modelsim中,任何使用VHDL、Verilog HDL、SystemC等语言实现的设计,都被编译到一个库中。

♥方法一:File>New>Library选择新建并映射到该库;♥方法二:在modelsim>提示符下运行命令vlib work2-建立库,vmap work work2-建立映射库;2.2建立工程Modelsim仿真需要建立自己的工程,同时modelsim还提供了文件夹管理工程的功能。

♥step1:File>New>project,并指定库文件名;♥step2:新建文件或导入文件;2.3编译文件建立好工程后,使用compile功能对源文件进行编译。

Libero环境启动modelsim时,系统执行run.do脚本文件自动编译源文件。

♥鼠标右击文件,选择compile All对所有的工程文件执行编译操作;♥启动仿真,使用simulation>start simulation>选择design选项卡功能使modelsim进入仿真状态,之后可以运行仿真。

在libero环境下,运行modelsim直接从运行仿真这一步骤开始。

♥运行仿真可以设置仿真时间或选择仿真全部♥tcl命令:do run.do –当设计修改后,使用此命令重新导入设计;Do wave.do-打开波形列表文件,或者向当前波形添加列表;Restart-复位当前仿真,从0时刻重新仿真;Run 1ms-运行仿真1ms时间;Run all-运行全部的仿真;在libero环境下,可以自己编写脚本文件代替run.do文件,在项目比较大的情况下可以大大简化仿真的操作。

modelsim仿真详细过程

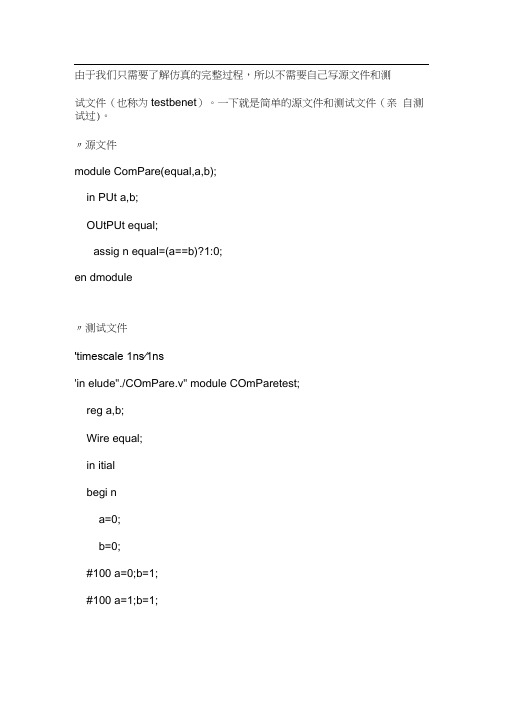

由于我们只需要了解仿真的完整过程,所以不需要自己写源文件和测试文件(也称为testbenet)。

一下就是简单的源文件和测试文件(亲自测试过)。

〃源文件module ComPare(equal,a,b);in PUt a,b;OUtPUt equal;assig n equal=(a==b)?1:0;en dmodule〃测试文件'timescale 1ns∕1ns'in elude"./COmPare.v" module COmParetest;reg a,b;Wire equal;in itialbegi na=0;b=0;#100 a=0;b=1;#100 a=1;b=1;#100 a=1;b=0; #100 $stop; endCOmPare ComPare1(.equal(equal),.a(a),.b(b)); en dmodule有了源文件和测试文件下面就开始用modelsim 进行仿真了步骤一:新建工程和∙v 文件(也就是源文件和测试文件) 打开modelsim 软件,点击file ,选择new — >project 然后就会弹出下面窗口:reα aWire iniEi begin a≡0 b=o≠ιoo≠100 #100 ≠100end-all I -CcIlltinUe I -finish I -iπit I -next I -SteP I -OVers√4* 1 ⅛ ι m a i m i然后在PrOjeCt name 那一栏写上工程名(随便去,一般是字母),在PrOjeCt location 选择工程路径(路径最好没有中文,听说的),然后点 OK 。

进入下个界面:l..∕sy nops¥E仁/sv 」Id∖.∣sl...5t =A J, '■■M'.Jn '..∕□JCotnPare endmod口*Module. V MCreate new file” •弹出界面:然后点击小框里面的“HelP I Colur™ILaVoUt AlICOLUJl∏3l⅛⅝l Project - E:/SirTI∕lx4∕compareStatugType ]θrd 皀{l⅜di⅜ecjΓ⅛meIM I COmPareHV5双击GGmPare.v 文件会弹出编译窗口:Ln-Smodule GOInPdre (equal t IrLPUt a, t ; output equal ;ASSign equal≡{a≡≡b) ?e τιdι∏Q dule复制上面源文件代码,粘贴到上图右边窗口里面IIt WindOW HeIP]>] ⅛I M J E⅛m∕lχ4∕QQ<nPare l V i+ X然后点击保存图标,然后再新建测试文件。

quartus联合Modelsim SE 10仿真最强教程

quartus 和modelsim联合仿真教程一、设置Modelsim SE 10.0c的路径,以便进行联合仿真使用。

(1) Tools—>optins。

设置路径(2) Modelsim 目录下,选择安装路径找到win32所在的路径然后点击OK ……(3) 设置仿真方式下面圆圈里面的选择 Modelsim 和语言二、新建工程,进行进行设计。

网上很多不在多说。

仿真通过,分配引脚。

综合布局布线。

进行时序约束。

(1)引脚分配(2)简单时序约束(3)进行仿真设置:自动生成 textbeach用quartus ii 打开textbeach .vt 文件。

系统自动会在你的工程文件下生成一个modelism 文件夹,这个就是你联合仿真的工程文件,再里面找到.vt 文件打开。

(4)编写textbeach 文件(5)进行仿真设置:点击 0k ,然后点击textbeach 。

会弹出来下面的一个框,点击NEW.然后会弹出来下面的一个文本框,1,处写你的测试文件名,2,处写下面你testbeach文件下的顶层文件名。

3,处打钩。

4处 il 以你的textbeach上的为准。

5,找到你的.VT文件。

6、点击add 。

7、OK/8、OK/9、apply/10、OK。

综合一下。

进行仿真。

三、减少对库的编译,以减少仿真时间。

(1)点击”>>” 把你的器件系列添加进来。

2、选择venlog 语言或者VHDL 语言,3、选择你的库的保存文件夹,5,点击开始,等待生成完成,关闭。

(2)0、1处都把库加入进去。

四、ROM仿真设置。

生成ROM(ROM应用项目例程)。

(1)设置保存路径,及保存文件名,设置仿真文件路径。

(2)创建.mf文件。

更改相应值。

(3)完成。

五、下载添加驱动(新建工程时添加驱动此时可以不添加)其他未用到的引脚可以设置成输入暂态。

选择开发板上面的flash选择E PC……选择下载USB-Blaster。

利用ModelSim SE6.0C实现时序仿真

1) 打开一个工程文件。

2) 打开Settings设置栏,选择EDA Tools Settings下的Simulation栏。

在右边出现的设置栏中将“Toolname”的下拉菜单选择“ModelSim(Verilog)”(如果工程用VHDL语言实现,则可以选择“ModelSim(VHDL)”;如果ModelSim使用的是for Altera的专用版本,则可以选择“ModelSim-Altera(Verilog)”或“ModelSim-Altera(VHDL)”)。

另外在设置栏中还有其他的核选框。

1. 如果选中“Maintain hierarchy”,则表示在做时序仿真时就能看到像在功能仿真的工程文件层次结构,可以找到定义的内部信号。

因为在做后仿时,源文件中的信号名称已经没有了,被映射为软件综合后自己生成的信号名,观察起来很不方便。

这个设置与ISE里综合右键属性的Keep Hierarchy选择YES的功能是一样的。

2. 如果选中“Generate netlist for functional simulation only”,则表示只能做功能仿真。

3) 点击“Start Compilation”按钮编译工程,完成之后在当前的工程目录下可以看到一个名为“Simulation”的新文件夹,下面的“ModelSim”文件夹下包括仿真需要的.vo网表文件和包含延迟信息的.sdo 文件。

4) 打开ModelSim软件(或者在Quartus下“Settings->EDA Tools Setting->Simulation”出现的设置栏中选中“Run this tool automatically after compilation”,直接从Quartus下调用ModelSim软件),可以在当前工程目录下新建一个Project。

在Project标签栏内点击右键,出现在快捷菜单中选择“Add toProject->Existing File…”。

ModelsimSE仿真步骤

WILDSCModelsimSE仿真教程Verilog & VHDL孙玉阳2014/6/3对于ModelsimSE仿真设置网上很难找到详细教程,在此写一篇基于Verilog 和VHDL的ModelsimSE的仿真设置教程,以期缩短大家ModelsimSE学习时间,由于时间仓促,不足之处还请见谅。

目录1 ModelsimSE仿真——Verilog HDL (2)1.1 建立资源库 (2)1.1.1 建立资源库的目的 (2)1.1.2 建立资源库前准备 (2)1.1.3 建立资源库的步骤 (3)1.2 功能仿真 (11)1.2.1 建立ModelsimSE工程 (11)1.2.2 添加Quartus工程文件 (12)1.2.3 编译 (14)1.2.4 仿真 (18)1.3 时序仿真 (21)2 ModelsimSE仿真——VHDL (25)2.1 建立资源库 (25)2.1.1 建立资源库的目的 (25)2.1.2 建立资源库前准备 (25)2.1.3 建立资源库的步骤 (26)2.2 功能仿真 (33)2.2.1 建立ModelsimSE工程 (33)2.2.2 添加Quartus工程文件 (34)2.2.3 编译 (37)2.2.4 仿真 (40)2.3 时序仿真 (44)1ModelsimSE仿真——Verilog HDL1.1建立资源库1.1.1建立资源库的目的Quartus Verilog工程文件里面在使用Primitives、Megafunction、LPM等Quartus自带模块时,会调用Quartus本身自带的一些库文件,但是ModelsimSE在仿真Quartus Verilog工程文件时不会自动去调用Quartus的库文件,同时ModelsimSE也不自带与Primitives、Megafunction、LPM相关的库文件。

所以在仿真Primitives、Megafunction、LPM等模块时,必须在ModelsimSE里建立与其对应的资源库,否则无法仿真。

如何用ModelsimSE仿真IP核-以PLL为例

如何⽤ModelsimSE仿真IP核-以PLL为例我们之前介绍了如何使⽤Modelsim SE进⾏仿真和利⽤do⽂件的仿真⽅法,但是其中待仿真的模块是我们⾃⼰编写的Verilog模块,但是在实际⼯作中,我们的设计中会经常⽤到FPGA ⼚商给我们提供的现成模块—IP核,这些模块我们看到不到源代码,只知道IP核的端⼝信息,当我们要仿真的时候,同样要向Modelsim提供这些IP核的信息,⽽FPGA⼚商也会给我们提供相应的IP核的编译库⽂件,我们如果设计中包含这些IP核,就必须在仿真之前,将这些库⽂件编译到Moldelsim 的库中去。

其实IP核只是我们要添加的其中⼀种库(MegaFunction),除此之外,我们还需要添加lpm库(设计中如果调⽤了lpm原件,需要添加此库),还有原语库(primitive),器件库(我们⽤的是cyclone),当然同⼀种库,还会分Verilog版和VHDL版。

这⾥只介绍Verilog版相关库⽂件的添加,VHDL版的,⽅法类似,⼤家只需更换相应的VHDL编译⽂件即可。

1.1.1.建⽴仿真库我们将IP核等相关库⽂件编译到Modelsim中后,以后凡是设计中调⽤到IP核时,我们就不⽤再重复添加了。

我们看⼀下如何在Modelsim中查看我们已经编译好的库,打开modelsim,如下图,会默认弹出名为library的窗⼝,窗⼝中的内容就有我们已经添加的库,⼀部分是Modelsim⾃带的库。

下⾯我们开始准备添加相关库⽂件。

第⼀步,⾸先在新建⼀个⽂件夹,⽤来存放我们编译后的库⽂件,这⾥命名为altera_lib,我们这⾥存放到了“C:\modeltech64_10.2c\”路径下,然后在altera_lib下新建四个⽂件夹lpm、altera_mf、altera_primitive、cyclone,如下图,后⾯我们会建⽴四个对应且相同名称的库。

第⼆步,建⽴库,我们以添加IP核库⽂件(altera_mf)为例进⾏介绍。

FPGA系统设计的仿真验证之: ModelSim的仿真流程

FPGA系统设计的仿真验证之:ModelSim的仿真流程7.3 的流程7.3.1 ModelSim的安装ModelSim的最新版本可以从互连网上免费得到,需要购买的只是License文件。

ModelSim的下载地址为http:///。

打开网站页面后可以点击Download,用户填写完一张表格以后可以得到一个小时的下载时光。

获得License的办法有无数种。

首先可以在线申请License文件,选取“开头→程序→ModelSim SE 5.8c →Submit License Request”,会打开一个网页,填写信息以后点击Submit就可以在线申请License了。

另外也可以点击“开头→程序→Modelsim SE 5.8c→License Request Instructions”会打开一个文本文档,按要求填写好后发到指定邮箱即可。

在得到License以后点击“开头→程序→Modelsim SE 5.8c→License Wizard”,在弹出的对话框里面指定License文件即可。

7.3.2 用法ModelSim举行功能仿真用法ModelSim对设计的HDL程序举行仿真分为功能仿真和时序仿真两种。

本节将以一个详细的实例讲解如何用法ModelSim对HDL工程举行功能仿真。

时序仿真的详细内容将在7.4节详细介绍。

这里我们用法的例子是一个分频的设计。

所谓分频电路是将较高频率的时钟分频,得到较低频率的时钟。

分频电路的用法较为广泛。

例如,我们要编写一个显示时光的电路就需要一个分频器,将晶振的频率分频得到1Hz的时钟信号。

分频有几种办法。

对于较为规章的分频,如2分频、4分频、8分频等,可以调用或者ISE本身的库函数来实现。

对于较不规章的分频,我们也有两种办法:一种是利用计数器的某一第1页共4页。

Modelsim SE的使用方法

仿真模型/库:根据设计内调用器件供应商提供的模块而 定。

2013/10/31

西安邮电学院计算机系

4

2.2代码仿真步骤

建立工程:

在modelsim中建立Project。如图2.1所示,点击file -> new -> project。得到creat project的弹出窗口,如图2. 2所示。在project name栏中填写你的项目名称,建议和

2013/10/31

西安邮电学院计算机系

18

在这里仿真以Altera 的器件为例。利用经过综合布局布线 的网表和具有时延信息的文件进行仿真,可以比较精确的仿 真逻辑的时序是否满足要求。

2013/10/31

西安邮电学院计算机系

19

3.1仿真需要的文件

综合布局布线生成的网表文件

测试激励

元件库 时序仿真需要综合布局布线生成的具有时延信息的文

2013/10/31

西安邮电学院计算机系

12

图2.4

2013/10/31 西安邮电学院计算机系 13

图2.5

2013/10/31 西安邮电学院计算机系 14

开始仿真:如下图示

2013/10/31

西安邮电学院计算机系

15

仿真波形如下图

2013/10/31

西安邮电学院计算机系

16

波形信号的保存:

件(sdf)文件。

2013/10/31

西安邮电学院计算机系

20

3.2

仿真步骤

在Quartus中正确设置仿真工具: 如图3.1所示,点击Quartus的Assignment菜单下的EDA Tools Settings,进入图3.2中,点击EDA tool type, 在Tools Settings的下拉菜单中,根据你所使用的语言与

如何使用Modelsim SE 进行门级仿真

如何使用Mod elsim SE进行门级仿真仿真分为功能仿真和时序仿真两部分,其中功能仿真是最基本的仿真验证,它只能仿真设计中的逻辑功能。

通过功能仿真,可以验证整个系统的逻辑功能是否正确。

用户可以通过观看仿真的波形来对系统的逻辑功能进行分析,并可以以此为依据,对设计进行必要的修改和完善。

布局布线以前的仿真都称为功能仿真,它包括综合钱仿真(Pre-Synthesis Simulation)和综合后仿真(Post-Synthesis Simulation)。

综合前仿真主要针对基于原理图框图设计,综合后仿真既适合原理图框图设计,也适合与HDL语言的设计。

时序仿真(后仿真,gate level simulation)时序仿真使用布局布线后期间给出的模块和连线的延时信息,在最坏的情况下对电路的行为作出实际的评估。

时序仿真使用的仿真器和功能仿真使用的仿真器是相同的,所需的流程和激励也是相同的,唯一的差别是进行时序仿真时加载到仿真器时的信息多了一个延时信息,而在最后的仿真结果的波形图中,时序仿真后的信号加载了时延,而功能仿真没有。

从以上来看,时序仿真是整个开发流程中十分重要的一环,我曾经由于不重视时序仿真而导致整个设计非常的不稳定。

而Modelsim上手也有一定难度,故在此做一下记录,为大家节省点时间。

这里主要来说明一下如何使用Quartus II + Modelsim 来进行时序仿真。

首先说一下环境:我这里使用的是Quartus II 11.0 && Modelsim SE 10.0c目的:在Quartus中写好的代码,编译过之后,可以自动进行时序仿真。

以下为设置步奏:打开或者新建一个项目,这里为了节省时间,直接用以前的项目了然后进行完全编译。

其它的,按照图片顺序来进行即可…然后就是一大堆弹出的窗口,仿真已经在进行着了。

(这个……其实会出错的,因为你后面还有那么一点点东西需要搞定,需要动脑子噻…接着往下走着)当然,仅仅这些是不能让仿真顺利进行的。

ISEmodelsim联合仿真教程

ISE、modelsim联合教程一、ISE的使用1、建立工程:A、点击File,然后New projectB、输入工程名和工程文件夹所在位置,那个Working Directory不用动,它会自动跟Location变化的(PS:工程名一定要用英文,存放工程的文件夹也一定要放在英文目录下,否则编译会出问题,这一点非常重要!!!)C、设定芯片类型什么的,点击Next,点击Finish就行了(PS:这里什么都不用修改,因为芯片类型啥的都可以在后面随时进行修改的)2、给工程添加文件:A、鼠标右击工程图标下面的芯片图标,选择New source,当您想往该工程中添加文件的时候选择下面的Add source(PS:一个工程下可以有多个文件)B、选择新建的文件类型,这里我们选择verilog module,在右边输入文件名称就可以了,文件位置默认是在工程文件下下(PS:文件名跟工程名最好一样,否则在后面也可能出现奇怪的问题,当程序写完了,要用modelsim仿真的时候这里就要添加verilog text fixture 文件了)C、设置程序的输入和输出端口,port name就是端口名称,如果该端口是输入端口就在direction中选择input,输出端口就选择output,如果该端口是总线的形式,就勾选上bus,在MSB中输入最高位,在LSB中输入最低位,比如是8位宽的总线,则在MSB中写7,LSB中写0(PS:这里我用一个之前写的小程序举例子,一个并串转换器,输入有两路,一路是奇数1、3、5、7、9等,一路是偶数2、4、6、8、10等,然后让输出是1、2、3、4、5等,这里我将采取调用IP核的方式,IP核就是ISE封装好的器件,就跟matlab 的内置函数差不多,我们设定好它的参数后直接例化调用它就好了,就不用再自己写了)设置好后点击Next,然后点击Finish即可从这里我们可以看到,刚才设置的参数ISE已经帮我们设置好了,接下来我们开始调用IP 核D、调用IP核,右击practice文件名,选择new source(PS:因为IP核是隶属于verilog 文件的,所以要在文件中添加IP核,这里的隶属关系一定要搞懂!!!)选择那个大灯泡,就是IP核了,同样只需要起名字就行了,不用管位置,名字最好用文件名加个ipcore后缀我们在这个例子中是想用两个fifo来不断的存储和输出数据,通过时钟和读写使能控制fifo实现并串转换,所以我们应该选择fifo的IP核,然后点击next不要点击generate 因为我们还有好多参数要设定这里选择读写不同时钟这里选择读写深度和读写位宽然后这里选择读满、写满等乱七八糟的东西的标志(PS:就是说这个fifo快被写满的时候就会有一个输出端口被拉高或拉低,这里根据个人需求设定,我没有用到就没有勾选)然后选择复位方式然后选择是否使用输出、输入计数端口(就是说要不要用端口来记进入和输出fifo的数据的个数,我们这个例子中并不需要记个数,所以不用勾选),然后点击generate就行了E、例化IP核,找到IP核所在的文件夹,点击左上角的打开按钮找到刚刚设定的IP核名称后缀为.v的文件(我这里是用我之前的文件了,所以是p2s_ipcore.v,如果您按照上述步骤操作这里应该会找到practice_ipcore.v)在该文件中找到下面图中的一段程序把这一段复制到之前创建的主文件中,就是practice.v的文件中的这个位置(在下图),我们发现p2s_ipcore后面多出了一个ipcore1,这个是我们在主程序中给ip核起的名字,就是说,刚才我们在创建ip核时给ip核起的名字是这个ip核在系统中的名字而不是在我们将要编程的文件中的名字,就像在学校别人都叫我们大名,但是在家里父母叫我们小名一样,然后我们也发现上图中的端口名称在下图中也被我们替换掉了,因为我们要给这个fifo输入,并控制它的输出,上图中的端口名只是告诉我们这些端口都是做什么作用,我们肯定是要用我们定义的端口来替换它的,对于不用的端口悬空就行了,比如empty端口我们就没用,悬空就行了,在下图中我们直接把empty删掉了,但是逗号千万不能删,这里有点难理解,您不懂的地方可以随时问我。

ModelSim之命令行仿真入门

ModelSim之命令⾏仿真⼊门下⾯是我们的Tcl仿真步骤:启动ModelSim SE, ⾸先看到在在ModelSim SE右边的窗⼝有ModelSim> 这样的提⽰符。

在提⽰符后,顺序运⾏以下命令:vlib work 该命令的作⽤是在该⽬录下建⽴⼀个work⽬录,请注意不要⽤操作系统来新建⼀个work的⽂件夹,因为⽤操作系统建⽴的work ⽂件夹并没有ModelSim SE⾃动⽣成的_info⽂件。

vmap work work 该命令的作⽤是将⽬前的逻辑⼯作库work和实际⼯作库work映射对应。

vlog camera.v camera_tb.v 该命令的作⽤是编译这些⽂件,要注意的是⽂件可以单独分开编译,但是⼀定要先编译被调⽤的⽂件。

假如是VHDL⽂件就可以⽤vcom file1,file2命令来编译。

vsim camera_tb 仿真命令, 注意后⾯的参数必须为camera_tb.v⽂件中的模块名。

add wave/camera_tb/ * 该命令的作⽤是将testbench⽂件camera_tb.v中模块camera_tb下所有的信号变量加到波形⽂件中去,注意在“*”前要加空格。

这时候你也可以看到wave⽂件被打开。

当然也可以单个信号的添加,例如添加时钟:add wave clk 等等。

run 2000 该命令的作⽤是运⾏2000个单位时间的仿真。

也可以⽤run –all命令来⼀直仿真下去。

这时候就可以在wave窗⼝⽂件中看到你的仿真结果。

当然也可以观察其它窗⼝的结果,⽤view命令显⽰view * 观察包括signals、wave、dataflow等窗⼝⽂件。

也可以分别打开。

例如⽤view signals来观察信号变量。

quit -f/-force/-sim 该命令分别是退出ModelSim(-f/-force)和退出仿真(-sim)。

ModelSim SE6..2b还有⼀个很好⽤的功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

WILDSCModelsimSE仿真教程Verilog & VHDL孙玉阳2014/6/3对于ModelsimSE仿真设置网上很难找到详细教程,在此写一篇基于Verilog 和VHDL的ModelsimSE的仿真设置教程,以期缩短大家ModelsimSE学习时间,由于时间仓促,不足之处还请见谅。

目录1 ModelsimSE仿真——Verilog HDL (2)1.1 建立资源库 (2)1.1.1 建立资源库的目的 (2)1.1.2 建立资源库前准备 (2)1.1.3 建立资源库的步骤 (3)1.2 功能仿真 (11)1.2.1 建立ModelsimSE工程 (11)1.2.2 添加Quartus工程文件 (12)1.2.3 编译 (14)1.2.4 仿真 (18)1.3 时序仿真 (21)2 ModelsimSE仿真——VHDL (25)2.1 建立资源库 (25)2.1.1 建立资源库的目的 (25)2.1.2 建立资源库前准备 (25)2.1.3 建立资源库的步骤 (26)2.2 功能仿真 (33)2.2.1 建立ModelsimSE工程 (33)2.2.2 添加Quartus工程文件 (34)2.2.3 编译 (37)2.2.4 仿真 (40)2.3 时序仿真 (44)1ModelsimSE仿真——Verilog HDL1.1建立资源库1.1.1建立资源库的目的Quartus Verilog工程文件里面在使用Primitives、Megafunction、LPM等Quartus自带模块时,会调用Quartus本身自带的一些库文件,但是ModelsimSE在仿真Quartus Verilog工程文件时不会自动去调用Quartus的库文件,同时ModelsimSE也不自带与Primitives、Megafunction、LPM相关的库文件。

所以在仿真Primitives、Megafunction、LPM等模块时,必须在ModelsimSE里建立与其对应的资源库,否则无法仿真。

1.1.2建立资源库前准备(备注:若需要后仿真(时序仿真)则进行这一步骤,若只进行前仿真(功能仿真)则跳过此步骤):打开待仿真的quartus工程,点击菜单Assignments->Settings,打开如下窗口将以下红色部分设置好,先点击apply,然后点击OK即可然后会发现quartus工程里多了个simulation文件夹,打开改文件夹simulation->modelsim,会发现里面有很多.VO和.SDO文件。

1.1.3建立资源库的步骤1.1.3.1建立文件夹首先在modelsimSE的安装目录下(比如,如果安装在C盘,则安装目录为C:\modeltech_10.0c)建立两个空文件夹文件名分别为altera_base_v,altera_device(这个名字最好就命名为这两个)。

1.1.3.2建立库altera_base_v打开modelsimSE,注意此时不要打开任何工程,如若已经打开modelsimSE工程,点击菜单file->change directory ,然后随便指定一个文件夹,将工程关掉。

下面开始建立lpm资源库,首先新建一个library,方法是打开菜单file->new->library,出现如下图所示窗口,按下图所示窗口填好,注意:Library Physical Name应该指向的是上一节所建立的altera_base_v文件夹。

点击OK之后,回到modelsim界面,会发现多出了altera_base_v (empty)库,现在这个库里什么都没有,下面往里面添加内容。

打开菜单Compile->Compile..,弹出如下界面:注意下图设置,Library一定要选择刚刚新建的altera_base_v库,查找范围则是在quartus 的安装目录下,在quartus的安装目录中找到sim_lib文件夹,比如我的quartus安装在C盘,则查找路径为C:\altera\11.0\quartus\eda\sim_lib。

为了建立altera_base_v库,需要编译3个文件,分别是220model.v,altera_mf.v,altera_primitives.v,这三个文件分别对应Quartus中的LPM库、Megafunction库、Primitiv库。

同时选中者三个文件,点击Compile,编译完之后点击Done。

此时发现刚刚新建的altera_base_v库前面出现了“+”号,说明里面已经有东西了,如下图所示:1.1.3.3建立库altera_device建立库altera与建立库altera_base_v的流程是一样的,首先新建一个library,方法是打开菜单file->new->library,出现如下图所示窗口,按下图所示窗口填好,注意:Library Physical Name应该指向的是上一节所建立的altera_device文件夹。

点击OK之后,回到modelsim界面,会发现多出了altera_device (empty)库,现在这个库里什么都没有,下面往里面添加内容。

打开菜单Compile->Compile..,弹出如下界面:注意下图设置,Library一定要选择刚刚新建的altera_device库,查找范围则是在quartus 的安装目录下,在quartus的安装目录中找到sim_lib文件夹,比如我的quartus安装在C盘,则查找路径为C:\altera\11.0\quartus\eda\sim_lib。

为了建立altera_device库,需要编译1个文件cycloneive_atoms.v(用什么型号的FPGA 选择什么名称的文件,这里用的FPGA是cycloneive),选中cycloneive_atoms.v后,点击Compile ,编译完之后点击Done,此时发现刚刚新建的altera_device库前面出现了“+”号,说明里面已经有东西了,如下图所示:1.1.3.4更改ModelsimSE的配置文件两个资源库altera_base_v,altera_device编译完成之后还没有结束,我们还需要改一下ModelsimSE的配置文件,配置文件在ModelsimSE的安装目录下(C:\modeltech_10.0c),文件名为modelsim.ini,在更改modelsim.ini时,最好先备份一下吧,防止不甚改错掉。

用记事本打开modelsim.ini(如果用记事本打开内容很乱,就用写字板打开吧),找到[Library],在后面添加如下图所示的两行命令,指定Library所在的位置,注意每一行命令一定要以回车结尾。

(modelsim.ini是只读文件,首先去掉只读才能更改)关闭ModelsimSE 软件,重新打开,会发现ModelsimSE 中的库多了以下两条,如果找不到这两条,证明库没有添加成功,检查modelsim.ini更改是否正确。

(注意:若是打开之前建立的ModelsimSE工程,则还是不会出现这两个库)1.2功能仿真1.2.1建立ModelsimSE工程打开ModelsimSE菜单file->new->Project,会出现下图对话框:Project Name既是所要建立的工程名,Project Location为工程存放的位置,Default Library Name既是工作库的名字,一般默认为work,不要去改这个名字。

一个ModelsimSE 工程只有一个工作库,很多个资源库,之前建立的altera_base_v,altera_device就是资源库。

1.2.2添加Quartus工程文件Quartus工程文件的结构如下如所示:这里建议把所有的模块名称都换为小写,理由如下:如果lpm_latch_12中有一个字母是大写,在将dsp_fpga_register.bdf生成dsp_fpga_register.v文件时,就会多生成lpm_latch_12_0.v、lpm_latch_12_1.v、…、lpm_latch_12_29.v共30个文件,这样子仿真往往会没有输出结果,如果是小写,就不会有这30个文件,所以在建立Quartus工程时,建议所有的模块名称全部改为小写。

由于ModelsimSE不能对BDF文件进行仿真,必须把BDF文件转换为verilog文件,只要选中BDF文件,在Quartus中选中菜单File->create/Update->create HDL Design file from current file即可。

在ModelsimSE中,如下图所示,选中红框出然后右击空白处,选择Add to Project –> Existing File,电机Browse..选择Quartus中对应的文件。

由上面的Quartus工程文件结构可以发现Quartus从顶层到底层共有两层,共4个实体模块,30个lpm_latch_12模块是同一个实体模块的复制,所以只能算一个,那么ModelsimSE中共需导入4个文件,如下图所示:这四个文件少一个都不行,多了也是不对的。

注意上图的蓝色问号了吧,这是由于ModelsimSE还没有对着四个文件进行编译。

下面新建testbench测试文件,在ModelsimSE中,如下图所示,选中红框出然后右击空白处,选择Add to Project –>New File,注意红框出选择Verilog,点击ok即可。

至于testbench文件如何编写,这里就不做详细叙述了,否则篇幅太大了。

这里只说一个建议吧,testbench文件中signal的名称是可以和Quartus顶层实体输入输出信号的名称一样的,如下图至此,ModelsimSE工程中该添加的文件都添加完了,下面就是编译仿真了。

1.2.3编译由于Quartus里调用了primitives库,所以ModelSimSE里也必须调用我们之前做的库,调用设置如下:在ModelSimSE里打开菜单Simulate->start simulation,打开如下图所示窗口:选择 Libraries,然后Add..,然后点击下拉箭头(注意不要选择Browse..,选择旁边的下拉箭头即可)。

添加如下图所示的两个库,点击OK即可。

在ModelsimSE中右击上一节添加的文件,点击Compile->Compile all编译所有的五个文件,编译通过后,蓝色的问号会全部变为绿色的对号,同时Transcript中也会显示0 failed 0 error,如下面两图:此时点击Library,展开work,会有一系列的实体名出现,这些实体名既是我们Quartus 中的实体名。