第三章逻辑门电路

《逻辑门电路》PPT课件

b

电子,形成电流ICN R b

P N I E N I E P

VC C

➢另外,集电结区的少 V B B

数载流子形成漂移电流

e IE

ICBO

两种载流子参与导电——双极性晶体管Bipolar Junction Transistor

2021-09-22

中国科学技术大学 快电子 刘树彬

17

BJT的开关工作状态

《逻辑门电路》PPT课件

本课件PPT仅供大家学习使用 学习完请自行删除,谢谢! 本课件PPT仅供大家学习使用 学习完请自行删除,谢谢! 本课件PPT仅供大家学习使用 学习完请自行删除,谢谢! 本课件PPT仅供大家学习使用 学习完请自行删除,谢谢!

第三章 逻辑门电路

3.1 MOS逻辑门电路 3.2 TTL逻辑门电路 3.3 射极耦合门电路 3.5 逻辑描述中的几个问题 3.6 逻辑门电路使用中的几个实际问题

7

N型半导体

在本征半导体中掺入五价杂质元素,如磷、砷等

硅原子 + 4

多余电子

+4

磷原子

+4

+4

+4

电子空穴对 自由电子

N型半导体

+5 +4

++ + + ++ + +

+3;

2021-09-22

多数载流子——自由电子 少数载流子—— 空穴

中国科学技术大学 快电子 刘树彬

施主离子

8

PN结

2021-09-22

中国科学技术大学 快电子 刘树彬

t1

t

IFVFR LVDV RF L

0.1IR t

第三章 逻辑门电路

数字集成电路构成了各种逻辑电路,如各种门电路、编译码器、 触发器、计数器、寄存器等。

CMOS电路相比于TTL,具有功耗低、工作电压范围宽、抗干扰能力强等优点。

最常用的TTL电路是74LS/HC等系列,使用5V的电压逻辑“0”输出电压为小于等于0.2V,逻辑“1”输出电压约为3V。通常CMOS集成电路工作电压范围为3-18V,所以不必像TTL电路那样,要用正好的5V电压。CMOS集成电压的输入电阻很高,这意味着驱动CMOS集成电路时,所消耗的驱动功率几乎可以不计。同时CMOS集成电路的耗电也非常的省,用CMOS集成电路制作的电子产品,通常都可以用于干电池供电通常用于生产RAM和交换应用系统,在计算机领域里通常指保存计算机基本启动信息(如日期、时间、启动设置等)的ROM芯片。BiCMOS成为射频电路中用得最多的工艺技术。它结合双极性集成电路BJT的高速性能和高驱动能力,以及CMOS的高密度,低功耗和低成本等优点,既可用于数字集集成电路,也可用于模拟集成电路。

延时功耗积

扇入与扇出数

扇入数:取决于逻辑门的输入端的个数。

扇出数:是指其在正常工作情况下,所能带同类门电路的最大数目。

扇出数的计算分两种情况: (a)拉电流和(b)灌电流

(a)带拉电流负载(高电平输出)

高电平扇出数:

(b)带灌电流负载(低电平输出)

特别要说明的是,源极在MOSFET里的意思是“提供多数载子的来源”。对NMOS而言,多数载流子是电子;对PMOS而言,多数载流子是电洞(空穴)。相对的,汲极(集电极)就是接受多数载流子的端点。

N沟道增强型MOSFET

结构(N沟道)

P沟道MOSFET

JFET的结构和工作原理

输入端的数目越多,则串联的管子也越多;

数字电路基础知识

第三章 数字电路基础知识1、逻辑门电路(何为门)2、真值表3、卡诺图4、3线-8线译码器的应用5、555集成芯片的应用一. 逻辑门电路(何为门)在逻辑代数中,最基本的逻辑运算有与、或、非三种。

每种逻辑运算代表一种函数关系,这种函数关系可用逻辑符号写成逻辑表达式来描述,也可用文字来描述,还可用表格或图形的方式来描述。

最基本的逻辑关系有三种:与逻辑关系、或逻辑关系、非逻辑关系。

实现基本逻辑运算和常用复合逻辑运算的单元电路称为逻辑门电路。

例如:实现“与”运算的电路称为与逻辑门,简称与门;实现“与非”运算的电路称为与非门。

逻辑门电路是设计数字系统的最小单元。

1.1.1 与门“与”运算是一种二元运算,它定义了两个变量A 和B 的一种函数关系。

用语句来描述它,这就是:当且仅当变量A 和B 都为1时,函数F 为1;或者可用另一种方式来描述它,这就是:只要变量A 或B 中有一个为0,则函数F 为0。

“与”运算又称为逻辑乘运算,也叫逻辑积运算。

“与”运算的逻辑表达式为:F A B =⋅ 式中,乘号“.”表示与运算,在不至于引起混淆的前提下,乘号“.”经常被省略。

该式可读作:F 等于A 乘B ,也可读作:F 等于A 与B 。

由“与”运算关系的真值表可知“与”逻辑的运算规律为:00001100111⋅=⋅=⋅=⋅= 表2-1b “与”运算真值表简单地记为:有0出0,全1出1。

由此可推出其一般形式为:001A A AA A A⋅=⋅=⋅=实现“与”逻辑运算功能的的电路称为“与门”。

每个与门有两个或两个以上的输入端和一个输出端,图2-2是两输入端与门的逻辑符号。

在实际应用中,制造工艺限制了与门电路的输入变量数目,所以实际与门电路的输入个数是有限的。

其它门电路中同样如此。

1.1.2 或门“或”运算是另一种二元运算,它定义了变量A 、B 与函数F 的另一种关系。

用语句来描述它,这就是:只要变量A 和B 中任何一个为1,则函数F 为1;或者说:当且仅当变量A 和B 均为0时,函数F 才为0。

数字逻辑第3章 门电路

逻辑式:Y=A + B

逻辑符号: A 1

B

Y

电压关系表

uA uB uY

0V 0V 0V 0V 3V 2.3V 3V 0V 2.3V 3V 3V 2.3V

真值表

ABY

0

0

0

0

1

1

1

0

1

1

1

1

三、三极管非门

5V

利用二极管的压降为0.7V, 保证输入电压在1V以下时,

电路可靠地截止。

A(V) Y(V) <0.8 5 >2 0.2

II H &

II L &

… …

NOH

I OH (max) I IH

N MIN ( NOH , NOL )

NOL

IOL(max) I IL

六、CMOS漏极开路门(OD)门电路(Open Drain)

1 . 问题的提出

普通门电路

在工程实践中,往往需要将两个门的输出端 能否“线与”?

并联以实现“与”逻辑功能,称为“ 线与 。

输入 0 10% tr tf

tPHL

输出

tPLH

tr:上升时间

tf:下降时间 tw:脉冲宽度 tPHL:导通传输时间

tPLH:截止传输时间

平均传输延迟时间 (Propagation delay)

tpd= tpHL+ tpLH 2

5、功耗: 静态功耗:电路的输出没有状态转换时的功耗。 动态功耗:电路在输出发生状态转换时的功耗。

PMOS

NMOS

3、增强型MOSFET的开关特性

iD管可变子类型恒

VGS1 击开/关的条(件1)N沟道增强开型/M关O的S等FE效T电:路

第三章逻辑门电路

4.74S系列——为肖特基TTL系列,进一步提高了速度。如图示。

5.74LS系列——为低功耗肖特基系列。 6.74AS系列——为先进肖特基系列,

它是74S系列的后继产品。

7.74ALS系列——为先进低 功耗肖特基系列,

t

50%

主要取决于存储时间ts, 5管门电路 tpd=40ns

o tpHL tpLH

t

4、功耗

静态功耗:当电路的输出没有状态转换时的 功耗。 例如:便携计算机、手机和PDA等。 动态功耗:CMOS电路在输出发生状态转换时的 功耗。

5、延时——功耗积

Dp tpdPD

tpd=(tPLH+tPHL)/2用平均传输延迟时间, tPLH---由低电平转换到高电平所花的时间.

SN (1)

74 (2)

S (3)

195 (4)

J 封装的4位并行移位寄存器 (5)

司制造的采用陶瓷双列直插

封装形式 J:陶瓷双列直插封装 器件种类:4位并行移位寄存器 器件系列:肖特基74TTL电路系列 产品系列 74系列 制造厂商 SN:美国TEXAS公司制造

TTL集成逻辑门电路系列简介

1.74系列——为TTL集成电路的早期产品,属中速TTL器件。

输入电压在3.5V~5.0V范围对应高电平逻辑1 输入电压在0~1.5V范围对应低电平逻辑0

输入低电平上限VIL、输入高电平下限VIH、 输出低电平上限VOL、输出高电平下限VOH、

2.噪声容限

1

VOH(min) VNH VIH(min) VIL(max) VNL

1

在保证输出高、低电平基本不变 的条件下,输入电平的允许波动 范围称为输入端噪声容限。

数字电路教案-阎石-第三章-逻辑门电路

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路.用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态.在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL电路).另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

3。

2 分立元件门电路3。

3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点工作状态截止放大饱和条件i B=0 0<i B<I BS i B>I BS工作特点偏置情况发射结反偏集电结反偏u BE〈0,u BC〈0发射结正偏集电结反偏u BE>0,u BC〈0发射结正偏集电结正偏u BE〉0,u BC〉集电极电流i C=0 i C=βi B i C=I CSce间电压u CE=V CC u CE=V CC-i C R cu CE=U CES=0.3Vce间等效电阻很大,相当开关断开可变很小,相当开关闭合3.2。

3二极管门电路1、二极管与门2、二极管或门u A u B u Y D1D20V 0V 0V 5V 5V 0V 5V 5V0V4。

3V4。

3V4.3V截止截止截止导通导通截止导通导通3。

2.4三极管非门3。

2。

5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

数电第三章讲解

起低阻通道,形成较大的 脉冲电流。 不仅增加了CMOS电路的 功耗,而且也成为CMOS 电路的内部干扰源。

22

3. CMOS反相器的输入特性

由于信号从栅极输入, 输入电阻很大,又有一个小的寄生电容, 如果输入端没有保护电路, 输入端可能被静电感应充电至高压, 造成绝缘栅击穿,使器件永久损坏。 为避免造成栅极击穿, 实际的CMOS集成电路的每一个输入端都设有输入保

第3章 集成逻辑门电路

3.1 概述

逻辑门电路(门电路): 用来实现基本逻辑关系的电子电路 集成逻辑门电路: 将若干个逻辑门电路集成在一块半导体材料基片上

1

集成逻辑门电路有两种类型器件:

(1)由三极管组成的双极型集成电路

例如:晶体管-晶体管逻辑电路 (简称TTL:Transistor-Transistor Logic)

和增强型NMOS驱动管(TN) 串联组成

11

TP的开启电压VGS(th)P < 0 TN的开启电压VGS(th)N > 0 电路正常工作的条件: VDD >∣VGS(th)P∣+ VGS(th)N,

且VGS(th)N =∣VGS(th)P∣, TN和TP具有相同的导通电阻

Ron和截止电阻Roff。

12

2.工作原理

当输入为低电平时: TN的VGSN = 0 v < VGS(th)N 管子截止。 TP的∣VGSP ∣= VDD 管子导通, 输出为高电平VOH vO =VOH≈VDD

13

当输入为高电平VDD时

TN的VGSN = VDD >VGS(th)N, 管子导通。 TP的VGSP = 0 v > VGS(th)P 负载管截止。 输出为低电平VOL, vO =VOL≈0 v。

23逻辑门电路

二极管相当于一个闭合的开关。

D

V

F

IF

RL

(a )

K

V

F

IF

RL

(b)

3

(2)加反向电压VR时,二极管截止,反向电流IS可忽略。

二极管相当于一个断开的开关。

D

V

R

IS

RL

K

V

R

RL

(a )

(b)

可见,二极管在电路中表现为一个受外加电压vi控制的开 关。当外加电压vi为一脉冲信号时,二极管将随着脉冲 电压的变化在“开”态与“关”态之间转换。这个转换

R c2

R c4

R b1

1.6kΩ

130Ω

4kΩ

V c2

1

3

T2 4

1

3

A

31

2T 2

D Vo

B

T1

C

Ve2

1

3

2T 3

R e2

1kΩ

输入级

中间级

输出级

22

2.TTL与非门的逻辑关系

(1)输入全为高电平3.6V时。

T2、T3导通,VB1=0.7×3=2.1(V ),

由于T3饱和导通,输出电压为:VO=VCES3≈0.3V

30

四、TTL与非门的带负载能力

1.输入低电平电流IIL与输入高电平电流IIH

(1)输入低电平电流IIL——是指当负载门电路的输入端

接低电平时,从负载门电路输入端流出的电流。

+VCC (+5V)

+VCC (+5V)

D1 0V

D2 5V

R 3kΩ

数电第三章门电路

§3.4 TTL门电路

数字集成电路:在一块半导体基片上制作出一个 完整的逻辑电路所需要的全部元件和连线。 使用时接:电源、输入和输出。数字集成电 路具有体积小、可靠性高、速度快、而且价 格便宜的特点。

TTL型电路:输入和输出端结构都采用了半导体晶 体管,称之为: Transistor— Transistor Logic。

输出高电平

UOH (3.4V)

u0(V)

UOH

“1”

输出低电平

u0(V)

UOL

UOL (0.3V)

1

(0.3V)

2 3 ui(V)

1 2 3 ui(V)

阈值UT=1.4V

传输特性曲线

理想的传输特性 28

1、输出高电平UOH、输出低电平UOL UOH2.4V UOL 0.4V 便认为合格。 典型值UOH=3.4V UOL 0.3V 。

uA t

uF

截止区: UBE< 死区电压, IB=0 , IC=ICEO 0 ——C、 E间相当于开关断开。

+ucc

t

4

0.3V

3.2.3MOS管的开关特 恒流区:UGS>>Uth , UDS

性: +VDD

0V ——D、S间相当于 开关闭合。

R

uI

Uo

Ui

NMO S

uO

夹断区: UGS< Uth, ID=0 ——D、S间相当于开关断开。

3.3.4 其它门电路

一、 其它门电路

其它门电路有与非门、或非门、同或门、异或门等等,比如:

二、 门电路的“封锁”和“打开”问题

A B

&

Y

C

当C=1时,Y=AB.1=AB

数字电子技术基础第三章逻辑门电路

数字电子技术基础第三章逻辑门电路

第一节 常见元器件的开关特性

3.MOS管的开关特性

A、MOS管静态开关特性

在数字电路中,MOS管也是作为 开关元件使用,一般采用增强型的 MOS管组成开关电路,并由栅源电压 uGS控制MOS管的导通和截止。

时间。

toff = ts +tf 关断时间toff:从输入信号负跃变的瞬间,到iC 下降到 0.1ICmax所经历的时间。

数字电子技术基础第三章逻辑门电路

第一节 常见元器件的开关特性

2.三极管的开关特性

B、晶体三极管动态开关特性

ton和toff一般约在几十纳秒(ns=10-9 s)范围。通常都

有toff > ton,而且ts > tf 。

0 .3V 3 .6V 3 .6V

1V 5V

3 .6V

数字电子技术基础第三章逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

1.TTL集成逻辑门电路

3 .6V 3 .6V 3 .6V

2.1V

0 .3V

数字电子技术基础第三章逻辑门电路

第三节 TTL和CMOS集成逻辑门电路

1.TTL集成逻辑门电路

数字电子技术基础第三章逻辑门电路

❖ 2.教学重点:不同元器件的静态开关特性,分立元件门电路 和组合门电路,TTL和CMOS集成逻辑门电路基本功能和电气特 性。

❖ 3.教学难点:组合逻辑门电路、TTL和CMOS集成逻辑门4.课时 安排: 第一节 常见元器件的开关特性 第二节 基本逻辑门电路 第三节 TTL和CMOS集成逻辑门电路

数电-第三章逻辑门电路

了解和掌握常见时序逻辑电路的原理和应用,如寄存器、 计数器、顺序脉冲发生器等。

可编程逻辑器件应用

1 2

可编程逻辑器件简介

了解可编程逻辑器件的基本概念和分类,如PAL、 GAL、CPLD、FPGA等。

可编程逻辑器件编程

学习使用相应的开发工具和编程语言,对可编程 逻辑器件进行编程和配置,实现特定的逻辑功能。

典型组合逻辑电路

了解和掌握常见组合逻辑电路的 原理和应用,如编码器、译码器、

数据选择器、比较器等。

时序逻辑电路分析与设计

时序逻辑电路分析

分析时序逻辑电路的工作原理,包括触发器的状态转换、 时钟信号的作用等,进而理解电路的功能。

时序逻辑电路设计

根据实际需求,设计实现特定功能的时序逻辑电路。包括 确定输入、输出变量,选择适当的触发器类型,画出状态 转换图或时序图等步骤。

数电-第三章逻辑门 电路

• 逻辑门电路基本概念 • 基本逻辑门电路 • 复合逻辑门电路 • 逻辑门电路应用 • 逻辑门电路实验与仿真 • 逻辑门电路总结与展望

目录

Part

01

逻辑门电路基本概念

逻辑门定义与分类

逻辑门定义

逻辑门是数字电路中的基本单元 ,用于实现基本的逻辑运算功能 ,如与、或、非等。

逻辑符号为带有小圆圈的与门符号。

或非门电路

01

02

03

或非门逻辑功能

实现输入信号的逻辑或操 作,并取反输出结果。

或非门符号

逻辑符号为带有小圆圈的 或门符号。

或非门真值表

输入全为0时,输出为1; 输入有1时,输出为0。

异或门电路

异或门逻辑功能

实现输入信号的异或操作, 即输入信号相同时输出为0, 不同时输出为1。

数字电子技术基础:第三章 逻辑门电路

逻辑符号

C

vI /vO

TG

vO /vI

C

C

υo/ υI

2. CMOS传输门电路的工作原理

vI /vO

5V到+5V

C

+5V

TP +5V vO /vI

5V TN

5V

C

设TP:|VTP|=2V, TN:VTN=2V

I的变化范围为-5V到+5V。

c=0=-5V, c =1=+5V

1)当c=0, c =1时 GSN= -5V (-5V到+5V)=(0到-10)V

在由于电路具有互补对称的性质,它的开通时间与关 闭时间是相等的。平均延迟时间:<10 ns。

动态功耗

CMOS反相器的PD与f和 2 VDD

CMOS反相器从一个稳定状态转变到另一个稳定状态时所产生的功耗

PD=PC+PT

分布电容CL充放电引起的功耗: PC CL fVD2D

CMOS管瞬时交替导通引起的功耗:PT CPD fVD2D

74标准系列 74LS系列

74AS系列

74LVC 74VAUC 低(超低)电压 速度更加快 与TTL兼容 负载能力强 抗干扰 功耗低

74ALS

3.1 概述

门电路:实现基本逻辑/复合逻辑运算的单元电路

逻辑状态的描述—— 正逻辑:高电平→1,低电平→0 负逻辑:高电平→0,低电平→1

缺点:功耗较大/速度较慢

VDD VIH(min) I OH(total) I IH(total)

… …

I0H(total) &1

+V DD RP

&

&1

IIH(total) &

第三章 逻辑门电路

2、输入和输出的高低电压 、 ( 1 ) 输出高电平电压 VOH——在正逻辑体制中代表 在正逻辑体制中代表 逻辑“ 的输出电压 的输出电压。 的理论值为3 逻辑 “ 1”的输出电压 。 VOH 的理论值为 3.6V, , 产品规定输出高电压的最小值V ( ) 产品规定输出高电压的最小值 OH( min) =2.4V。 。

– – – – – 延迟时间td 上升时间tr r 存储时间ts 下降时间tf 开关时间:

• 开通时间ton= td + tr r • 关闭时间toff= ts + tf f • 要设法减小,提高BJT开关的运用速度

3.3 基本逻辑门电路

一、二极管与门和或门电路 1.与门电路 .

+VCC (+5V) R 3kΩ D1 A D2 B L

L = A⋅ B ⋅C

3.6V A B C 0.3V 1V

1

Rc2 R b1 4kΩ 5V

3 3 1

R c4 130Ω

3 1

1.6kΩ

T 4 导通 2 D 导通 Vo

3

4.3V 截止

1

T 22

T1 饱和 R e2 1kΩ

3.6V

T 2 3 截止

3.4.5 TTL与非门的技术参数

• 1、传输特性

– 各种类型的TTL门电路,其传输特性大同小异。

开关 断开

VF-VD (a) vi

VF

VF ≈ RL

i

IF = RL

(b) 0

-VR

t1

t

i

IF

通常把二极管从正 向导通转为反向截止 所经过的转换过程称 为发向恢复过程。 ts 存储时间 tt 渡越时间 ts+tt 反向恢复时间 VR IR = RL

第3章集成逻辑门电路

22

PN结的形成

由空间电荷区产生的、方向为N区指向P区 的内建电场阻碍了扩散运动,同时使少子产生 漂移运动,即N区的空穴向P区漂移, P区的电 子向N区漂移。

当漂移运动和扩散运动达到动态平衡时, 扩散电流等于漂移电流且方向相反,PN结中电 流为零,PN结宽度及电位差Uho为恒定值。

PN结的形成由两个运动共同形成:多子的 扩散运动和少子的漂移运动。

19

PN结的形成

多子扩散

P区

空间电荷区

N区

内电场方向

20

PN结的形成

空间电荷区

P区

N区

多子扩散 内电场方向 少子漂移

21

PN结的形成

由于载流子的浓度差,P区的空穴向N区 扩散,N区的电子向P区扩散。这种由于浓 度差引起的运动称为扩散运动。

双极型电路的缺点:功耗大。

应用领域:SSI,MSI。

5

3.1 概述

随着集成规模的增加,LSI,VLSI的出现,TTL 已不能适用,CMOS电路(单极型)得到了广泛的 使用。CMOS电路的最大优点:功耗低。随着技术 的发展,速度和驱动能力和TTL基本相同。

在单极型电路中,还包括NMOS和PMOS等。

23

PN结的形成

P区

P N结

N区

内电场方向

室温下,内电场建立的电位差: 硅:(0.6~0.8)V 锗:(0.1 ~0.3)V 24

PN 结的单向导电性

所谓“单向导电性”是指PN结在不同极性 外加电压作用下,其导电能力有极大差异的 特性。PN结最显著的特性为单向导电性。

第3章-逻辑门电路

3 逻辑门电路MOS 逻辑门电路3.1.2 求下列情况下TTL 逻辑门的扇出数:(1)74LS 门驱动同类门;(2)74LS 门驱动74ALS 系列TTL 门。

解:首先分别求出拉电流工作时的扇出数N OH 和灌电流工作时的扇出数N OL ,两者中的最小值即为扇出数。

从附录A 可查得74LS 系列电流参数的数值为I OH =,I OL =8mA ,I IH =,I IL =;74ALS 系列输入电流参数的数值为I IH =,I IL =,其实省略了表示电流流向的符号。

(1) 根据(3.1.4)和式()计算扇出数74LS 系列驱动同类门时,输出为高电平的扇出数0.4200.02OH OH IH I mA N I mA=== 输出为低电平的扇出数 8200.4OL OL IL I mA N I mA ===所以,74LS 系列驱动同类门时的扇出数N O 为20。

(2) 同理可计算出74LS 系列驱动74ALS 系列时,有0.4200.02OH OH IH I mA N I mA=== 8800.1OL OL IL I mA N I mA === 所以,74LS 系列驱动74ALS 系列时的扇出数N O 为20。

3.1.4 已知图题所示各MOSFET 管的T V =2V ,忽略电阻上的压降,试确定其工作状态(导通或截止)。

解:图题3.1.4(a )和(c )的N 沟道增强型MOS ,图题(b )和(d )为P 沟道增强型MOS 。

N 沟道增强型MOS 管得开启电压V T 为正。

当GS V <V T 时,MOS 管处于截止状态;当GS V ≥V T ,且DS v ≥(GS V —V T )时,MOS 管处于饱和导通状态。

对于图题3.1.4(a ),GS V =5V ,DS v =5V ,可以判断该MOS 管处于饱和导通状态。

对于图题3.1.4(c ),GS V =0V <V T ,所以MOS 管处于截止状态。

第三章 逻辑门电路

第三章逻辑门电路[题3.1] 选择题1. 三态门输出高阻状态时,是正确的说法。

A.用电压表测量指针不动B.相当于悬空C.电压不高不低D.测量电阻指针不动2. 以下电路中可以实现“线与”功能的有。

A.与非门B.三态输出门C.集电极开路门D.漏极开路门3.以下电路中常用于总线应用的有。

A.TS L门B.O C门C.漏极开路门D.CM OS与非门4.三极管作为开关使用时,要提高开关速度,可。

A.降低饱和深度B.增加饱和深度C.采用有源泄放回路D.采用抗饱和三极管5.T TL电路在正逻辑系统中,以下各种输入中相当于输入逻辑“1”。

A.悬空B.通过电阻 2.7kΩ接电源C.通过电阻 2.7kΩ接地D.通过电阻510Ω接地6.对于T T L与非门闲置输入端的处理,可以。

A.接电源B.通过电阻3kΩ接电源C.接地D.与有用输入端并联7.C MO S数字集成电路与TT L数字集成电路相比突出的优点是。

A.微功耗B.高速度C.高抗干扰能力D.电源范围宽8.逻辑表达式Y=AB可以用实现。

A.正或门B.正非门C.正与门9.要使TTL与非门工作在转折区,可使输入端对地外接电阻R I。

A.>R ONB.<R OFFC.R OFF<R I<R OND.>R OFF10.与CT4000系列相对应的国际通用标准型号为。

A.CT74S肖特基系列B. CT74LS低功耗肖特基系列C.CT74L低功耗系列D. CT74H高速系列[题3.2] 判断题(正确打√,错误的打×)1.TTL与非门的多余输入端可以接固定高电平。

()2.当TTL与非门的输入端悬空时相当于输入为逻辑1。

()3.普通的逻辑门电路的输出端不可以并联在一起,否则可能会损坏器件。

()4.CMOS OD门(漏极开路门)的输出端可以直接相连,实现线与。

()5.CMOS或非门与TTL或非门的逻辑功能完全相同。

()6.三态门的三种状态分别为:高电平、低电平、不高不低的电压。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MOS管是金属(metal)—氧化物(oxid)—半导体(semiconductor)场 效应晶体管,利用电场效应来控制其电流大小的半导体器件。

MOS管分类

PMOS管: 结构简单,工作速度低,负电源工作。 NMOS管: 工艺复杂,正电源工作。 CMOS管: PMOS管和NMOS管组成互补电路。

2020/11/23

28

N增强型MOS管输出特性

2020/11/23

29

MOS开关及其等效电路

对应一定的电压范围,而不是一个固定值。当逻辑电路的 输入信号在一定范围内变化时,输出电压并不会改变。

2020/11/23

12

2. 噪声容限

噪声容限表示门电路的抗干扰能力,指在保证输出电平不变的条 件下,输入电平允许波动的范围。

负载门输入高电平时的噪声容限: VNH —当前级门输出高电平的最小值

时允许负向噪声电压的最大值。

第三章 逻辑门电路

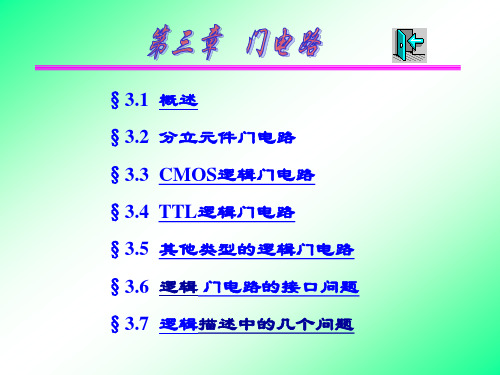

➢ 3.1 MOS逻辑门电路 ➢ 3.2 TTL逻辑门电路 ➢ 3.5 逻辑描述中的几个问题 ➢ 3.6 逻辑门电路使用中的几个实际问题

2020/11/23

1

3.1 MOS逻辑门电路

➢ 3.1.1 数字集成电路简介 ➢ 3.1.2 逻辑电路的一般特性 ➢ 3.1.3 MOS开关及其等效电路 ➢ 3.1.4 CMOS反相器 ➢ 3.1.5 CMOS逻辑门电路 ➢ 3.1.6 CMOS漏极开路门和三态输出门电路 ➢ 3.1.7 CMOS传输门 ➢ 3.1.8 CMOS逻辑门电路的技术参数 ➢ 3.1.9 NMOS门电路

扇出数:是指其在正常工作情况下,所能带同类门电路 的最大数目。 扇出数的计算分两种情况: (a)拉电流和(b)灌电流

2020/11/23

16

(a)带拉电流负载(高电平输出)

当驱动门的输出端为高电平时,将有电流IOH从驱动门拉出而流入负载门, 负载门的输入电流为IIH,当负载门的个数增加时,总的拉电流将增加, 会引起输出高电压的降低。但不得低于输出高电平的下限值,这就限制 了负载门的个数。

2020/11/23

2

3.1.1 数字集成电路简介

1 、逻辑门:实现基本逻辑运算和复合逻辑运算的单元电路, 如与门,与非门,或门等等。门电路中以高/低电平表示逻辑 状态的1/0。

2、 逻辑门电路的分类 分立门电路

逻辑门电路 集成门电路

二极管门电路

三极管门电路 NMOS门 MOS门电路 PMOS门

CMOS门

2020/11/23

7

CMOS电路的优势

CMOS发展比TTL晚,但是以其较高的优越性在很多场合逐 渐取代了TTL。

以下比较两者性能,大家就知道其中原因。

1. CMOS是场效应管构成,TTL为双极晶体管构成;

2. CMOS的逻辑电平范围比较大(5~15V),TTL只能 在5V下工作;

3. CMOS的高低电平之间相差比较大、抗干扰性强, TTL则相差小,抗干扰能力差;

2020/11/23

24

当VDS=0V,VGS较小时,虽然在P型衬底表面形成一层耗尽 层,但负离子不能导电。

当VDS=0V,当VGS=VT时,在P型衬底表面形成一层电子层, 形成N型导电沟道。

2020/11/23

25

当VGS>VT时, 沟道加厚, 外加较小的VDS时,ID随着 VDS迅速增加,由于沟道存在电位梯度,沟道厚度不均 匀,其形状为楔形,此时MOS管进入可变电阻区。

输入高电平的下限值 VIH(min)

输出高电平的下限值 VOH(min)

输出低电平的上限值 VOL(max)

2020/11/23

11

注意:

1. VH 和 VL都是对具体门输入/输出高、低电平电压值的要 求。

2. 在正逻辑体制中,用逻辑1和0分别表示高、低电平。 3. 高电平表示逻辑状态1,低电平表示逻辑状态0,一种状态

74LS系列

74AS系列

2020/11/23

74ALS

9

3.1.2 逻辑电路的一般特性

▪ 输入和输出的高、低电平 ▪ 噪声容限 ▪ 传输延迟时间 ▪ 功耗(静态和动态) ▪ 延时–功耗积 ▪ 扇入数与扇出数

2020/11/23

10

1. 输入和输出的高、低电平

1输出 0输出

1输入 0输入

输入低电平的上限值 VIL(max)

❖ CMOS电路相比于TTL,具有功耗低、工作电压范围宽、 抗干扰能力强等优点,工作速度也已经赶上甚至超过TTL 电路,因此几乎所有超大规模存储器以及PLD器件均采用 CMOS工艺制造,且成本较低。

2020/11/23

4

双极型集成电路

直接耦合晶体管集成电路(DCTL)

电阻-晶体管集成电路(RTL)

2020/11/23

26

2020/11/23

27

VDS增加到使VGD=VGS-VDS =VT时, 导电沟道在靠近漏极的一点刚开始出现夹断,称为预夹断。 此时的漏极电流ID 基本饱和。

VDS继续增加使VGD=VGS-VDS <VT

导电沟道夹断的区域向源极方 向延伸,对应特性曲线的饱和 区,VDS增加的部分基本降落 在随之加长的夹断沟道上, ID基本趋于不变。

氧化物半导体,是一种大规模应用于集成电路芯片制造的原料。采用 CMOS技术可以将成对的金属氧化物半导体场效应晶体管(MOSFET) 集成在一块硅片上。该技术通常用于生产RAM和交换应用系统,在计算 机领域里通常指保存计算机基本启动信息(如日期、时间、启动设置等)的 ROM芯片。

➢ CMOS由PMOS管和NMOS管共同构成,它的特点是低功耗。由于CMOS

TTL门电路

2020/11/23

3

❖ 数字集成电路产品的种类有很多种。数字集成电路构成了 各种逻辑电路,如各种门电路、编译码器、 触发器、计

数器、寄存器等。他们广泛应用在生活中的各个方面,小 至电子表,大至计算机,都是由数字集成电路构成。

❖ 从集成结构上来分,数字集成电路分为双极型电路(TTL 、ECL 、HTL等)、MOS型(PMOS 、NMOS 、CMOS )、BiMOS型(BiMOS和BiCMOS)。

输出逻 辑摆幅

/V

CT54/74 +5 10

15

TTL

CT54LS/74LS +5 7.5

2

150

1.2 2.2 3.5

15

0.4 0.5 3.5

HTL

+15 85

30

2550

7 7.5 13

CE10K系列 -5.2 2

25

ECL

CE100K系列 -4.5 0.75

40

50

0.155 0.125 0.8

74HC 74HCT

速度加快 与TTL兼容 负载能力强 抗干扰 功耗低

74VHC 74VHCT

速度两倍于74HC 与TTL兼容 负载能力强 抗干扰 功耗低

74LVC 74VAUC

低(超低)电压 速度更加快 与TTL兼容 负载能力强 抗干扰功耗低

2.TTL 集成电路: 广泛应用于中大规模集成电路

74系列

TTL系列

➢ TTL电路是晶体管-晶体管逻辑电路的英文缩写(Transistor-Transistor-Logic),是 数字集成电路的一大门类。它采用双极型工艺制造,具有高速度低功耗和品种多等 特点。 从六十年代开发成功第一代产品以来现有以下几代产品: 第一代TTL包括SN54/74系列,(其中54系列工作温度为-55℃~+125℃,74系列 工作温度为0℃~+75℃) ,低功耗系列简称LTTL,高速系列简称HTTL。 第二代TTL包括肖特基箝位系列(STTL)和低功耗肖特基系列(LSTTL)。 第三代为采用平面工艺制造的STTL(ASTTL)和低功耗STTL(ALSTTL)。由于 LSTTL和ALSTTL的电路延时功耗积较小,STTL和ASTTL速度很快,因此获得了 广泛的应用。

低电平扇出数:

N OL

I OL (驱动门) I IL (负载门)

ห้องสมุดไป่ตู้

IOL :驱动门的输出端为低电平时的电流

IIL :负载门输入端电流

2020/11/23

18

各类数字集成电路主要性能参数的比较

电路类型

电源电 压/V

传输延 迟时间

/ns

静态功耗 /mW

功耗-延迟 积/mW-ns

直流噪声容限 VNL/V VNH/V

中一对MOS组成的门电路在瞬间要么PMOS导通、要么NMOS导通、要 么都截至,比线性的三极管(BJT)效率要高得多,因此功耗很低。

➢ 相对于其他逻辑系列,CMOS逻辑电路具有以下优点:

1、允许的电源电压范围宽,方便电源电路的设计

2、逻辑摆幅大,使电路抗干扰能力强

3、静态功耗低

4、隔离栅结构使CMOS器件的输入电阻极大,从而使CMOS器件驱动 同类逻辑门的能力比其他系列强得多。

CMOS电路的静态功耗非常低,CMOS门电路有动态功

耗,动态功耗正比于转换频率和电源电压的平方。

对于TTL门电路来说,静态功耗是主要的。

2020/11/23

15

5. 延时功耗积 是速度功耗综合性的指标-延时功耗积,用符号DP表示

DPtpdPD

6. 扇入与扇出数 扇入数:取决于逻辑门的输入端的个数。

饱和型集成 二极管-晶体管集成电路(DTL)

电路

高阀值晶体管集成电路(HTL)

晶体管-晶体管集成电路(TTL)

双极型数字

集成注入集成电路(I2L)

集成电路

抗饱和型集成电路---肖特基晶体管-晶体管集成电路 (STTL)

2020/11/23

非饱和型集成电路---发射极耦合集成电路(ECL)

5

双极型集成电路