二位加法器

加法器电路设计实验报告

加法器电路设计实验报告【加法器电路设计实验报告】一、实验目的本实验的主要目标是通过实际操作,设计并实现一个基础的加法器电路,以深入理解数字逻辑电路的设计原理和工作方式。

通过对半加器、全加器以及多位加法器的设计与搭建,进一步熟悉集成门电路的应用,掌握组合逻辑电路的设计方法,并能对电路的逻辑功能进行有效的验证与分析。

二、实验原理加法器是数字系统中的基本运算单元,其核心工作原理基于二进制数的加法规则。

在最基础的层面上,一个半加器(Half Adder)用于计算两个一位二进制数的和,同时产生一个进位输出;而全加器(Full Adder)在此基础上增加了处理来自低位的进位输入,可以完成三位二进制数的相加。

对于多位二进制数的加法,可以通过级联多个全加器来实现。

1. 半加器:由两个异或门(XOR)实现“和”输出,一个与门(AND)实现“进位”输出,即S=A XOR B,Cout=A AND B。

2. 全加器:除了接收两个数据输入A和B外,还接收一个进位输入Cin,同样由异或门计算“和”,但“进位”输出需要考虑三个输入的与或逻辑关系,即S=A XOR B XOR Cin,Cout=(A AND B) OR (B AND Cin) OR (A AND Cin)。

三、实验步骤1. 半加器设计:首先,利用集成电路库中的逻辑门元件构建半加器,将A 和B作为异或门的输入得到和信号S,将A和B分别连接到与门的两个输入端得到进位信号Cout。

2. 全加器设计:在半加器的基础上,增加一个输入端Cin代表低位的进位,同样运用异或门和与门组合形成全加器的逻辑结构,根据全加器的逻辑表达式连接各门电路。

3. 多位加法器设计:为了实现多位二进制数的加法,将若干个全加器按照从低位到高位的顺序级联起来,每级全加器的进位输出连接到下一级的进位输入。

四、实验结果及分析经过电路设计与仿真测试,成功实现了从半加器到多位加法器的功能转化。

当给定两组多位二进制数后,所设计的加法器电路能够准确无误地计算出它们的和,并正确显示进位信息。

2位串行进位的并行加法器真值表

2位串行进位的并行加法器真值表在数字电路中,加法器是常见的逻辑电路之一,用于进行数字的加法运算。

而串行进位的并行加法器是一种常见的加法器类型,它能够实现多位数字的加法运算,具有高效、稳定的特点。

在本文中,我们将对2位串行进位的并行加法器进行深入探讨,包括其真值表、工作原理和应用场景等方面。

一、2位串行进位的并行加法器真值表让我们来了解一下2位串行进位的并行加法器的真值表。

真值表是描述逻辑电路在不同输入组合下的输出情况的表格,通过真值表可以清晰地了解逻辑电路的工作状态。

对于2位串行进位的并行加法器,其真值表如下所示:输入 | 进位 | 输出 A | B | Cin | S | Cout 0 | 0 | 0 | 0 | 0 0 | 0 | 1 | 1 | 0 0 | 1 | 0 | 1 | 0 0 | 1 | 1 | 0 | 1 1 | 0 | 0 | 1 | 0 1 | 0 | 1 | 0 | 1 1 | 1 | 0 | 0 | 1 1 | 1 | 1 | 1 | 1从上面的真值表可以看出,2位串行进位的并行加法器的输出S和Cout与输入A、B和进位Cin之间存在着一定的逻辑关系。

理解并熟记这些逻辑关系对于正确设计和应用加法器起着至关重要的作用。

二、工作原理接下来,让我们来了解2位串行进位的并行加法器的工作原理。

在加法器中,每一位使用了半加模块和全加模块。

半加模块能够实现单个位的加法运算,而全加模块则可以实现考虑进位的加法运算。

串行进位的并行加法器通过将多个全加模块串联起来,实现了高效的多位加法运算。

具体来说,对于2位串行进位的并行加法器,每个位需要经过两个半加模块和一个全加模块的计算。

在计算的过程中,要考虑上一位的进位对当前位的影响,因此需要进行串行进位的处理。

通过合理的电路设计和逻辑门的组合,2位串行进位的并行加法器能够实现快速、准确的多位加法运算。

三、应用场景2位串行进位的并行加法器广泛应用于数字信号处理、计算机系统、通信系统等领域。

2位串行进位并行加法器真值表

2位串行进位并行加法器真值表一、引言在数字逻辑电路中,加法器是一种常用的逻辑电路,用于实现数字的加法运算。

其中,串行进位并行加法器是一种常见的加法器类型,能够实现多位二进制数字的加法。

本文将围绕2位串行进位并行加法器的真值表展开讨论。

二、2位串行进位并行加法器的原理2位串行进位并行加法器是由两个全加器和一个或门组成的加法电路。

其中,全加器是用来实现带有进位的加法运算的基本逻辑单元,而或门用于处理进位信号。

其原理可以简述为:当两个二进制位相加时,需要考虑进位问题,因此需要使用全加器进行处理,同时需要使用或门将进位信号传递到下一位的全加器中。

三、2位串行进位并行加法器真值表的构建为了清晰地展现2位串行进位并行加法器的运行情况,我们可以通过构建真值表来进行分析。

真值表是用来列举所有可能输入情况下的输出结果的表格,可以帮助我们直观地了解电路的运行情况。

基于上述原理,我们可以构建2位串行进位并行加法器的真值表如下:输入A 输入B 输入Ci 输出S 输出Co0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1在上述真值表中,输入A和输入B分别代表两个加数的二进制位,输入Ci代表进位输入,输出S代表本位的和,输出Co代表进位输出。

四、2位串行进位并行加法器真值表的分析通过观察上述真值表,可以得出以下几点分析:1. 当输入A和输入B都为0时,无论进位输入Ci为何值,输出S和输出Co都为0。

这是因为在这种情况下没有进位产生,所以输出和进位都为0。

2. 当输入A和输入B都为1时,无论进位输入Ci为何值,输出S都为0,而输出Co都为1。

这是因为在这种情况下,无论进位输入如何,两个1相加都会产生进位。

3. 当输入A和输入B中有一位为1时,此时的情况与进位输入Ci有关,可以通过观察真值表得出输出S和输出Co的值。

通过对真值表的分析,可以清晰地了解2位串行进位并行加法器在不同输入情况下的工作原理和输出结果,这有助于我们深入理解加法器的运行方式。

EDA 实验一 用两种方法设计2位全加器

实验一用两种方法设计2位全加器实验目的:熟悉利用Quartus II的开发环境设计简单的组合逻辑电路,掌握层次化设计的方法,并通过一个2位全加器的设计把握利用EDA软件进行电子线路设计的各种详细流程。

实验原理:一个2位全加器可由2个1位全加器构成,加法器间的进位可以用串行的方式实现,即将低位的进位输出与高位的进位输入相连接。

而1个全加器的设计可以使用2个半加器进行组合。

这种层次化的设计过程中,每一个层次都可以使用原理图或是VHDL语言来实现。

实验任务:1、完成半加器、全加器的设计,每个层次都可以用原理图或是VHDL语言实现。

将其进行仿真和测试,并生成相应的硬件符号。

2、建立更高层次的原理图设计,将2个1位全加器构成1个2位全加器,完成相应的仿真和测试,使其可以在硬件电路板上实现。

实验内容:1、半加器,全加器(两种方法)方法一:半加器:library ieee;use ieee.std_logic_1164.all;entity h_adder isport(a,b:in std_logic;co,so:out std_logic);end entity h_adder;architecture act of h_adder isbeginso<=a xor b;co<=a and b;end architecture act;全加器:library ieee;use ieee.std_logic_1164.all;entity f_adder isport(ain,bin,cin:in std_logic;sum,cout:out std_logic);end entity f_adder;architecture act of f_adder iscomponent h_adderport(a,b:in std_logic;co,so:out std_logic);end component;signal co1,co2,temp:std_logic;beginu1:h_adder port map(a=>ain,b=>bin,co=>co1,so=>temp);u2:h_adder port map(a=>temp,b=>cin,co=>co2,so=>sum); cout<=co1 or co2;end architecture;方法二:半加器:全加器:2、一个2位全加器仿真波形:第一种设计方法:第二种设计方法:实验结果与总结:丰富自己,取悦自己,随缘,随顺,随境,你的心才会敞开,才会接纳更多的有可能。

串行加法器

串行加法器简介串行加法器是一种基本的数字加法电路,用于将两个二进制数进行相加。

它的原理是将两个二进制数的每一位进行逐位相加,并根据进位信息将结果传递到下一位的相加操作中,最终得到相加后的结果。

串行加法器的主要优点是在每一位的计算中,只需要一个全加器,因此可以通过级联多个全加器来实现多位加法。

同时,由于计算过程是逐位进行的,串行加法器可以处理非常大的数字。

原理串行加法器由一个或多个全加器组成。

全加器是一个组合逻辑电路,具有三个输入和两个输出。

输入包括两个二进制位的值以及上一位的进位信号,输出是当前位的和值和进位信号。

假设我们要相加的两个二进制数为A和B,并且它们的长度为n位。

首先,我们将A和B的最低位输入到第一个全加器中,并将进位信号设置为0。

全加器通过逻辑门电路计算出当前位的和值和进位信号,并将和值输出。

接下来,将A和B的下一位输入到第二个全加器中,并将上一个全加器的进位信号作为输入。

重复这个过程,直到最高位的全加器计算完成。

最终,我们将所有全加器的和值连结在一起,得到最终的相加结果。

示例现在我们来看一个4位串行加法器的示例。

假设我们要相加的两个二进制数为A=1011和B=0110。

它们的长度都是4位。

首先,我们将A和B的最低位输入到第一个全加器中,并将进位信号设置为0。

根据逻辑门电路的计算规则,我们可以得到第一位的和值S1和进位信号C1。

此时,S1=1和C1=0。

接下来,将A和B的下一位输入到第二个全加器中,并将C1作为进位信号输入。

根据逻辑门电路的计算规则,我们可以得到第二位的和值S2和进位信号C2。

此时,S2=0和C2=1。

重复这个过程,直到最高位的全加器计算完成。

最终,我们可以得到相加后的结果为S=10001。

应用串行加法器在计算机体系结构中被广泛应用。

它可以用于实现各种数字逻辑操作,例如整数相加、浮点数相加等。

串行加法器的设计是计算机体系结构中的基础知识,理解串行加法器的原理和工作方式对于理解计算机的运算过程非常重要。

流水线技术在高速数字电路设计中的应用

摘要:流水线技术是设计高速数字电路的一种最佳选择之一,对其实现原理作了较形象的阐述。

针对加法器在DSP中的重要作用,对流水线加法器中流水线技术的应用作了较深入的说明。

同时,对流水线技术中引入寄存器事项也作了较全面的阐述。

1 前言数字信号处理技术(DSP)在许多领域都得到广泛的应用,在数字电路设计时,设计者都希望设计出具有理想速度的电路系统。

目前,并行技术、流水线技术等都是很好的备选方案。

对于组合逻辑电路占主要成分的电路中,流水线技术是首先考虑的技术。

现在,现场可编程门阵列FPGA的集成度已达到很高的程度,且设计灵活,可在实验室里进行,并具有丰富的寄存器,适合设计人员使用流水线技术来进行设计以提高数字电路的整体运行速度。

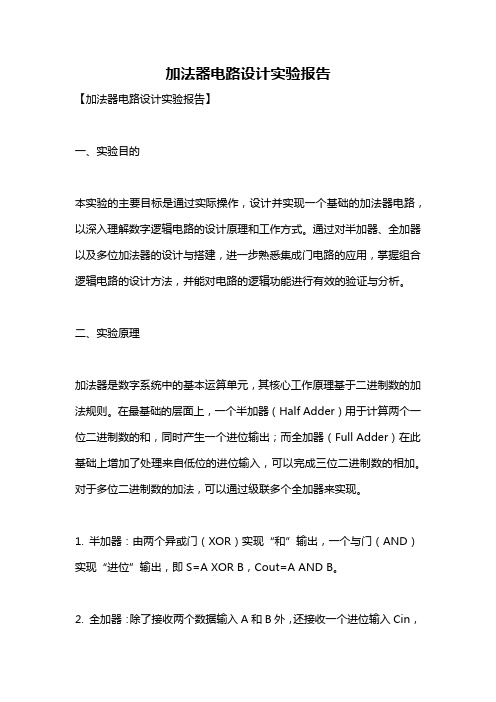

2 流水线技术的作用原理流水线技术就是把在一个时钟周期内执行的操作分成几步较小的操作,并在多个较高速的时钟内完成。

如图1、2所示,对图1中的两个寄存器间的数据通路,在图2中将其分成了3级,并在其间插入了两个寄存器,这就是流水线技术的使用。

图1常规的数据通路图2采用流水线技术数据通路对图1中的数据通路,设tpd≈x,则该电路(不考虑寄存器的影响)从输入到输出的最高时钟频率就为1/x。

而在图z中,假设在理想情况下所分成的3级,每级的tpd≈x/3,则该电路从输入到输出的最高频率可提高到原来的3倍,采用流水线技术有效地提高了系统的时钟频率,因而在多个时钟周期连续工作情况下,就提高了整个系统的数据处理量。

当然,这不包括电路中所加入的寄存器时延,因此每级的实际延迟应比x/ 3稍大。

但在多个时钟周期连续工作情况下,可忽略不计,所以流水线技术能提高系统的数据流量。

3 流水线技术的设计应用加法运算是最基本的数字信号处理(DSP)运算,减法、乘法、除法或FFT运算都可分解为加法运算。

因此进行加法运算的加法器就成为实现DSP的最基本器件,因而研究如何提高其运行速度很有必要。

流水线技术在提高系统整体运行速率方面绩效显著,因而采用流水线技术的流水线加法器就成为继串联加法器、并行加法器之后在选择加法器时的首选。

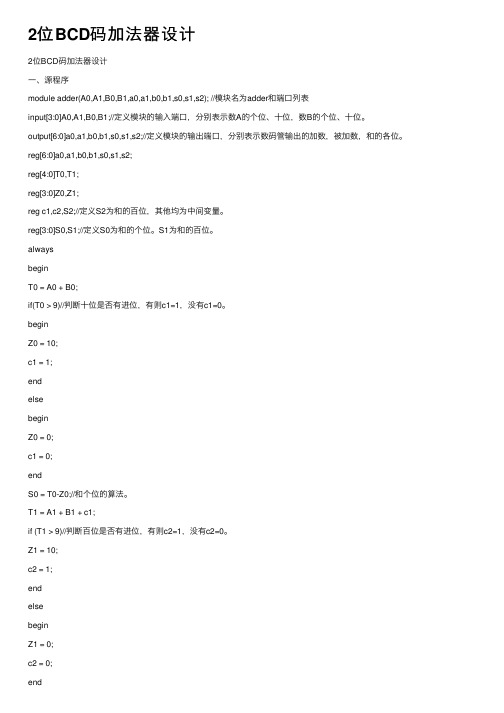

2位BCD码加法器设计

2位BCD码加法器设计2位BCD码加法器设计⼀、源程序module adder(A0,A1,B0,B1,a0,a1,b0,b1,s0,s1,s2); //模块名为adder和端⼝列表input[3:0]A0,A1,B0,B1;//定义模块的输⼊端⼝,分别表⽰数A的个位、⼗位,数B的个位、⼗位。

output[6:0]a0,a1,b0,b1,s0,s1,s2;//定义模块的输出端⼝,分别表⽰数码管输出的加数,被加数,和的各位。

reg[6:0]a0,a1,b0,b1,s0,s1,s2;reg[4:0]T0,T1;reg[3:0]Z0,Z1;reg c1,c2,S2;//定义S2为和的百位,其他均为中间变量。

reg[3:0]S0,S1;//定义S0为和的个位。

S1为和的百位。

alwaysbeginT0 = A0 + B0;if(T0 > 9)//判断⼗位是否有进位,有则c1=1,没有c1=0。

beginZ0 = 10;c1 = 1;endelsebeginZ0 = 0;c1 = 0;endS0 = T0-Z0;//和个位的算法。

T1 = A1 + B1 + c1;if (T1 > 9)//判断百位是否有进位,有则c2=1,没有c2=0。

Z1 = 10;c2 = 1;endelsebeginZ1 = 0;c2 = 0;endS1 = T1-Z1;//和⼗位的算法。

S2 = c2;//和百位的算法。

End//利⽤case语句分别让数码管显⽰加数,被加数,和的各位。

always @(A0)begincase(A0)4'd0:a0=7'b0000001;4'd1:a0=7'b1001111;4'd2:a0=7'b0010010;4'd3:a0=7'b0000110;4'd4:a0=7'b1001100;4'd5:a0=7'b0100100;4'd6:a0=7'b0100000;4'd7:a0=7'b0001111;4'd8:a0=7'b0000000;4'd9:a0=7'b0000100;default: a0=7'bx;endalways @(A1) begincase(A1)4'd0:a1=7'b0000001; 4'd1:a1=7'b1001111; 4'd2:a1=7'b0010010; 4'd3:a1=7'b0000110; 4'd4:a1=7'b1001100;4'd5:a1=7'b0100100; 4'd6:a1=7'b0100000; 4'd7:a1=7'b0001111; 4'd8:a1=7'b0000000; 4'd9:a1=7'b0000100; default: a1=7'bx; endcaseendalways @(B0)begincase(B0)4'd0:b0=7'b0000001; 4'd1:b0=7'b1001111; 4'd2:b0=7'b0010010; 4'd3:b0=7'b0000110; 4'd4:b0=7'b1001100;4'd5:b0=7'b0100100;4'd7:b0=7'b0001111; 4'd8:b0=7'b0000000; 4'd9:b0=7'b0000100; default: b0=7'bx; endcaseendalways @(B1)begincase(B1)4'd0:b1=7'b0000001; 4'd1:b1=7'b1001111; 4'd2:b1=7'b0010010; 4'd3:b1=7'b0000110; 4'd4:b1=7'b1001100;4'd5:b1=7'b0100100; 4'd6:b1=7'b0100000; 4'd7:b1=7'b0001111; 4'd8:b1=7'b0000000; 4'd9:b1=7'b0000100; default: b1=7'bx; endcaseendalways @(S0)begincase(S0)4'd0:s0=7'b0000001;4'd2:s0=7'b0010010; 4'd3:s0=7'b0000110; 4'd4:s0=7'b1001100; 4'd5:s0=7'b0100100; 4'd6:s0=7'b0100000;4'd7:s0=7'b0001111; 4'd8:s0=7'b0000000; 4'd9:s0=7'b0000100; default: s0=7'bx; endcaseendalways @(S1) begincase(S1)4'd0:s1=7'b0000001; 4'd1:s1=7'b1001111; 4'd2:s1=7'b0010010; 4'd3:s1=7'b0000110; 4'd4:s1=7'b1001100;4'd5:s1=7'b0100100; 4'd6:s1=7'b0100000; 4'd7:s1=7'b0001111; 4'd8:s1=7'b0000000; 4'd9:s1=7'b0000100; default: s1=7'bx; endcaseendalways @(S2) begincase(S2)4'd0:s2=7'b0000001; 4'd1:s2=7'b1001111; 4'd2:s2=7'b0010010; 4'd3:s2=7'b0000110; 4'd4:s2=7'b1001100;4'd5:s2=7'b0100100; 4'd6:s2=7'b0100000; 4'd7:s2=7'b0001111; 4'd8:s2=7'b0000000; 4'd9:s2=7'b0000100; default: s2=7'bx; endcaseendendmodule⼆、仿真结果能够完成从1到99的加法运算,并且正常显⽰。

一位加法器原理

一位加法器原理

加法器是一种数字电路,用于将两个二进制数相加。

其原理如下:

1. 加法器通常由多个全加器组成。

全加器是一个三输入、两输出的电路,其输入为两个二进制位和一个进位信号,输出为一个二进制位和一个向高位的进位信号。

2. 当两个二进制位相加时,如果它们的和小于2,那么输出为

它们的和,进位信号为0;如果它们的和等于2,那么输出为0,进位信号为1;如果它们的和等于3,那么输出为1,进位

信号为1。

3. 在加法器中,多个全加器按位相连,每一位的进位信号都连接到下一位的进位输入,最高位的进位信号需要外部提供。

4. 加法器的输出为两个二进制数的和,如果最高位的进位信号为1,那么说明出现了溢出,加法器不能正确处理这样的数字。

5. 加法器还可以实现减法运算,将其中一个数取反后加上另一个数即可。

总之,加法器是计算机基础电路中非常重要的一种电路,它将二进制数的加法和减法实现为电路操作,为计算机的运算提供了重要支持。

多位加法器电路图解

多位加法器电路图解前面讲过,半加器实现两个1位二进制数相加时不考虑低位的进位,输出变量只有两个(加数和被加数),而全加器实现两个1位二进制数相加时则考虑低位的进位,输入变量有3个(加数、被加数和低位的进位)。

多位二进制数相加的特点是:最低位时两个数最低位的相加,不需考虑进位。

其余各位都是3个数相加,包括加数、被加数和低位送来的进位。

任何位相加都产生本位和与向高位的进位两个结果。

因此要进行多位二进制数相加,最简洁的方法是将多个1位加法器进行级联,称为串行进位加法器。

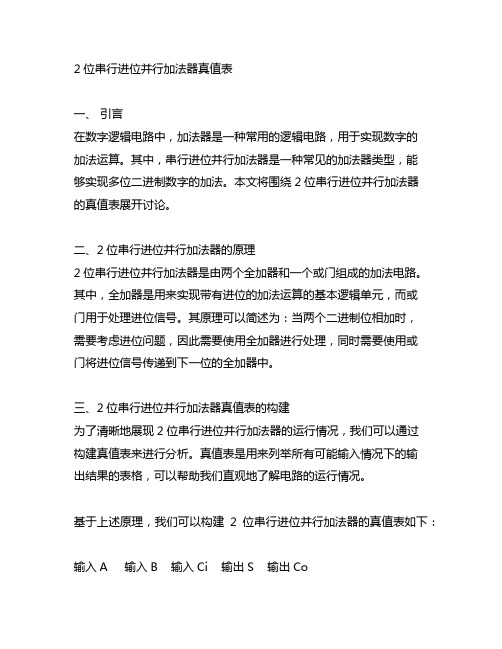

图1与图2所示都是4位串行进位加法器。

图1所示电路中最低位都是半加器,其余各位是全加器,图2所示电路中都是全加器,最低位全加器的CI端接0。

从图中可见,两个4位相加数A3A2A1A0和B3B2B1B0的各位同时送到相应全加器的输入端,进位数串行传送,相加的结果是CO,S3S2S1S0。

1位加法器的个数等于相加数的位数。

图1 4位加法器电路(最低位是半加器)图2 4位加法器电路(最低位是全加器) 串行进位加法器的优点是电路比较简洁,缺点是速度比较慢。

由于进位信号是串行传递,最终一位的进位输出CO3要经过4位全加器传递之后才能形成。

假如进位增加,传输延迟时间将更长,工作速度更慢。

为了提高速度,人们又设计了一种多位数快速进位(又称超前进位)的加法器。

所谓快速进位,是指加法运算过程中,各级进位信号同时送到各位全加器的进位输入端。

现在的集成加法器大多采纳这种方法。

74LS283是一种典型的快速进位的集成4位二进制加法器。

图3所示为74LS283加法器的图形符号。

图3 74LS283型4位加法器的图形符号一片74LS283只能进行4位二进制数的加法运算,将多片74LS283进行级联,就可扩展加法运算的位数。

用2片74LS283组成的8位二进制数加法电路如图4所示。

图4 8位二进制数加法器电路。

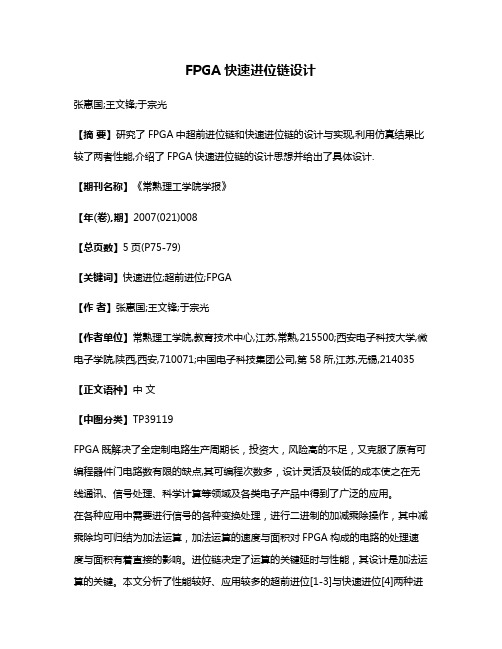

FPGA快速进位链设计

FPGA快速进位链设计张惠国;王文锋;于宗光【摘要】研究了FPGA中超前进位链和快速进位链的设计与实现,利用仿真结果比较了两者性能,介绍了FPGA快速进位链的设计思想并给出了具体设计.【期刊名称】《常熟理工学院学报》【年(卷),期】2007(021)008【总页数】5页(P75-79)【关键词】快速进位;超前进位;FPGA【作者】张惠国;王文锋;于宗光【作者单位】常熟理工学院,教育技术中心,江苏,常熟,215500;西安电子科技大学,微电子学院,陕西,西安,710071;中国电子科技集团公司,第58所,江苏,无锡,214035【正文语种】中文【中图分类】TP39119FPGA既解决了全定制电路生产周期长,投资大,风险高的不足,又克服了原有可编程器件门电路数有限的缺点,其可编程次数多,设计灵活及较低的成本使之在无线通讯、信号处理、科学计算等领域及各类电子产品中得到了广泛的应用。

在各种应用中需要进行信号的各种变换处理,进行二进制的加减乘除操作,其中减乘除均可归结为加法运算,加法运算的速度与面积对FPGA构成的电路的处理速度与面积有着直接的影响。

进位链决定了运算的关键延时与性能,其设计是加法运算的关键。

本文分析了性能较好、应用较多的超前进位[1-3]与快速进位[4]两种进位链,在晶体管级给出一个简单的实现方案,并实际构成4位进位链以比较两种进位链的速度与面积性能,然后讨论FPGA中快速进位链的设计。

根据全加器的真值表(表1),全加器的和表示为进位可表示为其等价形式为其中称Pi=AiBi为进位产生项,值为1时,进位输出由此项决定;Gi=Ai⊕Bi为进位传播项(有些情况如镜像结构中也将进位传播项定义为Pi=Ai+Bi),值为1时,进位输出等于进位输入;同一时刻Pi与Gi只能有一项成立。

此表达式是一个递归表达式,第i个加式的进位输出最终可以归结为只和相加数及最初的进位输入相关,如第四个加式的进位输出为C4=G3+P3G2+P3P2G1+P3P2P1G0+P3P2P1P0C0,从而各级进位可以并行计算,与串行进位链中进位的逐级传递相比,利用超前进位速度有明显的提高,但以消耗较多的面积为代价。

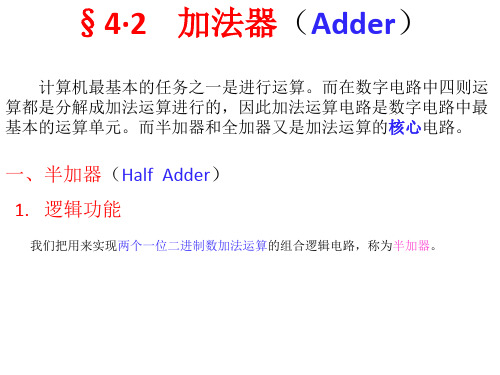

组合逻辑电路(加法器)

Ci m3 m5 Ai Bi ( Ai Bi )Ci 1 Ai Bi

全加器的逻辑图和逻辑符号

Si m1 m2 m4 m7 Ai BiCi 1 Ai BiCi 1 Ai BiCi 1 Ai BiCi 1 Ai ( BiCi 1 BiCi 1 ) Ai ( BiCi 1 BiCi 1 ) Ai ( Bi Ci 1 ) Ai ( Bi Ci 1 ) Ai Bi Ci 1

加法器

半加器和全加器

1、半加器

能对两个1位二进制数进行相加而求得和及进位的逻辑 电路称为半加器.

半加器真值表 Ai Bi 0 1 0 1 Si 0 1 1 0 Ci 0 0 0 1

本位 的和 向高 位的 进位

Ai Bi

=1

Si Ci

加数

0 0 1 1

&

半加器电路图 Ai Bi ∑

CO

Si Ci

Si Ai Bi Ai Bi Ai Bi Ci Ai Bi

0

0

1

1

被加数/被减数

加数/减数

加减控制

BCD码+0011=余3码

C0-1=0时,B0=B,电路 执行A+B运算;当C0-1=1 时,B1=B,电路执行A -B=A+B运算。

3、二-十进制加法器

修正条件 C C3 S3S2 S3S1

8421 BCD 输出 S3 ' S2 ' S1 ' S0' 4 位二进制加法器 C0-1 A1 A0 B3 B2 B1 B0

4位超前进位加 法器递推公式

S 2 P2 C1 1G0 P 2P 1P 0C0 1 C2 G2 P2C1 G2 P2G1 P2 P S3 P3 C2 1G0 P 3P 2P 1P 0C0 1 C3 G3 P3C2 G3 P3G2 P3 P2G1 P3 P2 P

加法器(Adder) 数电课件

2. 分析

半加器有两个输入:加数 、被加数Ai ;两个输出:B和i 输出 、进位输出 。

Si

Ci

3. 真值表

半加器的真值表如表4.2.1—1所示。

表4.2.1—1

4. 逻辑函数表达式

半加器的逻辑函数表达式为

Si Ai Bi Ai Bi Ai Bi Ci Ai Bi

5. 逻辑电路图

定

。

An1 An、2 L A2 A1 A0 Cn1Cn2 L C2C1C0

B和n1Bn给2出L,B便2可B1以B直0 接C确01

方法二

C0 P0C01 G0

C1 P1C0 G1

P1 P0C01 G0 G1

C2 P2C1 G2

P2 P1 P0C01 G0 G1 G2

图4.2.5—3 Ⅰ. 加减控制输入为0时,该电路实现加法运算; Ⅱ. 加减控制输入为1时,该电路实现减法运算(补码加法)。

返回

半加器的逻辑函数表达式为

Si Ai Bi Ai Bi Ai Bi Ci Ai Bi

5. 逻辑电路图

半加器的逻辑电路图如图4.2.1—1所示。

(公式4.2.1) (公式4.2.2)

图4.2.1—1

6. 逻辑符号

半加器的逻辑符号如图4.2.1—2所示。

图4.2.1—2

二、全加器(Full Adder)

依次递推可知,只要

定

。

An1 An、2 L A2 A1 A0 Cn1Cn2 L C2C1C0

B和n1Bn给2出L,B便2可B1以B直0 接C确01

四位超前进位加法器的逻辑电路图如图4.2.3—2所示。 图4.2.3—2

四、中规模集成加法器

数字逻辑实验报告

F 表示进位

A0

B0

A1

B1

C1

C2

F

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

1

0

1

0

0

0

0

1

1

1

1

0

0

1

0

0

0

1

0

0

1

0

1

1

0

0

0

1

1

0

1

1

0

0

1

1

1

0

0

1

1

0

0

0

1

0

0

1

0

0

1

1

1

0

1

0

1

0

0

0

1

1

0

1

1

0

1

1

1

1

0

0

0

0

1

1

1

0

1

0

0

1

1

1

1

0

0

1

1

1

1

1

1

1

0

1

实现电路:(两个全加器)

选做第二题:

五、实验记录

实验(1)

第一题:

1. 步骤:接好电路,接通电源,进行逻辑特性验证实验 1)7400 引脚的接法: 1 接 k11,L1 2 接 k10,L2 ,3 接 L3

2、真值表:

A

B

F

0

0

1

0

2位BCD码加法器

2位BCD码加法器一、实验内容:利用V erilog HDL语言,编写一个2为BCD码加法器程序,并在DE2板是实现功能的运用。

A0、A1,B0、B1分别是2个输入数字,S0-S2为输出,经过BCD加法器的运算,能实现BCD码加法功能。

设计思路:A0、B0分别是A、B的低位,相加的值T0=A0+B0,若T0>10,则Z0赋值为10,同时进位C0=1,和值低位S0=T0-Z0;同理,高位A1、B1,T1=A1+B1+C0,若T1>10,则Z1=10,进位C1=1,和值高位S1=T1-Z1;S2=C1。

二、实验源程序:1)BCD加法器module BCDadder(A0,A1,B0,B1,S0,S1,S2,clear); //定义输入模块input [3:0]A0; //考虑到A0、B0、A1、B1的值可能input [3:0]A1; 超过十进制数8,顾定义长度为4位;input [3:0]B0;input [3:0]B1;input clear;output S0;output S1;output S2;reg [3:0]S0;reg [3:0]S1;reg [3:0]S2;reg [4:0]C0;reg [4:0]C1;reg [4:0]T0; //低位和值可能超过16,所以定义T0、T1长reg [4:0]T1; 度为5;reg [4:0]Z0;reg [4:0]Z1;always @(posedge clear) //以每一次复位上升沿到来开始计算和值;beginT0=A0+B0; //低位相加和值赋T0;if(T0>9)beginZ0=10; //如果低位相加有进位,则赋值Z0=10;C0=1; //如果T0>9,则有进位,此时C0=1;endelsebeginZ0=0;C0=0;endbeginT1=A1+B1+C0; //高位为A1加B1再加进位C0,赋值给T1;if(T1>9)beginZ1=10;C1=1;endelsebeginZ1=0;C1=0;endendbeginS0=T0-Z0; //和值S0到S1赋值;S1=T1-Z1;S2=C1;endendendmodule2)输入数A0、A1、B0、B1显示module indisplay(A0,A1,B0,B1,displayA0,displayA1,displayB0,displayB1); input [3:0]A0;input [3:0]A1;input [3:0]B0;input [3:0]B1;output [6:0]displayA0;output [6:0]displayA1; //定义7段数码管的输出;output [6:0]displayB0;output [6:0]displayB1;reg [6:0]displayA0;reg [6:0]displayA1; //定义其类型为寄存器类型;reg [6:0]displayB0;reg [6:0]displayB1;always@(A0 or A1 or B0 or B1) //当输入A、B中任何一位变化,即执行输入显示程序;begincase(A0) //输入A0显示4'd0:displayA0=7'b1000000;4'd1:displayA0=7'b1111001;4'd2:displayA0=7'b0100100;4'd3:displayA0=7'b0110000;4'd4:displayA0=7'b0011001;4'd5:displayA0=7'b0010010;4'd6:displayA0=7'b0000010;4'd7:displayA0=7'b1011000;4'd8:displayA0=7'b0000000;4'd9:displayA0=7'b0010000;default: displayA0=7'b1000000; //默认时,数码管显示数字“0”;endcasecase(A1) //输入A1显示4'd0:displayA1=7'b1000000;4'd1:displayA1=7'b1111001;4'd2:displayA1=7'b0100100;4'd3:displayA1=7'b0110000;4'd4:displayA1=7'b0011001;4'd5:displayA1=7'b0010010;4'd6:displayA1=7'b0000010;4'd7:displayA1=7'b1011000;4'd8:displayA1=7'b0000000;4'd9:displayA1=7'b0010000;default:displayA1=7'b1000000; //默认时,数码管显示数字“0”;endcasecase(B0) //输入B0显示4'd0:displayB0=7'b1000000;4'd1:displayB0=7'b1111001;4'd2:displayB0=7'b0100100;4'd3:displayB0=7'b0110000;4'd4:displayB0=7'b0011001;4'd5:displayB0=7'b0010010;4'd6:displayB0=7'b0000010;4'd7:displayB0=7'b1011000;4'd9:displayB0=7'b0010000;default:displayB0=7'b1000000; //默认时,数码管显示数字“0”;endcasecase(B1) //输入B1显示4'd0:displayB1=7'b1000000;4'd1:displayB1=7'b1111001;4'd2:displayB1=7'b0100100;4'd3:displayB1=7'b0110000;4'd4:displayB1=7'b0011001;4'd5:displayB1=7'b0010010;4'd6:displayB1=7'b0000010;4'd7:displayB1=7'b1011000;4'd8:displayB1=7'b0000000;4'd9:displayB1=7'b0010000;default:displayB1=7'b1000000; //默认时,数码管显示数字“0”;endcaseendendmodule3)输出显示module display(S0,S1,S2,display1,display2,display3);input[3:0] S0;input[3:0] S1;input[3:0] S2;output[6:0] display1;output[6:0] display2;output[6:0] display3;reg[6:0] display1;reg[6:0] display2;reg[6:0] display3;always @(S0 or S1 or S2) //当和值S中的任何一位变化,就开始执行显示程序;begincase(S0) //和值第一位S0显示;4'd0:display1=7'b1000000;4'd1:display1=7'b1111001;4'd2:display1=7'b0100100;4'd3:display1=7'b0110000;4'd4:display1=7'b0011001;4'd5:display1=7'b0010010;4'd6:display1=7'b0000010;4'd7:display1=7'b1011000;4'd8:display1=7'b0000000; //默认时,数码管显示数字“0”;default: display1=7'b1000000; //默认时,数码管显示数字“0”;endcasecase(S1) //和值第二位S1显示;4'd0:display2=7'b1000000;4'd1:display2=7'b1111001;4'd2:display2=7'b0100100;4'd3:display2=7'b0110000;4'd4:display2=7'b0011001;4'd5:display2=7'b0010010;4'd6:display2=7'b0000010;4'd7:display2=7'b1011000;4'd8:display2=7'b0000000;4'd9:display2=7'b0010000;default:display2=7'b1000000; //默认时,数码管显示数字“0”;endcasecase(S2) //和值第三位S2显示;4'd0:display3=7'b1000000;4'd1:display3=7'b1111001;4'd2:display3=7'b0100100;4'd3:display3=7'b0110000;4'd4:display3=7'b0011001;4'd5:display3=7'b0010010;4'd6:display3=7'b0000010;4'd7:display3=7'b1011000;4'd8:display3=7'b0000000;4'd9:display3=7'b0010000;default:display3=7'b1000000; //默认时,数码管显示数字“0”;endcaseendendmodule4)模块连接三、实验仿真与实现1)BCD加法器仿真输入A为24,B为48,当clear复位后,和值S为72,与理论一致,故BCD加法器正常;输入A为06,B为14,在clear的上升沿来到是计算和值,display得出相应值,从仿真结果可以看出程序正常实现BCD码加法器功能。

224 基本的二进制加法减法器图22(a)示出了补码运算的二进

对一位全加器(FA)来说,Si的时间延迟 为6T(每级异或门延迟3T),Ci+1的时间 延迟为5T,其中T被定义为相应于单级 逻辑电路的单位门延迟。T通常采用 一个“与非”门或一个“或非”门的 图2.2(b) 行波进位的补码加法/减法器 时间延迟来作为度量单位。

现在我们计算一个n位的行波进位加法器的时间延迟。假如采用 图2.2(b)所示的一位全加器并考虑溢出检测,那么n位行波进位加 法器的延迟时间ta为 t a= n · 2T+9T=(2n+9)T (2.22)

2.2.4 基本的二进制加法/减法器 图2.2(a)示出了补码运算的二进制加法/减法器逻辑结构图.由图看到,n个1 位的全加器(FA)可级联成一个n位的行波进位加法器.M为方式控制输入线, 当M=0时,做加法(A+B)运算;当M=l时,做减法(A-B)运算,在后一 种情况下, A-B运算转化成[A] 补+[-B] 补运算,求补过程由B+1来实现.因此 图中是右边的全加器的起始进位输入端被连接到功能方式线M上,做减法时 M=l,相当于在加法器的最低位上加1.另外图中左边还表示出单符号位法的溢 出检测逻辑:当Cn=Cn-1时,运算无溢出;而当Cn≠Cn-1时,运算有溢出,经异或 门产生溢出信号.

2.2.5 十进制加法器

十进制加法器可由BCD码(二-十进制码)来设计,它可以在 二进制加法器的基础上加上适当的“校正”逻辑来实现, 该校正逻辑可将二进制的“和”改变成所要求的十进制格 式。 n位BCD码行波式进位加法器的一般结构如图 2.3(a)所示,它由n级组成,每一级将一对4位的BCD数字相 加,并通过一位进位线与其相邻级连接。而每一位十进制 数字的BCD加法器单元的逻辑结构示于图2.3(b)。 在十进制运算时,当相加二数之和大于9时,便产生进位。可 是用BCD码完成十进制数运算时,当和数大于9时,必须对和 数进行加6修正。这是因为,采用BCD码后,在二数相加的和 数小于等于9时,十进制运算的结果是正确的;而当相加的 和数大于9时,结果不正确,必须加6修正后才能得出正确的 结果。因此,当第一次近似求值时,可将它看成每一级是一 个4位二进制加法器来执行,就好像xi和yi是普通4位二进 制数一样。

基于SOPC的自演化硬件实现

基于SOPC的自演化硬件实现刘洁丽;姚睿【摘要】The design and implementation of evolvable hardware based on the SOPC were presented.The method took Virtex-Ⅱ Pro development board as hardware platform,and the embedded soft-core microprocessor named Microblaze as controller.First,a method called virtual reconfigurable circuit was designed by hardware description language VHDL.Then,the virtual reconfigurable circuit was made into evolvable IP core and connected with soft-core microprocessor Microblaze through OPBbus.Finally,the genetic algorithm was given based on Microblaze to make evolutionary operation as to the evolvable IP core and an adder circuit was used to verify the implementation of evolvable hardware.The result shows that this method can make chromosome code simplified greatly and operated quickly,and it also has the flexibility of software as well as the customizability of hardware.%提出了一种基于SOPC(片上可编程系统)的自演化硬件实现的设计方法,并以Virtex-ⅡPro开发板为硬件平台,内嵌的软核处理器Microblaze为控制核心.首先使用VHDL硬件描述语言设计虚拟可重构电路;然后将虚拟可重构电路定制成可进化IP核并通过OPB总线与软核处理器相连;最后在处理器上编写遗传算法程序对定制的可进化核进行进化操作,以一位加法器为例验证了自演化硬件的实现.结果表明,该方法不但可以大大简化染色体编码,便于进化操作,而且软件上操作灵活方便,硬件上又具有可定制性.【期刊名称】《佳木斯大学学报(自然科学版)》【年(卷),期】2012(030)002【总页数】4页(P209-212)【关键词】演化硬件;片上可编程系统;虚拟可重构;遗传算法;可进化核【作者】刘洁丽;姚睿【作者单位】南京航空航天大学自动化学院,江苏南京210016;南京航空航天大学自动化学院,江苏南京210016【正文语种】中文【中图分类】TN929.50 引言演化硬件(Evolvable Hardware)是一种将演化算法与可编程器件有机结合起来的硬件系统.演化硬件像生物一样能够根据环境的变化改变自身的硬件结构,以适应其生存环境的硬件,即大规模集成电路.它是演化算法在硬件系统结构中设计、调节等的应用[1].图1 系统硬件架构图自演化硬件是在硬件内部完成遗传操作和适应度计算[2-3],例如在同一片FPGA 上演化生成目标电路[4-5],利用其片上集成的微处理器核执行演化算法.自演化硬件对于实现自适应硬件具有重要的意义.本文使用Xilinx公司的Virtex-ⅡPro系列型号为ML310的FPGA开发板,用其软核Microblaze运行标准遗传算法[6-7],采用基于虚拟可重构电路的可进化核,实现了基于SOPC的自演化硬件,并以一位加法器电路进行了验证.图2 OPB可进化模块1 系统的硬件设计架构本文实现的基于SOPC的自演化硬件系统[8]的硬件架构如图1所示.其中嵌入式处理器Microblaze软核是硬件架构图的核心,标准遗传算法编写在其中,它通过OPB总线可以实现与程序存储器、数据存储器的高速通信;可进化核是基于虚拟可重构电路实现的,是遗传算法的实现载体;时钟模块可以用于满足复杂的时钟和时钟域需求以及延时控制;串口通信接口与PC机相连,通过超级终端输出进化操作过程以及进化结果.1.1 Microblaze处理器软核Microblaze是Xilinx公司推出的32位软处理器核,是业界最快的软处理器IP核解决方案,支持CoreConnect总线的标准外设集合,具有重复利用性和兼容性.Microblaze结构最显著的特点是基于CoreConnect构建.CoreConnect技术是由IBM开发的片上总线通信链,通过多个IP核相互连接,构成一个完整的嵌入式系统.CoreConnect技术应用在平台设计中时,CPU核、系统以及外设IP 核可以重复使用,以达到更高的整体系统性能.图3 虚拟可重构电路的结构1.2 可进化核设计可进化核作为实现载体,需要自己设计,并且保证软核处理器Microblaze能对其进行访问,即实现染色体的配置及结果的读回.设计好的可进化核需要通过IPIF 接口挂接在OPB总线上,如图2所示图4 cell单元的内部结构示意图可进化核包括虚拟可重构电路[9-10]及其配置控制电路.可进化核需要实现虚拟可重构电路的染色体编码,然后将编码配置信息进行读回.虚拟可重构电路可以根据具体的应用需要来配置电路的功能,并且可以封装成独立于具体的FPGA开发板的IP核且FPGA开发板不需要支持部分可重构.虚拟可重构电路还能简化染色体的编码,在重构的过程中不涉及配置位流文件的编码和修改,具有比较好的适用性和可移植性.图5 找到最优解时超级终端的部分输出图1.3 虚拟可重构电路设计虚拟可重构电路模型一般由两部分组成[11],基本功能单元以及功能单元之间的连接.基本功能单元一般可以包含很多种功能,可以根据基因算法与对可重构电路的配置相应地选择其功能.基本单元之间的互连则在基因算法的配置下,连接不同的功能单元,形成一条从输入到输出的数据通道.本文设计的虚拟可重构电路是一个由8×5个可重配置功能块组成的阵列,如图3所示.基本功能单元由3输入的LUT组成,基本单元之间的互连如下:第一列的输入由原始输入,以及原始输入的反向构成,第二列的输入由原始输入与第一列的输出构成,第三列的输入由第一列的输出以及第二列的输出构成,依次类推,后面每一列的输入都由前两列的输出构成.每个可配置功能单元Cell的内部结构示意图如图4所示.它由3个输入和1个输出表示.LUT查找表即最右边的模块提供了逻辑功能运算,电路的3个输入由图中的3个16选1的选择器决定.同时前面3个16选1的选择器的输出又作为控制位来用决定后面查找表LUT的输入.由图4可知,对单个Cell单元功能进行配置需要的染色体长度是20位,所以整个虚拟可重构电路阵列的染色体配置位=5*8*20=800位.通过对虚拟可重构电路进行遗传操作来寻找满足适应度的正确的染色体配置,即可实现期望功能电路.整个虚拟可重构电路在ISE10.1工具中用硬件描述语言(VHDL)来构建.此结构模型可以根据具体的应用需要准确的设计出可配置功能单元阵列、布线电路和配置寄存器.2 系统验证与实验结果本文的具体设计目标是在设计的基于SOPC的自演化硬件平台上,运用标准遗传算法对挂接在OPB总线可进化核进行染色体的配置并将结果读回,通过遗传算法的迭代过程,进化出期望的电路.其中标准遗传算法的迭代操作及对外设的读写在Microblaze处理器上,采用软件的方法实现.下面以一位加法器为例说明系统设计过程与运行结果.2.1 设计过程在嵌入式系统开发工具XPS中利用BSB搭建了最小系统的硬件结构,包括时钟模块,串口通信接口等.在ISE工具中设计虚拟可重构电路,并将此虚拟可重构电路定制成可进化核添加到系统的硬件结构中,构成自演化系统的硬件平台.在SDK工具中编写基本遗传算法程序,实现对可进化核的染色体配置与结果的读回、适应度的计算以及进化操作等.最终将软硬件结合生成的位流文件下载到FPGA中,通过超级终端输出进化操作过程以及进化结果.2.2 实验结果本设计中进化的输出结果是通过超级终端显示的,超级终端的输出结果以及单次进过程的适应度变化曲线分别如图5和图6所示.图6 进化过程中适应度变化曲线实验中的进化参数设置为:种群规模数为128,联赛选择规模的大小为5,变异率为2%,最大进化代数为100代,最大适应度为16.从图5,6中,我们可以看出,在上述参数的设定下,进化操作运行到43代时,找到了最优解,此时,适应度正好为16.在调试软件应用时,我们发现,遗传算法参数的改变,对进化结果也会产生很大的影响,比如如果联赛选择规模过大,进化过程的计算量将加大,相应的进化速度就会变慢,同时过高的联赛选择规模还会使被选的个体重复出现.所以,选择合理的进化过程的操作参数对进化的结果,进化的效率有着很好的帮助.3 结论本文通过对基于SOPC的自演化硬件设计方法的研究,给出了自演化嵌入式系统的总体结构,本文中的嵌入式系统是在Xilinx公司生产的Virtex-ⅡPro系列型号为ML310的开发板设计的,以进化一位加法器电路为例验证了所设计的实验平台的有效性.实验结果表明,该实验平台不但能够根据用户的需要添加自己设计的IP核,而且能够在嵌入式处理器中有效地实现基于遗传算法的进化电路.这种设计方法具有很好的灵活性和通用性,具有进一步的研究价值.下一步,我们可以多用几个电路来验证系统的正确性,例如二位加法器,二位乘法器等等.参考文献:[1] 姚睿.数字进化硬件关键技术研究[D].南京:南京航空航天大学,2008.[2] Resano J,Mozos D,Verkest D,et al.A Reconfiguration Manager for Dynamically Reconfigurable Hardware[J].IEEE Trans on Design& Test of Computers,2005,22(5):452-460.[3] Sapargalitev Y,Kalganova T.Absolutely Free Extrinsic Evolution of Passive Low - pass Filter[C].Canadian Conference on E-lectrical and Computer Engineering.Ottawa,Canada,2006:1210-1213.[4] Zhang Y,Smith S,Tyrrell A.Digital Circuit Design Using Intrinsic Evolvable Hardware[C].Proc 2004 NASA/DoD Conference on Evolvable Hardware Krakow,Portland,2004:55-62.[5] Tufte G,Haddow P.Biologically-inspired:a Rule-based Self-reconfiguration of a Virtex Chip[C].Proc the ComputationalScience(ICCS).Krakow Poland,2004:1249-1256.[6] 陈国良,王煦法,庄镇泉.遗传算法及其应用[M].北京:人民邮电出版社,1996:28-97.[7] 汤欢,赵曙光.基于FPGA实现的遗传算法[J].电子测量技术,2009,32(1):151 -153,161.[8] 杨强浩.基于EDK的FPGA嵌入式系统开发[M].北京:机械工业出版社,2008.[9] Lukas Sekanina.Evolutionary Functional Recovery in Virtual Reconfigurable Circuits[J].Brno university of Technology.2000,0(0):1-21.[10] 宗平,周叶丹.一种可进化IP核的设计与实现[J].单片机与嵌入式系统应用.2004:8-10.[11] 赵亮.基于FPGA的SOC设计方法实现进化硬件的研究[D].合肥工业大学.合肥:合肥工业大学,2009.。

22多位串行进位加法器设计

2.2 多位串行进位加法器设计一个全加器可以实现一位二进制数加法运算。

多个全加器可以构成串行进位加法器实现多位二进制数的运算。

串行进位加法器的优点是电路结构比较简单,缺点是运算速度慢。

本节希望通过多位串行进位加法器的设计,进一步练习Quartus Ⅱ软件平台的操作方法,掌握模块符号的创建方法,了解串行进位加法器的原理和设计方法以及7段显示译码器7448的功能及应用。

2.2.1 设计实例1.设计要求在节2.1的基础上,利用全加器和半加器的逻辑符号设计一个两位串行进位加法器电路。

相加结果用七段数码显示器以十进制形式显示。

2.硬件环境设计可以在FPGA开发装置上实现,两个两位的二进制加数由4个按键输入。

若采用DE2开发板实现设计,其LED数码管为共阳显示器,采用静态驱动方式,每个显示器的七个段控制a~g及小数点dp分别输出。

若采用LP-2900开发装置实现设计,其LED数码管为共阴显示器。

六个显示器的七个段控制a~g及小数点dp分别对应相连,各显示器的共阴极分别由一个3线-8线译码器74138的输出Y0~Y5控制。

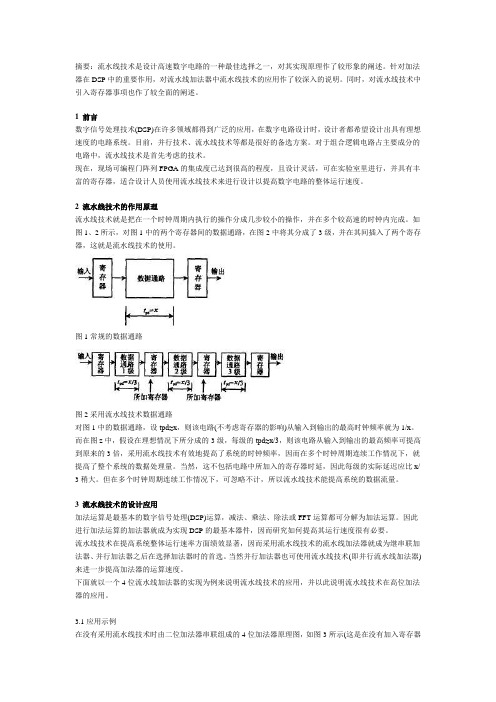

译码器的3位输入码分别由FPGA的I/O端口DE3、DE2、DE1控制,如图2-2-1所示。

图2-2-1 LP-2900开发装置FPGA与LED数码显示器的电路连接3线-8线译码器的3位输入码DE3、DE2、DE1为“000”~“101”时,输出Y0~Y5中有一个为0,FPGA的a~g端口将控制共阴极为0的数码管显示。

比如,当DE3、DE2、DE1为“011”时,Y3=0,数码管C4显示。

由于本设计只需一位显示,所以可任意选择DE3、DE2、DE1为“000”~“101”中的一组码。

采用DE2开发板实现设计,可任选8个LED 数码管中的一个显示运算结果,不需要控制DE3、DE2和DE1脚。

2.2.2 设计原理分析1.多位串行进位加法器的逻辑功能多位串行进位加法器采用多个全加器构成。

每个全加器负责一位二进制数的运算,三个输入分别为本位的被加数、加数和低位的进位输出。

二位加法器芯片组成四位加法器

二位加法器芯片组成四位加法器在现代科技发展的背景下,数字电路已经成为了我们生活中不可或缺的一部分。

而在数字电路中,加法器是最为基础的组成单元之一。

二位加法器是一种能够对两个二进制数进行相加运算的电路,而四位加法器则是由多个二位加法器组成的,能够对两个四位二进制数进行相加运算。

本文将深入探讨二位加法器芯片如何组成四位加法器,以及其在计算机科学中的重要性。

首先,我们要了解二位加法器的结构和工作原理。

二位加法器由两个输入端和两个输出端组成。

输入端分别连接两个待相加的二进制数的对应位,输出端则分别输出相加结果的和位和进位位。

在二位加法器中,和位的计算相当于对两个输入进行异或运算,而进位位的计算则相当于对两个输入进行与运算并与其前一个进位位进行或运算。

通过这样的运算,二位加法器可以实现对两个二进制数的相加。

接下来,我们要考虑如何将多个二位加法器组合成四位加法器。

四位加法器由四个二位加法器组成,其中每个二位加法器负责计算相应位置的和位和进位位。

具体来说,第一个二位加法器负责计算最低位的和位和进位位,第二个二位加法器负责计算次低位的和位和进位位,以此类推。

最终,四位加法器的输出端将输出四位二进制数的和位和进位位。

使用二位加法器芯片组成四位加法器的好处在于,它能够大大简化电路的设计和实现过程。

通过使用相同的二位加法器芯片,我们只需要将它们连接起来,就能够实现一个高效的四位加法器。

这不仅减少了硬件的成本和复杂性,还提高了电路的可靠性和可维护性。

事实上,二位加法器芯片组成四位加法器的原理可以进一步扩展到更高位数的加法器中。

通过将多个四位加法器连接在一起,我们可以实现八位加法器、十六位加法器,甚至更大位数的加法器。

这种层次化的设计思路使得我们能够灵活地构建各种不同大小的加法器,以满足不同的计算需求。

除了在数字电路中的应用,二位加法器芯片组成四位加法器也在计算机科学中扮演着重要的角色。

在计算机的运算器中,加法器是一个必不可少的部分,它负责处理两个二进制数的相加运算,并将结果输出给控制器。