状态机例子-自动售货机

生活中有限状态机

货币有0.5,1.0,机器可找零,每次投入一种硬币,机器可以输出货物,也可找零:

二,从

这仅仅只是投币这一动作的状态图,其实展开来说我觉得单顾客而言还有很多个动作状态,比如选择饮料这一动作,如下图:

选择

人本来就是一个复杂的个体,信息输入人脑后还会有一系列的状态。

二.售货机器来分析

售货机根据顾客的投币来找零和出货,售货机对顾客的输入进行识别后出货并判断顾客投币是否足够是否需要找零:

对于售货机,我觉得售货机也有很多个状态,比如,顾客选择饮料后按键,售货机会根据按键计算该吐出哪种饮料,然后饮料下的挡板收缩,该饮料就掉下来了:

三,从补货售货员来分析

补货员又分为两个部分,查看及取走钱币及查看及补充饮料:

自动售货机类图:

有限状态机是一种具有离散输入输出系统的模型,在任何时刻都处于一个特定的状态。对于事件驱动的程序设计,它是非常有用的设计模型。在某一个状态下有事件发生时,根换到下一个状态。

自动售货机我想从三个方面来分析它的有限状态机(以下是用例图):

一,从顾客来分析

《游戏智能》

实验报告

项目名称生活中的有限状态机

专业班级20121123

姓 名骆晓芳(2012137125)

实验成绩:

批阅教师:

2014年12月19 日

生活中的有限状态机——自(英语:Finite-state machine, FSM),又称有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。

离散数学有限自动机模型应用举例

离散数学有限自动机模型应用举例离散数学是数学的一个分支,主要研究离散对象和离散关系。

而有限自动机是离散数学中的重要概念之一,用于描述具有有限数量的状态和状态之间的转换关系。

有限自动机模型在计算机科学和其他领域中有着广泛的应用。

本文将从几个具体的应用案例来探讨离散数学有限自动机模型的应用。

案例一:自动售货机自动售货机是我们日常生活中常见的一种自动化设备。

它通过有限自动机模型来实现对商品的管理和售卖。

假设自动售货机有3个状态,分别为“待机”、“选择商品”和“完成交易”。

当用户投入硬币后,自动售货机会从“待机”状态转换为“选择商品”状态,用户可以通过按下相应按钮来选择商品。

一旦用户选定商品,自动售货机将通过有限自动机模型转换到“完成交易”状态,并同时释放商品和找零。

这个案例清晰地展示了有限自动机模型如何应用于自动售货机的控制。

案例二:电话拨号电话拨号也是离散数学有限自动机模型的一个应用。

在传统电话中,数字键盘上有10个数字按钮和几个特殊按钮(如*和#)。

每次按下一个按钮时,电话系统都会根据当前状态和按下的按钮进行状态转换。

例如,当你拨号时,初始状态为“待命”状态,按下数字按钮后,系统将从“待命”状态转移到“拨号中”状态,并显示所拨的号码。

这个过程中,电话系统一直在根据当前状态和按下的按钮进行状态转换,直到通话结束。

这种电话系统的设计正是基于离散数学有限自动机模型,它能够准确地响应用户的操作。

案例三:词法分析器在计算机科学中,词法分析器是编译器的一个基本组成部分,用于将源代码分解为有意义的元素(如标识符、关键字和运算符)。

离散数学有限自动机模型可以用来构建词法分析器。

通过使用有限自动机,可以将源代码作为输入,并根据代码的语法规则将其分解为不同的词法单元。

例如,当遇到空格时,词法分析器将从初始状态转换到“空格”状态,并且继续分析后续字符。

同样地,当遇到标识符或关键字时,词法分析器将进行相应的状态转换并识别它们。

事件驱动 状态机 实例讲解 -回复

事件驱动状态机实例讲解-回复什么是事件驱动?事件驱动(Event-driven)是一种计算机编程范例,它通过响应事件的方式来控制程序的执行流程。

事件驱动编程是一种反应性编程方法,它基于事件的发生而触发相应的处理流程。

在事件驱动的程序中,程序状态通常是静态的,只有当外部事件发生时,程序才会进入相应的处理流程,执行相关的代码。

事件驱动的编程模型可以适用于多种情况,如图形用户界面(GUI)开发、网络编程、服务器开发等。

在这些场景下,用户的操作、网络请求、外部设备的输入等都可以被视为事件,并通过事件驱动模型进行处理。

不同于传统的顺序编程模型,事件驱动模型具有以下几个特点:1. 程序按照事件顺序响应:程序会等待事件发生,然后根据事件的顺序依次进行处理。

事件驱动编程通常具有异步的特性,即不会一直等待事件的发生,而是可以同时处理多个事件。

2. 事件处理是离散的:每个事件都会有相应的处理流程,事件之间是相互独立的。

这使得程序能够更好地适应外部环境的变化。

3. 事件驱动编程具有高度的灵活性和可扩展性:由于事件驱动模型基于事件的发生来触发相应的处理流程,使得程序可以根据实际需求进行动态调整和扩展。

4. 事件驱动模型对并发和并行编程友好:事件驱动编程天然支持多线程、多任务并发执行。

不同的事件可以由不同的线程或进程处理,从而提高程序的执行效率和响应性。

什么是状态机?状态机(State machine)是一种将系统行为建模的数学模型。

它描述了一个系统的内部状态以及状态之间的转换规则。

状态机由一组状态和状态转移构成,状态表示系统所处的状态,转移表示状态之间的切换。

状态机可以分为两种类型:有限状态机(Finite-state machine,FSM)和无限状态机(Infinite-state machine)。

有限状态机中,状态的数量是有限的,系统的状态会在不同的输入条件下从一个状态转移到另一个状态,形成一个状态转移图。

无限状态机中,状态的数量是无限的,系统的状态可能具有连续性或无规律性。

有限状态机-售货机例子

S0

11 / 1 10 / 0

S1

11 / 0

米勒型状态机 状态转换图

01 / 0 1x/1 01 /1 1x /1 10 / 0

S3

输出与输入有关

01 / 0

S2

00 / 0

00 / 0

下一状态 输入

当前状态

状态译码 (下一状态组合逻组合逻辑)

输出

module vend_moore(Reset , Clk , D_in , D_out); ……

竞争冒险不能消除。

摩尔型状态机输入与输出隔离,输出稳定,能

测试分析

有效消除竞争冒险,是设计首选。

always @(current_state ) …… // 输出译码

always @(current_state ) D_out_moore= (current_state==S4); endmodule

通过测试平台进行功能仿真, 并与米勒型状态机进行对比。

测试分析

仿真结果分析:

米勒型状态机输出与当前状态和输入都有关,

……

S1:begin if (D_in[1] & D_in[0]) next_state<=S4; else if (D_in[1]) next_state<=S3; else if(D_in[0]) next_state<=S2; else next_state<=S1; end S2:begin ……

程序实现

always @(current_state or D_in) begin …… // 状态译码 end

always @(posedge Clk or posedge Reset) begin …… // 状态寄存 end always @(current_state ) …… // 输出译码 endmodule

SOC设计实验报告

#2 five_cents=0; //5 两个五分,一个十分 #20 five_cents=1; #2 five_cents=0; #10 five_cents=1; #2 five_cents=0; #10 ten_cents=1; #2 ten_cents=0; #10 $stop; end AUTOSEL AUTOSEL(five_cents,ten_cents,clk,rst_n,soda_out); Endmodule 测试波形图如下所示:

Wire Load Model Mode: Ie_reg[0]

(rising edge-triggered flip-flop clocked by clk)

Endpoint: out (output port clocked by clk)

Path Group: clk

1 Five

input rst;

output out; wire out;

=1 ten=

Five= 1 St2

reg [1:0]state;

1

parameter st0=2'b00,

st1=2'b01,

st2=2'b10,

st3=2'b11;

always@(posedge clk or negedge rst)

490.20 490.20

clock network delay (ideal)

20.00 510.20

clock uncertainty

-20.00 490.20

output external delay

-80.00 410.20

data required time

410.20

-----------------------------------------------------------

数字逻辑状态机例子

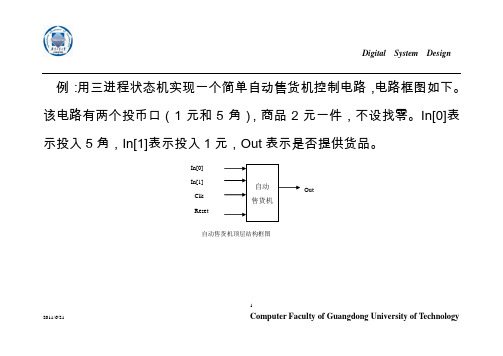

Digital System Design12011/6/21Computer Faculty of Guangdong University of Technology例:用三进程状态机实现一个简单自动售货机控制电路,电路框图如下。

该电路有两个投币口(1元和5角),商品2元一件,不设找零。

In[0]表示投入5角,In[1]表示投入1元,Out 表示是否提供货品。

Digital System Design22011/6/21Computer Faculty of Guangdong University of Technology根据题意,可分析出状态机的状态包括: S0(00001):初始状态,未投币或已取商品 S1(00010):投币5角 S2(00100):投币1元 S3(01000):投币1.5元 S4(10000):投币2元或以上用独热码表示状态编码,如上所示。

相应状态转换图如下(按Moore 状态机设计)。

Digital System Design32011/6/21Computer Faculty of Guangdong University of Technology自动售货机状态转换图Digital System Design42011/6/21Computer Faculty of Guangdong University of Technology设计代码第一个Always 块:状态转移。

Digital System Design52011/6/21Computer Faculty of Guangdong University of Technology第二个Always 块:状态转移的组合逻辑条件判断Digital System Design62011/6/21Computer Faculty of Guangdong University of Technology第三个Always 块:输出组合逻辑Digital System Design72011/6/21Computer Faculty of Guangdong University of Technology测试平台代码Digital System Design82011/6/21Computer Faculty of Guangdong University of Technology功能仿真结果Digital System Design92011/6/21Computer Faculty of Guangdong University of Technology综合结果。

有限状态机课程设计报告EDASodaMachine自动售货机

1有限状态机有限状态机(Finite State Machine )是一种具有内部记忆的抽象机器模型,是时序电路的一种,通过有限状态机课实现高效率高可靠逻辑控制。

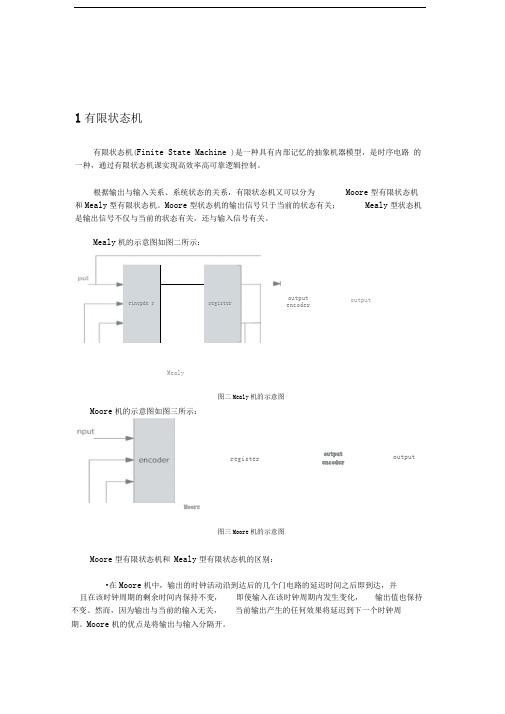

根据输出与输入关系、系统状态的关系,有限状态机又可以分为Moore型有限状态机和Mealy型有限状态机。

Moore型状态机的输出信号只于当前的状态有关;Mealy型状态机是输出信号不仅与当前的状态有关,还与输入信号有关。

Mealy机的示意图如图二所示:Mealy图二Mealy机的示意图Moore机的示意图如图三所示:Moore图三Moore机的示意图Moore型有限状态机和Mealy型有限状态机的区别:•在Moore机中,输出的时钟活动沿到达后的几个门电路的延迟时间之后即到达,并且在该时钟周期的剩余时间内保持不变,即使输入在该时钟周期内发生变化,输出值也保持不变。

然而,因为输出与当前的输入无关,当前输出产生的任何效果将延迟到下一个时钟周期。

Moore机的优点是将输出与输入分隔开。

einepde r registeroutputencoderoutputregisteroutputencoderoutput• 在Mealy 机中,因为输出是输入的函数,如果输入改变,则输出可以在下一个时钟周期的中间发生改变。

这使得Mealy 机比Moore 机,对输入变化的响应要早一个时钟周期,一旦输入信号或状态发生变化,输出信号随着输入信号变化。

• 实现同样功能,Moore 机要比Mealy 机需要更多的状态。

通过分析本次实验,利用Mealy 机更加容易理解,并且使用Moore 会使用更多的状态,所以本次实验使用Mealy 型有限状态机。

2 Soda Machine机的设计2.1 Soda Machine机的状态转换图Soda Machine 机的状态转换图如图四所示。

Soda Machine图四Soda Machine 机的状态转换图图中共有10个状态,为ST0 — ST9。

工程实训报告-Modelsim实验四-有限状态机之自动售货机-(1)

实验项目名称:有限状态机指导教师:实验日期:实验概述:【实验目的及实验设备】实验目的:(1)掌握有限状态机的应用方法。

(2)掌握有限状态机的静态测试方法,能够进行程序设计。

(3)学习测试模块的编写,综合和不同层次的仿真。

(4)用有限状态机设计一个自动售货机(饮料价格为2.5元)。

实验设备及仪器名称:CPU型号:英特尔*****************************操作系统类型:Windows XP SP3仿真软件:MAX Plus 2软件、Modelsim SE-64 10.0c实验内容及步骤:【实验原理及电路图】系统能够根据用户输入的硬币,判断钱币是否足够,当所投硬币达到或者超过购买者所选面值时,则根据顾客的要求自动售货,并找回剩余的硬币,然后回到初始状态,当所投硬币面值不够时,则给出提示,并通过一个复位键退回所投硬币。

然后回到初始状态。

该实验输入有4个clk,reset,表示投一元币y,表示投五角币w。

输出有2个,表示饮料出现的out和找五角钱的w_out.该实验共5个状态,s0:表示投币为0的状态,s1:表示投入5角的,s2:表示投入1元,s3:表示投入1.5元,s4:表示投入2元。

当投入2.5时out输出1,状态回到s0,当投入3元时out 和w_out都输出1,状态回到s0.【实验方案】(实验步骤,记录)1、打开Modelsim SE-64 10.0c软件。

else beginout=0;w_out=0;s=s4;endendcaseendendmodule测试程序:module shou;wire y;reg w;reg reset;reg clk;paramerer clkperiod=100;shouhuoji shou(y,w,reset,clk)initial beginw=0;clk=0;reset=1;#150 reset=0;#100 reset=1;endalways#(clkperiod/2) clk=~clk;always#(clkperiod+30) $random;initial $monitor(Stime, “y=%b”,y);endmodule3、编译并调试程序,出现错误立即修改直至无错误出现。

有限状态机-售货机例子

自动售货机

实例分析

实例分析

简易自动售货机控制电路

In[1]

(1元)

In[0]

(Hale Waihona Puke 角)Clk(时钟)

Reset

(重置)

售货机 控制电路

D_out

(提供商品)

In / D_out 00/0

xx/1

状态分析

01/0

00/0

11/0

S0

S1

10/0 11/0

01/0 10/0

1x/0

00/0

01/0 1x/0

end S2:begin ……

输输入入

√状状态态译译码码

下下一一状状态态

√状状态态寄寄存存

当当前前状状态态

输输出出译译码码

输输出出

时时钟钟

always @(posedge Clk or posedge Reset) begin …… // 状态寄存 end

完整代码在教材 p374

always @(posedge Clk or posedge Reset) begin if (Reset) current_state<=S0; else current_state<=next_state; end

自动售货机实例分析实例分析简易自动售货机控制电路售货机控制电路clk时钟reset重置dout提供商品010xx11x0000010100000000010000100110110dout状态分析0101x0010xx11x0000010100000000010000100110110dout摩尔型状态机状态转换图0101x0输出与输入无关只跟当前状态有关s0s2s3s1011x100米勒型状态机状态转换图1x输出与输入有关程序实现状态译码下一状态组合逻辑状态寄存输出译码输出组合逻辑时钟输出输入下一状态当前状态modulevendmooreresetalwayscurrentstatedinbegin状态译码endalwaysposedgeclkposedgeresetbegin状态寄存endalwayscurrentstate输出译码endmodulealwayscurrentstatedinbegin状态译码endalwaysposedgeclkposedgeresetbegin状态寄存endalwayscurrentstatecasecurrentstates0

简单自动售货机VerilogHDL程序

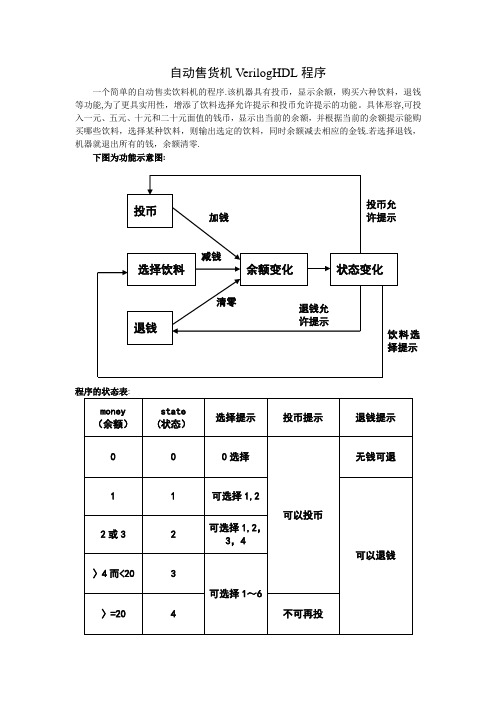

自动售货机VerilogHDL程序一个简单的自动售卖饮料机的程序.该机器具有投币,显示余额,购买六种饮料,退钱等功能,为了更具实用性,增添了饮料选择允许提示和投币允许提示的功能。

具体形容,可投入一元、五元、十元和二十元面值的钱币,显示出当前的余额,并根据当前的余额提示能购买哪些饮料,选择某种饮料,则输出选定的饮料,同时余额减去相应的金钱.若选择退钱,机器就退出所有的钱,余额清零.下图为功能示意图:程序的状态表:程序中包含了一个状态机,定义了一个任务(task)和函数(function),用该任务调用了该函数,使用若干分支语句,详见附后源程序和测试程序。

附上程序编译仿真图:源程序如下:`define one 3'b001`define five 3'b010`define ten 3'b011`define twenty 3’b100module automart(money,state,moneyout,coinable,adrkable,bdrkable,cdrkable,drkout1,drkout2,drkout3,drkout4,drkout5,drkout6,coin,clk,reset,moneyback,choice1,choice2,choice3,choice4,choice5,choice6);input[2:0]coin;//投币输入,分为1、5、10、20元四种输入input clk,reset,moneyback,choice1,choice2,choice3,choice4,choice5,choice6;//moneyback为退钱输入,choice1~6是饮料选择output moneyout,coinable,adrkable,bdrkable,cdrkable,drkout1,drkout2,drkout3,drkout4,drkout5,drkout6;//依次为退钱输出,投币许可提示,饮料选择许可,6种饮料输出output[2:0] state;//状态记录output[7:0] money;//余额显示reg[7:0] money;reg[2:0] state;reg moneyout,coinable,backable,adrkable,bdrkable,cdrkable; parameter A=3'b000,B=3'b001,C=3'b010,D=3'b011,E=4’b100;assign drkout1=choice1&adrkable;assign drkout2=choice2&adrkable;assign drkout3=choice3&bdrkable;assign drkout4=choice4&bdrkable;assign drkout5=choice5&cdrkable;assign drkout6=choice6&cdrkable;always@(posedge clk)repeat(1)@(posedge clk)if (!reset)beginstate<=A;money=0;moneyout=0;endelsebegincase(state)A:begin//初始状态A,可投币进入别的状态coinable=1;backable=0;adrkable=0;bdrkable=0;cdrkable=0;endB: begin//状态B,只能买1元的饮料,可退钱或投币coinable=1;backable=1;adrkable=1;bdrkable=0;cdrkable=0;endC: begin//状态C,可买1或2元的饮料,退钱或投币coinable=1;backable=1;adrkable=1;bdrkable=1;cdrkable=0;endD:begin//状态D,可买三档价格饮料,可退钱或投币coinable=1;backable=1;adrkable=1;bdrkable=1;cdrkable=1;endE:begin//状态E,可买三档价格饮料,可退钱,不可继续投钱coinable=0;backable=1;adrkable=1;bdrkable=1;cdrkable=1;enddefault: state=A;endcasecondition(money,state,coin,coinable);//调用任务endalways@(negedge drkout1 or negedge drkout2)money=money—8’h01;//买1元的饮料,余额减1元always@(negedge drkout3 or negedge drkout4)money=money—8'h02;//买2元的饮料,余额减2元always@(negedge drkout5 or negedge drkout6)money=money—8'h04;//买4元的饮料,余额减4元always@(negedge moneyback)beginif(backable)beginmoneyout=1;money=0;//选择退钱,则推出金钱,余额清零endelsemoney=money+0;endtask condition;//该任务可以判断余额的改变,状态切换inout[7:0] moneycon;inout[2:0] statecon;input[2:0] coincon;input coinablecon;beginif (coinablecon)//允许投币时begincase (coincon)//根据投币面值改变余额,切换状态`one : moneycon=moneycon+8'h01;`five :moneycon=moneycon+8'h05;`ten : moneycon=moneycon+8'h0a;`twenty :moneycon=moneycon+8'h14;default:moneycon=moneycon+0;//无投币则余额不变endcasestatecon=condition_s(moneycon);//调用函数endelse if (moneycon〈8’h14)//不允许投币时,根据余额变化statecon=condition_s(moneycon);//直接切换状态endendtaskfunction [2:0] condition_s;//根据余额的值切换状态的函数input [7:0] money_s;reg [7:0]money_s;beginif (money_s==0)condition_s=A;else if(money_s==8’h01)condition_s=B;else if(money_s==8’h02||money_s==8’h03)condition_s=C;else if(money_s〉=8’h04&&money_s〈8’h14)condition_s=D;else condition_s=E;endendfunctionendmodule测试程序如下:`timescale 100ns/1ns`define clk_cycle 50module test;reg moneyback,choice1,choice2,choice3,choice4,choice5,choice6; reg [2:0] coin;reg clk,reset;wire[7:0] money;wire[2:0]state;wire moneyout,coinable,adrkable,bdrkable,cdrkable,drkout1,drkout2,drkout3,drkout4,drkout5,drkout6;parameter one=3’b001,five=3’b010,ten=3'b011,twenty=3'b100;always #`clk_cycle clk= ~clk;initialbegincoin=0;moneyback=0;clk=0;choice1=0;choice2=0;choice3=0;choice4=0;choice5=0;choice6=0;reset=1;#10 reset=0;#200 reset=1;#400 coin=one;//投币1元,#220 coin=0;#200 coin=one;//投1元,余额2元#220 coin=0;#200 coin=five;//投5元,余额7元#220 coin=0;#200 coin=twenty;//投20元,余27#220 coin=0;#200 choice1=1;//买1元饮料,余26#220 choice1=0;#200 choice3=1;//买2元饮料,余24#220 choice3=0;#200 choice4=1;//买2元饮料,余22#220 choice4=0;#200 choice5=1;//买4元饮料,余18#220 choice5=0;#200 choice6=1;//买4元饮料,余14#220 choice6=0;#200 choice6=1;//买4元饮料,余10#220 choice6=0;#200 choice6=1;//买4元饮料,余6#220 choice6=0;#200 choice6=1;//买4元饮料,余2#220 choice6=0;#200 coin=five;//投5元,余7#220 coin=0;#200 moneyback=1;//退钱#220 moneyback=0;endautomart m(.money(money),。

状态机例子-自动售货机

Digital System Design12011/6/21Computer Faculty of Guangdong University of Technology例:用三进程状态机实现一个简单自动售货机控制电路,电路框图如下。

该电路有两个投币口(1元和5角),商品2元一件,不设找零。

In[0]表示投入5角,In[1]表示投入1元,Out 表示是否提供货品。

自动 售货机In[0] In[1] Clk ResetOut自动售货机顶层结构框图Digital System Design22011/6/21Computer Faculty of Guangdong University of Technology根据题意,可分析出状态机的状态包括: S0(00001):初始状态,未投币或已取商品 S1(00010):投币5角 S2(00100):投币1元 S3(01000):投币1.5元 S4(10000):投币2元或以上用独热码表示状态编码,如上所示。

相应状态转换图如下(按Moore 状态机设计)。

Digital System Design32011/6/21Computer Faculty of Guangdong University of Technologyxx/101/0 10/010/001/001/0S1S0S4S2Reset自动售货机状态转换图10/0S301/0x1/0Digital System Design42011/6/21Computer Faculty of Guangdong University of Technology设计代码第一个Always 块:状态转移。

`timescale 1ns/100psmodule saler_3always(Reset,Clk,In,Out); input Clk,Reset; input [1:0] In; output Out; reg Out;reg [4:0] state, next_state;parameter S0=5'b00001, S1=5'b00010, S2=5'b00100, S3=5'b01000,S4=5'b10000; always @(posedge Clk or posedge Reset)Digital System Design52011/6/21Computer Faculty of Guangdong University of Technologybegin if (Reset) state<=S0; elsestate<=next_state; end第二个Always 块:状态转移的组合逻辑条件判断always @(state or In) begin case(state)S0:begin if (In[1]) next_state<=S2;Digital System Design62011/6/21Computer Faculty of Guangdong University of Technologyelse if(In[0]) next_state<=S1;elsenext_state<=S0; end S1:begin if (In[1]) next_state<=S3; else if(In[0]) next_state<=S2; elsenext_state<=S1;end S2:begin if (In[1]) next_state<=S4; else if(In[0]) next_state<=S3;elsenext_state<=S2; end S3:beginif (In[0]|In[1]) next_state<=S4;Digital System Design72011/6/21Computer Faculty of Guangdong University of Technologyelsenext_state<=S3; end S4:beginnext_state<=S0;enddefault:next_state<=S0; endcase end第三个Always 块:输出组合逻辑always @(state ) begincase(state) S0:beginOut<=0; end S1:begin Out<=0;Digital System Design82011/6/21Computer Faculty of Guangdong University of Technologyend S2:beginOut<=0;end S3:begin Out<=0; endS4:beginOut<=1;enddefault:Out<=0; endcase end endmodule测试平台代码Digital System Design92011/6/21Computer Faculty of Guangdong University ofTechnology`timescale 1ns/1ns module testbench_saler; reg clk,reset; reg [1:0] in; wire out;parameter DELY=20; saler_3alwaystb(.Clk(clk),.Reset(reset),.In(in),.Out(out)); always #(DELY/2) clk = ~clk; initial beginclk=0; reset=0;#20 reset=1;#20 reset=0;endinitial begin in=0; repeat(20)#20 in=$random; endDigital System Design102011/6/21Computer Faculty of Guangdong University ofTechnologyinitial #400 $finish;endmodule功能仿真结果Digital System Design 112011/6/21 Computer Faculty of Guangdong University of Technology综合结果Digital System Design Array122011/6/21 Computer Faculty of Guangdong University ofTechnology。

自动售货机用例(图)

自动售货机用例图

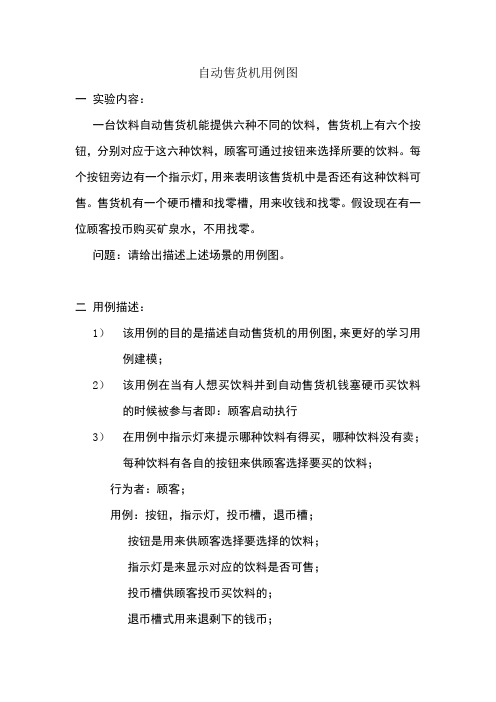

一实验内容:

一台饮料自动售货机能提供六种不同的饮料,售货机上有六个按钮,分别对应于这六种饮料,顾客可通过按钮来选择所要的饮料。

每个按钮旁边有一个指示灯,用来表明该售货机中是否还有这种饮料可售。

售货机有一个硬币槽和找零槽,用来收钱和找零。

假设现在有一位顾客投币购买矿泉水,不用找零。

问题:请给出描述上述场景的用例图。

二用例描述:

1)该用例的目的是描述自动售货机的用例图,来更好的学习用例建模;

2)该用例在当有人想买饮料并到自动售货机钱塞硬币买饮料的时候被参与者即:顾客启动执行

3)在用例中指示灯来提示哪种饮料有得买,哪种饮料没有卖;

每种饮料有各自的按钮来供顾客选择要买的饮料;

行为者:顾客;

用例:按钮,指示灯,投币槽,退币槽;

按钮是用来供顾客选择要选择的饮料;

指示灯是来显示对应的饮料是否可售;

投币槽供顾客投币买饮料的;

退币槽式用来退剩下的钱币;

三自动售货机的对象图:

四用例图:

指示灯提示饮料是否可售

吐饮料

五实验小结:

1)在本次实验中初次使用Rational Rose来画用例图,在画用例图之间要寻找并确定行为者,以及寻找并确定用例;

2)一个用例表示系统中一个与特定行为者相关的完整功能。

用例通过关联与行为者链接,关联指出一个用例与哪些行

为者交互,所以在确定了行为者和用例之后,要理清楚各

个用例之间的关系,在画用例图时候才能够顺手,才能过

完成自动售货机系统中的一系列动作,才能特定行为者一

个可观擦到的结果值;。

自动售货机控制系统VHDL有限状态机实现

自动售货机控制系统VHDL有限状态机实现1 引言有限状态机FSM(Finite State Machine)及其设计技术是实用数字系统设计中实现高效率、高可靠逻辑控制的重要途径。

传统的状态机设计方法需进行繁琐的状态分配、绘制状态表、化简次态方程等,而利用VHDL可以避免这些繁琐的过程,直接利用状态转换图进行状态机的描述,所有的状态均可表达为CASE_WHEN结构中的一条CASE语句,而状态的转移则通过IF_THEN_ELsE语句实现。

此外,与VHDL的其它描述方式相比,状态机的VHDL表述丰富多样,程序层次分明,结构清晰,易读易懂;在排错、修改和模块移植方面也有其独到的特点。

2 自动售货机控制系统的实现2.1 自动售货机功能描述及控制系统组成设计一个自动售货机的逻辑控制电路。

它有两个投币口分别为一元投币口和五角投币口,假设每次只能投入一枚一元或五角硬币,投入一元五角硬币后机器自动给出一瓶矿泉水,投入两元硬币后,在给出一瓶矿泉水的同时找回一枚五角的硬币。

图1为自动售货机控制系统方框图,由投币信号处理模块和功能控制模块组成。

2.2 自动售货机控制功能的状态描述取投币信号为输入逻辑变量,投入一枚一元硬币时用A=1表示,未投入时A=0。

投入一枚五角硬币用B=1表示,未投入时B=0。

给出矿泉水和找钱为两个输出变量,分别用Z和Y表示,给出矿泉水时Z=1,不给时Z=0,找回一枚五角硬币时Y=1,不找时Y=0。

根据上面的功能描述,可用三个状态S0,S1,S2表示,未投币前的初始状态为S0,投入五角硬币以后为S1,投入一元硬币后(包括投入一枚一元硬币和投入两枚五角硬币的情况)为S2,再投入一枚五角硬币后电路返回S0,同时输出为Z=1,Y=0;如果投入的是一枚一元硬币,则电路也应能返回S0,同时输出为Z=1,Y=1。

根据上面的分析可得到状态转换图如图2所示。

2.3 自动售货机功能控制模块的VHDL实现根据图2所示的状态转换图,用VHDL语言中的CASE_WHEN结构和IF_THEN_ELSE语句实现控制功能,源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY shj_ctrl ISPORT(A,B:IN STD_LOGIC;clk:IN STD_LOGIC;Z,Y:OUT STD_LOGIC);END shj_ctrlARCHITECTURE beha OF shi_ctrl ISTYPE states IS(S0,S1,S2);SIGNAL state:states;SIGNAL X:STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINX<=A&B;PROCESS(x,state)BEGINIF rising_edge(clk) THENCASE state ISWHEN S0=>Z<='0';Y<='0';IF(X="01")THENstate<=s1;ELSIF(X="10")THENstate<=s2;ELSEstate<=s0;END IF;WHEN S1=>Z<='0';Y<='0';IF(X="01")THENstate<=s2;ELSIF(X="10")THENstate<=S0;Z<='1';Y<='0';ELSEstate<=s1;END IF;WHEN S2=>Z<='0';Y<='0';IF(X="01")THENstate<=S0;Z<='1';Y<='0';ELSIF(X="10")THENstate<=s0;Z<='1';Y<='1';ELSEstate<=s2;END IF;END CASE;END IF;END PROCESS;END beha;c上面程序中,A、B分别为一元硬币和五角硬币驱动信号,Z为矿泉水输出信号,Y为找钱输出信号。

用C语言实现自动售货机

⽤C语⾔实现⾃动售货机⾃动售货机如图所⽰的简易⾃动售货机,物品架1、2上共有10样商品,按顺序进⾏编号,分别为1-10。

同时标有价格与名称,- ⼀个编号对应⼀个可操作按钮,供选择商品使⽤。

如果物架上的商品被⽤户买⾛,储物柜中会⾃动取出商品送到物架上,保证物品架上⼀定会有商品.⽤户可以⼀次投⼊较多钱币,并可以选择多样商品,售货机可以⼀次性将商品输出并找零钱。

⽤户购买⽅法:(1)放⼊钱币,⽤户可以以此放⼊多个纸币,⾯额可以是1元、2元、>5元、10元。

售货机会统计总⾦额并显⽰。

(2)依次输⼊要购买的产品,可购买多个产品,售货机⾃动判断余额,若余额不⾜,则找零后退出程序。

若需⾃主退出需按退出按钮,程序中⽤输⼊“-1表⽰”。

售货机本着⼈性化原则,绝不会私吞⽤户钱,也不会⽩送给⽤户商品。

因此在选择货物号时,要注意以下⼏个点:1.若什么都不买,⽤户投⼊的钱全部将退回;2.若购买商品后还有余额,但⽤户⾃主退出程序,退回余额;3.若⽤户购买货物时余额不⾜,将停⽌购买此商品,退回余额代码如下:4.钱正好花光,没有余额,结束程序。

#include<stdio.h>#define N 10int sum=0;int sum1;typedef struct sell{int num;char name[20];int price;}sell;void main(){int i,c,s;int s1=0,s2=0,s3=0,s4=0,s5=0,s6=0,s7=0,s8=0;//记录商品购买数量sell se[N]={{1,"Table-water",1},{2,"Table-water",1},{3,"Table-water",1},{4,"Coca-Cola",2},{5,"Milk",2},{6,"Beer",3},{7,"Orange-Juice",3},{8,"Sprite",3},{9,"Oolong-Tea",4},{10,"Green-Tea",4}}; //售货机装⼊商品do {printf("Please put in coins:");scanf("%d",&c); //投币if(c==1||c==2||c==5||c==10)sum=sum+c;else if(c==-1) break;elseprintf("error!\n");}while(c!=-1);printf("Total:%d yuan\n",sum);printf("Please select the goods serial number:");scanf("%d",&s); //选择商品号se[-2].price =0;sum1=sum-se[s-1].price ; //第⼀个选的商品超过投币数if(sum1<0||s==-1) printf("Not enough money!\n");else sum=sum1;while(sum>=0&&s!=-1) //什么都没买或者钱够但是不想买了{if(sum>=0){ //钱花光了for(i=0;i<3;i++)if(s==se[i].num )s1++;for(i=3;i<N;i++){if(s==se[i].num &&i==3) {s2++;break;}else if(s==se[i].num &&i==4) {s3++;break;}else if(s==se[i].num &&i==5) {s4++;break;}else if(s==se[i].num &&i==6) {s5++;break;}else if(s==se[i].num &&i==7) {s6++;break;}else if(s==se[i].num &&i==8) {s7++;break;}else if(s==se[i].num &&i==9) {s8++;break;}}printf("There is still %d yuan left\n",sum );printf("Please select the goods serial number:");scanf("%d",&s);sum1=sum-se[s-1].price ; //最后⼀个商品钱不够if(sum1<0||s==-1) {printf("Not enough money!\n");break;}sum=sum1;}else printf("Not enough money!\n");}/*输出已购买商品名及数量*/if(s1!=0) printf("%s:%d\n",se[0].name ,s1);if(s2!=0) printf("%s:%d\n",se[3].name ,s2);if(s3!=0) printf("%s:%d\n",se[4].name ,s3);if(s4!=0) printf("%s:%d\n",se[5].name ,s4);if(s5!=0) printf("%s:%d\n",se[6].name ,s5);if(s6!=0) printf("%s:%d\n",se[7].name ,s6);if(s7!=0) printf("%s:%d\n",se[8].name ,s7);if(s8!=0) printf("%s:%d\n",se[9].name ,s8);if(sum>=0) printf("change:%d yuan\n",sum);//输出余额}运⾏结果:以上就是本⽂的全部内容,希望对⼤家的学习有所帮助,也希望⼤家多多⽀持。

自动售货机 verilog

SOPC及EDA技术课程结业报告题目:基于状态机的自动售货机设计院(系)电气工程及其自动化姓名学号班号基于状态机的自动售货机设计一.实验目的1. 学习FPGA入门知识,了解FPGA的编程形式;2. 掌握Quartus II的使用步骤;3. 掌握基于状态机原理的自动售货机设计过程。

二.实验原理自动售货机是可完成无人自动售货,集光、机、电一体化的商业自动化设备。

自动售货机不受任何场地限制,方便快捷,可以每天24小时售货,因此深受上班族的欢迎,很多城市的公共场所里面都放置有自动售货机,出售的商品五花八门,从饮料、零食、香烟、糖果,到牙刷、方便面、自动照相机。

近年来,我国的自动售货机行业突飞猛进:在汽车总站、商厦、医院、小区、学校等地区纷纷涌现出自动售货机的踪迹。

这种方便快捷的购物方式越来越受到人们的青睐,同时也是现代化城市配套设施的需求。

因为自动售货机作为社会上完成商品零售和综合服务的独立设施,所以必须要求它的结构可靠、稳定而且执行效率高。

传统的自动售货机控制系统采用单片机作为控制核心,这样不仅会在输入输出接口上做大量的工作,而且系统的抗干扰性也比较差。

可编程控制器(Programmable Logical Controller,简称PLC)是综合了计算机技术、自动控制技术和通讯技术而发展起来的一种新型的工业控制装置,它具有可靠性高、编程简单、维护方便等优点,已在工业控制领域得到广泛地应用。

PLC是以CPU为核心, 综合了计算机技术和通信技术发展起来的一种通用的工业自动控制装置, 是现代工业控制的三大支柱(PLC、机器人和CAD/CAM) 之一。

PLC的工作原理与计算机的工作原理基本是一致的, 可以简单地表述为在系统程序的管理下, 通过运行应用程序完成用户任务。

但是PLC也有它自己的特点, PLC在确定了工作任务, 装入了专用程序后成为一种专用机, 它采用循环扫描工作方式, 系统工作任务管理及应用程序执行都是用循环扫描方式完成的。

状态机自动售货机

找零口

投币口

出 货 口

2020/4/29

#

6

1、需求分析

自动售货机的VHDL设计。

已投入0元 S0 已投入0.5元 S1

要求:

五种状态 已投入1元 S2

货物单价:1.5元 两种硬币:1元或0.5元 每次可投入一枚硬币 可以输出货物 也可能找零

已投入1.5元 S3

已投入2元 S4

三种输入:0元 0.5元 1元

ARCHITECTURE be OF ZD IS

TYPE fsm_st IS (S0,S1,S2,S3,S4);

SIGNAL current_state,next_state:fsm_st;

BEGIN

reg:PROCESS(RST,clk)

BEGIN

IF RST='1' THEN current_state<=S0;

reg:PROCESS(RST,clk)

--时序进程

BEGIN CASE current_state IS

……

WHEN S0=>

End proceWsHs;EN S1=>

com:PROCWEHSESN(cSu2rr=e>nt_state,IN1)--组合进程

BEGIN WHEN S3=>

Y<…=…"00"; WHEN S4=>

clk reset state_inputs

PROCESS REG

3、编程及仿真

FSM: s_machine

current_state next_state

PROCESS COM

comb_outputs

2020/4/29

python设计模式之状态模式

python设计模式之状态模式python设计模式之状态模式⾯向对象编程着⼒于在对象交互时改变它们的状态。

在很多问题中,有限状态机(通常名为状态机)是⼀个⾮常⽅便的状态转换建模(并在必要时以数学⽅式形式化)⼯具。

⾸先,什么是状态机?状态机是⼀个抽象机器,有两个关键部分,状态和转换。

状态是指系统的当前(激活)状况。

例如,假设我们有⼀个收⾳机,其两个可能的状态是在调频波段( FM)或调幅波段( AM)上调节。

另⼀个可能的状态是从⼀个FM/AM⽆线电台切换到另⼀个。

转换是指从⼀个状态切换到另⼀个状态,因某个事件或条件的触发⽽开始。

通常,在⼀次转换发⽣之前或之后会执⾏⼀个或⼀组动作。

假设我们的收⾳机被调到107 FM⽆线电台,⼀次状态转换的例⼦是收听⼈按下按钮切换到107.5 FM。

状态机的⼀个不错的特性是可以⽤图来表现(称为状态图),其中每个状态都是⼀个节点,每个转换都是两个节点之间的边。

下图展⽰了⼀个典型操作系统进程的状态图(不是针对特定的系统)。

进程⼀开始由⽤户创建好,就进⼊“已创建/新建”状态。

这个状态只能切换到“等待”状态,这个状态转换发⽣在调度器将进程加载进内存并添加到“等待/预备执⾏”的进程队列之时。

⼀个“等待”进程有两个可能的状态转换:可被选择⽽执⾏(切换到“运⾏”状态),或被更⾼优先级的进程所替代(切换到“换出并等待”状态)。

进程的其他典型状态还包括“终⽌”(已完成或已终⽌)、“阻塞”(例如,等待⼀个I/O操作完成)等。

需要注意,⼀个状态机在⼀个特定时间点只能有⼀个激活状态。

例如,⼀个进程不可能同时处于“已创建”状态和“运⾏”状态。

状态机可⽤于解决多种不同的问题,包括⾮计算机的问题。

⾮计算机的例⼦包括⾃动售货机、电梯、交通灯、暗码锁、停车计时器、⾃动加油泵及⾃然语⾔⽂法描述。

计算机⽅⾯的例⼦包括游戏编程和计算机编程的其他领域、硬件设计、协议设计,以及编程语⾔解析。

1. 现实⽣活的例⼦这⾥再⼀次提到零⾷⾃动售货机(在之前的第10章中见过),它也是⽇常⽣活中状态模式的⼀个例⼦。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Digital System Design

1

2011/6/21

Computer Faculty of Guangdong University of Technology

例:用三进程状态机实现一个简单自动售货机控制电路,电路框图如下。

该电路有两个投币口(1元和5角),商品2元一件,不设找零。

In[0]表示投入5角,In[1]表示投入1元,Out 表示是否提供货品。

自动 售货机

In[0] In[1] Clk Reset

Out

自动售货机顶层结构框图

Digital System Design

2

2011/6/21

Computer Faculty of Guangdong University of Technology

根据题意,可分析出状态机的状态包括: S0(00001):初始状态,未投币或已取商品 S1(00010):投币5角 S2(00100):投币1元 S3(01000):投币1.5元 S4(10000):投币2元或以上

用独热码表示状态编码,如上所示。

相应状态转换图如下(按Moore 状态机设计)。

Digital System Design

3

2011/6/21

Computer Faculty of Guangdong University of Technology

xx/1

01/0 10/0

10/0

01/0

01/0

S1

S0

S4

S2

Reset

自动售货机状态转换图

10/0

S3

01/0

x1/0

Digital System Design

4

2011/6/21

Computer Faculty of Guangdong University of Technology

设计代码

第一个Always 块:状态转移。

`timescale 1ns/100ps

module saler_3always(Reset,Clk,In,Out); input Clk,Reset; input [1:0] In; output Out; reg Out;

reg [4:0] state, next_state;

parameter S0=5'b00001, S1=5'b00010, S2=5'b00100, S3=5'b01000,S4=5'b10000; always @(posedge Clk or posedge Reset)

Digital System Design

5

2011/6/21

Computer Faculty of Guangdong University of Technology

begin if (Reset) state<=S0; else

state<=next_state; end

第二个Always 块:状态转移的组合逻辑条件判断

always @(state or In) begin case(state)

S0:begin if (In[1]) next_state<=S2;

Digital System Design

6

2011/6/21

Computer Faculty of Guangdong University of Technology

else if(In[0]) next_state<=S1;

else

next_state<=S0; end S1:begin if (In[1]) next_state<=S3; else if(In[0]) next_state<=S2; else

next_state<=S1;

end S2:begin if (In[1]) next_state<=S4; else if(In[0]) next_state<=S3;

else

next_state<=S2; end S3:begin

if (In[0]|In[1]) next_state<=S4;

Digital System Design

7

2011/6/21

Computer Faculty of Guangdong University of Technology

else

next_state<=S3; end S4:begin

next_state<=S0;

end

default:next_state<=S0; endcase end

第三个Always 块:输出组合逻辑

always @(state ) begin

case(state) S0:begin

Out<=0; end S1:begin Out<=0;

Digital System Design

8

2011/6/21

Computer Faculty of Guangdong University of Technology

end S2:begin

Out<=0;

end S3:begin Out<=0; end

S4:begin

Out<=1;

end

default:Out<=0; endcase end endmodule

测试平台代码

Digital System Design

9

2011/6/21

Computer Faculty of Guangdong University of

Technology

`timescale 1ns/1ns module testbench_saler; reg clk,reset; reg [1:0] in; wire out;

parameter DELY=20; saler_3always

tb(.Clk(clk),.Reset(reset),.In(in),.Out(out)); always #(DELY/2) clk = ~clk; initial begin

clk=0; reset=0;

#20 reset=1;

#20 reset=0;

end

initial begin in=0; repeat(20)

#20 in=$random; end

Digital System Design

10

2011/6/21

Computer Faculty of Guangdong University of

Technology

initial #400 $finish;

endmodule

功能仿真结果

Digital System Design 11

2011/6/21 Computer Faculty of Guangdong University of Technology

综合结果

Digital System Design Array

12

2011/6/21 Computer Faculty of Guangdong University of

Technology。