时序约束总结

时序约束的概念

时序约束的概念

时序约束是指在设计和开发硬件或软件系统时,对于其中的各个元件或操作的时间关系的限制要求。

它用来确保系统在特定的时间范围内以期望的顺序和时间间隔进行操作。

时序约束在各个层面的设计中都有应用,包括电子电路设计、数字系统设计、通信协议设计等。

时序约束可以包括以下几个方面:

1.时钟频率和时钟沿:为了实现正确的操作顺序,时序约束会定义系统中的时钟频率和时钟沿的要求。

这可以保证各个元件在时钟信号的控制下按照预期的时序进行操作。

2. 时序延迟:时序约束可以规定不同元件或操作之间的最大或最小延迟要求。

这可以确保信号在指定的时间范围内到达目标元件,避免信号延迟导致的系统故障或性能下降。

3. 时序关系:时序约束可以定义不同元件或操作之间的时间关系,如顺序、并行和同步等。

这确保了系统在不同元件之间的通信和操作按照特定的时间顺序进行。

4. 时序约束检查:通过时序约束检查工具,可以对设计中的时序约束进行验证。

时序约束

在进行FPGA的设计时,经常会需要在综合、实现的阶段添加约束,以便能够控制综合、实现过程,使设计满足我们需要的运行速度、引脚位置等要求。

通常的做法是设计编写约束文件并导入到综合实现工具,在进行FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。

下面主要总结一下Xilinx FPGA时序约束设计和分析。

一、周期约束周期约束是Xilinx FPGA 时序约束中最常见的约束方式。

它附加在时钟网线上,时序分析工具会根据周期约束来检查时钟域内所有同步元件的时序是否满足需求。

周期约束会自动的寄存器时钟端的反相。

如果相邻的两个元件的时钟相位是相反的,那么它们之间的延迟将被默认的限制成周期约束的一半。

在进行周期约束之前,必须对电路的时钟周期明了,这样才不会出现约束过松或者过紧的现象。

一般情况下,设计电路所能达到的最高运行频率取决于同步元件本身的Setup Time 和Hold Time,以及同步元件之间的逻辑和布线延迟。

周期约束一般是使用下面的约束方法:1、period_item PERIOD=period {HIGH|LOW} [high_or low_item]其中,period_item可以是NET或TIMEGRP,分别代表时钟线名称net name或元件分组名称group-name。

用NET表示PERIOD约束作用到名为“net name”的时钟网线所驱动的同步元件上,用TIMEGRP表示PERIOD约束作用到TIMEGRP所定义的分组(包括FFS、LATCH和RAM等同步元件)上。

period是目标时钟周期,单位可以是ps、ns、μS和ms 等。

HIGH|LOW指出时钟周期中的第1个脉冲是高电平还是低电平,high or low time为HIGH LOW指定的脉冲的持续时间,默认单位是ns。

如果没有该参数,时钟占空比是50%。

例如,NET SYS_CLK PERIOD=10 ns HIGH 4ns2、NET“clock net name”TNM_NET=“timing group name”;TIMESPEC“TSidentifier”=PERIOD “TNM reference”period {HIGH | LOW} [high or low item]INPUT_JITTER value;很多时候为了能够定义比较复杂的派生关系的时钟周期,就要使用该方法。

第九章时序约束

3、 输出延迟的设定

这种路径的约束是为了让FPGA设计工具能够优化FPGA内部从

最后一级寄存器到输出端口的路径,确保其输出的信号能够被 下一级芯片正确的采到。约束名称:output delay 约束条件的影响主要有3个因素:外部芯片的Tsu,电路板上信 号延迟Tpd,时钟延迟Tclk. Tsu的参数通常需要查外部芯片的数 据手册。 计算公式:output delay = Tsu+Tpd-Tclk. 例如:系统时钟100MHz, 电路板上最大延迟2ns, 时钟最大延迟 1.7ns, Tsu 1ns, 输出延迟的值: max output delay = 1+21.7=1.3ns . 这个参数的含义是指 让FPGA的设计工具把最后一级 寄存器到输出端口之间的路径延迟(包括门延迟和线延迟)控 制在 10ns-1.3ns=8.7ns 以内。

指一个同源时钟到达两个不同的寄存器时钟端 的时间偏移

Slack

表示设计是否满足时序的一个称谓,正的slack表示 满足时序(时序的余量),负的slack表示不满足时 序(时序的欠缺量)。

Slack = Required clock period – Actual clock

period

Slack:Setup slack

Setup Slack = Slack clock period – (Micro tCO+ Data Delay + Micro tSU)

Slack:hold slack

hold slack= (Micro tCO+ Data Delay + Micro

th)-(B-A)

Quartus 工具运行时序分析

时序约束路径

时序约束主要围绕4种时序路径来进行设置: ★从输入端口到寄存器 ★从寄存器到寄存器

fpga的时序约束

fpga的时序约束FPGA的时序约束时序约束是在FPGA设计中非常重要的一项工作,它用于确保电路在特定的时钟频率下能够正常工作。

在设计中,时序约束可以指定信号的到达时间、时钟的周期、时钟与数据的关系等,以保证电路的正确性和性能。

一、时序约束的作用时序约束的作用主要有以下几点:1. 确保电路在特定的时钟频率下能够正常工作;2. 优化电路的性能,提高工作频率;3. 避免电路中的时序违反,如时钟抖动、时钟突变等;4. 提供给综合工具和布局布线工具,以使其能够对电路进行优化和布局布线。

二、时序约束的类型时序约束可以分为以下几种类型:1. 输入时序约束:指定输入信号的到达时间,以确保电路能够正确地捕获和处理这些信号。

输入时序约束主要包括输入延迟约束和输入时钟约束。

2. 输出时序约束:指定输出信号的产生时间,以确保输出信号能够在规定的时钟周期内产生。

输出时序约束主要包括输出延迟约束和输出时钟约束。

3. 时钟约束:指定时钟的周期和相位关系,以确保时钟信号的稳定传输和接收。

时钟约束主要包括时钟周期约束和时钟相位约束。

4. 组合逻辑约束:指定组合逻辑电路的延迟和路径约束,以确保电路能够正确地计算和处理数据。

三、时序约束的编写时序约束的编写是FPGA设计中非常重要的一步,它要求工程师对电路的时序要求有深入的理解,并且需要具备一定的经验和技巧。

一般来说,时序约束的编写可以分为以下几个步骤:1. 确定时钟频率和时钟域:首先需要确定电路的工作频率和时钟域,以便后续的时序约束编写和优化。

2. 分析电路的时序要求:通过对电路的功能和时序要求进行分析,确定需要约束的信号和约束类型。

3. 编写时序约束:根据分析的结果,编写时序约束文件,将时序要求转化为约束语句,以指导综合工具和布局布线工具的优化和布线。

4. 时序约束的调试和优化:在完成时序约束的编写后,需要对时序约束进行调试和优化,以确保电路能够在规定的时钟频率下正常工作。

四、时序约束的注意事项在编写时序约束时,需要注意以下几点:1. 约束的准确性:时序约束的准确性非常重要,它直接影响到电路的正确性和性能。

时序约束的概念和基本策略

时序约束的概念和基本策略时序约束的概念和基本策略引言在现代电子设计中,时序约束是一项至关重要的任务。

它是指在电路中确定各个信号之间的时间关系,以确保电路能够按照预期的方式运行。

时序约束涉及到许多方面,包括时钟分配、逻辑延迟、信号传输等等。

在本文中,我们将详细介绍时序约束的概念和基本策略。

一、时序约束的概念1.1 什么是时序?在电路设计中,时序指的是各个信号之间发生的时间顺序关系。

例如,在一个简单的计数器电路中,一个时钟脉冲会触发计数器加1操作。

如果这个操作完成后立即出现下一个脉冲,则会导致计数器计数错误。

因此,在这种情况下,需要对脉冲之间的时间进行限制。

1.2 什么是时序约束?时序约束是一种用于限制各个信号之间时间顺序关系的技术。

它可以确保电路按照预期方式运行,并且可以帮助设计人员避免一些常见问题,例如信号噪声、稳定性问题等。

1.3 为什么需要时序约束?在现代电子设计中,时序约束非常重要。

这是因为现代电路的速度非常快,信号传输时间非常短。

如果不对信号进行时序约束,则可能会导致一些问题,例如:- 信号噪声:由于信号传输时间非常短,因此可能会受到噪声的干扰。

通过时序约束可以确保信号在正确的时间到达目标设备。

- 稳定性问题:如果两个信号在错误的时间交错到达,则可能会导致电路不稳定。

通过时序约束可以确保各个信号之间的时间顺序关系正确。

1.4 时序约束的应用领域时序约束广泛应用于各种电子设计中,包括:- 高速数字电路设计- FPGA设计- ASIC设计- PCB布局和布线二、时序约束的基本策略2.1 了解器件特性在进行时序约束之前,必须了解所使用器件的特性。

这包括器件的逻辑延迟、输入输出延迟等参数。

这些参数对于确定各个信号之间的时间关系至关重要。

2.2 确定主频率和时钟分配主频率和时钟分配是确定各个信号之间时间关系的重要因素。

通过确定主频率和时钟分配,可以确保各个信号在正确的时间到达目标设备。

2.3 确定时序限制一旦了解了器件特性并确定了主频率和时钟分配,就可以开始制定时序限制。

FPGA时序约束方法

FPGA时序约束方法以下是一些常见的FPGA时序约束方法:1.基本时序约束:-设置时钟频率:通过指定主时钟频率,可以限制设计中时序路径的最小时间。

-设置时钟约束:通过指定主时钟边沿的时刻,可以确保设计在正确的时刻进行时序采样。

-设置时钟分频比:通过设置时钟分频比,可以控制时钟的有效时间。

2.时序路径约束:-设置最大延迟:通过设置时序路径的最大延迟,可以确保时序路径在指定的时间范围内完成,避免过长的时序路径导致的性能问题。

-设置最小延迟:通过设置时序路径的最小延迟,可以确保时序路径在指定的时间范围内完成,避免过短的时序路径导致的稳定性问题。

-限制时钟频率:通过限制时序路径上的时钟频率,可以避免时钟频率过高导致的时序问题。

3.输入输出约束:-设置数据到达时间:通过设置输入数据到达时间,可以确保输入数据在有效时钟边沿之前稳定。

-设置数据输出时间:通过设置输出数据的稳定时间,可以确保输出数据在有效时钟边沿之后稳定。

4.时序分析和优化:-时序分析:使用时序分析工具来评估设计中的时序路径,并查找潜在时序问题。

-时序优化:根据时序分析的结果,对设计中的时序路径进行改进,以达到更好的时序性能。

5.约束语言:- 静态时序约束:使用硬件描述语言(如Verilog或VHDL)的时序约束语法,以标记和约束特定的时序路径。

-动态时序约束:使用专门的时序约束语言(例如SDC或SDF)来描述更复杂的时序关系,以支持更精确的时序约束。

6.约束验证:-时序约束检查:使用约束检查工具来验证时序约束的正确性和完整性。

-时序仿真:使用时序仿真工具来验证设计在特定时序约束下的行为和性能。

总结起来,FPGA时序约束方法是通过设置主时钟频率、时钟约束、时序路径约束、输入输出约束等来确保设计在FPGA器件上满足预期的时序要求。

时序约束语言和约束验证工具则提供了有效的手段来描述和验证这些约束,以确保设计的正确性和性能。

FPGA时序分析时序约束知识

FPGA时序分析时序约束知识一、FPGA时序分析的基本概念1.时序分析的定义时序分析是指通过计算和模拟来评估数字电路在不同条件下的时序要求是否能够满足。

它主要包括时钟周期、时钟偏移、时钟抖动、信号传输延迟等方面的考虑。

2.时序要求时序要求是指数字电路在设计中必须满足的时序条件。

常见的时序要求包括时钟频率、最小信号保持时间、最小信号恢复时间等。

3.时序路径时序路径是指数字电路中信号从输入到输出所经过的所有逻辑门和寄存器。

4.时序违规时序违规是指数字电路在设计中无法满足时序要求的情况。

时序违规可能导致电路功能失效,甚至硬件故障。

二、FPGA时序分析的关键步骤1.时序约束的设置时序约束是在FPGA设计中非常重要的一部分,它用于定义时钟频率、时钟边沿以及其他关键参数。

时序约束通常以SDC(Synopsys Design Constraints)的格式提供。

时序约束的设置需要综合考虑到电路的功能需求、时钟分频、时钟域划分以及时钟边沿和信号的传输延迟等各种因素。

时序约束应该准确地描述信号的起始时间、到达时间和关系,以确保设计满足时序要求。

2.时序路径分析时序路径分析是指通过分析不同信号路径的延迟和时间关系来评估设计是否满足时序要求。

时序路径分析可以通过静态分析和动态仿真两种方式进行。

静态分析主要是利用逻辑综合工具对电路的时序路径进行分析和计算。

动态仿真则是通过对电路进行时钟驱动的行为级仿真来评估时序路径。

两种方法都可以获得电路的路径延迟和时间关系,以判断设计是否满足时序要求。

3.时序修复当时序分析发现设计存在时序违规时,需要进行时序修复来解决问题。

时序修复主要包括时钟域划分、时钟频率调整、逻辑重构等方法。

时钟域划分是指将设计划分为不同的时钟域,确保时钟边沿的一致性。

时钟频率调整是通过逻辑优化和时序约束调整来改善设计的时序性能。

逻辑重构则是通过改变电路的结构和时序路径,以使设计满足时序要求。

三、时序约束的知识1.时钟频率设置时钟频率设置是指设置时钟的工作频率,以控制电路的运行速度和性能。

FPGA设计中关于时序约束(转)

FPGA设计中关于时序约束(转)FPGA设计中关于时序约束关于FPGA设计中,时序约束的定义的总结说明1.全局时序约束1.1 PERIOD约束用于约束同一时间域中同步逻辑单元之间的时序关系,PERIOD 约束会自动处理寄存器时钟端的反相问题,即,如果相邻同步元件时钟相位取反,那么它们之间的延时将被默认PERIOD约束值的一半。

NET “net_name” PERIOD = period {HIGH|LOW} [high_or_low_time];最小时钟周期的计算: Tclk = Tcko + Tnet +Tlogic + Tsetup -Tclk_skew; 其中,Tcko为从时钟输入到DFF输出端的时钟输出时间,Tnet为网线延时,Tlogic为同步元件之间的组合逻辑延时,Tsetup为同步元件的建立时间。

1.2 OFFSET约束用于约束数据的建立时间和保持时间,主要是输入PAD到同步单元和同步单元到输出PAD的时序关系OFFSET_IN_BEFORE用于定义输入数据比有效时钟沿提前多长时间准备好,其芯片内部与输入引脚相连的组合逻辑的延时不能大于该时间,否则,输入的数据就达不到要求的建立时间。

OFFSET_IN_AFTER用于定义输入数据在有效时钟沿后多长时间到达芯片的输入引脚,其作用和BEFORE是一样的,不过BEFORE的时钟沿是AFTER的下一个沿,如果一起定义的话。

上述约束用于设定在数据输入时,保证有效时钟沿到来时,数据已经达到稳定。

OFFSET_OUT_AFTER用于定义了输出数据在有效时钟沿之后多长时间之内保持稳定,其实是定义了输出的最大的数据保持时间,芯片内部的输出延时必须小于这个值。

OFFSET_OUT_BEFORE用于定义在下一个时钟信号到来之前的某个时间,必须输出数据,以供下一级器件使用。

这些约束用于对设计输出端的数据输出进行约束,以满足下一级器件的建立时间的要求,保证下一级的采样数据是稳定可靠的。

fpga的时序约束

fpga的时序约束【最新版】目录1.FPGA 的时序约束概述2.时序约束的种类3.时序约束的解决方法4.时序约束的优化策略5.总结正文FPGA 的时序约束是指在 FPGA 设计中,为了保证电路的正确运行,需要对各个逻辑电路的输入和输出信号的时序关系进行限制。

时序约束是FPGA 设计中一个重要的概念,对于保证 FPGA 设计的正确性和可靠性有着至关重要的作用。

时序约束的种类主要有以下几种:1.输入时序约束:输入信号的时序关系,包括输入信号的时序延迟和时序提前。

2.输出时序约束:输出信号的时序关系,包括输出信号的时序延迟和时序提前。

3.输入输出时序约束:输入和输出信号的时序关系,包括输入和输出信号的时序延迟和时序提前。

4.静态时序约束:静态时序约束是指在静态时序分析中需要满足的时序关系。

5.动态时序约束:动态时序约束是指在动态时序分析中需要满足的时序关系。

针对不同的时序约束,有以下几种解决方法:1.调整时序约束:通过调整输入和输出信号的时序关系,使得电路的时序约束得到满足。

2.修改逻辑设计:通过修改逻辑设计,减少逻辑电路的复杂度,从而降低时序约束的复杂度。

3.使用时序约束编辑器:通过使用时序约束编辑器,可以直观地编辑时序约束,使得时序约束得到满足。

4.使用时序约束优化工具:通过使用时序约束优化工具,可以自动地优化时序约束,使得时序约束得到满足。

在解决时序约束的同时,还需要对时序约束进行优化,以提高 FPGA 设计的性能。

时序约束的优化策略主要有以下几种:1.优化时序约束:通过优化时序约束,可以降低时序约束的复杂度,从而提高 FPGA 设计的性能。

2.使用时序约束放松:通过使用时序约束放松,可以在满足电路正确运行的前提下,降低时序约束的限制,从而提高 FPGA 设计的性能。

3.使用时序约束压缩:通过使用时序约束压缩,可以减少时序约束的数量,从而提高 FPGA 设计的性能。

总之,FPGA 的时序约束是 FPGA 设计中一个重要的概念,需要对各个逻辑电路的输入和输出信号的时序关系进行限制。

时序分析(2):时序约束原理

时序分析(2):时序约束原理⼀、基本概念1.时序:时钟和数据的对应关系2.约束:告诉综合⼯具,我们希望时序达到什么样的标准3.违例:时序达不到需要的标准4.收敛:通过调整布局布线⽅案来达到这个标准5.静态时序分析:电路未跑起来时,延时等已知,以此分析时序6.动态时序分析:电路跑起来,如Modelsim软件(理想状态)⼆、时序分析基本模型模型分为以下四种:(注:PAD指管脚)寄存器与寄存器之间输⼊PAD与寄存器之间寄存器与输出PA D之间输⼊PAD 与输出PAD之间(太极端,不讨论)知识补充:1、全局时钟:FPGA时钟到各个寄存器的时间⾮常接近。

2、⾃分频时钟:⾛的是数据线,到各个寄存器的时间差异⾮常⼤。

三、理想状态的建⽴时间和保持时间1、建⽴时间 Time setup(1) 接收时钟上升沿前,发送数据要准备好的时间(2) Tsu = 数据锁存沿(Latch)- 数据发送沿(Lanch)= 时钟周期2、保持时间 Time hold(1) 接收时钟上升沿后,发送数据要保持住的时间(2) Th = 发送端数据变化时 - 接收端数据锁存 = 03、补充(1) D触发器本⾝也有建⽴/保持时间的概念,称之为寄存器建⽴时间门限和寄存器保持时间门限,这是⼀个固有属性,是确定的、不变的。

当理想状态时,我们讨论建⽴/保持时间就相当于讨论D触发器的这⼀固有属性。

(2) FPGA所有时序问题,根本原因都是“建⽴时间和保持时间”的问题。

(3) 解决建⽴时间不⾜的⽅法是“减少延时”,⽽解决保持时间不⾜的⽅法是“增加延时”。

4、符号说明四、建⽴时间余量和保持时间余量Lunch edge:发射沿,以 clk_pad 为基准,⼀般看成 0 时刻。

实际时间是上⼀个寄存器所⽤的时间,因此⽤ clk1,看数据到达下⼀个寄存器的 D 端⽤了多久时间,结束时间⼜是多久。

Latch edge:接收沿,以 clk_pad 为基准,⼀般看成 0+Tcyc 时刻,要求时间是下⼀个寄存器计算的时间,所以⽤ clk2,看它⾃⾝需要的到达时间和结束时间是什么时候。

vivado时序约束分析报告

vivado时序约束分析报告1. 引言在数字电路设计过程中,时序约束是非常重要的一项任务,它用于指定设计中各个芯片内部和芯片之间的时间关系。

时序约束的正确设置能够确保设计的稳定性和性能,并帮助设计人员避免一些潜在的电路问题。

本文将对vivado时序约束进行分析,介绍其约束设置和分析过程。

2. vivado时序约束设置vivado是Xilinx公司推出的一款综合工具,它提供了一套全面的时序约束设置工具。

在vivado中,时序约束可以通过Constraints Language (XDC) 文件进行设置。

XDC文件采用一种类似于Verilog HDL的语法,通过约束语句来定义各种时序约束。

vivado中时序约束包括时钟约束、时间关系约束和路径约束。

时钟约束通过指定时钟周期和时钟频率来确保设计的稳定性。

时间关系约束用于指定各个时序元素之间的要求时延,例如数据不能在时钟上升沿之前到达等。

路径约束则用于指定信号在特定路径上的最大时延或最小时延要求。

时序约束在XDC文件中通过属性子句进行设置。

属性子句可以分为实例属性和全局属性两种。

实例属性用于具体指定某个特定的时序约束,而全局属性则适用于整个设计。

通过灵活设置时序约束属性,设计人员可以对设计进行精确的控制。

3. vivado时序约束分析过程vivado提供了丰富的时序约束分析工具,帮助设计人员检查和优化设计的时序性能。

以下是vivado时序约束分析的基本过程:3.1 设定约束在进行时序约束分析之前,首先要设置合适的约束。

通过XDC文件中的约束语句,将时钟频率、最大时延要求等信息准确地传达给vivado。

只有正确设置了约束,才能进行后续的时序分析。

3.2 分析时序报告在vivado中,可以通过“Timing Summary”报告来查看设计的时序分析结果。

该报告会详细列出各个时序路径的时延信息,包括起始点、终止点、传播时延、最大时延等。

通过分析时序报告,设计人员可以了解设计中各个路径的时序情况,查找问题所在。

FPGA时序约束的6种方法

FPGA时序约束的6种方法对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA 工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

下文总结了几种进行时序约束的方法。

按照从易到难的顺序排列如下:0.核心频率约束这是最基本的,所以标号为0.1.核心频率约束+时序例外约束时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay.但这还不是最完整的时序约束。

如果仅有这些约束的话,说明设计者的思路还局限在FPGA 芯片内部。

2.核心频率约束+时序例外约束+I/O 约束I/O 约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时(InputDelay、OutputDelay)、上下拉电阻、驱动电流强度等。

加入I/O 约束后的时序约束,才是完整的时序约束。

FPGA 作为PCB 上的一个器件,是整个PCB 系统时序收敛的一部分。

FPGA 作为PCB 设计的一部分,是需要PCB 设计工程师像对待所有COTS 器件一样,阅读并分析其I/O Timing Diagram 的。

FPGA 不同于COTS 器件之处在于,其I/O Timing 是可以在设计后期在一定范围内调整的;虽然如此,最好还是在PCB 设计前期给与充分的考虑并归入设计文档。

正因为FPGA 的I/O Timing 会在设计期间发生变化,所以准确地对其进行约束是保证设计稳定可控的重要因素。

许多在FPGA 重新编译后,FPGA 对外部器件的操作出现不稳定的问题都有可能是由此引起的。

3.核心频率约束+时序例外约束+I/O 约束+Post-fit Netlist引入Post-fit Netlist 的过程是从一次成功的时序收敛结果开始,把特定的一组逻辑(Design Partition)在FPGA 上实现的布局位置和布线结果(Netlist)固定下来,保证这一布局布线结果可以在新的编译中重现,相应地,这一组逻辑的时序收敛结果也就得到了保证。

ISE时序约束总结2

Timing Groups and OFFSET ConstraintsObjectivesAfter completing this module, you will be able to:•Use the Constraints Editor to create groups of path endpoints •Use the Constraints Editor to create path-specific OFFSET constraintsOutline•Introduction •Creating Groups •OFFSET Constraints •SummaryPath-Specific TimingConstraints•Using global timing constraints (PERIOD, OFFSET, and PAD-TO-PAD) will constrain your entire design•Using only global constraints often leads to over-constrained designs –Constraints are too tight–Increases compile time and can prevent timing objectives from being met–Review performance estimates provided by your synthesis tool or the Post-Map Static Timing Report•Path-specific constraints override the global constraints on specified paths –This allows you to loosen the timing requirements on specific pathsMore About Path-Specific Timing Constraints•Areas of your design that may benefit from path-specific constraints –Multi-cycle paths–Paths that cross between clock domains–Bidirectional buses–I/O timing•Path-specific timing constraints should be used to define your performance objectives and should not be indiscriminately placedGlobal Constraint Review•Using the global PERIOD, OFFSET IN, and OFFSET OUT constraints will constrain all of these paths•This makes it easy to control the overall performance of your designCDATAPath-Specific Constraint Example• A path-specific constraint can optimize as little as one path•This gives you greater control over your design’s performance and gives the implementation tools the greatest flexibility in meeting your performanceand utilization needsCDATAThe Advanced Tab of the Constraints Editor•Creating path-specificconstraints requires two steps–Step 1:Create groups of pathend points–Step 2:Communicate thetiming objective between thegroups•The constraints we discuss inConstraints EditorOutline •Introduction•Creating Groups •OFFSET Constraints •SummaryCreating Groups of Endpoints•Path-specific timing constraints will only be effective if path end points can be easily grouped together–Otherwise, constraining a large design would be time consuming and painstaking•The Constraints Editor makes this easy by allowing you to define groups of path end points (pads, flip-flops, latches, and RAMs)•Specific delay paths can then be constrained with advanced timing constraintsCreating Groups of Endpoints•With the Constraints Editor,grouping path end points ismade easy with the followingoptions:–Group by nets–Group by instance name–Group by hierarchy–Group by output net name–Timing THRU Points option–Group by clock edgeGrouping by Nets orOutput Net Name •Step 1: Enter a group name•search for–Optional filter string•Available list•Step 3: Select nets and click Add–Nets appear in the Time NameTargets listGrouping by Nets versusOutput Net Name•Grouping by net “NET_A”will create a group containing FLOP2 only –Group contains flip-flops that are driven by the selected net •Grouping by output new “NET_A”will create a group containing FLOP1only–Group contains the flip-flop that sources the selected net•Steps are the same•Design Element Types are different–Instance Name: FFs, pads, latches, RAMs–Hierarchy: User levels, Xilinx-created levelsGrouping by Instance Nameor Hierarchy••defined group–the group•Step 3: Select clock edgeGrouping by Clock EdgeTiming THRU Points•Allows you to optimize paths through specific nets and 3-state buffers•In this example, a group of nets was named TEOUTS. A constraint can now be referenced such that only the delay paths through the TEOUTS nets will be optimizedTiming THRU Points•Group nets or 3-state buffers •Use these groups to identifyspecific paths to be constrainedManaging Groups•Groups that you have defined are written into the UCF file–INST <element_name> TNM = <group_name>; OR–NET <net_name> TNM_NET = <group_name>; OR–TIMEGRP <group_name> = <elements>;•To add items to an existing group, click one of the grouping buttons and use the same Time Name–Not allowed when grouping by output net name•To delete a group, right-click on the line in the Constraints window and select Delete Constraint–Or delete the line with a text editor•You cannot remove items from a group with the Constraints Editor –Edit the UCF file with a text editorOutline•Introduction •Creating Groups•OFFSET constraints •SummaryReview of Global OFFSETConstraints•Use the Pad-to-Setup and Clock-to-Pad columns to specify OFFSETs for all I/O paths on each clock domain•Easiest way to constrain most I/O paths–However, this may lead to an over-constrained designPin-Specific OFFSETConstraints•Use the Pad-to-Setup and Clock-to-Pad columns to specify OFFSETs for each I/O pin•Use this type of constraint when only a few I/O pins need different timingCreating Groups of Pads •Groups of I/O pads can be made in the Ports tab–Use Shift-click or CTRL-click to select multiple pads–Enter a group name and click the Create Group button•Click the Pad to Setup or Clock to Pad button to define group OFFSETs –Or use the Advanced tabCreating Group OFFSETConstraints•OFFSET IN/OUTconstraints can also beentered in theAdvanced tab•The Pad-to-Setup andClock-to-Pad optionsallow you to enterOFFSET IN/OUTconstraints on specificgroups of padsGroup OFFSET Constraints•••Select a clock domain•Source SynchronousOFFSET Constraints•For source synchronous inputs, youcan specify the width of the validdata windowOFFSET Constraints withTwo-Phase Clocks•OFFSET constraints define the relationship between the data and the initial clock edge at the pins of the FPGA•Initial clock edge is defined in the global PERIOD constraint using the HIGH or LOW keyword–HIGH: Initial edge rising (default)–LOW: Initial edge falling•If all I/O are clocked on a single edge, use the HIGH/LOW keywords in the PERIOD constraint to define which edge is used•If both clock edges are used, create two OFFSET constraints –One for each clock edge–This includes cases where DDR flip-flops are usedOFFSET IN Using Both Clock Edges •Input data is valid 3 ns before rising and falling edge –PERIOD constraint is 10 ns, initial edge rising, 50-percent duty cycle •Create groups of flip-flops for each clock edge •For inputs clocked on a rising edge, OFFSET = IN 3 ns BEFORE clk;•For inputs clocked on a falling edge, OFFSET = IN –2 ns BEFORE clk;– 2 ns after initial (rising) edge = 3 ns before falling edgeclkOFFSET OUT Using Both Clock Edges•Output data must be valid 3 ns after rising and falling edge –PERIOD constraint is 10 ns, initial edge rising, 50-percent duty cycle •Create groups of flip-flops for each clock edge •For outputs clocked on a rising edge, OFFSET = OUT 3 ns AFTER clk;•For outputs clocked on a falling edge, OFFSET = OUT 8 ns AFTER clk;–8 ns after initial (rising) edge = 3 ns after falling edgeclkOutline•Introduction •Creating Groups •OFFSET Constraints•SummaryReview Questions•How do path-specific timing constraints improve your design’s performance?•How would you constrain this design to get an internal clock frequency of 100 MHz?•The input will be valid at least 3 ns before the rising edge of CLK. The output must be valid 4 ns after the falling edge of CLK. Write the appropriateOFFSET constraintsINCLKRESET_ARESET_BAnswers•How do path-specific timing constraints improve your design’s performance?–They give the implementation tools more flexibility to meet all of your timing objectives•How would you constrain this design to get a maximum internal clock frequency of 100 MHz?–Enter a global PERIOD constraint of 10 ns on the CLK signal•Write the appropriate OFFSET constraints.–Assuming that the PERIOD constraint uses the HIGH keyword and 50-percent duty cycle:•OFFSET = IN 3 ns BEFORE CLK;•OFFSET = OUT 9 ns AFTER CLK;Summary•Path-specific constraints are used to override global constraints –Keeps your design from becoming over-constrained–Allows the software to make intelligent trade-offs to meet all of your performance goals•Creating path-specific constraints is a two-step process–Create groups of path endpoints–Communicate the timing objective between the groups•Path-specific OFFSET constraints can be entered on either the Ports tab or the Advanced tab•When using both clock edges for I/O, write separate OFFSET constraints for each clock edgeWhere Can I Learn More?•Timing Presentation on the Web: →Tech Tips →Timing & Constraints•Constraints Guide: →Software Documentation –Documentation may also be installed on your local machine。

【精品博文】关于时序约束的一点总结

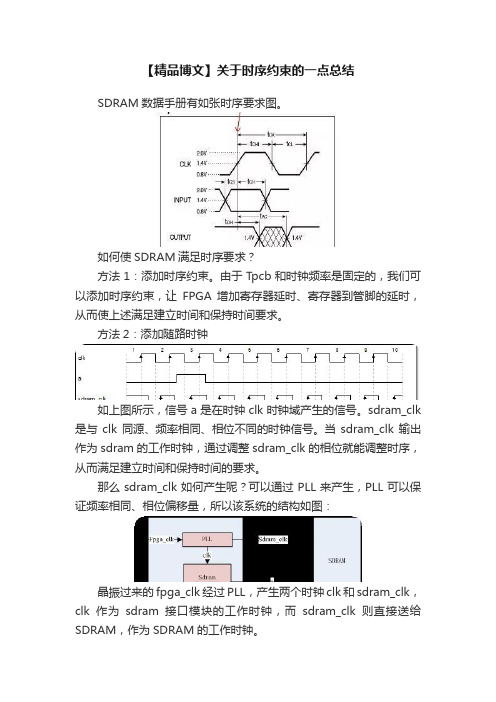

【精品博文】关于时序约束的一点总结SDRAM数据手册有如张时序要求图。

如何使SDRAM满足时序要求?方法1:添加时序约束。

由于Tpcb和时钟频率是固定的,我们可以添加时序约束,让FPGA增加寄存器延时、寄存器到管脚的延时,从而使上述满足建立时间和保持时间要求。

方法2:添加随路时钟如上图所示,信号a是在时钟clk时钟域产生的信号。

sdram_clk 是与clk同源、频率相同、相位不同的时钟信号。

当sdram_clk输出作为sdram的工作时钟,通过调整sdram_clk的相位就能调整时序,从而满足建立时间和保持时间的要求。

那么sdram_clk如何产生呢?可以通过PLL来产生,PLL可以保证频率相同、相位偏移量,所以该系统的结构如图:晶振过来的fpga_clk经过PLL,产生两个时钟clk和sdram_clk,clk作为sdram接口模块的工作时钟,而sdram_clk则直接送给SDRAM,作为SDRAM的工作时钟。

以上2种方法有什么优缺点?如何取舍?方法1是比较正规的传统方法,不用再产生时钟。

但调试起来麻烦,这是由于时钟约束是比较飘渺的东西,不知道有没有起作用(也有可能自己约束错了而不知道,也有可能约束太紧而满足不了)。

方法2调试起来简单,PLL设置简单,出错可能性小。

通过不断调整相位,最终肯定可以正确通信。

缺点也明显,接口一多,每个都要做随路时钟就浪费了。

最近一直在做时序约束,总结一下时序约束过程。

(1)根据时序约束报告找到相关路径。

看是什么原因导致的违规。

违规的原因有可能是路径本身需要多周期约束,或者程序代码if嵌套太多,判断条件太长,组合逻辑乱用等。

如果是代码问题,看是否能优化设计。

能够通过TimeQuest发现时序的不足,重新优化自己的设计,而不是一味的改变约束命令,这才是TimeQuest存在的最大意义(2)像SDRAM,DDR,MAC核这种设计,可以通过PLL位移时钟,达到改变输入输出延时的效果其他总结:get_registers 对应多周期约束;get_ports 对应时钟约束get_nets 对应IO约束get_clocks 对应跨时钟约束做时序约束还是要多参考官方文档,多做一些官方的参考设计,细心,耐心优化自己的设计。

XilinxFPGA编程技巧之常用时序约束详解

Xilinx FPGA编程技巧之常用时序约束详解1. 基本的约束方法为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。

最普遍的三种路径为:. 输入路径(Input Path),使用输入约束. 寄存器到寄存器路径(Register-to-Register Path),使用周期约束. 输出路径(Output Path),使用输出约束. 具体的异常路径(Path specific exceptions),使用虚假路径、多周期路径约束1.1. 输入约束Input ConstraintOFFSET IN约束限定了输入数据和输入时钟边沿的关系。

1.1.1. 系统同步输入约束System Synchronous Input在系统同步接口中,同一个系统时钟既传输数据也获取数据。

考虑到板子路径延时和时钟抖动,接口的操作频率不能太高。

1-1简化的系统同步输入SDR接口电路图1-2SDR系统同步输入时序上述时序的约束可写为:NET "SysClk" TNM_NET = "SysClk";TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;OFFSET = IN 5 ns VALID 5 ns BEFORE "SysClk";1.1.2. 源同步输入约束Source Synchronous Input在源同步接口中,时钟是在源设备中和数据一起产生并传输。

1-3简化的源同步输入DDR接口电路1-4DDR源同步输入时序上图的时序约束可写为:NET "SysClk" TNM_NET = "SysClk";TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" RISING;OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" FALLING;1.2. 寄存器到寄存器约束Register-to-Register Constraint寄存器到寄存器约束往往指的是周期约束,周期约束的覆盖范围包括:. 覆盖了时钟域的时序要求. 覆盖了同步数据在内部寄存器之间的传输. 分析一个单独的时钟域内的路径. 分析相关时钟域间的所有路径. 考虑不同时钟域间的所有频率、相位、不确定性差异1.2.1. 使用DLL, DCM, PLL, and MMCM等时钟器件自动确定同步关系使用这一类时钟IP Core,只需指定它们的输入时钟约束,器件将自动的根据用户生成IP Core时指定的参数约束相关输出,不需用户手动干预。

集成电路设计中的时序约束分析

集成电路设计中的时序约束分析随着科技的不断发展,集成电路在许多领域得到广泛应用。

集成电路设计中的时序约束分析是保证电路正确运行的关键之一。

本文将从什么是时序约束,时序约束的分析方法和时序约束优化三个方面进行阐述。

一、什么是时序约束时序约束是指在完成集成电路设计之前对其进行的规定性的要求,用来保证在实际应用中电路的正确性和性能稳定性。

这些要求包括输入和输出电平的稳定性、时钟频率和同步信号的稳定性等。

在集成电路设计中,时序约束是非常重要的,它可以保证电路的正常运行和避免潜在的故障。

此外,合理的时序约束可以帮助设计人员在尽量缩短电路设计时间的情况下实现高性能的电路。

二、时序约束的分析方法在集成电路设计中时序约束的分析包括单个时序分析和时序路由分析两种类型。

单个时序分析主要是通过分析电路中的各个信号之间的时间关系,并根据这些关系来确定电路中的时序约束。

这种方法可以帮助设计人员在保证电路稳定性的前提下尽量提高电路性能。

另外,单个时序分析还可以检测电路的故障,并对电路进行排查和修复。

时序路由分析又称为时序优化,它是在单个时序分析的基础上,通过对电路的布局和路由进行优化,进一步提高电路的性能。

时序路由分析主要是通过改变电路中的信号路径,以满足不同的时序约束要求。

三、时序约束优化在集成电路设计中,时序约束优化是提高电路性能的关键之一。

合理的时序约束优化可以最大程度地利用电路资源,提高电路的工作效率和性能,降低电路的功耗。

对于时序约束的优化,主要需要考虑以下几个方面:1、资源利用率:合理的时序约束可以充分利用电路中的资源,避免浪费,提高电路的资源利用率。

2、功耗:合理的时序约束可以降低电路的功耗,提高电路的效率。

3、可靠性:合理的时序约束可以保证电路的正常运行,并降低电路故障率。

总之,时序约束分析是集成电路设计中的重要环节,它直接影响到电路的性能和可靠性。

通过对时序约束的分析和优化,可以最大程度地利用电路资源,提高电路的性能和稳定性,同时也可以提高电路的可靠性。

电脑芯片分析中的时序约束和时钟分析

电脑芯片分析中的时序约束和时钟分析在现代电子产品中,芯片的设计和性能至关重要。

而在芯片设计过程中,时序约束和时钟分析是不可或缺的部分。

本文将详细介绍电脑芯片分析中的时序约束和时钟分析的概念和作用,并探讨其在芯片设计中的重要性。

一、时序约束的概念和作用时序约束是指对于电路的时序行为所提出的各种约束条件,用以规定芯片内部电路在不同时钟周期中的操作关系。

它是芯片设计分析的重要一环,具有以下几个作用:1. 确定芯片的最大频率:时序约束可以帮助设计人员确定芯片的最大工作频率,从而保证芯片的正常运行。

通过设置适当的时序约束,可以限制芯片内部电路的延迟和时序关系,提高芯片的工作效率和性能。

2. 验证芯片的时序正确性:时序约束可以用于验证芯片的时序正确性。

通过对芯片的时序约束进行仿真和分析,可以检测出芯片设计中可能存在的时序错误,提前进行修改和优化,避免出现设计缺陷。

3. 优化芯片的功耗和面积:时序约束可以用于优化芯片的功耗和面积。

通过合理设置时序约束,可以减少芯片内电路的冗余和无效操作,减小功耗和芯片面积,提高整个系统的效能。

二、时序约束的关键要素在时序约束中,有几个关键要素需要考虑:1. 时钟周期:时钟周期是指芯片内部电路在一个时钟周期内完成一次操作的时间。

时钟周期是芯片设计的基本单位,决定了芯片的工作速度和时序要求。

2. 延迟:延迟是指芯片内部电路从接收输入信号到输出响应所需的时间。

延迟是芯片设计中重要的指标之一,需要根据时序约束进行控制和优化。

3. 约束条件:约束条件是指对芯片内部电路工作的各种限制和要求。

常见的约束条件包括输入输出延迟、时序关系、最大工频等。

三、时钟分析的概念和作用时钟分析是对芯片内部时钟信号进行分析和优化的过程。

在芯片设计中,时钟信号起到同步和调度电路的作用,时钟分析主要包括以下几个方面:1. 时钟树分析:时钟树是指芯片中所有时钟信号的传输路径。

时钟树分析可以帮助设计人员了解芯片中时钟信号的传输效率和延迟情况,发现潜在的时钟问题,进行优化和改进。

时序约束总结

时序约束总结很多人发贴,来信询问关于约束、时序分析的问题,比如:如何设置setup,hold时间?如何使用全局时钟和第二全局时钟(长线资源)?如何进行分组约束?如何约束某部分组合逻辑?如何通过约束保证异步时钟域之间的数据交换可靠?如何使用I/O逻辑单元内部的寄存器资源?如何进行物理区域约束,完成物理综合和物理实现?等等。

为了解决大家的疑难,我们将逐一讨论这些问题。

今天先讨论一下约束的作用?有些人不知道何时该添加约束,何时不需要添加?有些人认为低速设计不需要时序约束?关于这些问题,希望下面关于约束作用的论述能够有所帮助!附加约束的基本作用有3:(1)提高设计的工作频率对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。

通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。

(2)获得正确的时序分析报告几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或布局布线后的时序分析报告,从而对设计的性能做出评估。

静态时序分析工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析报告。

(3)指定FPGA/CPLD引脚位置与电气标准FPGA/CPLD的可编程特性使电路板设计加工和FPGA/CPLD设计可以同时进行,而不必等FPGA/CPLD引脚位置完全确定,从而节省了系统开发时间。

这样,电路板加工完成后,设计者要根据电路板的走线对FPGA/CPLD加上引脚位置约束,使FPGA/CPLD与电路板正确连接。

另外通过约束还可以指定IO引脚所支持的接口标准和其他电气特性。

为了满足日新月异的通信发展,Xilinx新型FPGA/CPLD可以通过IO引脚约束设置支持诸如AGP、BLVDS、CTT、GTL、GTLP、HSTL、LDT、LVCMOS、LVDCI、LVDS、LVPECL、LVDSEXT、LVTTL、PCI、PCIX、SSTL、ULVDS等丰富的IO接口标准。

ISE时序约束总结3

Path-Specific Timing ConstraintsOutline•Inter-Clock Domain Constraints •Multi-cycle Paths•False Paths •Miscellaneous Constraints •SummaryCLKConstraining Between Rising and Falling Clock Edges •The PERIOD constraint automatically accounts for two-phase clocks –Includes adjustments for non-50-percent duty-cycle clocks •Example: A PERIOD constraint of 10 ns on CLK will apply a 5-ns constraint between these two flip-flops •No path-specific constraints are required for this caseRelated Clock Domains •Create a PERIOD constraint for one clock–Define all related clocks in terms of this PERIOD constraint•The implementation tools will use the relationships to determine how to cross between clock domains•DCM with multiple outputs:–Define a PERIOD constraint on the input to the DCM–The implementation tools will “push”the constraint onto each output–All constraints will be defined relative to the original PERIOD constraintUnrelated Clock Domains •In this example, the delay path between the two clock domains is NOT covered by either of the PERIOD constraints–This is the default behavior•You must add a constraint to cover paths when crossing between related clock domains–Example: Same frequency, but CLK_B is phase shifted •You must add a synchronization circuit when crossing between unrelated clock domainsPERIOD CLK_A PERIOD CLK_B CLK_ACLK_BUnrelated Clock Domains •To constrain the paths between the two clock domains (highlighted in gray)–Define groups of registers CLK_A and CLK_B with the Group by Nets option •Automatically done if you have specified a PERIOD constraint for both clock domains–Place a Slow/Fast Path Exception between the two groups of registersPERIOD CLK_APERIOD CLK_B 5 ns CLK_ACLK_B•Step 1: Create the groupsoption–Group by clock net –Skip this step if PERIODconstraints are defined•Step 2: Create theconstraint by clicking thebuttonUnrelated Clock Domains•–Must begin with “TS ”•constraint•Unrelated Clock DomainsOutline•Inter-Clock Domain Constraints•Multi-cycle Paths•False Paths •Miscellaneous Constraints •SummaryMulti-cycle Path Constraints•Multi-cycle paths occur whenregisters are not updated onconsecutive clock cycles Array–Always at least one clock cyclebetween updates–Typically, the registers arecontrolled by a clock enable• A prescaled counter is oneexample–Registers in COUT14 areupdated every 4 clock cycles–Paths between these registersare multi-cycle pathsConstraints•Step 1: Create a globalPERIOD constraint (notshown)•option–Group by enable net•Step 3: Click the Multi-cycle Paths buttonConstraints•Enter a TIMESPEC name•previously defined•the PERIOD constraintOutline•Inter-Clock Domain Constraints •Multi-cycle Paths•False Paths •Miscellaneous Constraints •SummaryFalse Paths•The False Paths optionsfrom being applied tospecific paths–constrained paths inyour designDefining False Paths•Use the False Paths(FROM:TO:TIG) button to defineendpoints–TIG = Timing IGnore–applied to the paths–Paths through specific nets or 3-THRU points option•What is wrong with this example?Defining False Paths by Nets•The False Paths by Nets optionallows you to ignore timingconstraints on a specific net–Any delay path containing theRESET net will not beconstrained•The Ignored TIMESPECsoption allows specificconstraints to be ignored–TS_P2P constraint will beignored on paths containingthe RESET netOutline•Inter-Clock Domain Constraints •Multi-cycle Paths•False Paths•Miscellaneous Constraints •SummaryMiscellaneous Tab•IOBs•Mark asynchronous registers–Prevents “X”propagation duringsimulation•Low Skew Resources–Use for high-fanout controlsignals•area groups for floorplanning••Define initial values for storageelementsProrating Constraints•Prorating allows the tools to use the most accurate information –The implementation tools use the worst-case operating temperature andvoltage for your chosen device package (85 ºfor Commercial, 100 ºforIndustrial)•Specify your own worst-case conditions–This will prorate the device delay characteristics to accurately reflect your worst-case system conditionsTiming Constraint Priority•False Paths–Must be allowed to override any timing constraint•FROM THRU TO•FROM TO•Pin-Specific OFFSETs •Group OFFSETs–Groups of pads or registers •Global PERIOD and OFFSETs –Lowest priority constraints Highest LowestTiming ConstraintInteraction•Whenever a path is covered by more than one constraint, the tools must choose which constraint to use for timing analysis•If the constraints are of different types, the highest priority constraint is applied•If the constraints are of the same type (Example: FROM TO), the decision is more complex–Can be dictated with the PRIORITY keyword in the UCF file•To see where your constraints overlap, generate a Timing Specification Interaction (TSI) file–Under Properties for Post-Place & Route Static Timing Report, type in a filename–In the Timing Analyzer, select Analyze →Constraints InteractionOutline•Inter-Clock Domain Constraints •Multi-cycle Paths•False Paths •Miscellaneous Constraints•SummarySkills CheckReview QuestionBackground Information•Prescaled 16-bit counter is created in two blocks–Q0 and Q1 in block PRE2 toggle at 200 MHz–Q[15:2] toggle every fourth clock edge (50 MHz)–The design is fully synchronous because all registers share the same clock •However, COUT14 registers are disabled 3/4 of the time so they do not have tomeet a 200-MHz PERIOD constraintReview Questions•What constraints need to be placed on this design to assure it will meet the performance objectives?•How would you enter these constraints through the Constraints Editor?•How do multi-cycle path constraints improve your design’s performance?Answers•What type of constraints need to be placed on this design to assure it will meet the performance objectives?–Global PERIOD constraint of 5 ns (or 200 MHz)–Multi-cycle path constraint of 5 x 4 = 20 ns (or 200 / 4 = 50 MHz)•How would you enter these constraints through the Constraints Editor?–PERIOD constraint: Use the Global tab–Multi-cycle path constraint:•Group the flip-flops in COUT14 by clock enable net (group name: MSB)•Constrain from MSB to MSB•How do multi-cycle path constraints improve your design’s performance?–They allow the implementation tools to place some logic farther apart and use slower routing resourcesReview Questions•If a PERIOD constraint were placed on this design, what delay paths would be constrained?•If the goal is to optimize the input and output times without constraining the paths between registers, what constraints are needed?–Assume that a global PERIOD constraint is already definedAnswers•If a PERIOD constraint were placed on this design, what delay paths would be constrained?–Paths between the control registers and the status registers would be constrainedAnswers•If the goal is to optimize the input and output times without constraining the paths between registers, what constraints are needed?–Enter OFFSET constraints on the Global tab–Define False Paths By Nets•Select the BIDIR_BUS[7:0] nets•Select the global PERIOD constraint to be ignoredSummary•Use a Slow/Fast Path Exception to constrain paths that cross between clock domains•Identifying multi-cycle and false paths allows the implementation tools to make appropriate tradeoffs–These paths will use slower routing resources, which frees up fast routing for critical signals•Prorating your operating conditions gives the tools the most accurate picture of your design environment•In general, more-specific constraints have a higher priority than less-specific constraintsWhere Can I Learn More?•Timing Presentation on the Web: →Tech Tips →Timing & Constraints•Constraints Guide: →Software Documentation –Documentation may also be installed on your local machinePDF created with pdfFactory Pro trial version 。

fifo 时序约束

fifo 时序约束FIFO时序约束FIFO(First In, First Out)是一种常见的时序约束,用于描述数据在系统中的传输顺序。

它确保数据按照它们被发送的顺序被接收和处理。

本文将介绍FIFO时序约束的概念、应用以及对电子系统设计的影响。

一、FIFO时序约束的概念FIFO时序约束是指在电子系统设计中,对数据的传输顺序进行约束的一种方法。

它要求在数据发送和接收的过程中,数据按照它们被发送的顺序被接收和处理。

这种约束可以应用于各种电子系统,包括计算机处理器、通信系统、存储系统等。

二、FIFO时序约束的应用1. 计算机处理器在计算机处理器中,FIFO时序约束用于确保指令按照正确的顺序被执行。

由于指令的执行顺序可能会受到多个因素的影响,如指令重排序、流水线等,因此需要使用FIFO时序约束来保证指令的正确执行顺序。

2. 通信系统在通信系统中,FIFO时序约束用于确保数据在发送和接收过程中的顺序不会被打乱。

例如,在以太网通信中,数据包的传输顺序需要按照FIFO时序约束来进行。

3. 存储系统在存储系统中,FIFO时序约束用于确保数据在存储和读取过程中的顺序不会被打乱。

例如,在内存中存储数据时,需要按照FIFO时序约束来保证数据的正确存储和读取顺序。

三、FIFO时序约束对电子系统设计的影响1. 性能影响FIFO时序约束可能会对系统的性能产生一定的影响。

由于需要保证数据的顺序传输,可能会增加系统的延迟。

因此,在电子系统设计中需要权衡FIFO时序约束对性能的影响。

2. 设计复杂性FIFO时序约束可能会增加系统的设计复杂性。

在设计过程中,需要考虑到数据的传输顺序,并确保设计满足FIFO时序约束。

这可能需要对系统进行额外的优化和调整,增加设计的复杂性。

3. 时序验证由于FIFO时序约束的存在,需要对系统进行时序验证,以确保数据的传输顺序符合约束。

时序验证是一项重要的工作,需要使用专业的工具和方法来进行。

四、总结FIFO时序约束是一种常见的时序约束,用于描述数据在系统中的传输顺序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

很多人发贴,来信询问关于约束、时序分析的问题,比如:如何设置setup,hold时间?如何使用全局时钟和第二全局时钟(长线资源)?如何进行分组约束?如何约束某部分组合逻辑?如何通过约束保证异步时钟域之间的数据交换可靠?如何使用I/O逻辑单元内部的寄存器资源?如何进行物理区域约束,完成物理综合和物理实现?等等。

为了解决大家的疑难,我们将逐一讨论这些问题。

今天先讨论一下约束的作用?有些人不知道何时该添加约束,何时不需要添加?有些人认为低速设计不需要时序约束?关于这些问题,希望下面关于约束作用的论述能够有所帮助!附加约束的基本作用有3:(1)提高设计的工作频率对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。

通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。

(2)获得正确的时序分析报告几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或布局布线后的时序分析报告,从而对设计的性能做出评估。

静态时序分析工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析报告。

(3)指定FPGA/CPLD引脚位置与电气标准FPGA/CPLD的可编程特性使电路板设计加工和FPGA/CPLD设计可以同时进行,而不必等FPGA/CPLD引脚位置完全确定,从而节省了系统开发时间。

这样,电路板加工完成后,设计者要根据电路板的走线对FPGA/CPLD加上引脚位置约束,使FPGA/CPLD与电路板正确连接。

另外通过约束还可以指定IO引脚所支持的接口标准和其他电气特性。

为了满足日新月异的通信发展,Xilinx新型FPGA/CPLD可以通过IO引脚约束设置支持诸如AGP、BLVDS、CTT、GTL、GTLP、HSTL、LDT、LVCMOS、LVDCI、LVDS、LVPECL、LVDSEXT、LVTTL、PCI、PCIX、SSTL、ULVDS等丰富的IO接口标准。

另外通过区域约束还能在FPGA上规划各个模块的实现区域,通过物理布局布线约束,完成模块化设计等。

贴2:时序约束的概念和基本策略!时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。

通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。

例如用OFFSET_IN_BEFORE约束可以告诉综合布线工具输入信号在时钟之前什么时候准备好,综合布线工具就可以根据这个约束调整与IPAD相连的Logic Circuitry的综合实现过程,使结果满足FFS的建立时间要求。

附加时序约束的一般策略是先附加全局约束,然后对快速和慢速例外路径附加专门约束。

附加全局约束时,首先定义设计的所有时钟,对各时钟域内的同步元件进行分组,对分组附加周期约束,然后对FPGA/CPLD输入输出PAD附加偏移约束、对全组合逻辑的PAD TO PAD路径附加约束。

附加专门约束时,首先约束分组之间的路径,然后约束快、慢速例外路径和多周期路径,以及其他特殊路径。

贴3:周期(PERIOD)的含义周期的含义是时序中最简单也是最重要的含义,其它很多时序概念会因为软件商不同略有差异,而周期的概念确是最通用的,周期的概念是FPGA/ASIC 时序定义的基础概念。

后面要讲到的其它时序约束都是建立在周期约束的基础上的,很多其它时序公式,可以用周期公式推导。

周期约束是一个基本时序和综合约束,它附加在时钟网线上,时序分析工具根据PERIOD约束检查时钟域内所有同步元件的时序是否满足要求。

PERIOD 约束会自动处理寄存器时钟端的反相问题,如果相邻同步元件时钟相位相反,那么它们之间的延迟将被默认限制为PERIOD约束值的一半。

如下图所示,时钟的最小周期为:TCLK = TCKO +TLOGIC +TNET +TSETUP -TCLK_SKEWTCLK_SKEW =TCD2-TCD1其中TCKO为时钟输出时间,TLOGIC为同步元件之间的组合逻辑延迟,TNET为网线延迟,TSETUP为同步元件的建立时间,TCLK_SKEW为时钟信号延迟的差别。

这个帖子打算先澄清一些时序约束的基本概念,然后将在综合工具(Synplify Pro为例),设计平台(ISE5.x 和Quartus2.2为例)的具体约束方法和技巧,然后将如何利用时序分析工具分析关键路径。

如果没有意外,应该30多个帖子吧。

仿真时序本来是Deve的老本行,随时需要Deve加入一起把这个帖子办好。

欢迎大家畅谈观点,本站的版主,冲锋啊,嘻嘻。

贴4:数据和时钟之间的约束:OFFSET和SETUP、HOLD时间。

为了确保芯片数据采样可靠和下级芯片之间正确的交换数据,需要约束外部时钟和数据输入输出引脚之间的时序关系(或者内部时钟和外部输入/输出数据之间的关系,这仅仅是从采用了不同的参照系罢了)。

约束的内容为告诉综合器、布线器输入数据到达的时刻,或者输出数据稳定的时刻,从而保证与下一级电路的时序关系。

这种时序约束在Xilinx中用Setup to Clock(edge),Clock(edge)to hold 等表示。

在Altera里常用tsu (Input Setup Times)、th (Input Hold Times)、tco (Clock to Out Delays)来表示。

很多其它时序工具直接用setup和hold表示。

其实他们所要描述的是同一个问题,仅仅是时间节点的定义上略有不同。

下面依次介绍。

贴5:关于输入到达时间,这一贴估计问题比较多,看起来也比较累,但是没有办法,这些都是时序的基本概念啊。

搞不清楚,永远痛苦,长痛不如短痛了,呵呵。

Xilinx的"输入到达时间的计算"时序描述如图所示:定义的含义是输入数据在有效时钟沿之后的TARRIVAL时刻到达。

则,TARRIVAL=TCKO+TOUTPUT+TLOGIC 公式1根据”贴3“介绍的周期(Period)公式,我们可以得到:Tcko+Toutput+Tlogic+Tinput+Tsetup-Tclk_skew=Tclk;公式2将公式1代入公式2:Tarrival+Tinput+Tsetup-Tclk_skew=Tclk,而Tclk_skew满足时序关系后为负,所以TARRIVAL +TINPUT+TSETUP <TCLK 公式3,这就是Tarrival应该满足的时序关系。

其中TINPUT为输入端的组合逻辑、网线和PAD的延迟之和,TSETUP为输入同步元件的建立时间。

贴6数据xx和数据到达时间的关系:TDELAY为要求的芯片内部输入延迟,其最大值TDELAY_MAX与输入数据到达时间TARRIVAL的关系如图2所示。

也就是说:TDELAY_MAX+TARRIVAL=TPERIOD 公式4所以:TDELAY<TDELAY_MAX=TPERIOD-TARRIVAL帖7要求输出的稳定时间从下一级输入端的延迟可以计算出当前设计输出的数据必须在何时稳定下来,根据这个数据对设计输出端的逻辑布线进行约束,以满足下一级的建立时间要求,保证下一级采样的数据是稳定的。

计算要求的输出稳定时间如图所示。

公式的推导如下:定义:TSTABLE = TLOGIC +TINPUT +TSETUP从前面帖子介绍的周期(Period)公式,可以得到(其中TCLK_SKEW=TCLK1-TCLK2):TCLK=TCKO+TOUTPUT+TLOGIC+TINPUT+TSETUP+TCLK_SKEW将TSTABLE的定义代入到周期公式,可以得到:TCLK=TCKO+TOUTPUT+TSTABLE+TCLK_SKEW所以,TCKO +TOUTPUT+TSTABLE<TCLK这个公式就是TSTABLE必须要满足的基本时序关系,即本级的输出应该保持怎么样的稳定状态,才能保证下级芯片的采样稳定。

有时我们也称这个约束关系是输出数据的保持时间的时序约束关系。

只要满足上述关系,当前芯片输出端的数据比时钟上升沿提早TSTABLE 时间稳定下来,下一级就可以正确地采样数据。

其中TOUTPUT为设计中连接同步元件输出端的组合逻辑、网线和PAD的延迟之和,TCKO为同步元件时钟输出时间。

这里的概念介绍比较繁复,但是如果想掌握数据与时钟关系的基本约束,就必须搞清楚这些概念,下一帖介绍这些概念的具体应用,实施上述约束的方法和具体命令。

转贴lipple的问题:请问斑竹上面几贴那些延时属于setup,哪些属于hold啊其中TDELAY为要求的芯片内部输入延迟,其最大值与输入数据到达时间TARRIVAL的关系如帖6所述:TDELAY_MAX + TARRIVAL = TPERIOD,所以TDELAY < TPERIOD - TARRIVAL = 20 - 14 =6 ns.输出偏移约束例:设时钟周期为20ns,后级输入逻辑延时TINPUT为4ns、建立时间TSETUP 为1ns,中间逻辑TLOGIC的延时为10ns,那么TSTABLE=15ns,于是可以在数据输入引脚附加NET DATA_OUT FFET=OUT 15ns BEFORE CLK 约束,也可以直接对芯片内部的输出逻辑直接进行约束,NET DATA_OUT FFET=OUT TOUTPUT_DELAY AFTER CLK,其中TOUTPUT_DELAY为要求的芯片内部输出延迟,其最大值与要求的输出数据稳定时间TSTABLE的关系为:TOUTPUT_DELAY_MAX+TSTABLE= TPERIOD.TOUT_DELAY< TPERIOD - TSTABLE = 20 - 15 = 5ns这些概念和推导有些枯燥和乏味,但是如果要掌握好数据与时钟之间的约束,就要耐心看下去,明天介绍一下Altera的相关约束方法。

帖9 Altera对应的时序概念这两天太忙了,帖子上的有些慢,请朋友们原谅,我会尽量按照计划写完这个主题的。

前面8个帖子介绍了一些时序概念,有的是FPGA/ASIC设计的一般性时序概念,有的为了方便叙述,主要介绍了Xilinx对应的这些时序概念,和具体的约束熟悉。

下面几个帖子主要介绍Altera对应的这些时序概念和约束方法。

前面首先介绍的第一个时序概念是周期,Period,这个概念是FPGA/ASIC通用的一个概念,各方的定义相当统一,至多是描述方式不同罢了,所有的FPGA 设计都首先要进行周期约束,这样做的好处除了在综合与布局布线时给出规定目标外,还能让时序分析工具考察整个设计的Fmax等。