微电子器件期末复习题 含答案

12年期末考试题B答案

成都学院10级“微电子器件”期末考试题B卷(答案)一、填空题(20分)1、在N型半导体中,(电子)为多数载流子,( 空穴 )为少数载流子。

2、在PN结的空间电荷区中,P区一侧带(负)荷,N区一侧带(正)电荷。

3、势垒电容反映的是PN结的势垒区电离杂质电荷随外加电压的变化率.PN结的掺杂浓度越高,则势垒电容就越(大);外加反向电压越高,则势垒电容就越(小)。

4、为了提高晶体管的基区输运系数,应当使基区宽度(远小于)基区少子扩散长度。

5、晶体管的共发射极直流短路电流放大系数β是指,发射结(正)偏、集电结(零)偏时的(集电极)电流与(基极)电流之比。

6、当(K Pmax)降到1时的频率称为最高振荡频率f M .7、对于频率不是特别高的一般高频管,提高特征频率f T的主要措施是(减小基区宽度)。

8、MOSFET是利用外加电压产生(电场)来控制漏极电流大小,因此它是(电压)控制器件。

9、跨导gm反映了场效应管(栅源电压)对(漏极电流)控制能力,其单位是(西门子)10、要提高N沟道MOSFET的阈电压V T,应使衬底掺杂浓度N A(提高),使栅氧化层厚度T ox(增厚)。

二选择题(10分)1、当PN结外加正向偏压时,扩散电流(A)漂移电流,当外加反向偏压时,扩散电流(B )漂移电流。

A 大于,B。

小于,C等于,D 不定2、当对PN结外加反向电压时,其势垒区宽度会( A ),势垒区的势垒高度会( C )。

A 变宽, B变窄,C 变高,D 不变3、P+N结耗尽层宽度主要取决于:BA p+区浓度B n区的浓度C P+区和n区的浓度4、限制双极结型晶体管最高工作电压的主要因素是:CA雪崩击穿电压 B基区穿通电压 C雪崩击穿电压和基区穿通电压的较小者5、对于实际的增强型MOSFET,简单说明阈值电压(VT)包括哪几个部分的电压分量(ABD )(多选) A栅氧化层上的电压Vox,B平带电压VFB ,C源漏电压VDSD 使半导体表面产生强反型层(沟道)所需要的电压2φFP6。

微电子器件课程复习题教学内容

微电子器件课程复习题“微电子器件”课程复习题一、填空题1、若某突变PN 结的P 型区的掺杂浓度为163A 1.510cm N -=⨯,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为( )和( )。

2、在PN 结的空间电荷区中,P 区一侧带( )电荷,N 区一侧带( )电荷。

内建电场的方向是从( )区指向( )区。

3、当采用耗尽近似时,N 型耗尽区中的泊松方程为( )。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越( )。

4、PN 结的掺杂浓度越高,则势垒区的长度就越( ),内建电场的最大值就越( ),内建电势V bi 就越( ),反向饱和电流I 0就越( ),势垒电容C T 就越( ),雪崩击穿电压就越( )。

5、硅突变结内建电势V bi 可表为( ),在室温下的典型值为( )伏特。

6、当对PN 结外加正向电压时,其势垒区宽度会( ),势垒区的势垒高度会( )。

7、当对PN 结外加反向电压时,其势垒区宽度会( ),势垒区的势垒高度会( )。

8、在P 型中性区与耗尽区的边界上,少子浓度n p 与外加电压V 之间的关系可表示为( )。

若P 型区的掺杂浓度173A 1.510cm N -=⨯,外加电压V = 0.52V ,则P 型区与耗尽区边界上的少子浓度n p 为( )。

9、当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度( );当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度( )。

10、PN 结的正向电流由( )电流、( )电流和( )电流三部分所组成。

11、PN结的正向电流很大,是因为正向电流的电荷来源是();PN结的反向电流很小,是因为反向电流的电荷来源是()。

12、当对PN结外加正向电压时,由N区注入P区的非平衡电子一边向前扩散,一边()。

每经过一个扩散长度的距离,非平衡电子浓度降到原来的()。

13、PN结扩散电流的表达式为()。

微电子器件课程复习题

1、若某突变PN 结的P 型区的掺杂浓度为A^A =1.5xlO ,6cm-\则室温下该区的平衡多子浓度加与平衡少子浓度〃po 分别为(M = l ・5xlO"cm-3)和(皿=1・5><10%加-3)。

2、在PN 结的空间电荷区中,P 区一侧带(负)电荷,N 区一侧带(正)电荷。

内建电场的方向是从(N ) 区指向(P )区。

[发生漂移运动,空穴向P 区,电子向N 区]越高,则内建电场的斜率越(大)。

4、PN 结的掺杂浓度越高,则势垒区的长度就越(小),内建电场的最大值就越(大),内建电势V bi 就越(大儿 反向饱和电流/o 就越(小)[P20],势垒电容C T 就越(大儿 雪崩击穿电压就越(小)oKT N N 5、硅突变结内建电势血可表为(% =——In 亠2) P9,在室温下的典型值为(0.8)伏特。

q 叮6、 当对PN 结外加正向电压时,其势垒区宽度会(减小),势垒区的势垒高度会(降低)。

7、 当对PN 结外加反向电压时,其势垒区宽度会(增大),势垒区的势垒高度会(提高)。

8、 在P 型中性区与耗尽区的边界上,少子浓度与外加电压y 之间的关系可表示为 (np (-Xp ) = H/;o exp (-^-) ) P18o 若 P 型区的掺杂浓度 N A =1.5x10门cnV',外加电压 V= 0. 52V,则P 型区与耗尽区边界上的少子浓度©为(7.35x102讣〃尸)o9、 当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(大);当对 PY 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(小)。

10、 PN 结的正向电流由(空穴扩散)电流、(电子扩散)电流和(势垒区复合)电流三部分所组成。

11、 PN 结的正向电流很大,是因为正向电流的电荷来源是(多子);PN 结的反向电流很小,是因为反 向电流的电荷来源是(少子)。

微电子器件_电子科技大学中国大学mooc课后章节答案期末考试题库2023年

微电子器件_电子科技大学中国大学mooc课后章节答案期末考试题库2023年1.线性缓变结的耗尽层宽度正比于【图片】。

参考答案:正确2.反向偏置饱和电流可看成是由中性区内少数载流子的产生而导致的。

参考答案:正确3.减薄p+n突变结的轻掺杂区厚度,不但能减少存储电荷,还能降低反向抽取电流。

参考答案:错误4.在异质结双极型晶体管中,通常用()。

参考答案:宽禁带材料制作发射区,用窄禁带材料制作基区5.( )的集电结反向电压VCB称为共基极集电结雪崩击穿电压,记为BVCBO。

参考答案:发射极开路时,使6.【图片】对高频小信号注入效率的影响的物理意义是,【图片】的存在意味着【图片】必须先付出对势垒区充放电的多子电流【图片】后,才能建立起一定的【图片】。

这一过程需要的时间是()。

参考答案:发射结势垒电容充放电时间常数7.某长方形扩散区的方块电阻为200Ω,长度和宽度分别为100μm和20μm,则其长度方向的电阻为()。

参考答案:1KW8.要提高均匀基区晶体管的电流放大系数的方法()。

参考答案:减小基区掺杂浓度_减小基区宽度9.防止基区穿通的措施是提高()。

参考答案:增大基区宽度_增大基区掺杂浓度10.从发射结注入基区的少子,由于渡越基区需要时间tb ,将对输运过程产生三方面的影响( )。

参考答案:时间延迟使相位滞后_渡越时间的分散使减小_复合损失使小于111.晶体管的共发射极输出特性是指以输入端电流【图片】作参量,输出端电流【图片】与输出端电压【图片】之间的关系。

参考答案:正确12.电流放大系数与频率成反比,频率每提高一倍,电流放大系数下降一半,功率增益降为四分之一。

参考答案:正确13.特征频率【图片】代表的是共发射极接法的晶体管有电流放大能力的频率极限,而最高振荡频率【图片】则代表晶体管有功率放大能力的频率极限。

参考答案:正确14.模拟电路中的晶体管主要工作在()区。

参考答案:放大15.共发射极电路中,基极电流IB是输入电流,集电极电流IC是输出电流。

微电子器件期末试题

微电子器件期末试题一、填空题1.PN结中P区和N区的掺杂浓度分别为NA和ND,本征载流子浓度为ni,kTNANDln则PN结内建电势Vbi的表达式Vbi?。

2qni2.对于单边突变结P?N结,耗尽区主要分布在N区,该区浓度越低,则耗尽区宽度值越大,内建电场的最大值越小;随着正向偏压的增加,耗尽区宽度值降低,耗尽区内的电场降低,扩散电流提高;为了提高P?N结二极管的雪崩击穿电压,应降低N区的浓度,这将提高反向饱和电流IS。

解析:?|E|_n?sma_qND_p?_d??s|Ema_|qNA?s|Ema_|?s|Ema_|qND_n?qNA??s?111?)| Ema_|?s|Ema_|qNDNAqN0(?s11Vbi???Ed_?(_n?_p)|Ema_|?|Ema_|2?_p22qN0|Ema_ |?(2qN0Vbi)?[122kTNANDln(?sNAND)12ni]2?s(NA?ND)对于单边突变结,可通过适当降低轻掺杂一侧的掺杂浓度,使势垒区拉宽来提高雪崩击穿电压。

反向饱和电流IS?(qDpLpDpqDnDn2pn?np)?qni(?)LnLpNDLnNA3.在设计和制造晶体管时,为提高晶体管的电流放大系数,应当增加发射区和基区的掺杂浓度的比值解析:???_??[1?(NE,降低基区宽度。

NB?1WB2DWNR)](1?EBB)?(1?b)(1?口E) 2LBDBWENE?BR口BqV,此2kT4.对于硅PN 结,当V0.45V时,电流密度J满足关系式lnJ?qV,此时以正向扩散电流为主;在室温下,反向电流以势垒区kT产生电流为主,该电流与ni存在?ni关系。

解析:当温度较低时,总的反射电流中以势垒区产生电流为主;当温度较高时,则以反射扩散电流为主。

对于硅PN结,在室温下以势垒区产生电流为主,只有在很高的温度下才以反向扩散电流为主。

反向扩散电流含ni2因子,势垒区产生电流则含?ni因子。

微电子器件 简答题 答案更正

微电子器件

期末考试复习题答案更正及补充

(简答题部分)

主?

答:当 V 比较小时,以 J r 为主; 当 V 比较大时,以 J d 为主。

E G 越大,则过渡电压值就越高。

补:7 、 什么是小注入条件?什么是大注入条件?写出小注入条件和大注入条件下的结定律,并讨论两种情况下中性区边界上载流子浓度随外加电压的变化规律。

大注入,就是注入到半导体中的非平衡少数载流子浓度接近或者超过原来的平衡多数载流子浓度时的一种情况。

改:14、提高基区掺杂浓度会对晶体管的各种特性,如 γ、α、β、

TE C 、EBO BV 、pt V 、A V 、bb r '等

产生什么影响?

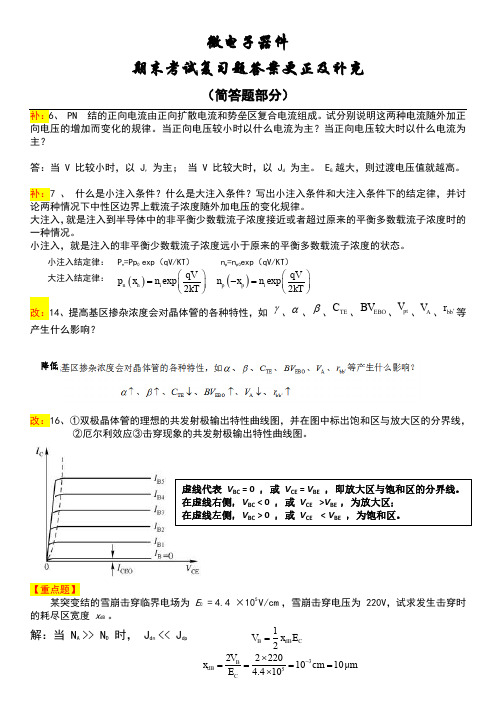

改:16、①双极晶体管的理想的共发射极输出特性曲线图,并在图中标出饱和区与放大区的分界线,

②厄尔利效应③击穿现象的共发射极输出特性曲线图。

【重点题】

某突变结的雪崩击穿临界电场为 E C = 4.4 ×105 V/cm ,雪崩击穿电压为 220V ,试求发生击穿时

的耗尽区宽度 x dB 。

解:当 N A >> N D 时, J dn << J dp

降低

虚线代表 V BC = 0 ,或 V CE = V BE ,即放大区与饱和区的分界线。

在虚线右侧,V BC < 0 ,或 V CE >V BE ,为放大区;

在虚线左侧,V BC > 0 ,或 V CE < V BE ,为饱和区。

B dB

C 3B dB 5C 12

2222010cm 10μm 4.410V x E V x E -=⨯====⨯。

微电子器件复习题

一、填空题1.突变PN 结低掺杂侧的掺杂浓度越高,则势垒区的长度就越 小 ,建电场的最大值越 大 ,建电势V bi 就越 大 ,反向饱和电流I 0就越 小 ,势垒电容C T 就越 大 ,雪崩击穿电压就越 小 。

P272.在PN 结的空间电荷区中,P 区一侧带 负 电荷,N 区一侧带 正 电荷。

建电场的方向是从 N 区指向 P 区。

3.当采用耗尽近似时,N 型耗尽区中的泊松方程为 。

由此方程可以看出,掺杂浓度越高,则建电场的斜率越 大 。

4.若某突变PN 结的P 型区的掺杂浓度为183A 1.510cm N -=⨯,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为 和 。

5.某硅突变PN 结的153D N 1.510cm -=⨯,31810.51N -⨯=cm A ,则室温下n0n0p0n p p 、、和p0n 的分别为 、 、 和 ,当外加0.5V 正向电压时的p p ()n x -和n n ()p x 分别为 、 ,建电势为 。

6.当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度 大 ;当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度 小 。

7.PN 结的正向电流很大,是因为正向电流的电荷来源是 多子 ;PN 结的反向电流很小,是因为反向电流的电荷来源是 少子 。

8.PN 结的正向电流由 空穴扩散电流 电流、 电子扩散电流 电流和 势垒区复和电流 电流三部分所组成。

9.PN 结的直流电流电压方程的分布为 。

10.薄基区二极管是指PN 结的某一个或两个中性区的长度小于 该区的少子扩散长度 。

在薄基区二极管中,少子浓度的分布近似为 线性 ;薄基区二极管相对厚基区二极管来说,其它参数都相同,则PN 结电流会 大的多 。

11.小注入条件是指注入某区边界附近的 非平衡少子 浓度远小于该区的 平衡多子 浓度。

12.大注入条件是指注入某区边界附近的 非平衡少子 浓度远大于该区的 平衡多子 浓度。

微电子期末考试复习题(附答案)

1. 光敏半导体、掺杂半导体、热敏半导体是固体的三种基本类型。

( × ) 2.用来做芯片的高纯硅被称为半导体级硅,有时也被称为分子级硅。

(×)电子3. 硅和锗都是Ⅳ族元素,它们具有正方体结构。

( × ) 金刚石结构4.硅是地壳外层中含量仅次于氮的元素。

( × ) 氧5.镓是微电子工业中应用最广泛的半导体材料,占整个电子材料的95%左右。

( × ) 硅6.晶圆的英文是wafer,其常用的材料是硅和锡。

( × ) 硅和锗7.非晶、多晶、单晶是固体的三种基本类型。

( √ )8.晶体性质的基本特征之一是具有方向性。

( √ )9.热氧化生长的SiO2属于液态类。

( × ) 非结晶态10.在微电子学中的空间尺寸通常是以μm和mm为单位的。

( × )um和nm 11.微电子学中实现的电路和系统又称为数字集成电路和集成系统,是微小化的。

( × ) 集成电路12.微电子学是以实现数字电路和系统的集成为目的的。

( × ) 电路13.采用硅锭形成发射区接触可以大大改善晶体管的电流增益和缩小器件的纵向尺寸。

( √ )14.集成电路封装的类型非常多样化。

按管壳的材料可以分为金属封装、陶瓷封装和塑料封装。

( √ )15.源极氧化层是MOS器件的核心。

( × ) 栅极16. 一般认为MOS集成电路功耗高、集成度高,不宜用作数字集成电路。

( × ) 功耗低,宜做17. 反映半导体中载流子导电能力的一个重要参数是迁移率。

( √ )18. 双极型晶体管可以作为放大晶体管,也可以作为开关来使用。

( √ )19. 在P型半导体中电子是多子,空穴是少子。

( × ) 空穴是多子20. 双极型晶体管其有两种基本结构:PNP型和NPN 型。

( √ )21. 在数字电路中,双极型晶体管是当成开关来使用的。

( √ )22. 双极型晶体管可以用来产生、放大和处理各种模拟电信号。

《微电子器件原理》复习题课件

《微电⼦器件原理》复习题课件考试时间: (第⼗周周⼆6-8节)考试地点:待定《微电⼦器件原理》复习题及部分答案⼀、填空1、PN结电容可分为扩散电容和过渡区电容两种,它们之间的主要区别在于扩散电容产⽣于过渡区外的⼀个扩散长度范围内,其机理为少⼦的充放电,⽽过渡区电容产⽣于空间电荷区,其机理为多⼦的注⼊和耗尽。

2、当MOSFET器件尺⼨缩⼩时会对其阈值电压V T产⽣影响,具体地,对于短沟道器件对V T的影响为下降,对于窄沟道器件对V T的影响为上升。

3、在NPN型BJT中其集电极电流I C受V BE电压控制,其基极电流I B受V BE电压控制。

4、硅-绝缘体SOI器件可⽤标准的MOS⼯艺制备,该类器件显著的优点是寄⽣参数⼩,响应速度快等。

5、PN结击穿的机制主要有雪崩击穿、齐纳击穿、热击穿等等⼏种,其中发⽣雪崩击穿的条件为V B>6E g/q。

6、当MOSFET进⼊饱和区之后,漏电流发⽣不饱和现象,其中主要的原因有沟道长度调制效应,漏沟静电反馈效应和空间电荷限制效应。

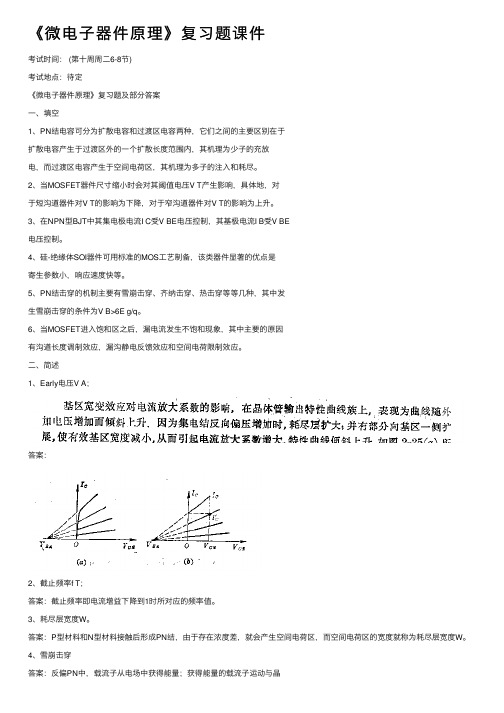

⼆、简述1、Early电压V A;答案:2、截⽌频率f T;答案:截⽌频率即电流增益下降到1时所对应的频率值。

3、耗尽层宽度W。

答案:P型材料和N型材料接触后形成PN结,由于存在浓度差,就会产⽣空间电荷区,⽽空间电荷区的宽度就称为耗尽层宽度W。

4、雪崩击穿答案:反偏PN中,载流⼦从电场中获得能量;获得能量的载流⼦运动与晶格相碰,使满带电⼦激出到导带,通过碰撞电离由电离产⽣的载流⼦(电⼦空⽳对)及原来的载流⼦⼜能通过再碰撞电离,造成载流⼦倍增效应,当倍增效应⾜够强的时候,将发⽣“雪崩”——从⽽出现⼤电流,造成PN结击穿,此称为“雪崩击穿”。

5、简述正偏PN结的电流中少⼦与多⼦的转换过程。

答案:N型区中的电⼦,在外加电压的作⽤下,向边界Xn漂移,越过空间电荷区,在边界Xp形成⾮平衡少⼦分布,注⼊到P区的少⼦,然后向体内扩散形成电⼦扩散电流,在扩散过程中电⼦与对⾯漂移过来的空⽳不断复合,结果电⼦扩散电流不断转为空⽳漂移电流.空⽳从P区向N区运动也类同.6、太阳电池和光电⼆极管的主要异同点有哪些?答案:相同点:都是应⽤光⽣伏打效应⼯作的器件。

《微电子器件》题集

《微电子器件》题集一、选择题(每题2分,共20分)1.下列哪种材料常用于制造微电子器件中的晶体管?A. 硅(Si)B. 铜(Cu)C. 铝(Al)D. 铁(Fe)2.在CMOS逻辑电路中,哪种类型的逻辑门在输入为高电平时导通?A. NAND门B. NOR门C. AND门D. OR门3.以下哪个参数描述的是二极管的电流放大能力?A. 击穿电压B. 反向电流C. 电流放大系数D. 截止频率4.在集成电路制造中,哪种工艺步骤用于定义晶体管和其他元件的几何形状?A. 氧化B. 扩散C. 光刻D. 金属化5.MOSFET器件中,栅极电压对沟道电流的控制是通过什么机制实现的?A. 欧姆定律B. 量子隧穿效应C. 电场效应D. 热电子发射6.下列哪项技术用于减小集成电路中的寄生电容和电阻?A. SOI技术B. BICMOS技术C. CMOS技术D. TTL技术7.在半导体存储器中,DRAM与SRAM相比,主要缺点是什么?A. 成本高B. 速度慢C. 需要定期刷新D. 功耗高8.下列哪种类型的二极管常用于微波电子器件中?A. 肖特基二极管B. 光电二极管C. 变容二极管D. 整流二极管9.集成电路的特征尺寸越小,通常意味着什么?A. 集成度越低B. 性能越差C. 功耗越高D. 制造成本越高10.在半导体工艺中,哪种掺杂技术用于形成P-N结?A. 离子注入B. 扩散C. 外延生长D. 氧化二、填空题(每空2分,共20分)1.在CMOS逻辑电路中,当输入信号为低电平时,PMOS晶体管处于______状态,而NMOS晶体管处于______状态。

2.二极管的正向电压超过一定值时,电流会急剧增加,这个电压值称为二极管的______电压。

3.在集成电路制造中,______步骤用于形成晶体管的栅极、源极和漏极。

4.MOSFET器件的沟道长度减小会导致______效应增强,从而影响器件的性能。

5.DRAM存储单元由一个晶体管和一个______组成。

微电子学概论复习题及答案(详细版).

Vgs Vtn

2

2

截至区(Cut off): Vgs – Vt ≤0 Ids=0

8.MOS 晶体管分类 答:按载流子类型分:

• NMOS: 也称为 N 沟道,载流子为电子。 • PMOS: 也称为 P 沟道,载流子为空穴。 按导通类型分: • 增强(常闭)型:必须在栅上施加电压才能形成沟道。 • 耗尽(常开)型:在零偏压下存在反型层导电沟道,必须在栅上施加偏压才能使沟道

4.半导体中的载流子、迁移率(课件)

半导体中的载流子:在半导体中,存在两种载流子,电子以及电子流失导致共价键上留下的

空位(空穴)均被视为载流子。通常 N 型半导体中指自由电子,P 型半导体中指空穴,它们

在电场作用下能作定向运动,形成电流。

q

m

迁移率:单位电场作用下载流子获得平均速度,反映了载流子在电场作用下输运能力

什么是半导体? 金属:电导率 106~104(W∙cm-1),不含禁带; 半导体:电导率 104~10-10(W∙cm-1),含禁带; 绝缘体:电导率<10-10(W∙cm-1),禁带较宽; 半导体的特点: (1)电导率随温度上升而指数上升; (2)杂质的种类和数量决定其电导率; (3)可以实现非均匀掺杂; (4)光辐照、高能电子注入、电场和磁场等影响其电导率; 硅:地球上含量最丰富的元素之一,微电子产业用量最大、也是最重要的半导体材料。 硅(原子序数 14)的物理化学性质主要由最外层四个电子(称为价电子)决定。每个硅原子 近邻有四个硅原子,每两个相邻原子之间有一对电子,它们与两个原子核都有吸引作用, 称为共价键。 化合物半导体:III 族元素和 V 族构成的 III-V 族化合物,如,GaAs(砷化镓),InSb(锑 化铟),GaP(磷化镓),InP(磷化铟)等,广泛用于光电器件、半导体激光器和微波器件。 2.掺杂、施主/受主、P 型/N 型半导体(课件)

微电子器件 (附答案) (第三版)

DE DB

−1

9、

= IC

A= E JnC

AE β= ∗ JnE

AE β

∗

qDBni2 WB NB

exp

qVBE kT

式中,β ∗

= 1− 12

WB LB

2

= 1− WB2

2DBτ B

= 0.9986

将 A=E 104 μm2 ,β=∗ 0.9986, =q 1.6 ×10−19 C,

15、

γ

= 1− DEWB NB ,γ

DBWE NE

npn

= 1− DpWB NB , DnWE NE

γ

pnp

= 1− DnWB NB DpWE NE

由 D kT 可知,D ∝ µ µq

µn > µp , ∴ Dn > Dp , γ npn > γ pnp

β∗

= 1− WB2 ,

2DBτ B

β* npn

当 xi 增大时,Emax 减小, 当 xi → ∞sh时a, nrEenmax → 0

20、

已知: = σ p σn

= 由于 Jdp

= J dn

因此

J d=p J dn

qµ= p NA µp NA >> 1 qµn ND µn ND

qDp ni2 Lp ND

exp

qV kT

−

1

qDn ni2 Ln NA

shanren

6、

ND2

ND1

由平衡时多子电流为零

Jn

=

qDn

dn dx

+

qµn nE

=

0

得: E =− Dn ⋅ 1 ⋅ dn =− kT ⋅ 1 ⋅ dn =− kT ⋅ d ln n

微电子器件基础知识单选题100道及答案解析

微电子器件基础知识单选题100道及答案解析1. 微电子器件的核心是()A. 晶体管B. 电容器C. 电阻器D. 电感器答案:A解析:晶体管是微电子器件的核心。

2. 以下哪种材料常用于半导体制造?()A. 铜B. 硅C. 铝D. 银答案:B解析:硅是常用于半导体制造的材料。

3. 半导体中的载流子主要包括()A. 电子和质子B. 电子和空穴C. 正离子和负离子D. 中子和电子答案:B解析:半导体中的载流子主要是电子和空穴。

4. PN 结的主要特性是()A. 单向导电性B. 双向导电性C. 电阻不变性D. 电容不变性答案:A解析:PN 结的主要特性是单向导电性。

5. 场效应管是()控制型器件。

A. 电流B. 电压C. 电阻D. 电容答案:B解析:场效应管是电压控制型器件。

6. 双极型晶体管是()控制型器件。

A. 电流B. 电压C. 电阻D. 电容答案:A解析:双极型晶体管是电流控制型器件。

7. 集成电路的集成度主要取决于()A. 芯片面积B. 晶体管数量C. 制造工艺D. 封装技术答案:B解析:集成电路的集成度主要取决于晶体管数量。

8. 以下哪种工艺常用于芯片制造?()A. 蚀刻B. 锻造C. 铸造D. 车削答案:A解析:蚀刻工艺常用于芯片制造。

9. 微电子器件的性能参数不包括()A. 电流放大倍数B. 输入电阻C. 输出电阻D. 重量答案:D解析:重量不是微电子器件的性能参数。

10. 增强型MOS 管的阈值电压()A. 大于0B. 小于0C. 等于0D. 不确定答案:A解析:增强型MOS 管的阈值电压大于0 。

11. 耗尽型MOS 管的阈值电压()A. 大于0B. 小于0C. 等于0D. 不确定答案:B解析:耗尽型MOS 管的阈值电压小于0 。

12. 半导体中的施主杂质提供()A. 电子B. 空穴C. 质子D. 中子答案:A解析:半导体中的施主杂质提供电子。

13. 半导体中的受主杂质提供()A. 电子B. 空穴C. 质子D. 中子答案:B解析:半导体中的受主杂质提供空穴。

微电子器件期末复习题含答案

在无能为力,后期会继续上传计算题集锦,敬请期待。

另,由于本人微电子班,无光源班群,请有心人士转载至光源班群,共同通过

期末考试!

微电子器件(第三版)陈星弼

电子科技大学中山学院/——1

陈卉/题目 王嘉达/答案

答案为个人整理,如有错误请 仔细甄别 ! 厚德 博学 求是 创新

29、晶体管的共发射极直流短路电流放大系数

是指(发射)结正偏、(集电)结零

偏时的(集电极)电流与(基极)电流之比。

30、在设计与制造晶体管时,为提高晶体管的电流放大系数,应当(减小)基区宽度,

(降低)基区掺杂浓度。

31、某长方形薄层材料的方块电阻为 100Ω,长度和宽度分别为 300μm 和 60μm ,则

振荡频率 f M 。

59、晶体管的高频优值 M 是(功率增益)与(带宽)的乘积。

60、晶体管的高频小信号等效电路与直流小信号等效电路相比,增加了三个元件,它

们是(集电结势垒电容)

、(发射结势垒电容)和(发射结扩散电容)

。

61、对于频率不是特别高的一般高频管, ec 中以( Ib )为主,这时提高特征频率 f T 的

主要措施是(减小基区宽度)

。

微电子器件(第三版)陈星弼

电子科技大学中山学院/——6

陈卉/题目 王嘉达/答案

答案为个人整理,如有错误请 仔细甄别 ! 厚德 博学 求是 创新

62、为了提高晶体管的最高振荡频率 f M ,应当使特征频率 f T(增大)

,基极电阻 rbb(降

低)

,集电结势垒电容 CTC (降低)

场的方向是从(N)区指向(P)区。[发生漂移运动,空穴向 P 区,电子向 N 区]

微电子器件课程复习题

微电子器件课程复习题1、若某突变PN 结的P 型区的掺杂浓度为163A1.510cm N -=?,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为(316105.1-?=cm N A )和(314105.1-?=cm NA )。

2、在PN 结的空间电荷区中,P 区一侧带(负)电荷,N 区一侧带(正)电荷。

内建电场的方向是从(N )区指向(P )区。

[发生漂移运动,空穴向P 区,电子向N 区]3、当采用耗尽近似时,N 型耗尽区中的泊松方程为(D S E u q dx d ε=→)。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越(大)。

4、PN 结的掺杂浓度越高,则势垒区的长度就越(小),内建电场的最大值就越(大),内建电势V bi 就越(大),反向饱和电流I 0就越(小)[P20],势垒电容C T 就越(大),雪崩击穿电压就越(小)。

5、硅突变结内建电势V bi 可表为(2ln iD A bi n N N q KT v =)P9,在室温下的典型值为(0.8)伏特。

6、当对PN 结外加正向电压时,其势垒区宽度会(减小),势垒区的势垒高度会(降低)。

7、当对PN 结外加反向电压时,其势垒区宽度会(增大),势垒区的势垒高度会(提高)。

8、在P 型中性区与耗尽区的边界上,少子浓度n p 与外加电压V 之间的关系可表示为()exp()(0KTqv p p p n x n =-)P18。

若P 型区的掺杂浓度173A 1.510cm N -=?,外加电压V = 0.52V ,则P 型区与耗尽区边界上的少子浓度n p 为(3251035.7-?cm )。

9、当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(大);当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(小)。

10、PN 结的正向电流由(空穴扩散)电流、(电子扩散)电流和(势垒区复合)电流三部分所组成。

《微电子器件》大学题集

《微电子器件》题集一、选择题(每题2分,共20分)1.微电子技术的核心是基于哪种材料的半导体器件?()A. 硅(Si)B. 锗(Ge)C. 砷化镓(GaAs)D. 氮化硅(Si₃N₃)2.在CMOS集成电路中,NMOS和PMOS晶体管的主要作用是?()A. 分别实现逻辑“1”和逻辑“0”的输出B. 作为开关控制电流的通断C. 用于构成存储单元D. 提供稳定的电压基准3.下列哪项不是PN结二极管的主要特性?()A. 单向导电性B. 击穿电压高C. 温度稳定性好D. 具有放大功能4.在MOSFET中,栅极电压对沟道电流的控制是通过什么机制实现的?()A. 改变沟道宽度B. 改变耗尽层宽度C. 改变载流子浓度D. 改变源漏间电阻5.双极型晶体管(BJT)在放大区工作时,集电极电流与基极电流的比值称为?()A. 放大倍数B. 电流增益C. 电压增益D. 功耗比6.下列哪种材料常用于制作微电子器件中的绝缘层?()A. 二氧化硅(SiO₃)B. 氧化铝(Al₃O₃)C. 氮化硼(BN)D. 碳化硅(SiC)7.在集成电路制造过程中,光刻技术的关键步骤是?()A. 涂胶B. 曝光C. 显影D. 以上都是8.下列哪项技术用于提高集成电路的集成度?()A. 减小特征尺寸B. 增加芯片面积C. 使用更厚的衬底D. 降低工作温度9.微电子器件中的金属-氧化物-半导体 (MOS)结构,其氧化物层的主要作用是?()A. 提供导电通道B. 隔绝栅极与沟道C. 存储电荷D. 增强电场效应10.在CMOS逻辑电路中,静态功耗主要由什么因素决定?()A. 漏电流B. 开关频率C. 逻辑门数量D. 电源电压与漏电流的共同作用二、填空题(每题2分,共20分)1.微电子器件的基本单元是_______,它通过控制_______来实现对电流的调控。

2.在PN结正向偏置时,_______区的多数载流子向_______区扩散,形成正向电流。

3.MOSFET的阈值电压是指使沟道开始形成_______的最小栅极电压。

半导体微电子器件考试习题课与答案

势垒高度

ni2

复习-PN结

PN结总电流(肖克莱方程)

Dn np0 Dp pn0 kqV T J = q + e 0 1 L Lp n

肖克莱方程是在理想PN结条件下导出的, 它只是揭示了PN结导电性质的基本原理. 但实际的PN结与它有差异,主要是因为没 有考虑以下效应(1)表面效应(2)势垒 区中的载流子产生和复合(3)大注入效应 (4)串联电阻效应

复习-PN结

所产生的电势差称为自建电势差,其作用是 对载流子的扩散运动形成势垒,使载流子通 过结的净流动为零,达到平衡.这个势垒的 存在使整个结构在结区形成能带弯曲,其弯 曲高度称为势垒高度,它恰恰补偿了原来两 边半导体中费米能级的高度差,使两边达到 等高的同意费米能级. N NA

N P qVD = EF EF = k0T ln D

第十章作业

10.1均匀掺杂的n++p+n型双极晶体管, 处于热平衡状态.(a)画出其能带图, a (b)画出器件中的电场,(c)晶体管 处于正向有源区时,重复(a)和(b).

第十章作业

10.5(a)一个双极晶体管工作于正向 有源区,基极电流iB=6.0A,集电极电 i =6.0A 流iC=6.0A.计算β,α和iE.对于 iB=50A,iC=2.65mA,重复(a).

1,讨论影响共射极电流增益பைடு நூலகம்的因素

β≈

1 NB DE x B 1 x B J r 0 eVBE + + exp NE DB x E 2 LB J s 0 2kT

2

出现在P278表10.3 其中NB,NE为基极,发射极掺杂浓度DB, DE为基极,发射极少子扩散系数,xB,xE 为中性基极,发射极宽度,LB为基区少子扩 散长度,Jr0,Js0为零偏复合电流和饱和电 流密度

微电子器件复习题

微电子器件复习题一、填空题1.突变PN 结低掺杂侧的掺杂浓度越高,则势垒区的长度就越小,内建电场的最大值越大,内建电势V bi 就越大,反向饱和电流I 0就越小,势垒电容C T 就越大,雪崩击穿电压就越小。

P272.在PN 结的空间电荷区中,P 区一侧带负电荷,N 区一侧带正电荷。

内建电场的方向是从 N 区指向 P 区。

3.当采用耗尽近似时,N 型耗尽区中的泊松方程为。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越大。

4.若某突变PN 结的P 型区的掺杂浓度为183A1.510cm N -=?,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为和。

5.某硅突变PN 结的153D N 1.510cm -=?,31810.51N -?=cm A ,则室温下n0n0p0n p p 、、和p0n 的分别为、、和,当外加0.5V 正向电压时的p p ()n x -和n n ()p x 分别为、,内建电势为。

6.当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度大;当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度小。

7.PN 结的正向电流很大,是因为正向电流的电荷来源是多子;PN 结的反向电流很小,是因为反向电流的电荷来源是少子。

8.PN 结的正向电流由空穴扩散电流电流、电子扩散电流电流和势垒区复和电流电流三部分所组成。

9.PN 结的直流电流电压方程的分布为。

10.薄基区二极管是指PN 结的某一个或两个中性区的长度小于该区的少子扩散长度。

在薄基区二极管中,少子浓度的分布近似为线性;薄基区二极管相对厚基区二极管来说,其它参数都相同,则PN 结电流会大的多。

11.小注入条件是指注入某区边界附近的非平衡少子浓度远小于该区的平衡多子浓度。

12.大注入条件是指注入某区边界附近的非平衡少子浓度远大于该区的平衡多子浓度。

13.势垒电容反映的是PN 结的微分电荷随外加电压的变化率。

微电子材料与器件复习题(终极版)(1)

微电⼦材料与器件复习题(终极版)(1)《微电⼦材料与器件》复习题1.设计制备NMOSFET的⼯艺,并画出流程图。

概括的说就是先场氧,后栅氧,再淀多晶SI,最后有源区注⼊(1)衬底P-SI;(2)初始氧化;光刻I;场区注硼,注硼是为了提⾼场区的表⾯浓度,以提⾼场开启;场区氧化;去掉有源区的SI3N4和SIO2;预栅氧,为离⼦注⼊作准备;调整阈电压注⼊(注硼),⽬的是改变有源区表⾯的掺杂浓度,获得要求的晶硅;光刻II,刻多晶硅,不去胶;离⼦注⼊,源漏区注砷,热退⽕;去胶,低温淀积SIO2;光刻III刻引线孔;蒸铝;光刻IV刻电极;形成N阱初始氧化淀积氮化硅层光刻1版,定义出N阱反应离⼦刻蚀氮化硅层N阱离⼦注⼊,注磷形成P阱去掉光刻胶在N阱区⽣长厚氧化层,其它区域被氮化硅层保护⽽不会被氧化去掉氮化硅层P阱离⼦注⼊,注硼推阱退⽕驱⼊去掉N阱区的氧化层形成场隔离区⽣长⼀层薄氧化层淀积⼀层氮化硅光刻场隔离区,⾮隔离区被光刻胶保护起来反应离⼦刻蚀氮化硅场区离⼦注⼊热⽣长厚的场氧化层去掉氮化硅层形成多晶硅栅⽣长栅氧化层淀积多晶硅光刻多晶硅栅刻蚀多晶硅栅形成硅化物淀积氧化层反应离⼦刻蚀氧化层,形成侧壁氧化层淀积难熔⾦属Ti或Co等低温退⽕,形成C-47相的TiSi2或CoSi去掉氧化层上的没有发⽣化学反应的Ti或Co⾼温退⽕,形成低阻稳定的TiSi2或CoSi2形成N管源漏区光刻,利⽤光刻胶将PMOS区保护起来离⼦注⼊磷或砷,形成N管源漏区形成P管源漏区光刻,利⽤光刻胶将NMOS区保护起来离⼦注⼊硼,形成P管源漏区形成接触孔化学⽓相淀积磷硅玻璃层退⽕和致密光刻接触孔版反应离⼦刻蚀磷硅玻璃,形成接触孔形成第⼀层⾦属淀积⾦属钨(W),形成钨塞淀积⾦属层,如Al-Si、Al-Si-Cu合⾦等光刻第⼀层⾦属版,定义出连线图形反应离⼦刻蚀⾦属层,形成互连图形形成穿通接触孔化学⽓相淀积PETEOS通过化学机械抛光进⾏平坦化光刻穿通接触孔版反应离⼦刻蚀绝缘层,形成穿通接触孔形成第⼆层⾦属淀积⾦属层,如Al-Si、Al-Si-Cu合⾦等光刻第⼆层⾦属版,定义出连线图形反应离⼦刻蚀,形成第⼆层⾦属互连图形合⾦形成钝化层在低温条件下(⼩于300℃)淀积氮化硅光刻钝化版刻蚀氮化硅,形成钝化图形测试、封装,完成集成电路的制造⼯艺2.集成电路⼯艺主要分为哪⼏⼤类,每⼀类中包括哪些主要⼯艺,并简述各⼯艺的主要作⽤。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

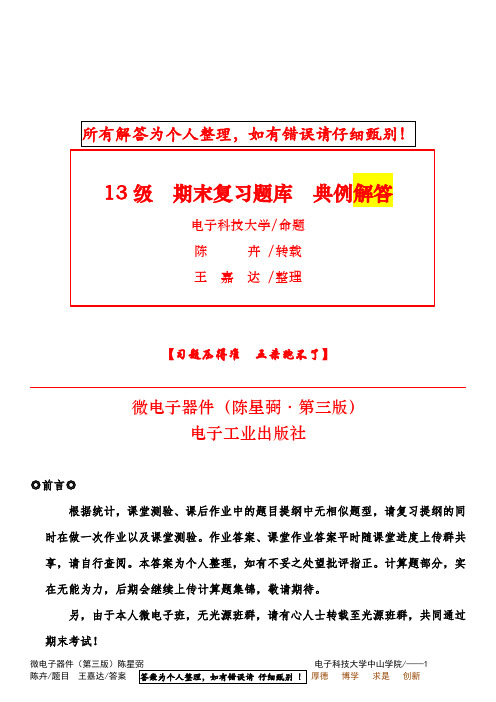

【习题压得准五杀跑不了】微电子器件(陈星弼·第三版)电子工业出版社◎前言◎根据统计,课堂测验、课后作业中的题目提纲中无相似题型,请复习提纲的同时在做一次作业以及课堂测验。

作业答案、课堂作业答案平时随课堂进度上传群共享,请自行查阅。

本答案为个人整理,如有不妥之处望批评指正。

计算题部分,实在无能为力,后期会继续上传计算题集锦,敬请期待。

另,由于本人微电子班,无光源班群,请有心人士转载至光源班群,共同通过1、若某突变PN 结的P 型区的掺杂浓度为163A 1.510cm N -=⨯,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为(316105.1-⨯=cm N A )和(314105.1-⨯=cm N A )。

2、在PN 结的空间电荷区中,P 区一侧带(负)电荷,N 区一侧带(正)电荷。

内建电场的方向是从(N )区指向(P )区。

[发生漂移运动,空穴向P 区,电子向N 区]3、当采用耗尽近似时,N 。

由此方程可以看出,掺杂浓度越高,则内建电场的斜率越(大)。

4、PN 结的掺杂浓度越高,则势垒区的长度就越(小),内建电场的最大值就越(大),内建电势V bi 就越(大),反向饱和电流I 0就越(小)[P20],势垒电容C T 就越( 大 ),雪崩击穿电压就越(小)。

5、硅突变结内建电势V bi )[P9]在室温下的典型值为(0.8V )6、当对PN结外加正向电压时,其势垒区宽度会(减小),势垒区的势垒高度会(降低)。

7、当对PN 结外加反向电压时,其势垒区宽度会(增大),势垒区的势垒高度会(提高)。

8、在P 型中性区与耗尽区的边界上,少子浓度n p 与外加电压V 之间的关系可表示为P18。

若P 型区的掺杂浓度173A 1.510cm N -=⨯,外加电压V = 0.52V ,则P 型区与耗尽区边界上的少子浓度n p 为(3251035.7-⨯cm )。

9、当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(大);当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(小)。

10、PN 结的正向电流由(空穴扩散)电流、(电子扩散)电流和(势垒区复合)电流三部分所组成。

11、PN 结的正向电流很大,是因为正向电流的电荷来源是(多子);PN 结的反向电流12、当对PN结外加正向电压时,由N区注入P区的非平衡电子一边向前扩散,一边(复合)。

每经过一个扩散长度的距离,非平衡电子浓度降到原来的(1e)。

13、PN。

这个表达式在正向电,在反向电压下可简化为(JJ d-=)。

14、在PN结的正向电流中,当电压较低时,以(势垒区复合)电流为主;当电压较高时,以(扩散)电流为主。

15、薄基区二极管是指PN结的某一个或两个中性区的长度小于(该区的少子扩散长度)。

在薄基区二极管中,少子浓度的分布近似为(线性分布)。

16、小注入条件是指注入某区边界附近的(非平衡少子)浓度远小于该区的(平衡多子)浓度,因此该区总的多子浓度中的(非平衡)多子浓度可以忽略。

17、大注入条件是指注入某区边界附近的(非平衡少子)浓度远大于该区的(平衡多子)浓度,因此该区总的多子浓度中的(平衡)多子浓度可以忽略。

18、势垒电容反映的是PN结的(微分)电荷随外加电压的变化率。

PN结的掺杂浓度越高,则势垒电容就越(大);外加反向电压越高,则势垒电容就越(小)。

19、扩散电容反映的是PN结的(非平衡载流子)电荷随外加电压的变化率。

正向电流越大,则扩散电容就越(大);少子寿命越长,则扩散电容就越(大)。

【P51】20、在PN结开关管中,在外加电压从正向变为反向后的一段时间内,会出现一个较大的反向电流。

引起这个电流的原因是存储在(N)区中的(非平衡载流子)电荷。

这个电荷的消失途径有两条,即(反向电流的抽取)和(少子自身的复合)。

21、从器件本身的角度,提高开关管的开关速度的主要措施是(降低少子寿命)和(加快反向复合)。

(减薄轻掺杂区的厚度)22、PN结的击穿有三种机理,它们分别是(雪崩击穿)、(齐纳击穿)和(热击穿)。

23、PN结的掺杂浓度越高,雪崩击穿电压越(小);结深越浅,雪崩击穿电压就越(小)。

24、雪崩击穿和齐纳击穿的条件分别是(10→⎰dx i rd α)和(。

[P41] 25、晶体管的基区输运系数是指(基区中到达集电结的少子)电流与(从发射结刚注入基区的少子)电流之比。

[P67]由于少子在渡越基区的过程中会发生(复合),从而使基区输运系数(小于1)。

为了提高基区输运系数,应当使基区宽度(远小于)基区少子扩散长度。

26、晶体管中的少子在渡越(基区)的过程中会发生(复合),从而使到达集电结的少子比从发射结注入基区的少子(小)。

27、晶体管的注入效率是指(从发射区注入基区的少子)电流与(总的发射极)电流之比。

[P69]为了提高注入效率,应当使(发射)区掺杂浓度远大于(基)区掺杂浓度。

28、晶体管的共基极直流短路电流放大系数α是指发射结(正)偏、集电结(零)偏时的(集电极)电流与(发射极)电流之比。

29、晶体管的共发射极直流短路电流放大系数β是指(发射)结正偏、(集电)结零偏时的(集电极)电流与(基极)电流之比。

30、在设计与制造晶体管时,为提高晶体管的电流放大系数,应当(减小)基区宽度,(降低)基区掺杂浓度。

31、某长方形薄层材料的方块电阻为100Ω,长度和宽度分别为300μm 和60μm ,则其长度方向和宽度方向上的电阻分别为(Ω500)和(Ω20)。

若要获得1K Ω的电阻,则该材料的长度应改变为(m μ600)。

32、在缓变基区晶体管的基区中会产生一个(内建电场),它对少子在基区中的运动起到(加速)的作用,使少子的基区渡越时间(减小)。

33、小电流时α会(减小)。

这是由于小电流时,发射极电流中(势垒区复合电流)的比例增大,使注入效率下降。

34、发射区重掺杂效应是指当发射区掺杂浓度太高时,不但不能提高(注入效率),反而会使其(下降)。

造成发射区重掺杂效应的原因是(发射区禁带变窄)和(俄歇复合增强)。

[P76]35、在异质结双极晶体管中,发射区的禁带宽度(大)于基区的禁带宽度,从而使异质结双极晶体管的(注入效率)大于同质结双极晶体管的。

[P79]36、当晶体管处于放大区时,理想情况下集电极电流随集电结反偏的增加而(不变)。

但实际情况下集电极电流随集电结反偏增加而(增加),这称为(基区宽度调变)效应。

[P83]37、当集电结反偏增加时,集电结耗尽区宽度会(变宽),使基区宽度(变窄),从而使集电极电流(增大),这就是基区宽度调变效应(即厄尔利效应)。

[P83]38、I ES 是指(集电结)短路、(发射)结反偏时的(发射)极电流。

39、I CS 是指(发射结)短路、(集电结)反偏时的(集电)极电流。

41、I CBO 是指(发射)极开路、(集电)结反偏时的(集电)极电流。

41、I CEO 是指(基)极开路、(集电)结反偏时的(集电)极电流。

42、I EBO 是指(集电极)极开路、(发射)结反偏时的(发射)极电流。

43、BV CBO 是指(发射)极开路、(集电)结反偏,当(CBO I )∞→时的V CB 。

44、BV CEO 是指(基)极开路、(集电)结反偏,当(CEO I )∞→时的V CE 。

45、BV EBO 是指(集电)极开路、(发射)结反偏,当(EBO I )∞→时的V EB 。

46、基区穿通是指当集电结反向电压增加到使耗尽区将(基区)全部占据时,集电极电流急剧增大的现象。

防止基区穿通的措施是(增加)基区宽度、(提高)基区掺杂浓度。

[P90]47、比较各击穿电压的大小时可知,BV CBO (大于)BV CEO ,BV CBO (远大于)BV EBO 。

48、要降低基极电阻bb r ',应当(提高)基区掺杂浓度,(提高)基区宽度。

50、发射极增量电阻r e 的表达式。

室温下当发射极电流为1mA 时,r e =(Ω26)。

51、随着信号频率的提高,晶体管的ωα、ωβ的幅度会(下降),相角会(滞后)。

52、在高频下,基区渡越时间b τ对晶体管有三个作用,它们是:(复合损失使小于 1β0* 小于 1)、(时间延迟使相位滞后)和(渡越时间的分散使|βω*|减小)。

53、基区渡越时间b τ是指(从发射结渡越到集电结所需要的平均时间)。

当基区宽度加倍时,基区渡越时间增大到原来的(2)倍。

54、晶体管的共基极电流放大系数ωα随频率的(增加)而下降。

当晶体管的ωα下α的截止频率,记为(αf )。

55、晶体管的共发射极电流放大系数ωβ随频率的(增加)而下降。

当晶体管的ωβ下降到021β时的频率,称为β的(截止频率),记为(βf )。

56、当βf f >>时,频率每加倍,晶体管的ωβ降到原来的(½);最大功率增益pmax K 降到原来的(¼)。

57、当(电流放大系数ωβ)降到1时的频率称为特征频率T f 。

当(晶体管最大功率max p )降到1时的频率称为最高振荡频率M f 。

58、当ωβ降到(1)时的频率称为特征频率T f 。

当pmax K 降到(1)时的频率称为最高振荡频率M f 。

59、晶体管的高频优值M 是(功率增益)与(带宽)的乘积。

60、晶体管的高频小信号等效电路与直流小信号等效电路相比,增加了三个元件,它们是(集电结势垒电容)、(发射结势垒电容)和(发射结扩散电容)。

61、对于频率不是特别高的一般高频管,ec τ中以(b I )为主,这时提高特征频率T f 的主要措施是(减小基区宽度)。

62、为了提高晶体管的最高振荡频率M f ,应当使特征频率T f (增大),基极电阻bb r '(降低),集电结势垒电容TC C (降低)。

63、对高频晶体管结构上的基本要求是:(尺寸小)、(结深浅)、(线条细)和(非工作基区重掺杂)。

64、N 沟道MOSFET 的衬底是(P )型半导体,源区和漏区是(N )型半导体,沟道中的载流子是(电子)。

65、P 沟道MOSFET 的衬底是(N )型半导体,源区和漏区是(P )型半导体,沟道中的载流子是(空穴)。

66、当GS T V V =时,栅下的硅表面发生(强反型),形成连通(源)区和(漏)区的导电沟道,在DS V 的作用下产生漏极电流。

67、N 沟道MOSFET 中,GS V 越大,则沟道中的电子就越(多),沟道电阻就越(小),漏极电流就越(大)。

68、在N 沟道MOSFET 中,T 0V >的称为增强型,当GS 0V =时MOSFET 处于(截止)状态;T 0V <的称为耗尽型,当GS 0V =时MOSFET 处于(导通)状态。

69、由于栅氧化层中通常带(正)电荷,所以(P )型区比(N )型区更容易发生反型。