传输线脉冲测试系统1套

GJB151A-RS105

10

数字存储示波器(LeCroy or Tektronix)

1

带宽: 500MHz

记录长度:250Kpt / Ch

采样率:Speed 1Gsa/S/Ch (Single shot)

显示:Color screen

11

现场安装调试培训

1

厂商工程师3天

12

国外工厂培训:2人2天 瑞士

1

二、系统参考价格

被测物尺寸

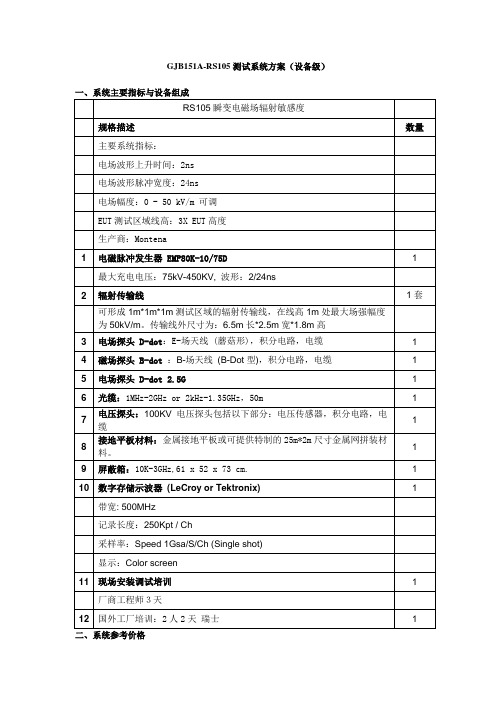

GJB151A-RS105测试系统方案(设备级)

一、系统主要指标与设备组成

RS105瞬变电磁场辐射敏感度

规格描述

数量

主要系统指标:

电场波形上升时间:2ns

电场波形脉冲宽度:24ns

电场幅度:0 - 50 kV/m 可调

EUT测试区域线高:3X EUT高度

生产商:Montena

1

电磁脉冲发生器 EMP80K-10/75D

1

最大充电电压:75kV-450KV,波形:2/24ns

2

辐射传输线

1套

可形成1m*1m*1m测试区域的辐射传输线,在线高1m处最大场强幅度为50kV/m。传输线外尺寸为:6.5m长*2.5m宽*1.8m高

3

电场探头 D-dot:E-场天线 (蘑菇形),积分电路,电缆

1

4

磁场探头 B-dot:B-场天线(B-Dot型),积分电路,电缆

1

5

电场探头 D-dot 2.5G

1

6

光缆:1MHz-2GHz or 2kHz-1.35GHz,50m

1

7

电压探头:100KV电压探头包括以下部分:电压传感器,积分电路,电缆

1

8

接地平板材料:金属接地平板或可提供特制的25m*2m尺寸金属网拼装材料。

Jitter及其测试技术介绍

Jitter及其测试技术介绍本文主要介绍时间抖动(jitter)的概念及其分析方法。

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。

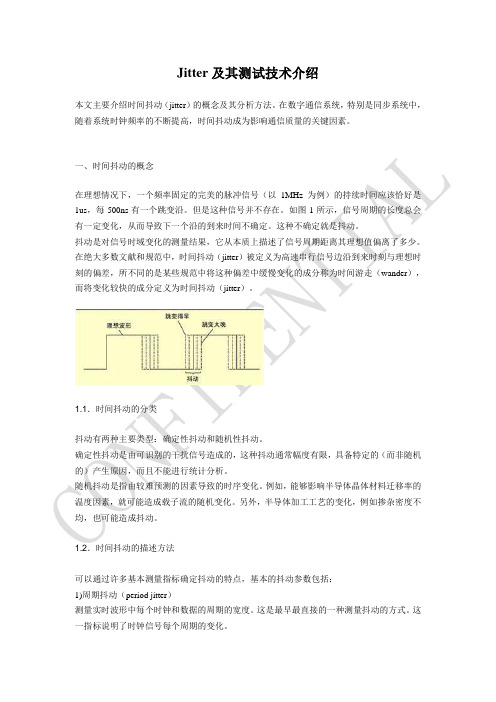

一、时间抖动的概念在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。

但是这种信号并不存在。

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。

在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

1.1.时间抖动的分类抖动有两种主要类型:确定性抖动和随机性抖动。

确定性抖动是由可识别的干扰信号造成的,这种抖动通常幅度有限,具备特定的(而非随机的)产生原因,而且不能进行统计分析。

随机抖动是指由较难预测的因素导致的时序变化。

例如,能够影响半导体晶体材料迁移率的温度因素,就可能造成载子流的随机变化。

另外,半导体加工工艺的变化,例如掺杂密度不均,也可能造成抖动。

1.2.时间抖动的描述方法可以通过许多基本测量指标确定抖动的特点,基本的抖动参数包括:1)周期抖动(period jitter)测量实时波形中每个时钟和数据的周期的宽度。

这是最早最直接的一种测量抖动的方式。

这一指标说明了时钟信号每个周期的变化。

2)周期间抖动(cycle-cycle jitter)测量任意两个相邻时钟或数据的周期宽度的变动有多大,通过对周期抖动应用一阶差分运算,可以得到周期间抖动。

这个指标在分析琐相环性质的时候具有明显的意义。

3)时间间隔误差(timer interval error,TIE)测量时钟或数据的每个活动边沿与其理想位置有多大偏差,它使用参考时钟或时钟恢复提供理想的边沿。

Agilent LVDS传输系统测试方案

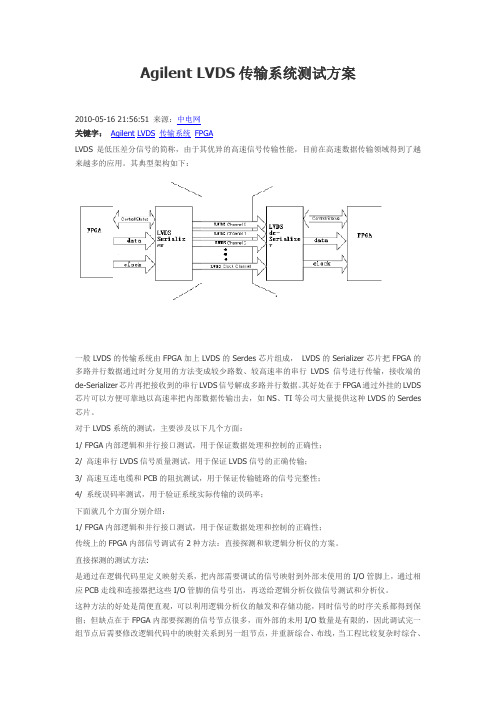

Agilent LVDS传输系统测试方案2010-05-16 21:56:51 来源:中电网关键字:Agilent LVDS传输系统FPGALVDS是低压差分信号的简称,由于其优异的高速信号传输性能,目前在高速数据传输领域得到了越来越多的应用。

其典型架构如下:一般LVDS的传输系统由FPGA加上LVDS的Serdes芯片组成,LVDS的Serializer芯片把FPGA的多路并行数据通过时分复用的方法变成较少路数、较高速率的串行LVDS信号进行传输,接收端的de-Serializer芯片再把接收到的串行LVDS信号解成多路并行数据。

其好处在于FPGA通过外挂的LVDS 芯片可以方便可靠地以高速率把内部数据传输出去,如NS、TI等公司大量提供这种LVDS的Serdes 芯片。

对于LVDS系统的测试,主要涉及以下几个方面:1/ FPGA内部逻辑和并行接口测试,用于保证数据处理和控制的正确性;2/ 高速串行LVDS信号质量测试,用于保证LVDS信号的正确传输;3/ 高速互连电缆和PCB的阻抗测试,用于保证传输链路的信号完整性;4/ 系统误码率测试,用于验证系统实际传输的误码率;下面就几个方面分别介绍:1/ FPGA内部逻辑和并行接口测试,用于保证数据处理和控制的正确性;传统上的FPGA内部信号调试有2种方法:直接探测和软逻辑分析仪的方案。

直接探测的测试方法:是通过在逻辑代码里定义映射关系,把内部需要调试的信号映射到外部未使用的I/O管脚上,通过相应PCB走线和连接器把这些I/O管脚的信号引出,再送给逻辑分析仪做信号测试和分析仪。

这种方法的好处是简便直观,可以利用逻辑分析仪的触发和存储功能,同时信号的时序关系都得到保留;但缺点在于FPGA内部要探测的信号节点很多,而外部的未用I/O数量是有限的,因此调试完一组节点后需要修改逻辑代码中的映射关系到另一组节点,并重新综合、布线,当工程比较复杂时综合、布线等花的时间非常长,所以对于比较复杂的设计测试效率比较低。

ES621系列动态电流电压曲线传输线脉冲测试系统

ES621系列动态电流电压曲线传输线脉冲测试系统(ES621SeriesDynamic

IV-CurveTLPSystem)

先进的动态电流电压曲线传输线脉冲系统

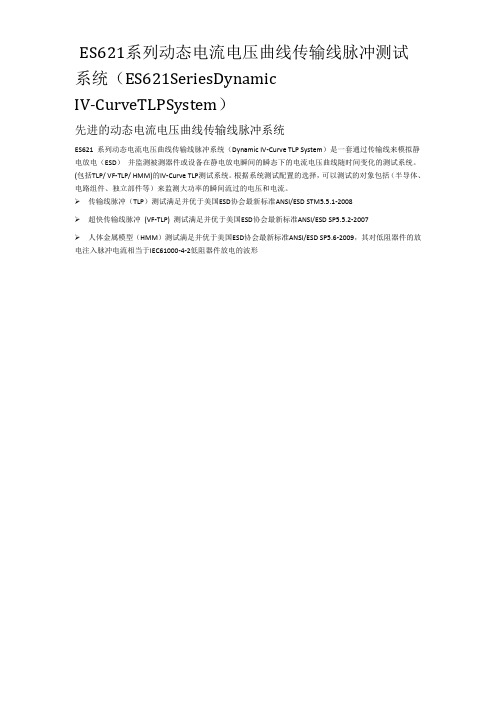

ES621 系列动态电流电压曲线传输线脉冲系统(Dynamic IV-Curve TLP System)是一套通过传输线来模拟静电放电(ESD)并监测被测器件或设备在静电放电瞬间的瞬态下的电流电压曲线随时间变化的测试系统。

(包括TLP/ VF-TLP/ HMM)的IV-Curve TLP测试系统。

根据系统测试配置的选择,可以测试的对象包括(半导体、电路组件、独立部件等)来监测大功率的瞬间流过的电压和电流。

传输线脉冲(TLP)测试满足并优于美国ESD协会最新标准ANSI/ESD STM5.5.1-2008

超快传输线脉冲(VF-TLP) 测试满足并优于美国ESD协会最新标准ANSI/ESD SP5.5.2-2007

人体金属模型(HMM)测试满足并优于美国ESD协会最新标准ANSI/ESD SP5.6-2009,其对低阻器件的放电注入脉冲电流相当于IEC61000-4-2低阻器件放电的波形。

脉冲耐压测试的基本原理和实验方法-概述说明以及解释

脉冲耐压测试的基本原理和实验方法-概述说明以及解释1.引言1.1 概述脉冲耐压测试是一种广泛应用于电力行业、电子器件制造等领域的测试方法。

其基本原理是通过施加高电压脉冲信号,检测被测对象在高电压下的耐压性能。

这种测试方法可以有效检测电子器件、绝缘材料等在电气环境下的安全可靠性。

在脉冲耐压测试中,被测对象置于一个受控的电场环境中,施加高压脉冲信号。

这些脉冲信号通常具有极短的上升时间和下降时间,而且在高电压状态下的持续时间非常短暂,以确保在测试过程中不会对被测对象造成永久性的损坏。

通过测量被测对象在该高压脉冲信号下的响应,可以评估其耐压性能。

脉冲耐压测试的实验方法包括准备被测样品、选择适当的测试仪器和设备、确定测试参数、执行测试过程、记录和分析测试结果等步骤。

在样品准备阶段,我们需要确保被测对象符合测试要求,并进行必要的清洁和保护。

选择适当的测试仪器和设备包括高压发生器、波形发生器、电容器、绝缘电阻器等,以确保能够生成高质量的脉冲信号并提供稳定的工作环境。

测试参数的确定包括脉冲电压的大小、脉冲信号的频率、测试时长等,这些参数应根据被测样品的特性和测试要求进行选择。

执行测试过程时,需要保证实验操作规范、稳定可靠,并对测试结果进行准确记录。

最后,通过对测试结果的分析和评估,可以得出被测样品的耐压性能评价,并提供相关的改进和优化建议。

总之,脉冲耐压测试是一种重要的测试手段,可以有效评估电子器件和绝缘材料在高压环境下的安全性和可靠性。

通过了解脉冲耐压测试的基本原理和实验方法,我们可以更好地理解、应用和改进这种测试技术,推动电力行业和电子器件制造的发展。

1.2文章结构文章结构部分的内容:本文主要由引言、正文和结论三部分组成。

引言部分主要对脉冲耐压测试进行概述,介绍其基本原理和实验方法,并指出本文的目的。

正文部分包括脉冲耐压测试的基本原理和实验方法。

其中,基本原理部分将详细解释脉冲耐压测试的概念、原理和工作过程,并介绍其在实际应用中的重要性。

用于ESD分析的传输线脉冲(TLP)测试--元件级

2015.01.23版

Wei Huang, Jerry Tichenor

Web: Email: info@ Tel: (+1) 573-202-6411 Fax: (+1) 877-641-9358 Address: 4000 Enterprise Drive, Suite 103, Rolla, MO, 65401

我们为何关注ESD?

有物理损伤, 但功能正常- ESD造成的IC损伤

Picture 6

ESD浪涌造成的过电压。IC仍然能工作,但已经接近 彻底损坏。

6

我们为何关注ESD?

硬件故障 - ESD造成的IC损伤

Picture 7

电气过应力(Electrostatic Over Stress - EOS)损坏

Semtech uClamp0541Z 数据表

ESDEMC TLP 测试结果

19

什么是TLP测试?

什么是TLP测试?

• 超快TLP测试: TVS二极管的开启特性 (脉冲开始的几个纳秒)

DUT电阻-时间-脉冲电压瀑布图

6V TLP脉冲

DUT电阻值上限取决于绘图 目的

20

什么是TLP测试?

标准TLP的典型应用

• 带电人体接触受试设备(DUT) • ANSI/ANSI/ESDA/JEDEC JS-001-2010 • 对地测试电压4000V, 电流< 3A (也可用8000V ) • 皮肤放电(IEC 61000-4-2标准是手持金属放电)

Picture 9

对地放电,上升时间(tr) – 2 to 10ns

ESD(静电放电)原理、模型及防护

料、防静电涂料等,以降低设备表面静电电荷的积累。

设备接地

Байду номын сангаас

02

将设备与大地连接,使设备上积累的静电电荷能够迅速泄放到

大地,避免静电放电对设备造成损害。

静电消除器

03

在关键部位安装静电消除器,通过产生相反电荷来中和设备表

面的静电电荷,达到消除静电的目的。

系统级防护策略

系统接地

将整个系统与大地连接,确保系统内各部分电位一致,减少静电放 电的可能性。

ESD(静电放电)原理、模型及防护

目录

• 静电放电(ESD)基本概念与原理 • ESD模型与特性分析 • ESD防护措施与方法 • ESD测试与评估方法 • ESD在工业生产中应用案例分享 • 总结与展望

01

静电放电(ESD)基本概念与原 理

静电产生及危害

静电产生原因

物质接触、摩擦、分离等过程导 致电荷不平衡,形成静电。

规范操作培训

制定详细的设备操作规范,对操作人员进行培训,确保其在操作 过程中能够遵循规范,减少静电放电的风险。

静电防护装备使用

要求操作人员佩戴防静电手环、防静电鞋等静电防护装备,降低 人体静电对设备的影响。

04

ESD测试与评估方法

测试标准介绍

这是国际电工委员会制定的静电放电抗扰度测试标准,它规定了 测试等级、测试方法、测试环境和设备要求等。

特性

HBM放电电流具有较快的上升时间和较短的持 续时间,通常持续几百纳秒。放电能量较低,但 足以对敏感器件造成损坏。

应用场景

HBM模型常用于评估手持设备、可穿戴设备等 便携式电子产品的ESD防护能力。

机器模型(MM)

描述

应用场景

ESD Technology 经典资料(第四部分)

E S D T e c h n o l o g y经典资料(4)第四部分第五章传输线触波产生器系统(TLPG System)前言:从对二次崩溃点的了解可知,二次崩溃电流(It2)代表了组件到达p-n接面所能承受的最大电流值,在过了此点后,组件就会出现永久性的破坏而有相当大的漏电电流,无法回复原来特性。

由此可知,当以人体静电放电模型来对元件做防护能力测试时,组件所能承受的最大静电放电电流应大约相当于该组件的It2,由于在MIL-STD 883 Method 3015.7 [1]中定义了人体放电电阻的大小为1500奥姆,因此可知组件的最大ESD承受电压V ESD为(1)其中R device为组件电流在达It2时的组件内阻值。

若在实际静电放电模型的测试方式下,由于量到的V ESD已在二次崩溃点后,此时之组件接面已呈现导体性质,因此R device几乎可以省略[2]。

而从人体静电放电模型(HBM)来看,若把充电电压源的部份当作是提供定额能量的能源供应处,由能源供应处提供的能量送入待测组件,在不断提供更高的定额能量下,量测组件的电压/电流值,将可得到待测元件的完整电压/电流特性曲线,如图5.0-1所示。

在这特性曲线中,可以得到所谓的二次崩溃点。

图5.0-1在静电放电防护电路中,会设计一组用来做静电放电排放的防护组件,以有效地排放由静电放电所产生的电流。

一些常见的静电放电防护电路已显示在图4.3-1中[3],在这些防护电路中的防护组件,其运作原理大致可分为以下几种组件:逆偏二极管、双载子晶体管(Bipolar)、金氧半(MOS)组件以及硅控制整流器(Silicon-Controlled Rectifier, SCR)等。

在这些静电放电保护电路中,大多是利用该组件工作在其一次崩溃(First Breakdown)区来排放ESD电流,元件在其一次崩溃区内仍不会被损伤,然而此崩溃区域是有其极限存在,这极限就是所谓的二次崩溃(Secondary Breakdown)的特性,当组件因为外加过压的(Overstress)电压或电流而进入二次崩溃区后,组件会造成永久性的损坏。

一种高速时钟分配电路单粒子效应测试系统设计

现代电子技术Modern Electronics TechniqueMay 2024Vol. 47 No. 102024年5月15日第47卷第10期0 引 言空间带电粒子中有许多成分[1⁃2],主要包含来自外空间射向地球的银河宇宙射线、太阳高能粒子和地球磁场捕获的高能粒子。

其中银河宇宙射线来自于太阳系以外的宇宙射线,是被星际磁场加速到达地球空间的高能带电粒子,包含质子、α粒子、重离子等[3];太阳上发生耀斑时会发射出高能带电粒子,主要成分是质子、少量的重离子[4];地球磁场俘获大量的高能粒子,在地球周围形成6~7个地球半径的粒子辐射区,称为Van Allen 带,包含质子、电子、重离子等[5⁃7]。

在这些带电粒子中,单粒子效应首要关注的是重离子引起的电离[8⁃9],本文所开展的试验就是模拟宇航空间环境。

单粒子效应是指单个高能粒子穿过集成电路灵敏区时,造成电路状态非正常改变的一种辐射效应,常见的单粒子效应包括单粒子锁定(Single⁃Event Latch up, SEL )、单粒子翻转(Single⁃Event Upset, SEU )、单粒子功能中断(Single⁃Event Functional Interrupt, SEFI )等。

其中单粒子锁定是高能粒子入射到电路,导致电路产生异常突变电流,主要发生于CMOS 电路中[10];单粒子翻转是高能粒子作用于集成电路,使得电路逻辑状态发生异常变化,一般发生在数据存储或指令相关电路中;单粒DOI :10.16652/j.issn.1004⁃373x.2024.10.011引用格式:魏亚峰,蒋伟,陈启明,等.一种高速时钟分配电路单粒子效应测试系统设计[J].现代电子技术,2024,47(10):57⁃63.一种高速时钟分配电路单粒子效应测试系统设计魏亚峰1, 蒋 伟1, 陈启明2, 孙 毅3, 刘 杰4, 李 曦1, 张 磊1(1.重庆吉芯科技有限公司, 重庆 400060; 2.中国原子能科学研究院, 北京 102400;3.北京卫星环境工程研究所, 北京 102400;4.中国科学院兰州近代物理研究所, 甘肃 兰州 730000)摘 要: 时钟分配电路是电子系统中信号处理单元参考时钟及多路时钟分配的关键元器件,其跟随系统在宇宙空间中容易受宇宙射线辐照发生单粒子效应,进而影响系统性能指标甚至基本功能。

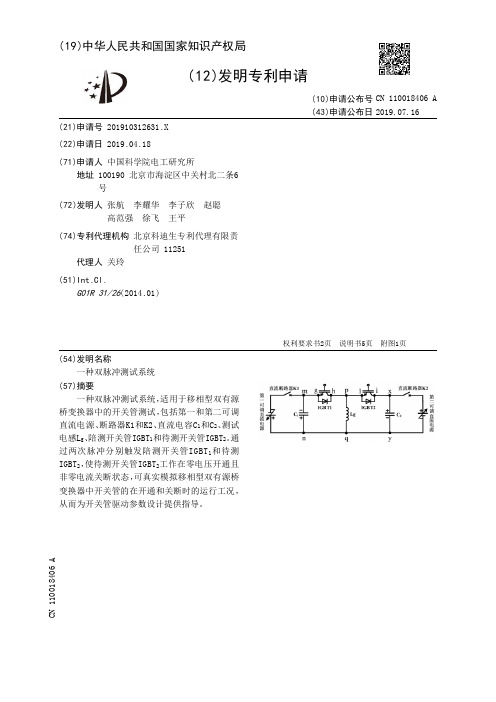

【CN110018406A】一种双脉冲测试系统【专利】

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 201910312631.X(22)申请日 2019.04.18(71)申请人 中国科学院电工研究所地址 100190 北京市海淀区中关村北二条6号(72)发明人 张航 李耀华 李子欣 赵聪 高范强 徐飞 王平 (74)专利代理机构 北京科迪生专利代理有限责任公司 11251代理人 关玲(51)Int.Cl.G01R 31/26(2014.01)(54)发明名称一种双脉冲测试系统(57)摘要一种双脉冲测试系统,适用于移相型双有源桥变换器中的开关管测试,包括第一和第二可调直流电源、断路器K1和K2、直流电容C 1和C 2、测试电感L g 、陪测开关管IGBT 1和待测开关管IGBT 2。

通过两次脉冲分别触发陪测开关管IGBT 1和待测IGBT 2,使待测开关管IGBT 2工作在零电压开通且非零电流关断状态,可真实模拟移相型双有源桥变换器中开关管的在开通和关断时的运行工况,从而为开关管驱动参数设计提供指导。

权利要求书2页 说明书5页 附图1页CN 110018406 A 2019.07.16C N 110018406A权 利 要 求 书1/2页CN 110018406 A1.一种双脉冲测试系统,其特征在于,所述的测试系统包含测试电感L g、第一可调直流电源、第二可调直流电源、直流断路器K1和K2、直流电容C1和C2、陪测开关管IGBT1和待测开关管IGBT2;第一可调直流电源和第二可调直流电源的结构相同、参数相同;直流断路器K1和K2结构相同、参数相同;直流电容C1和C2结构相同、参数相同;陪测开关管IGBT1和待测开关管IGBT2结构相同、参数相同;第一可调直流电源通过直流断路器K1后与直流电容C1并联,第二可调直流电源通过直流断路器K2后与直流电容C2并联;第一可调直流电源的正极端子连接直流电容C1的正极端子n,负极端子通过直流断路器K1后连接至直流电容C1的负极端子m;第二可调直流电源的正极端子通过直流断路器K2后连接至直流电容C2的正极端子x,负极端子连接至直流电容C2的负极端子y;陪测开关管IGBT1的集电极端子h连接至测试电感L g的端子p,陪测开关管IGBT1的发射极端子g连接至直流电容C1的负极端子m;待测开关管IGBT2的集电极端子i连接至直流电容C2的正极端子x,待测开关管IGBT2的发射极端子l连接至测试电感L g的端子p;测试电感的端子q分别与直流电容C1的正极端子n和直流电容C2的负极端子y相连。

Agilent LVDS传输系统测试方案

Agilent LVDS传输系统测试方案安捷伦应用工程师李凯LVDS是低压差分信号的简称,由于其优异的高速信号传输性能,目前在高速数据传输领域得到了越来越多的应用。

其典型架构如下:一般LVDS的传输系统由FPGA加上LVDS的Serdes芯片组成, LVDS的Serializer芯片把FPGA的多路并行数据通过时分复用的方法变成较少路数、较高速率的串行LVDS信号进行传输,接收端的de-Serializer芯片再把接收到的串行LVDS信号解成多路并行数据。

其好处在于FPGA通过外挂的LVDS芯片可以方便可靠地以高速率把内部数据传输出去,如NS、TI等公司大量提供这种LVDS的Serdes芯片。

对于LVDS系统的测试,主要涉及以下几个方面:1/ FPGA内部逻辑和并行接口测试,用于保证数据处理和控制的正确性;2/ 高速串行LVDS信号质量测试,用于保证LVDS信号的正确传输;3/ 高速互连电缆和PCB的阻抗测试,用于保证传输链路的信号完整性;4/ 系统误码率测试,用于验证系统实际传输的误码率;下面就几个方面分别介绍:1/ FPGA内部逻辑和并行接口测试,用于保证数据处理和控制的正确性;传统上的FPGA内部信号调试有2种方法:直接探测和软逻辑分析仪的方案。

直接探测的测试方法:是通过在逻辑代码里定义映射关系,把内部需要调试的信号映射到外部未使用的I/O管脚上,通过相应PCB走线和连接器把这些I/O管脚的信号引出,再送给逻辑分析仪做信号测试和分析仪。

这种方法的好处是简便直观,可以利用逻辑分析仪的触发和存储功能,同时信号的时序关系都得到保留;但缺点在于FPGA内部要探测的信号节点很多,而外部的未用I/O数量是有限的,因此调试完一组节点后需要修改逻辑代码中的映射关系到另一组节点,并重新综合、布线,当工程比较复杂时综合、布线等花的时间非常长,所以对于比较复杂的设计测试效率比较低。

软逻辑分析仪的方案:是FPGA厂家提供的一种测试方案,其原理是在FPGA逻辑代码设计阶段或综合完成后在工程中插入一个软逻辑分析仪的核,软逻辑分析仪的核需要占用一定的块RAM资源,可以用工作时钟把内部信号信号采集到块RAM里,采完以后再通过FPGA的JTAG接口把块RAM里的数据读到外部PC上显示波形。

基于双向可控硅的强鲁棒性静电防护器件

基于双向可控硅的强鲁棒性静电防护器件张峰;刘畅;黄鲁;吴宗国【摘要】针对双向可控硅(DDSCR)器件的静电放电(ESD)鲁棒性,提出在N阱中加入N+注入区(DDSCR_ N+)和在N阱中加入P+注入区(DDSCR_P+)2种改进型DDSCR结构,采用华润上华0.5μm Bipolar-CMOS-DMOS(BCD)工艺,分别制备传统DDSCR结构以及2种改进型DDSCR结构,通过半导体工艺及器件模拟工具(TCAD)进行仿真,分析不同结构的电流密度和ESD鲁棒性差异;流片后通过传输线脉冲测试(TLP)方法测试不同结构ESD防护器件特性.仿真和测试结果表明,改进型DDSCR_N+结构在具有和传统DDSCR器件的相同的触发和维持电压前提下,二次击穿电流比传统的DDSCR结构提高了160%,ESD鲁棒性更强,适用范围更广.%A typical dual-direction silicon controlled rectifier (DDSCR) and two new DDSCR were designed and fabricated based on CSMC 0.5 μm Bipolar-CMOS-DMOS (BCD) process in order to study the ESD robustness of DDSCR.The new structures include DDSCR with additional N+-implant in NWELL and additional P+ implant in NWELL.The total current density and ESD robustness of those three structures were analyzed with the simulation of TCAD software.Key features of those ESD protection devices were compared by TLP testing after tape-out.Both simulation and test results show that,DDSCR_N+ almost has the same triggering voltage and holding voltage of the proposed devices as the conventional DDSCR.DDSCR_N+ provides 160% improvement of secondary breakdown current and exhibits the stronger ESD robustness.【期刊名称】《浙江大学学报(工学版)》【年(卷),期】2017(051)008【总页数】5页(P1676-1680)【关键词】静电放电(ESD);双向可控硅(DDSCR);TCAD仿真;传输线脉冲测试;二次击穿电流【作者】张峰;刘畅;黄鲁;吴宗国【作者单位】中国科学技术大学信息科学技术学院,安徽合肥230026;中国科学院自动化研究所国家专用集成电路设计工程技术研究中心,北京100190;中国科学技术大学信息科学技术学院,安徽合肥230026;中国科学技术大学信息科学技术学院,安徽合肥230026;中国科学院自动化研究所国家专用集成电路设计工程技术研究中心,北京100190【正文语种】中文【中图分类】TN335集成电路制造技术已经进入纳米时代,随着器件特征尺寸的降低和集成电路复杂化的提升,静电放电(electrostatic discharge, ESD)问题越来越成为集成电路中最主要的可靠性问题之一[1].常见的ESD器件有BJT,MOS管,可控硅(silicon controlled rectifier, SCR)等.其中SCR类器件具有单位面积泄放电流大、寄生电容小的优点,成为新型ESD防护器件的研究热门[2].对于一些存在共模电压的总线接口,比如RS232/RS485/RS422/CAN等接口芯片,需要双向的ESD防护结构进行I/O口的正负ESD防护[3],如采用2个ESD防护器件堆叠来进行双向防护,不仅会占用过大的版图面积,而且会引入额外的寄生效应.因此,需要设计一个能够同时进行双向防护的双向可控硅(dual-direction silicon controlled rectifier, DDSCR)器件来解决上述问题.DDSCR防护器件设计窗主要包含3个关键的指标,分别是触发电压,维持电压和二次击穿电流.其中触发电压要小于内部电路的栅氧击穿电压;维持电压要大于内部电路的工作电压[4];二次击穿电流越大,ESD防护器件鲁棒性越高.在对于触发电压和维持电压的改进方面:Liu等[5]提出一种低触发电压的双向SCR结构[5];Wang等[6]研究了低触发电压,维持电压可调的双向SCR结构[6];Vashchenko对触发电压和维持电压都进行了研究调整[7],梁海莲等[8]提出了改进型的双向SCR结构并优化关键尺寸以满足窄小的ESD设计窗口.针对二次击穿电流值的提高,Guo等[9-10]提出通过改变金属走线提高双向SCR的鲁棒性.但上述研究中均未对双向SCR结构与二次击穿电流之间的关系开展研究.本文在传统DDSCR结构基础上,提出了改进型DDSCR器件结构,通过在N阱中加入N+注入区(DDSCR_N+)和在N阱中加入P+注入区(DDSCR_P+),可以在保持触发电压和维持电压前提下,提升二次击穿电流,从而达到了更强的ESD鲁棒性.1.1 DDSCR的防护机理对于DDSCR器件,在正向或反向ESD脉冲作用下,利用其内部反偏的PN结形成具有相同PNPN特性的ESD电流泄放路径,来实现对称性的双向ESD防护.同时,DDSCR类器件又可减小芯片面积,提高单位面积ESD防护效率.如图1(a)所示为传统的DDSCR剖面图及其对应的(b)单向SCR等效电路图.在传统的DDSCR中,2个P阱各包含一个高掺杂的N+注入区和P+注入区.该结构同时存在3个寄生的三极管,分别是器件两边的寄生NPN三极管和器件中间的寄生PNP三极管,从而形成两路PNPN电流泄放路径,即双向的SCR结构.正向ESD脉冲作用在Anode时,Cathode侧寄生NPN晶体管的PN结(N-WELL/P-WELL)是反偏的,达到雪崩击穿后产生大量的电子空穴对,产生雪崩倍增电流.一旦寄生P阱(Cathode侧)电阻上的电压降达到足够大,寄生NPN晶体管的发射结触发导通,电流上升.随之该电流又在N阱电阻上产生电压降,寄生PNP管触发导通,从而形成了正反馈的闭合回路,2个寄生晶体管进入饱和区,泄放ESD电流.反之,当反向的ESD脉冲作用在Anode时,等效于正向的ESD脉冲作用于cathode.因为该结构是对称的,所以这和在Anode侧加正向ESD脉冲是类似的,但是雪崩击穿的PN结发生在Anode侧的P-WELL/N-WELL.综上所述,该结构可以提供双向的具有回滞特性(S形I-V曲线)的ESD保护.1.2 改进型的DDSCR结构本文在传统的DDSCR结构中间的N阱中对称加入了N+注入区(DDSCR_N+)或P+注入区(DDSCR_P+),具体结构剖面如图2所示.N阱中的N+注入区或P+注入区可以提供大量载流子,增加寄生PNP三极管的基区电子浓度.电子对在基区的复合和电离的浓度加大,从而促进寄生三极管的开启和对电流的泄放,提高了ESD的放电能力.此外,改进型的DDSCR结构和传统结构的器件尺寸和版图设计均相同. 2.1 ESD器件仿真本文选用Silvaco公司的ATLAS仿真软件对DDSCR的物理机制进行仿真分析,分别对传统的DDSCR,DDSCR_N+和DDSCR_P+进行直流仿真.在器件的阳极施加ESD脉冲,模拟器件在ESD应力下的电学特性.3种结构的仿真剖面结构尺寸相同,与实际流片的版图尺寸一致,相关参数参照表1(各参数含义见图2).同时,其他仿真参数设置一致,只观察不同的剖面图结构对器件性能的影响,即N阱中N+或P+注入对器件鲁棒性的影响.如图3(a)所示为传统DDSCR在触发点和维持点的总电流密度J分布图;(b)是DDSCR_N+在触发点和维持点的总电流密度分布图;(c)是DDSCR_P+在触发点和维持点的总电流密度分布图.图3中总电流密度大小由不同颜色区分,具体数值显示在图中左下方区域.从图中可以看出,3个结构在雪崩击穿发生时电流主要集中分布在器件的表面区域,随着器件进入回滞(snapback),SCR结构完全开启泄放ESD电流,电流分布趋于器件体内.由于3个结构的工作机理相同,器件尺寸相同,其电流分布面积在触发点和维持点也大致相同,但是N+或P+注入区的加入改变了电流密度数值,随之影响了DDSCR的鲁棒性能.其中,DDSCR_N+结构在触发点和维持点的总电流密度极值最小,分别为5.07×103和7.19×104 A/cm2;DDSCR_P+结构次之,在触发点和维持点分别为5.26×103和1.12×105 A/cm2;传统DDSCR的总电流密度极值最大,在触发点和维持点分别为3.73×104和1.20×105 A/cm3.在相同的情况下,总电流密度值较小的结构能够承受更高的电压,从而拥有更强的ESD鲁棒性.2.2 TLP测试基于华润上华0.5 μm BCD工艺流片制备了传统的DDSCR及其改进结构,利用TLP 6000 Series测试系统进行传输线脉冲测试来表征DDSCR的ESD防护特性.TLP测试脉冲波形上升时间是5 ns,脉冲宽度100 ns,每施加一次TLP测试脉冲,同时进行器件的漏电流测试.传统的DDSCR,DDSCR_N+及DDSCR_P+结构均为完全对称结构,版图绘制完全对称,正反向TLP测试结果大致相当,给出正向的TLP 测试结果进行比较分析.3个结构的正向TLP测试结果曲线如图4所示,其中V为电压,I为电流,IL为漏电流.相应的TLP测试结果数据如表2所示.表中,Vt1为触发电压,Vh为维持电压,It2为二次击穿电流.图4中3个器件的漏电流在二次击穿前都在纳安级别的范围,因此可以有效地应用到I/O接口,并且减少漏电损失对内部电路正常工作所带来的影响.传统的DDSCR 及N阱中加入N+注入(DDSCR_N+)和P+注入(DDSCR_P+)的改进型DDSCR结构的触发电压Vt1分别为48.394、48.309、46.786 V;维持电压Vh分别为20.669、19.948、21.259 V.由于3个器件的触发的PN结相同,即N阱和P阱所形成的PN结,且剖面图横向尺寸相同,所以触发电压和维持电压大致相当[12].二次击穿电流是ESD防护器件能够承受的最大电流,是衡量ESD鲁棒性的重要指标.3个器件的ESD二次击穿电流It2分别是2.962,7.719和5.328 A,DDSCR_N+结构的It2相比传统的DDSCR提升了160%,DDSCR_P+结构的It2提升了79.8%.该测试结果与仿真结果相符,证明了N+注入区和P+注入区对于ESD防护器件性能的影响,即DDSCR_N+和DDSCR_P+结构的耐压能力更强,ESD鲁棒性更好.同时,DDSCR_N+结构比DDSCR_P+结构的二次击穿电流更大,拥有更强的ESD鲁棒性.本文基于华润上华0.5 μm BCD工艺,制备了传统DDSCR结构以及2种改进型DDSCR结构:DDSCR_N+,DDSCR_P+.并且进行了TCAD软件的仿真和TLP测试.仿真和测试结果表明,改进型的DDSCR器件和传统的DDSCR器件的触发电压和维持电压大致相同.其中,DDSCR_N+结构具有最高的二次击穿电流,因此该结构ESD耐压能力强,鲁棒性好,能够更好的应用在要求较高的I/O端口上.在后续的工作中,将会进一步考察器件的关键尺寸对触发电压和维持电压的调整以满足对双向ESD防护结构设计窗口的特殊要求.【相关文献】[1] DUVVURY C. ESD protection device issues for IC designs[C]∥ 2001 IEEE Custom Integrated Circuits. San Diego,USA: IEEE, 2001: 41-48.[2] KER M D, HSU K C. Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS integrated circuits [J]. IEEE Transactions on Device and Materials Reliability, 2005, 5(2): 235-249.[3] SALCEDO J A, LIOU J J, BERBIER J C. Design and integration of novel SCR-based devices for ESD protection in CMOS/BiCMOS technologies [J]. IEEE Transactions on Electron Devices, 2005, 52(12): 2682-2689.[4] 李冰,王刚,杨袁渊.基于SCR的ESD保护电路防闩锁设计[J].微电子学,2009,39(6): 786-789. LI Bing, WANG Gang, YANG Yuan-yuan. Latch-up free design of SCR-based ESD protection circuits [J]. Microelectronics, 2009, 39(6):786-789.[5] LIU Z W, VINSON J, LOU L F, et al. An improved bidirectional SCR structure for low-triggering ESD protection applications [J]. IEEE Electron Device Letters, 2008, 29(4): 360-362.[6] WANG Y, JIN X L, YANG L, et al. Robust dual-direction SCR with low trigger voltage, tunable holding voltage for high-voltage ESD protection [J]. Microelectronics Reliability, 2015, 55(3): 520-526.[7] VASHCHENKO V A, HOPPER P J. New dual-direction ESD device in Si-Ge BiCMOS process [C]∥2010 IEEE 10th International Conference on Solid-State and Integrated Circuit Technology. Shanghai: IEEE, 2010:935-937.[8] 梁海莲,董树荣,顾晓峰,等.基于0.5μm BCD工艺的双向SCR结构的ESD保护设计[J].浙江大学学报:工学版,2013, 47(11):2046-2050. LIANG Hai-lian, DONG Shu-rong, GU Xiao-feng, et al. ESD protection design of DDSCR structure based on the 0.5 μm BCD process [J]. Journal of Zhejiang University: Engineering Science, 2013, 47(11):2046-2050.[9] GUO W, LI M L, DONG S R. Effect of metal routing on the ESD robustness of dual-direction silicon controlled rectifier[C]∥2009 IEEE 16th I nternational Symposium on the Physical and Failure Analysis of Integrated Circuits. Suzhou: IEEE, 2009: 336-338.[10] DU X Y, DONG S R, HAN Y, et al. Analysis of metal routing technique in a novel dual direction multi-finger SCR ESD protection device [C]∥ 2008 IEEE 9th International Conference on Solid-State and Integrated Circuit Technology. Beijing: IEEE, 2008:337-340.[11] LEE J C, YOUNG R, LIOU J J, et al. An improved transmission line pulsing (TLP) setupfor electrostatic discharge (ESD) testing in sem iconductor devices and ICs[C]∥ 2001 IEEE International Conference on Microelectronic Test Structures. Kobe: IEEE, 2001:233-238.[12] WANG Y, LU G Y, ZHANG L Z, et al. Comprehensive study and corresponding improvements on the ESD robustness of different nLD MOS devices[C]∥ 2014 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits. Marina Bay Sands, Singapore: IEEE, 2014: 304-307.。

比价标书(模拟测试系统)

邀请招标文件标书编号:SJ-JYS2012-05 招标项目名称:模拟器件测试系统编制:湖北航天技术研究院计量测试技术研究所日期:二○一二年三月总目录第一章招标邀请 (3)第二章投标人须知 (4)第三章货物需求一览表及技术要求 (7)第四章合同条款及合同格式 (8)第五章附件 (12)湖北航天技术研究院计量测试技术研究所第3页共36 页第一章招标邀请:湖北航天技术研究院计量测试技术研究所(以下简称计研所)就模拟器件测试系统组织国内邀请招标,特邀请合格投标人投标。

1、招标设备名称、数量及要求:详见邀请招标文件第三章2、供货期:详见货物需求一览表3、付款方式:详见邀请招标文件第四章第九条,此条款不允许偏离。

4、投标地点:湖北航天计量测试技术研究所生产计划处5、投标截止时间:2012年3月23日上午10:00 前6、联系方式及联系人联系单位:湖北航天计量测试技术研究所通讯地址:湖北孝感长征路95号邮政编码:传真:0712-商务联系人:杨皖宁联系电话:0712- 传真:技术联系人:孟秀丽联系电话:0712-第二章投标人须知一、说明1 合格的投标人凡被邀请的、具有法人资格、有生产或供应能力的企业、科研机构均可参加投标(如果投标设备实行生产许可证制度,应有生产许可证)。

2 投标委托如投标者不是法定代表人,需持有《法定代表人授权书》。

3 招标机构计研所。

二、邀请招标文件5 邀请招标文件构成5.1 邀请招标文件由通用、技术两部分组成,主要有以下方面内容:a 投标人须知b货物需求一览表及技术规格c 合同条款及合同格式d 附件5.2 邀请招标文件由计研所编制。

三、投标文件的编制6投标文件计量单位投标文件中所使用的计量单位,除邀请招标文件中的特殊要求外,应采用国家法定的计量单位。

7 投标文件的组成7.1投标人编写投标书应包括下列部分:a.按照投标人须知要求填写的投标书、投标报价表;b.按照投标人须知要求出具的证明文件,证明投标人是合格的,而且中标后有能力履行合同;c.按照投标人须知第13条要求出具的证明文件,证明投标人提供的货物及服务是合格的货物和服务,且符合邀请招标文件规定。

集成电路中esd失效机理分析

1.2静电放电危害

由于物体间的接触分离(如摩擦、剥离、撕裂和搬运中的碰撞等)或电场感应,都会因物体之间或物体内部带电粒子的扩散、转移或迁移而形成物体表面电荷的积聚,即呈现带电现象。这种现象的存在,有可能导致物体表面电荷对空气中带异性电荷的微粒子尘埃的吸引造成电子敏感元器件绝缘性能的降低、结构腐蚀或破坏。当外界条件适宜时,这种积聚电荷还会产生静电放电,使元器件局部破损或击穿,严重时,还会引起火灾、爆炸等。曾报道某厂在修理程控交换机上的半导体集成电路时因静电引起爆炸事故的文章[1]。应当指出,静电引起电子元器件局部结构破损和性能降低,是对元器件使用寿命的一种潜在威胁,因为它难于检验,故造成事故的随机性更大,并且易于与其他失效原因混淆而被掩盖。

ESD保护电路的作用在于将出现在芯片管脚上的高电荷按照预先设计好的路径泄放掉,进而防止静电对内部电路的损坏。所以通过对ESD引起失效的器件进行物理失效分析,将有利于改善ESD电路性能和提高ESD防护等级。本文将对静电产生的危害及相关静电模型和ESD失效机理以及失效特征和如何进行预防进行阐述。

1

1.1静电产生的物理原理

(a)典型I/O接口

(b)I-V曲线

图1典型I/O电路及其I-V曲线

2.1.2突发性完全失效和潜在性失效

1.突发性完全失效

突发性完全失效是器件的一个或多个电参数突然劣化,完全失去规定功能的一种失效。通常表现为开路、短路以及电参数严重漂移。

半导体器件ESD损伤失效现象主要表现为:

• 介质击穿

ESD保护策略解析

芯片内置ESD保护设计

总结词

芯片内置ESD保护设计可以降低成本和电 路复杂度,但受限于芯片制造工艺和设计 规则。

VS

详细描述

现代集成电路设计中,芯片制造商会考虑 将ESD保护电路内置在芯片内部。这种设 计方法可以减少外部器件的数量,降低成 本,并提高系统的可靠性。然而,由于芯 片制造工艺和设计规则的限制,内置ESD 保护电路的设计和实现可能会面临一些挑 战。

等。

根据不同的应用场景和设备需求,可 以选择适当的ESD保护元件和电路,

以实现最优的ESD保护效果。

02

ESD保护策略

人体放电模型(HBM)

01

人体放电模型是最常用的ESD 模型之一,它模拟人体对ESD 的响应和行为。

02

HBM模型通过模拟人体接触带 电物体时,电流在人体内的流 动情况,评估ESD对人体的危 害。

04

ESD保护电路设计

独立器件设计

总结词

使用独立的ESD保护器件可以有效地提高系统的ESD保护能力,但会增加成本和电路复杂度。

详细描述

独立器件设计通常采用气体放电管、半导体二极管、瞬态二极管等元件,为电路提供额外的保护路径 ,降低系统损坏的风险。这些器件需要与被保护的电路元件进行良好的匹配和布局,以实现最佳的保 护效果。

ESD保护与系统可靠性关系研究

总结词

ESD保护与系统可靠性的关系是一个重要的研究领域。 ESD保护失效可能导致系统可靠性下降,甚至引发灾难 性事故。

详细描述

ESD保护失效会导致系统可靠性下降,因为ESD事件可 能损坏系统中的关键元件或电路,从而影响系统的正常 运行。此外,如果ESD保护失效,可能会引发更严重的 灾难性事故,如电击、火灾等。因此,对ESD保护与系 统可靠性的关系进行深入研究,对于提高系统可靠性具 有重要意义。

应用一种新的TLP测试方法解决ESD所引起的系统软失效问题

应用一种新的TLP测试方法解决ESD所引起的系统软失效问题作者:刘蕊来源:《科技视界》2017年第08期【摘要】随着电子产品的发展,ESD引发的问题越来越引起重视。

TLP作为一种研究时域ESD事件下的集成电路技术和电路行为的方法,被广泛应用到终端产品防护性能设计、模块或集成电路芯片的防护性能研究中。

本文通过介绍TLP的基本原理提出一种新的测试方法解决了如何通过TLP测试方法进行干扰噪声注入来评估系统的ESD软失效问题,该方法在手机类产品测试中非常有效。

【关键词】ESD;TLP;测试方法;系统软失效0 引言随着消费类终端手持式产品日益增多、结构更加复杂,且半导体工艺缩小及更小的SMT 封装、更低的电压等级、更低的电容值及更低的电流等级等,所面临的ESD(Electro-Static Discharge,静电放电)挑战日趋严重。

静电是一种客观存在的自然现象,产生的方式多种,如接触、摩擦、电器间感应等。

静电的特点是长时间积聚、高电压、低电量、小电流和作用时间短的特点。

当两个物体接触时,其中一个趋从于另一个吸引电子,因而二者会形成不同的充电电位。

人体自身的动作或与其他物体的接触,分离,摩擦或感应等因素,可以产生几千伏甚至上万伏的静电。

ESD对于电路引起的干扰、对元器件、CMOS电路及接口电路造成的破坏等问题越来越引起人们的重视。

电子设备的ESD很早就作为电磁兼容性测试的一项重要内容被写入国家标准和国际标准。

传输线脉冲TLP(Transmission Line Pulse)测试是通过将产生的高压脉冲注入到DUT (待测器件),并测量DUT在时域的电流电压波形来研究或评估集成电路ESD防护性能的一种方法。

本文重点介绍TLP的基本原理以及如何通过TLP测试方法进行干扰噪声注入来评估系统的ESD软失效问题。

1 TLP测试技术TLP 测试之前首先对电路中的一段传输线充电,然后将被测器件接入,充电后的传输线通过被测器件放电。

宽带局域网用双绞线特性参数仿真与测试系统设计

not only

test the characteristic parameters conceming with normal working state of the

twisted-pair cable but also pOint

out the

nature and

location of the

供1.04姗z网络用

供5MHz网络用 供16MHz网络用

供20Ⅻz网络用 供100姗z网络用

供200~400MI-Iz网络用 供500~600MHz网络用

双绞线适用于短距离的数据传输,因此特别适用于局域网应用。传输介质 采用双绞线的局域网的带宽取决于所用导线的质量、长度及传输技术。在采用 高速以太网络FastEthernet的计算机网络中,一般采用五类及五类以上的双绞线 电缆【5】。一般来说,超高速以太网络GBEthernet的传输速度,是高速以太网络 FastEthemet的十倍.现在一种称作Cat-5e(Enhanced

The simulation of the transmission line has

interface

and

clear output waves

and is

a

powerful tool to comprehend the issues about the

transmission

line.And

the twisted-pair cable testing system scheme discarded the

applied widely in the last 100 meters of the LAN because voice,data,image,and CATV analogue signal

一种基于双传输线的纳秒脉冲源的研制

一种基于双传输线的纳秒脉冲源的研制陈炜峰;胡绍朋;薛冬【摘要】采用双传输线发生纳秒级方波脉冲,设计了一种用来模拟核电磁脉冲在电路中激励的干扰信号的纳秒脉冲信号源,进行抗EMP试验.脉冲源由直流高压源、触发控制电路和脉冲形成电路三部分组成.试验中脉冲测量系统设计应注意阻抗匹配,电缆影响,抗干扰等问题.在负载不匹配情况下工作时信号具有较大波动且传送效率降低;负载匹配时,优化后的系统所获得的方波信号前沿1.4 ns,脉冲宽度为50.6 ns.【期刊名称】《科学技术与工程》【年(卷),期】2013(013)027【总页数】5页(P7992-7996)【关键词】双传输线;纳秒脉冲源;测量系统【作者】陈炜峰;胡绍朋;薛冬【作者单位】南京信息工程大学信息与控制学院,南京210044;南京信息工程大学信息与控制学院,南京210044;南京信息工程大学信息与控制学院,南京210044【正文语种】中文【中图分类】TN782电磁脉冲(EMP)是一种瞬变电磁现象。

从时域波形看,一般具有陡峭的前沿,宽度较窄;从频域看,则覆盖了较宽的频带。

电磁脉冲[1](EMP)的干扰及其防护问题已引起广泛的重视。

纳秒高压脉冲源是用于电磁兼容性试验研究领域中的一种模拟干扰源。

MIL-STD-461E中“电源传导敏感度试验(CSll5)”规定的标准波形为:上升沿时间小于2 ns,脉宽大于30 ns[1]。

如图1 所示。

纳秒级高电压脉冲是极快速的变化过程,其测量的过程中存在着诸多问题值得研究与重视[2—5]。

首先,发生器产生脉冲幅值较高——达几十千伏甚至到兆伏级;因此被测量电压值在测量系统中衰减倍数不低于为104量级,同时分压器的衰减倍数应达103量级;其次,脉冲具有前沿快的特点,这就要求纳秒级别高电压脉冲测量系统上升时间范围为亚纳秒到十纳秒;再次,电磁干扰在快脉冲情况下产生严重影响,较快的脉冲前沿相应地决定了短波长成分能量很大,同时空间电磁的干扰很强[6—8]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

传输线脉冲测试系统 1套

技术要求

一、设备的组成及配置清单

1.1 传输线脉冲发生器

1.2 示波器

1.3 漏电监测单元

1.4 自动化测试硬件系统(传输线脉冲波形注入的波形控制,被测器件的瞬态电

压和电流波形、IV曲线测试)

1.5 预装了自动化测试、记录软件的电脑台式主机(配置:i7处理器,8G内存,1T

硬盘),国内采购19英寸显示器、鼠标、键盘

1.6 探针台及测试配件(包含:体视显微镜(最高放大倍率90倍,国内采购),微距

探针座,探针臂,探针,测试配套的连接线缆,以及电压和电流探头)

二、系统各部分的技术规范要求

* 2.1 传输线脉冲脉冲发生器:

开路最大输出电压:±1.25 kV

短路最大输出电流:±25 A

系统阻抗:50Ω

上升沿时间: 0.1ns, 0.3ns, 0.6ns, 1ns,内置程控可选

传输线脉冲脉冲宽度:0.5ns, 1ns,5ns,100 ns,内置程控可选

* 2.2 数字源表:

电压量程:±200V 电压精度:≤±100nV

流量程:±1A 电流精度:≤±1pA

* 2.3 示波器:带宽≥13GHz,采样率≥40Gsa/s, 四个模拟通道

2.4 测试电脑和测试软件

能通过USB接口、GPIB接口或者网口控制示波器、SMU 传输线脉冲发生器;

能够设置五段或以上传输线脉冲测试电压序列、能够调整脉冲间隔、测量窗口和电压步长;

能够设置五个或以上DC测试点进行直流漏电测试;

系统校准包括电压、电流瞬态波形的起始时间校准,以及SOZL四步校准,校准完成后在软件中自动计算校正参数;

能够启用或禁用漏电测量;

能够保存测试结果(包括IV曲线图、IV曲线数据表格、每个瞬态电压、电流测试波形数据);

能够支持多种数据结果分析: IV 曲线, IVT 3D 图, 动态电阻, R-t的曲线及DUT 端能量积分功能;

能够调用四个或以上测试结果进行对比分析。

2.5探针测试装置:

可进行两线和四线的传输线脉冲探针测试,装置包括探针台、体视显微镜(最高放大倍率90倍,国内采购),探针座和探针臂,探针,测试配套的连接线缆,以及电压和电流探头。

2.6 双向开关模块: 用于传输线脉冲测试与漏电测试之间的切换

2.7 电流测量配件:

配备传输线脉冲测试电流探头

配备快速传输线脉冲TDR-S方式的电流测量低损传输线

* 2.8支持TDR-O方法的标准传输线脉冲测试和TDR-S方法的超快传输线脉冲测试,TDR-S测试方法需配备电压、电流测试通道的S参数频域补偿算法。

三、质保要求:验收合格后2年

显微高速成像系统1套

1.工作温度-10℃~50℃

2. 满幅分辨率不低于1280×800

3. 满幅拍摄速率不低于5200帧/秒

4. 分辨率为256×256时拍摄速率不低于50000帧/秒

5. 分辨率256×128时拍摄速率不低于100000帧/秒

* 6. 最高拍摄速率不低于55万帧/秒

7. 像元尺寸不小于20um

8. 黑白图像传感器,灵敏度不低于40000 ISO/ASA(12232SAT标准)

* 9. 最小曝光时间不大于1us

10. 内存容量不小于18G

11. 分辨率连续可调(64×8)

* 12. 具备基于图像的自动触发功能

13. 具备1us级二次曝光功能和自动曝光功能

* 14. 内置机械快门

15. 具备千兆以太网控制接口

16. 具备HD-SDI视频输出功能

17. 重量不大于2.5KG

18. 体积不大于12.7 cm×12.7 cm×12.7cm

19. 与现有Nikon设备匹配

20. 图像格式必须具备CINE、MOV、AVI、MP4等视频格式和BMP、TIFF、JPG等图片

格式,支持内存独立分段记录功能,不低于63段

21. 具备可编程输入输出接口

22. 配备分析处理软件,具备摄像机设置、分析回放、运动分析、图像处理、文件

管理及各式转换

23. 配备专用光源、标配电缆

* 24. 需提供生产厂家或总代理授权书、售后服务承诺书及技术证明材料(含彩页)

可调谐激光器1台

1.步进波长调谐,波长设置精度,±200 pm,步长分辨率:±10 pm

2.波长扫描范围覆盖1490-1610 nm

3.输出光功率 >+3 dBm @(全波段),输出功率 > ﹢6dBm @ (1520-1590 nm)

4.线宽 < 150 kHz(相干性控制开启),边模抑制比≥ 45dB

5.扫描速度:可达10 nm/s

6.输出:单模光纤输出,FC/APC接头

配置:可调激光器主机1台,电脑1台。

* 需提供生产厂家或总代理授权书、售后服务承诺书及技术证明材料(含彩页)

数字源表1台

1.用于高速直流参数测度

* 2. 提供宽动态范围10pA-10A,1uV-1100V,20w-1000w 3. 四象限工作

* 4. 0.012%精确度,5½的分辨率

5.可程控电流驱动和电压测量钳位的6位线电阻测量

6.内置快速失败/通过测试比较器

7.可选式接触检查功能

8.数字1/0提供快速分选与机械手连接,

9.达1700读数/秒(4位半分辨率),至GPIB总线

精密恒压泵 1台

技术参数:

双通道,每个通道单独控制不同气压。

一、压力驱动微流体进样仪

* 1. 压力输出波动:<0.005%

2.压力输出响应时间:9ms

* 3. 内置压力传感器误差:≤0.006%

4.压力输出稳定时间:≤40ms

5.压力和真空源:将压力/真空源(空气压缩机、高压气瓶或者真空泵)与OB1连

接

6.监控:使用控制软件对压力输出和流量进行控制,可以通过编程压力和流量输

出程序来实现智能自动控制

7.样品:根据设定,OB1可以将储液瓶中的液体压入微流控芯片的流道中或者将液

体从流道中吸出

8.芯片:通过精确的控制流体在芯片中的流动,OB1给予更加全面的样品控制。

9.产品输出参数:

9.1压力输出范围:-900-1000mbar

9.2 压力输出波动:满量程的0.05%(-1000-500mbar内为500 ubar);

满量程的0.25%(500-1000 mbar内为5 mbar)

9.3 响应时间.9ms

9.4 稳定时间:≤40ms

* 9.5 内置压力传感器分变率:满量程的0.006%(122 ubar)

10.外接压力源压力范围(最小压力-最大压力)真空源-1000mbar到0,

压力源1.5bar-10bar

二、微流体流量传感器

* 1.流量测量范围:0.07μl/min-5000μl/min

2.传感器响应时间:≤40ms

3.流量分辨率:1.5pl/s

4.低死体积: 1μl

5.双向流量测量

6.传感器内腔使用硼硅酸盐玻璃、石英玻璃或惰性PEEK材料,确保良好的化学和

生物相容性

7.微流控流量传感器:MSF 2

7.1流量范围:0到±7μL/min

7.2精度(m.v.=测量值):[-7到0.4]&[0.4到7]μL/min之间5% m.v.;

[-0.4到0.4]μL/min之间20nL/min

7.3传感器内径:150μm

8. 内部传感器毛细管为石英材质;

紧凑型变速蠕动泵1套

一、技术参数:

1. 控制类型:模拟变速

2. 每分钟最小转数(rpm):1.7

3. 每分钟最大转数(rpm):10

4. 速度控制:±5%

5. 通道数:1

6. 最大流速(mL/min):1.65

7. 最小流速(mL/min):0.002

8. 接受的管规格0.19、0.25、0.51、0.89、1.14、1.42、2.06 和2.79 mm 内径微

孔泵管

9. 辊数量:4

10. IP 防护等级:IP 22

11. 功率(Hz):50/60

12. 高度(cm):约9.5

13. 长度(cm):约8.9

14. 宽度(cm):约17.8

二、配置:

1. 双通直升式电磁阀1个

2. 配套泵管2个。