USB接口EMC设计方案

经典中的经典 以太网电接口采用UTP设计的EMC设计指导书

�以太网电接口采用UTP设计的EMC设计指导书一、UTP(非屏蔽网线)的介绍非屏蔽网线由两根具有绝缘保护层的铜导线组成,两根绝缘铜导线按照一定密度绞在一起,每一根导线在传输中辐射的电波会与另外一根的抵消,这样可降低信号的干扰程度。

用来衡量UTP的主要指标有:1、衰减:就是沿链路的信号损失度量。

2、近端串扰:测量一条UTP链路对另一条的影响。

3、直流电阻。

4、衰减串扰比(ACR)。

5、电缆特性。

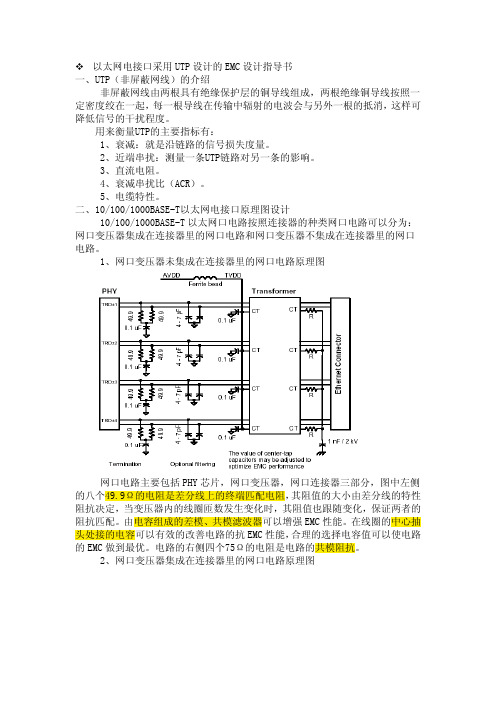

二、10/100/1000BASE-T以太网电接口原理图设计10/100/1000BASE-T以太网口电路按照连接器的种类网口电路可以分为:网口变压器集成在连接器里的网口电路和网口变压器不集成在连接器里的网口电路。

1、网口变压器未集成在连接器里的网口电路原理图网口电路主要包括PHY芯片,网口变压器,网口连接器三部分,图中左侧的八个49.9Ω的电阻是差分线上的终端匹配电阻,其阻值的大小由差分线的特性阻抗决定,当变压器内的线圈匝数发生变化时,其阻值也跟随变化,保证两者的阻抗匹配。

由电容组成的差模、共模滤波器可以增强EMC性能。

在线圈的中心抽头处接的电容可以有效的改善电路的抗EMC性能,合理的选择电容值可以使电路的EMC做到最优。

电路的右侧四个75Ω的电阻是电路的共模阻抗。

2、网口变压器集成在连接器里的网口电路原理图网口电路主要包括PHY芯片,网口连接器两部分,网口变压器部分集成在接口内部,同样左侧的49.9Ω的电阻阻值也是由变压器的匝数及差分线的特性阻抗决定的。

中间的电容组成共模、差模滤波器,滤除共模及差模噪声。

75Ω的共模电阻也集成在网口连接器的内部。

3、网口指示灯电路原理图带指示灯的以太网口电路原理图与不带指示灯灯的大致相同,只是多出指示灯的驱动电路。

注意点:1)、两个匹配电阻是否需要根据PHY层芯片决定,如有的PHY层芯片内部集成匹配电阻就不需要。

匹配电阻是接地还是接电源也是由PHY芯片决定,一般接电源。

TYPE-C接口EMC设计

强大的TYPE-C方案,简洁有效的EMC对策深圳韬略科技一、USB TYPE-C简介随着苹果公司4月份New MacBook的发布,支持正反插的USB TYPE-C瞬间名满全世界;随后联想、小米等知名企业纷纷推出USB TYPE-C方案的新产品,USB TYPE-C方案正式走向了新产品应用的热潮;USB TYPE-C的亮点在于更加纤薄的设计、更快的传输速度(最高10Gbps)以及更强悍的电力传输(最高100W),但是高达10GBPS的传输速度必然导致端口的辐射超标严重;而功率大、速度快特征对端口防护器件有了更高要求;如何有效、简洁的做出性价比高的方案便成了硬件工程师的难题。

本文从辐射发射和抗扰度两个方面为大家提供性价比高的EMC解决方案,希望对大家有所帮助。

二、TYPE-C脚位定义脚位说明:数据传输主要有TX/RX两组差分信号,CC1和CC2是两个关键引脚,作用很多:探测连接,区分正反面,区分DFP和UFP,也就是主从配置Vbus,有USB Type-C和USB Power Delivery两种模式。

配置Vconn,当线缆里有芯片的时候,一个cc传输信号,一个cc 变成供电Vconn。

配置其他模式,如接音频配件时,Dp,Pcie时电源和地都有4个。

三、TYPE-C的EMC问题点1、高达10GBPS的传输速度必然导致端口的辐射超标严重;2、TYPE-C电压范围广、功率大、速度快特征对端口防护器件有了更高要求;四、处理措施(一)、TYPE-C的EMI问题;问题点:高速数据交换时产生的共模辐射,例如240MHZ、480MHZ、720MHZ等;措施:在差分线上增加43R共模滤波器;数据对比:说明:增加共模滤波器后,480MHZ下降明显;(二)、TYPE-C的ESD问题;问题点:对TYPE-C端口进行静电放电时,会导致系统死机或数据交换中断;措施:在差分线上增加0.4PF的TVS排;说明:在信号线上增加TVS,能有效抑制静电对系统的影响。

电磁兼容(EMC)设计参考电路

GDT BF601M

1

1

R2

R3

2

2

14D471K 14D471K

B

D2 GDT BF601M

1000PF

PGND

PGND

PGND

PGND

备注:

A mon choke 的选用要注意产品的工作电流 2.L2\C4\X 根据EFT测试等级选择。 3.GDT2 BM601M for Surge,BM302M for Safty(1000V)。 4.IEC6100-4-5(1.2/50-8/20uS) 差模:6KV(2ohm),共模6kv(12ohm)

4

3

D1

XC664A*H*

C4

GDT BH601

1000PF D4

GDT BC201N

1000PF

2

1

R1

X2

MOV-110V 1UF

后级电路

D2 GDT BF801M

B

B

1.IEC61000-4-5 (1.2/50-820uS)差模6KV(2ohm)共模6KV(12ohm)

A

8/20uS冲击电流差模:20KA ,共模20KA 2.BH601为直流防雷器件的无续流放电管 3.C1,C2 设计预留

1 L2

2

C4

4

3

D3 1000PF

XC

C6

C7

后级电路

C

1UF/X1 10uF C5

1

R2 MOV-200V

R3 MOV-200V

1000PF 3.0SMCJ165CA

2

B

D2 GDT BF102M

PGND

PGND

A

A

备注: 1.L2 Common choke 的选型,注意电流以及DCR的大小

USB保护电路的EMC设计

USB保护电路的EMC设计1.确定电路布局电路布局是EMC设计中的重要一环。

首先,需要将接地电路的尽可能短。

接地电路是消除电磁串扰的关键,良好的接地是保证设备EMC性能的基础。

其次,将高频信号线与低频信号线分离布局,减少彼此之间的相互干扰。

此外,还需要根据系统需求,合理布局各个电路模块,减少信号线的长度和走线面积。

2.适当选择滤波器滤波器的设计对于EMC起着至关重要的作用。

在USB保护电路中,常常需要使用滤波器来抑制高频噪声和滤除电源线上的电磁干扰。

常用的滤波器包括LC滤波器、Ferrite Beads和EMI滤波器等。

在选择滤波器时,需要根据系统的特点和需求,合理选择滤波器的参数和类型。

3.良好的接地设计良好的接地设计是EMC设计中的重要一环。

首先,需要构建星型接地系统,即将所有的接地点连接在一起,并与外部接地点相连接。

其次,需要采用大面积的接地层来减少环路面积,并且减少共模噪声的辐射和接收。

另外,还要注意将模拟和数字地线分离布局,减少相互之间的干扰。

4.抗干扰设计在USB保护电路的EMC设计中,抗干扰设计是重要的一环。

主要包括以下几个方面:首先,需要合理选择电容和电感元件,以增加抑制干扰的能力。

其次,需要适当加入屏蔽罩或屏蔽层,以减少电磁辐射和电磁感受。

另外,要合理设置地孔和电流回路,在设计中避免环路,减少电磁干扰。

5.可靠的布线设计布线设计也是EMC设计中的关键一环。

在USB保护电路中,需要合理规划信号线和电源线的走线路径,尽量减少信号线的长度和延迟。

此外,还要合理设计PCB板的层压结构,减少信号线的串扰和电磁辐射。

6.使用合适的材料和元件选择合适的材料和元件也是EMC设计中的重要一环。

例如,选择具有良好屏蔽性能的材料和元件,如磁性材料、屏蔽罩等,以减少电磁辐射和电磁感受。

另外,选择高频特性好的元件,如高频滤波器等,以提高系统的EMC性能。

总结起来,USB保护电路的EMC设计是确保设备电磁兼容性和可靠性的重要环节。

32种EMC标准电路图纸及介绍

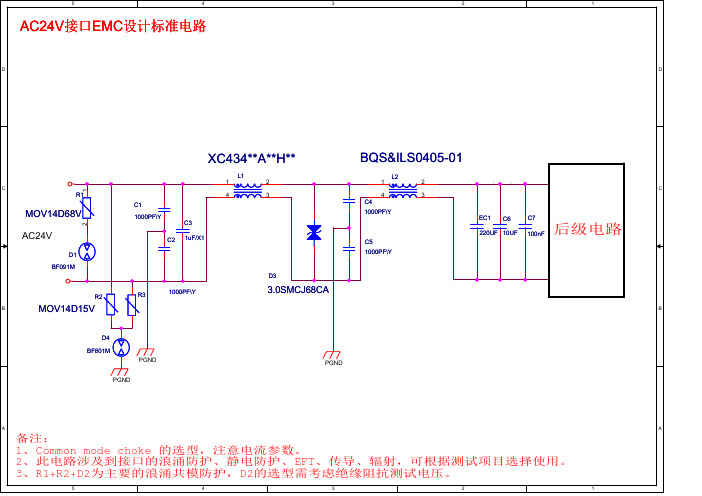

32种EMC标准电路图纸及介绍1、AC24V接口EMC设计标准电路

2、AC110V-220VEMC设计标准电路

3、AC380V接口EMC设计标准电路

4、AV接口EMC设计标准电路

5、CAN接口EMC设计标准电路

6、DC12V接口EMC设计标准电路

8、DC48接口EMC设计标准电路

10、DVIEMC设计标准电路

12、LVDS接口EMC设计标准电路

14、RJ11EMC设计标准电路

15、RS232 EMC设计标准电路

16、RS485EMC设计标准电路

17、SCART接口EMC设计标准电路

18、s-video接口EMC设计标准电路

19、USBDEVICE EMC设计标准电路

20、USB2.0接口EMC设计标准电路

21、USB3.0接口EMC设计标准电路

22、VGA接口EMC设计标准电路

23、差分时钟EMC设计标准电路

24、耳机接口EMC设计标准电路

25、复合视频接口EMC设计标准电路

26、汽车零部件电源口EMC标准设计电路

27、室内外天馈浪涌设计标准电路

28、无源晶振EMC设计标准电路

29、有源晶振EMC设计标准电路

30、以太网EMC(EMI)设计标准电路

31、以太网EMC(浪涌)设计标准电路(差模要求较高方案)

32、以太网EMC(浪涌)中心抽头方案(节约空间)。

欧盟统一后的手机USB接口及其EMC测试要求

欧盟统一后的手机USB接口及其EMC测试要求2011-01-28 18:28:09 来源:摩尔实验室浏览次数:615 文字大小:【大】【中】【小】关键字:USB接口统一EMC 测试从2011年1月1日开始,所有在欧盟销售的带usb接口的手机,其接口统一为micro-B USB,手机及配套充电器的接口如下图所示:手机充电器的接口一直以来都是五花八门,从Micro-B USB到MiniUSB,甚至还有专属充电数据接口存在,这样的设计极大的不方便消费者。

很多时候我们急需充电的时候却发现充电接口不一样。

针对这一现象,欧盟委员会已经批准了14家手机品牌大厂商达成的一项协议,统一了手机usb接口为micro-B USB,并采用micro-B USB手机充电器新标准。

目前支持此项决议的手机厂商包括摩托罗拉、诺基亚、华为、LG、三星、索尼爱立信等。

此项协议实施后,消费者就不用再去为充电而烦躁,让生活更加的轻松,同时能减少充电器的产量,换手机造成的丢弃充电器行为也会大大减少,并且能节约消费者的支出,对减轻环境污染与节能减排也是一大利好。

针对以上协议,欧盟对手机充电器制定了一个新法规其标准号为ETSI EN 301 489-34 V1.1.1 (2 010-10),此标准遵从CE指令。

也就是说,带micro-B USB口的手机充电器做CE认证,另外要符合此标准的要求。

现在我们就来了解一下这个新的法规对于micro-B USB口充电器设备在EMC测试方面都有哪些规定。

以方便大家申请欧盟CE认证。

EN301489-34是指关于无线电设备和服务的相关电磁兼容标准的第34部分,即关于移动电话的外部供电设备的特殊规定。

一.标准中规定了对设备进行供电的EPS(外部供电设备)即充电器必需要符合以下条件:设备通过使用一个micro-B的USB插头电缆的充电器进行电源供电;λ●充电电压为:5V±5 % ;λ●最大输出电流限定在500到1500MA;二. 关于EPS的测试需要注意到几个测试条件:λ●进行EPS的测试时它的直流输出端口必需要接一个能够代表它的连接设备的模拟负载。

USB2.0接口EMC防雷设计方案

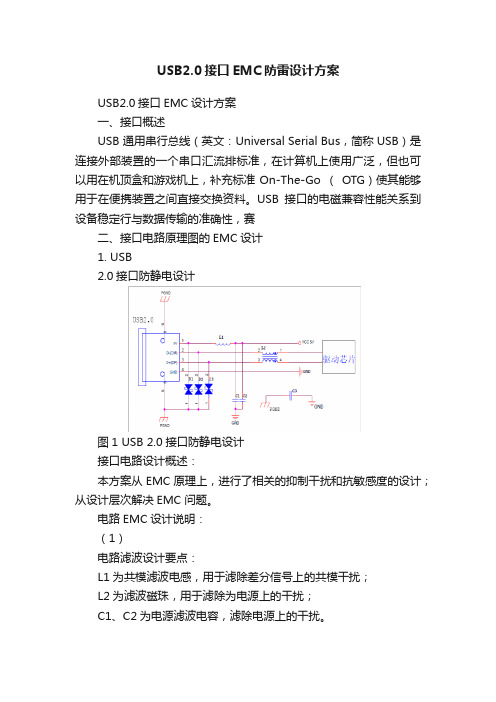

USB2.0接口EMC防雷设计方案USB2.0接口EMC设计方案一、接口概述USB 通用串行总线(英文:Universal Serial Bus,简称USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On-The-Go (OTG)使其能够用于在便携装置之间直接交换资料。

USB接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛二、接口电路原理图的EMC设计1. USB2.0接口防静电设计图1 USB 2.0接口防静电设计接口电路设计概述:本方案从EMC原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决EMC 问题。

电路EMC设计说明:(1)电路滤波设计要点:L1为共模滤波电感,用于滤除差分信号上的共模干扰;L2为滤波磁珠,用于滤除为电源上的干扰;C1、C2为电源滤波电容,滤除电源上的干扰。

L1共模电感阻抗选择范围为60Ω/100MHz~120Ω/100MHz,典型值选取90Ω/100MHz;L2磁珠阻抗范围为100Ω/100MHz ~1000Ω/100MHz,典型值选取600Ω/100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠;C1、C2两个电容在取值时要相差100倍,典型值为10uF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;C3为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV以上,C3容值可根据测试情况进行调整;(2)电路防护设计要点D1、D2和D3组成USB接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常。

D1、D2、D3选用TVS,TVS反向关断电压为5V;TVS管的结电容对信号传输频率有一定的影响,USB2.0的TVS结电容要求小于5pF。

接口电路设计备注:如果设备为金属外壳,同时单板可以独立的划分出接口地,那么金属外壳与接口地直接电气连接,且单板地与接口地通过1000pF电容相连;如果设备为非金属外壳,那么接口地PGND与单板地GND直接电气连接。

USB接口防静电方案列表

USB接口防静电方案列表

作为电脑和电子产品必备接口,USB堪称万能接口。

你的USB接口是2.0还是3.0?不管是使用还是设计接口都要考虑。

各USB接口理论传输速度如下:

USB 1.0:1.5 Mbps(Low Speed)

USB 1.1:12 Mbps(Full Speed)

USB 2.0:480 Mbps(Hi Speed)

USB 3.0:5 Gbps(640 Mbps, Super Speed)

USB3.1:10 Gbps

USB2.0接口静电保护

USB2.0提供500Mbps的传输速度,本方案采用单颗器件防护,节约空间,

保证信号完整性,满足IEC61000-4-2,等级4,接触放电8kV,空气放电15kV

如对Vbus有过流要求,需配PTC保护。

双USB 接口静电保护

USB2.0提供500Mbps的传输速度,本方案采用单颗器件防护2个USB,节约空间,保证信号完整性,满足IEC61000-4-2,等级4,接触放电8kV,空气放电15kV如对Vbus有过

流要求,需配PTC保护。

可以采用单颗器件同时保护高速数据线,满足静电的测试要求。

电子产品的接口防护需用过压保护器件,很多工程师意识到要用保护器件,但由于选型不当或没按照ESD电路PCB设计原则,造成产品静电测试或EMC测试不通过,产品多次验证测试,浪费人力财力,造成产品延迟上市的事情总有发生,或过度设计,造成成本压力。

雷卯电子专业为客户提供电磁兼容EMC的设计服务,提供实验室做摸底测试,从客户高效,控本方便完成设计,希望为更多的客户能快速通过EMC的项目,提高产品可靠性尽力。

雷卯电子电磁兼容实验室,提供免费测试,提供外围静电保护参考电路。

硬件设计:接口--USB2.0电路设计

硬件设计:接⼝--USB2.0电路设计参考资料:⼀、USB2.0物理特性 1.1、USB接⼝ USB连接器包含4条线,其中VBUS、GND⽤于提供5V电源,电流可达500mA;⽽D+、D-⽤于USB数据传输。

D+、D-是⼀组差分信号,差分阻抗为90欧,具有极强的抗⼲扰性;若遭受外界强烈⼲扰,两条线路对应的电平会同时出现⼤幅度提升或降低的情况,但⼆者的电平改变⽅向和幅度⼏乎相同,所以两者之间的电压差值可始终保持相对稳定。

扩展:USB OTG(即USB On-The-Go)技术在完全兼容USB2.0标准的基础上,增添了电源管理(节省功耗)功能,它允许设备既可作为主机,也可作为外设操作,实现了在没有主机的情况下,设备与设备之间的数据传输。

例如数码相机直接连接到打印机上,通过OTG技术,连接两台设备间的USB⼝,将拍出的相⽚⽴即打印出来。

USB OTG接⼝中有5条线: 2条⽤来传送数据D+ 、D-; 2条是电源线VBUS、GND; 1条是ID线,⽤于识别不同的电缆端点,mini-A插头(即A外设)中的ID引脚接地,mini-B插头(即B外设)中的ID引脚浮空。

当OTG设备检测到接地的ID引脚时,表⽰默认的是A设备(主机),⽽检测到ID引脚浮空的设备则认为是B设备(外设)。

1.2、反向不归零编码(NRZI) 反向不归零编码(Non Return Zero Inverted Code)的编码⽅式⾮常简单,即⽤信号电平的翻转代表“0”,信号电平保持代表“1”。

这种编码⽅式既可以保证数据传输的完整性,还不需要传输过程中包含独⽴的时钟信号,从⽽可以减少信号线的数量。

但是当数据流中出现长“1”电平时,就会造成数据流长时间⽆法翻转,从⽽导致接收器丢失同步信号,使得读取的时序发⽣严重的错误;所以在反向不归零编码中需要执⾏位填充的⼯作,当数据流中出现连续6个“1”电平就要进⾏强制翻转(即⾃动添加⼀位“0”电平),这样接收器在反向不归零编码中最多每七位就会出现⼀次数据翻转,从⽽保证了接收器的时钟同步,同时接收器端会扔掉⾃动填充的“0”电平,保证了数据的正确性(即使连续6个“1”电平后为“0”电平,NRZI仍然会填充⼀位“0”电平); USB的数据包就是采⽤反向不归零编码⽅式,所以在总线中不需要时钟信号。

常用电路的EMC设计

一.常用电路的EMC设计A.电源电路电源电路设计中,功能性设计主要考虑温升和纹波大小。

温升大小由结构散热和效率决定;输出纹波除了采用输出滤波外,输出滤波电容的选取也很关键:大电容一般采用低ESR电容,小电容采用0.1UF和1000pF共用。

电源电路设计中,电磁兼容设计是关键设计。

主要涉及的电磁兼容设计有:传导发射和浪涌。

传导发射设计一般采用输入滤波器方式。

外部采购的滤波器内部电路一般采用下列电路:Cx1和Cx2为X电容,防止差模干扰。

差模干扰大时,可增加其值进行抑制;Cy1和Cy2为Y电容,防止共模干扰。

共模干扰大时,可增加其值进行抑制。

需要注意的是,如自行设计滤波电路,Y电容不可设计在输入端,也不可双端都加Y电容。

浪涌设计一般采用压敏电阻。

差模可根据电源输入耐压选取;共模需要电源输入耐压和产品耐压测试综合考虑。

当浪涌能量大时,也可考虑压敏电阻(或TVS)与放电管组合设计。

1 电源输入部分的EMC设计应遵循①先防护后滤波;②CLASS B规格要求的电源输入端推荐两级滤波电路,且尽量靠近输入端;③在电源输入端滤波电路前和滤波电路中无采样电路和其它分叉电路;如果一定有采样电路,采样电路应额外增加了足够的滤波电路。

原因说明:①先防护后滤波:第一级防护器件应在滤波器件之前,防止滤波器件在浪涌、防雷测试中损坏,或导致滤波参数偏离,第二级保护器件可以放在滤波器件的后面;选择防护器件时,还应考虑个头不要太大,防止滤波器件在PCB布局时距离接口太远,起不到滤波效果。

②CLASS B规格要求的电源输入端推荐两级滤波电路,且尽量靠近输入端:CLASSB要求比CLASS A要求小10dB,即小3倍,所以应有两级滤波电路;CLASSA规格要求至少一级滤波电路;所谓一级滤波电路指包含一级共模电感的滤波电路。

③在电源输入端滤波电路前和滤波电路中无采样电路和其它分叉电路;如果一定有采样电路,采样电路应额外增加了足够的滤波电路:电源采样电路应从滤波电路后取;如果采用电路精度很高,必须从电源输入口进行采样时,必须增加额外滤波电路。

USB3.0电路EMC设计以及过压防护

USB3.0电路EMC 设计以及过压防护随着集成电路的飞速发展以及人们对大容量数据,高传输速率的需求,通用串行总线(Universal Serial Bus )USB 接口迎来另一次飞跃,全新的USB3.0规格在2008年底正式完成并公开发布。

USB3.0传输速率达到4.8Gbps ,是USB2.0的10倍,同时最大供电电流达到1000mA ,这对线路的EMC 和过压防护器件器件提出更高要求。

1. EMC 设计USB2.0采用高速差分信号线来传输数据,USB3.0在保留原有的差分信号线基础上新增两对并行的高速差分信号线,实现高速传输的目的。

而超高的传输速率使EMI 辐射更为严重,同时自身也更容易耦合共模噪音,因此对EMC 设计和相关EMC 器件提出更高要求。

针对USB3.0, 需要在不同的线路添加相应的器件来达到降低EMI, 增强EMS 的目的,推荐的设计方案如下:UPZ1608E181-2R0TF SDCW2012-2-900TF SDCW2012U-2-900TF SDCW2012U-2-900TF UPZ1608E181-2R0TF上述设计中分别在供电线路和地线上串联一颗磁珠,可以滤除设备内部耦合噪音,阻止噪音通过数据线向外辐射。

差分线上采用共模扼流电感可以有效抑制共模噪音。

但是相比USB2.0,USB3.0最大供应电流达到1000mA ,根据 USB 3.0标准,供电电压应该保持在5V +/- 5%的范围, 接口电压范围在4.45V ~5.25V, 因此从USB 电源到连接器压降一般不能超过0.3V ,在磁珠上的压降一般不要超过0.1V, 考虑到最大1A 的供给电流,磁珠直流电阻要小于0.1欧姆,额定电流要大于1A 。

综合以上因素,可以选用顺络电子的UPZ1608E181-2R0TF, 直流阻抗标称值0.05欧姆,额定电流2A ,可以很好满足要求。

在共模扼流器的选择上,USB3.0中兼容2.0的数据线的共模扼流器可以沿用USB2.0的器件:SDCW2012-2-900TF 。

关于欧盟mirco USB接口的新标准规定及相关测试内容详解

>1m

0.1m

ESD Generator EUT

Nearest Wall

PS

80cm

Vertical Coupling Plane

Horizontal Coupling Plane RR R=470kΩ RR

性能判据:

要符合 EPS 的判定准则。

3. 电快速瞬变脉冲群抗扰度 实验要求:

80cm

性能判据: 要符合 EPS 的判定准则。

4. 传导骚扰抗扰度(0.15- 80MHz)

试验要求:

试验按EN 61000-4-6 [8]进行。试验等级要求:

1) 试验应在 0.15MHz~80MHz 频率范围内进行;

2) 试验等级为等级 3 即 10 V rms,骚扰源经过 1kHz 的音频信号进行 80%的幅度调 制;

测试设置如下图所示:

< 40cm >

< 80cm >

EU

< 80cm >

LISN

Pulse Limiter Receiver

3.谐波电流测试

符合标准 EN 61000-3-2/A1[13]即谐波电流发射的要求适用于每相输入电流小于或等于 16A并且输出 功率高于 75W 的设备。由于移动设备即手机类产品基本达不到 75W 这个要求。所以这项不用测试。

要记录在报告中。

测试负载的选择

测试负载是模拟一个能够和 Micro-B 类型的 USB 端口相连接的移动终端(例 如手机)。在 EPS 的输出端口并联一个 1μF 的并联电容。然后串联一个 10k Ω 范围的滑动电阻用于获得最大的额定输出电流。从而实现 EPS 的最大工作 状态。以满足电磁兼容的测试要求。

USB2.0接口EMC设计方案

USB2.0接口EMC设计方案一、接口概述USB 通用串行总线(英文:Universal Serial Bus,简称USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On-The-Go ( OTG)使其能够用于在便携装置之间直接交换资料。

USB接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛盛技术应用电磁兼容设计平台(EDP)软件从接口原理图、结构设计,线缆设计三个方面来设计USB2.0接口的EMC设计方案二、接口电路原理图的EMC设计本方案由电磁兼容设计平台(EDP)软件自动生成1. USB2.0接口防静电设计图1 USB 2.0接口防静电设计接口电路设计概述:本方案从EMC原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决EMC 问题。

电路EMC设计说明:(1)电路滤波设计要点:L1为共模滤波电感,用于滤除差分信号上的共模干扰;L2为滤波磁珠,用于滤除为电源上的干扰;C1、C2为电源滤波电容,滤除电源上的干扰。

L1共模电感阻抗选择范围为60Ω/100MHz ~120Ω/100MHz,典型值选取90Ω/100MHz;L2磁珠阻抗范围为100Ω/100MHz ~1000Ω/100MHz,典型值选取600Ω/100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠;C1、C2两个电容在取值时要相差100倍,典型值为10uF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;C3为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV以上,C3容值可根据测试情况进行调整;(2)电路防护设计要点D1、D2和D3组成USB接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常。

D1、D2、D3选用TVS,TVS反向关断电压为5V;TVS管的结电容对信号传输频率有一定的影响,USB2.0的TVS结电容要求小于5pF。

USB 2.0的EMI和ESD设计

USB 2.0的EMI和ESD设计提供双向、实时数据传输的USB接口,以其即插即用、可热插拔和价格低廉等优点,目前已成为计算机和信息电子产品连接外围设备的首选接口。

时下流行的USB2.0具有高达480Mbps的传输速率,并与传输速率为12Mbps的全速USB1.1和传输速率为1.5Mbps的低速USB1.0完全兼容。

这使得数字图像器、扫描仪、视频会议摄像机等消费类产品可以与计算机进行高速、高性能的数据传输。

另外值得一提的是,USB2.0的加强版USB OTG可以实现没有主机时设备与设备之间的数据传输。

例如。

数码相机可以直接与打印机连接并打印照片,PDA可以与其它品牌的PDA进行数据传输或文件交换。

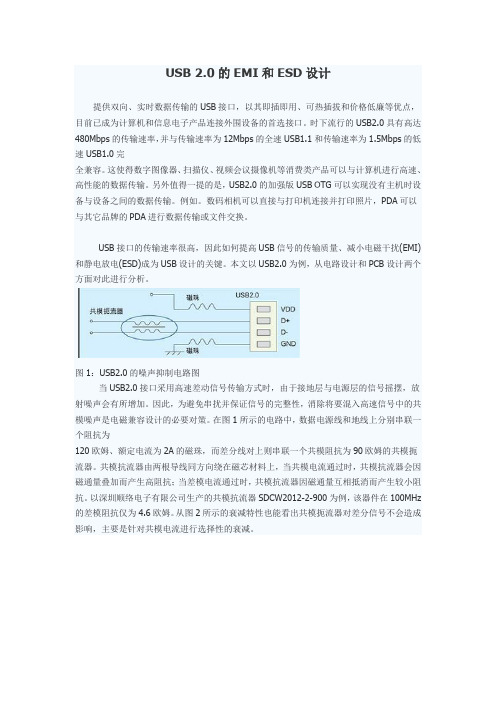

USB接口的传输速率很高,因此如何提高USB信号的传输质量、减小电磁干扰(EMI)和静电放电(ESD)成为USB设计的关键。

本文以USB2.0为例,从电路设计和PCB设计两个方面对此进行分析。

图1:USB2.0的噪声抑制电路图当USB2.0接口采用高速差动信号传输方式时,由于接地层与电源层的信号摇摆,放射噪声会有所增加。

因此,为避免串扰并保证信号的完整性,消除将要混入高速信号中的共模噪声是电磁兼容设计的必要对策。

在图1所示的电路中,数据电源线和地线上分别串联一个阻抗为120欧姆、额定电流为2A的磁珠,而差分线对上则串联一个共模阻抗为90欧姆的共模扼流器。

共模抗流器由两根导线同方向绕在磁芯材料上,当共模电流通过时,共模抗流器会因磁通量叠加而产生高阻抗;当差模电流通过时,共模抗流器因磁通量互相抵消而产生较小阻抗。

以深圳顺络电子有限公司生产的共模抗流器SDCW2012-2-900为例,该器件在100MHz 的差模阻抗仅为4.6欧姆。

从图2所示的衰减特性也能看出共模扼流器对差分信号不会造成影响,主要是针对共模电流进行选择性的衰减。

图2:SDCW2012-2-900的衰减频谱由于USB接口具有可热插拔性,USB接口很容易因不可避免的人为因素而导致静电损坏器件,比如死机、烧板等。

EMC案例分析精解6-- 磁珠放置不当引起的浪涌测试问题-牛金海V1

笔记本电脑上磁珠的应用

主机USB上磁珠的接口

USB HUB上的接口

课堂练习

某系统有66M的工作频率,EMC测试时发现它有 几个倍频超标,特别是200M频点超标严重。这 种情况整改需要选用什么样的磁珠? 选用原则 ,抑制干扰的时候,对于工作频点的阻抗要小, 不能影响正常工作。

磁珠A和磁珠B的阻抗峰值都在100MHz和200MHz 之间,但是磁珠A 的阻抗频率曲线比较平坦,但是磁珠B的比较陡峭。如果将两个磁珠 分别放在如下20MHz的信号线上看看,各自的效果如何?

具体操作时:磁珠A比较适合用于电源线,二磁珠B表适合信号线, 在保证信号完整的情况下,尽可能对EMI频点附近的噪声产生最大的 衰减。

磁珠在直流供电回路中的应用

不同场景采用不同类型的磁珠

谢 谢!

从输出波形来看,磁珠B的输出波形失真要明显 小于磁珠A。原因是磁珠B的阻抗频率波形比较陡 峭,其阻抗在200MHz时比较高,只对200MHz 附近的信号的衰减较大,但是对频谱很宽的方波 波形影响较小。而磁珠A的阻抗频率特性比较平 坦,其对信号的衰减频谱也较宽,因此对方波的 波形影响也较大

EMI测试结果显示,磁珠A与磁珠B都会对EMI的 噪声产生很大的衰减。磁珠A在整个EMI频谱范 围内的衰减要稍微好于磁珠B。

五、更深入的分析

磁珠专用于抑制信号线、电源线上的高频噪声和尖峰干扰,还具有吸收 静电脉冲的能力。磁珠是用来吸收超高频信号,象一些RF电路,PLL, 振荡电路,含超高频存储器电路(DDRSDRAM,RAMBUS等)都需 要在电源输入部分加磁珠,而电感是一种蓄能元件,用在LC振荡电 路,中低频的滤波电路等,其应用频率范围很少超过50MHZ。 磁珠 有很高的电阻率和磁导率,等效于电阻和电感串联,但电阻值和电感 值都随频率变化。

USB2.0接口差分信号线设计

引言通用串行总线(Universal Serial Bus)从诞生发展到今天,USB协议已从1.1过渡到2.O,作为其重要指标的设备传输速度,从1.5 Mbps;的低速和12 Mbps 的全速,提高到如今的480 Mbps的高速。

USB接口以其速度快、功耗低、支持即插即用、使用安装方便等优点得到了广泛的应用。

目前,市场上以USB2.0为接口的产品越来越多,绘制满足USB2.0协议高速数据传输要求的PCB板对产品的性能、可靠性起着极为重要的作用,并能带来明显的经济效益。

USB2.0接口是目前许多高速数据传输设备的首选接口,实践表明:在高速USB 主、从设备的研发过程中,正确设计PCB板能充分发挥USB2.O高速性能。

但是,若PCB板设计不当,则传输速率可能根本达不到预期目的,甚至会导致高速USB2.0设备只能工作在全速状态。

下面介绍USB2.0设备高速数据传输PCB板设计。

1 USB2.0接口差分信号线设计USB2.0协议定义由两根差分信号线(D 、D-)传输高速数字信号,最高的传输速率为480 Mbps。

差分信号线上的差分电压为400 mV,差分阻抗(Zdiff)为90(1±O.1)Ω。

在设计PCB板时,控制差分信号线的差分阻抗对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰电压。

差分线2D模型如图1所示。

差分线由两根平行绘制在PCB板表层(顶层或底层)发生边缘耦合效应的微带线(Microstrip)组成的,其阻抗由两根微带线的阻抗及其和决定,而微带线的阻抗(Zo)由微带线线宽(W)、微带线走线的铜皮厚度(T)、微带线到最近参考平面的距离(H)以及PCB板材料的介电常数(Er)决定,其计算公式为:Zo={87/sqrt(Er 1.41)]}ln[5.98H/(0.8W T)]。

影响差分线阻抗的主要参数为微带线阻抗和两根微带线的线间距(S)。

usb端口emi整改方案

USB端口EMI整改方案简介电磁干扰(EMI)是指在电子设备中,通过电缆、线路或空气传播的电磁能量干扰其他电子设备或系统的现象。

USB接口作为一种常见的外部设备连接方式,在一定程度上也会引起EMI问题。

为了避免USB端口引发的EMI问题,需要进行相应的整改措施。

本文档将介绍USB端口EMI问题的原因分析,并提供一套完整的整改方案,以减轻USB端口对其他电子设备或系统的干扰。

USB端口EMI问题的原因分析USB端口引发的EMI问题主要有以下几个方面的原因:1. 信号回波在USB数据传输过程中,信号的传输速度较快。

因此,当信号到达接收端时,可能会发生回波现象。

这种回波会产生不同频率的电磁波,从而导致EMI问题的发生。

2. USB电缆长度USB电缆的长度也是引发EMI问题的一个因素。

过长的电缆会增加信号传输的延迟,导致更多的信号回波和信号衰减,从而增加了EMI的发生概率。

3. 接地问题USB端口的接地问题也是引发EMI问题的原因之一。

当接地不良或接地回路不完整时,可能会引入额外的电磁能量,进而导致EMI。

4. 设计不合理一些USB端口设计不合理也可能导致EMI问题的出现。

例如,不合适的线路布局、不合格的元件选用等都可能引发EMI问题。

整改方案1. 加入滤波器滤波器是一种常见的用于解决EMI问题的工具。

可以在USB端口的电路中加入滤波器来抑制电磁干扰。

通常情况下,使用LC滤波器可以有效地过滤高频噪声。

2. 优化线路布局合理的线路布局可以降低EMI问题的发生概率。

在设计USB端口时,应尽量避免信号线与电源线、地线等相互交叉。

此外,要注意信号线的长度和走向,减少线路回绕。

3. 优化接地方案良好的接地方案对于减轻EMI问题至关重要。

确保接地回路完整、接地点良好地连接在一起,可以有效地消除因接地问题引起的EMI。

4. 合理选择元件在设计USB端口时,应选择合适的元器件。

合格的电容、电感、反向二极管等元件能够减少EMI问题的发生。

USB2.0接口EMC设计方案

电磁兼容设计平台(EDP)应用案例——以太网口USB2.0 接口 EMC 设计方案一、接口概述USB 通用串行总线(英文:Universal Serial Bus,简称 USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On-The-Go ( OTG)使其能够用于在便携装置之间直接交换资料。

USB 接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛盛技术应用电磁兼容设计平台(EDP)软件从接口原理图、结构设计,线缆设计三个方面来设计USB2.0 接口的 EMC 设计方案二、接口电路原理图的EMC设计本方案由电磁兼容设计平台(EDP)软件自动生成B2.0 接口防静电设计图1 USB 2.0接口防静电设计接口电路设计概述:本方案从 EMC 原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决 EMC 问题。

电路 EMC 设计说明:(1)电路滤波设计要点:L1 为共模滤波电感,用于滤除差分信号上的共模干扰;L2 为滤波磁珠,用于滤除为电源上的干扰;C1、C2 为电源滤波电容,滤除电源上的干扰。

L1共模电感阻抗选择范围为60Ω/100MHz ~120 Ω /100MHz ,典型值选取90Ω/100MHz ;L2 磁珠阻抗范围为 100Ω /100MHz ~1000Ω /100MHz ,典型值选取 600Ω /100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠;C1、C2 两个电容在取值时要相差 100 倍,典型值为 10uF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;C3 为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV 以上,C3 容值可根据测试情况进行调整;( 2)电路防护设计要点D1、 D2 和 D3 组成 USB 接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

U S B2.0接口E M C设计方案

一、接口概述

USB?通用串行总线(英文:Universal?Serial?Bus,简称USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On-The-Go(?OTG)使其能够用于在便携装置之间直接交换资料。

USB接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛盛技术应用电磁兼容设计平台(EDP)软件从接口原理图、结构设计,线缆设计三个方面来设计USB2.0接口的EMC设计方案

二、接口电路原理图的EMC设计

本方案由电磁兼容设计平台(EDP)软件自动生成

1. USB

2.0接口防静电设计

图1 USB 2.0接口防静电设计

接口电路设计概述:

本方案从EMC原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决EMC问题。

电路EMC设计说明:

(1)

电路滤波设计要点:

L1为共模滤波电感,用于滤除差分信号上的共模干扰;

L2为滤波磁珠,用于滤除为电源上的干扰;

C1、C2为电源滤波电容,滤除电源上的干扰。

L1共模电感阻抗选择范围为60Ω/100MHz ~120Ω/100MHz,典型值选取90Ω

/100MHz;

L2磁珠阻抗范围为100Ω/100MHz ~1000Ω/100MHz,典型值选取600Ω/100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠;

C1、C2两个电容在取值时要相差100倍,典型值为10uF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;

C3为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV以上,C3容值可根据测试情况进行调整;

(2)电路防护设计要点

D1、D2和D3组成USB接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常。

D1、D2、D3选用TVS,TVS反向关断电压为5V;TVS管的结电容对信号传输频率有一定的影响,USB2.0的TVS结电容要求小于5pF。

接口电路设计备注:

如果设备为金属外壳,同时单板可以独立的划分出接口地,那么金属外壳与接口地直接电气连接,且单板地与接口地通过1000pF电容相连;

如果设备为非金属外壳,那么接口地PGND与单板地GND直接电气连接。

三、连接器设计

本方案由电磁兼容设计平台(EDP)软件自动生成

USB AF连接器USB信号排序设计

图1 USB连接器结构设计

连接器USB与机体的搭接方式:

(1)面板开孔时采用精密的铣削加工技术,使孔眼的形状更适合连接器的放置,避免孔眼切削不精确的地方出现缝隙,进而降低电磁干扰辐射;经过测试证明,精确的铣削开孔加工可以提高12~18%的电磁兼容性;

(2)机体与USB金属连接器之间的接合处要增加金属弹片,使两者接合时能够保持良好的导电性能。

具体搭接方式如上图所示:

四、线缆设计

本方案由电磁兼容设计平台(EDP)软件自动生成

USB-2.0接口信号线缆

线缆设计要求:USB2.0 AF连接器普通型

图1 USB金属连接器的搭接

屏蔽层与金属连接器的搭接:

(1)屏蔽电缆的屏蔽层要求与金属连接器进行360°的搭接;搭接方式如上图:(2)屏蔽电缆屏蔽层要避免出现单独的“尾巴”现象。

五、结束语

电磁兼容设计平台(EDP),依据最专业的EMC专家方案知识库,快速输出符合产品设计要求的指导性的EMC解决方案。

即是工程师身边的产品设计、学习助手,又是企业的EMC技术方案库,是产品电磁兼容性能的保证。

图2 USB-2.0信号电缆

电缆设计:

(1)USB-2.0信号电缆采用网状编织屏蔽层的屏蔽方式,且网状编织层编织密度要求不小于90%;差分线组采用铝箔屏蔽;

(2)内部组线时,差分电缆采用双绞传输,双绞绞距一般为最小绞距的2倍,(最小绞距= D为电缆的外径);组线方式如上图所示:

(3)电缆两端需要增加磁环处理,磁环内径与电缆的外径要紧密结合,尽量选择厚长型的磁环。

走线设计:

(1)USB-2.0信号电缆走线时要求远离其他强干扰源,如电源模块;

(2)电缆走线最好单独走线或与其他模拟以及功率线缆保持10cm以上距离,切不可与其他线缆一起混合捆扎。