FPGA电路设计中的毛刺问题的研究

(整理)FPGA中的亚稳态毛刺异步FIFO.

(整理)FPGA中的亚稳态毛刺异步FIFO.1亚稳态1.1亚稳态的定义亚稳态是指触发器无法在某个规定时间段内达到一个确定的状态。

当一个触发器进入亚稳态时,该触发器的输出何时能稳定以及会稳定在哪个状态都不能确定。

在达到稳定之前的时间,触发器输出一些中间电平或者处于震荡状态,并且这种无用的输出电平可以沿着信号通路上级联的触发器传播下去。

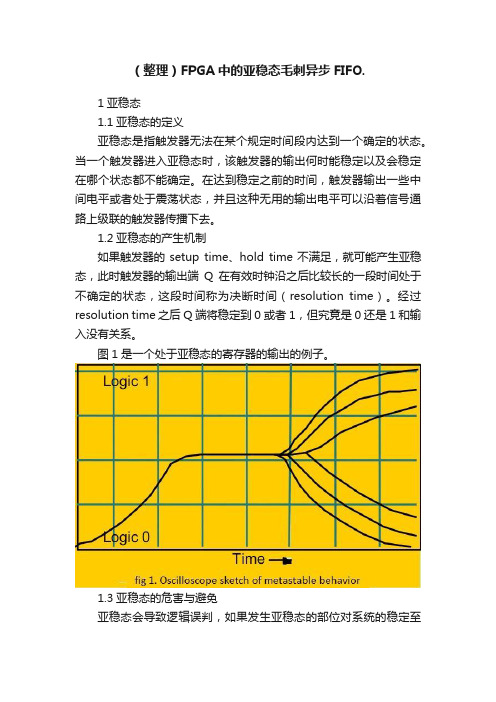

1.2亚稳态的产生机制如果触发器的setup time、hold time不满足,就可能产生亚稳态,此时触发器的输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,这段时间称为决断时间(resolution time)。

经过resolution time 之后Q端将稳定到0或者1,但究竟是0还是1和输入没有关系。

图1是一个处于亚稳态的寄存器的输出的例子。

1.3亚稳态的危害与避免亚稳态会导致逻辑误判,如果发生亚稳态的部位对系统的稳定至关重要同时缺少防错机制,则可能导致系统崩溃(逻辑挂死)。

逻辑误判可以通过特殊设计减轻危害,例如异步fifo的gray设计。

比发生部位本身的逻辑误判更严重的是亚稳态传递。

亚稳态传递会扩大故障面,让问题变得复杂。

在完全同步的设计中,CAD工具可以方便的分析每一个触发器的建立保持时间。

理论上一个时序完全收敛的纯同步设计不会有亚稳态问题。

和有赖于时序分析的完备性,例如所使用的timing mode与实际芯片及其工作条件的吻合度,实际时钟抖动、偏斜与预期是否一致等。

扩大时序裕量可以降低亚稳态发生的概率。

当前一个数字芯片上往往有多个时钟域,时钟域之间的异步设计是必不可少的。

只要系统中存在异步设计,则亚稳态无法避免,但我们可以尽量限制亚稳态的影响范围并通过特殊的逻辑设计容忍可能的逻辑误判。

1.3.1缩小亚稳态的影响范围a.“将异步输出寄存器的扇出限制为1”如图2所示,让异步输出寄存器的扇出为1相当于减少了异步路径的条数。

若异步信号有多个输出,则可能因为路径延迟和时钟偏斜导致有的寄存器采到有效值,有的寄存器进入不确定的状态,如图2和图3所示。

毛刺的消除

毛刺

时序仿真输出波形

引入了D 引入了D触发器的长帧同步时钟的产生

module longframe2(clk,strb); parameter DELAY=8; input clk; output strb; reg[7:0] counter; reg temp,strb; always@(posedge clk) begin if(counter==255) counter<=0; else counter<=counter+1; end always@(posedge clk) begin strb<=temp;end //引入触发器 //引入触发器 always@(counter) begin if(counter<=(DELAY-1)) temp<=1; else temp<=0; if(counter<=(DELAYend endmodule

消除毛刺后的时序仿真输出波形

延时方式去毛刺

延时方式去毛刺

逻辑方式去毛刺

逻辑方式去毛刺

定时方式去毛刺

定时方式去毛刺

跨时钟域设计

module metastable(clka,clkb,ina,outb); input clka,clkb,ina; output outb; reg outb,outa; always @(posedge clka) outa=ina; always @(posedge clkb) outb=outa; outa outb~reg0 endmodule

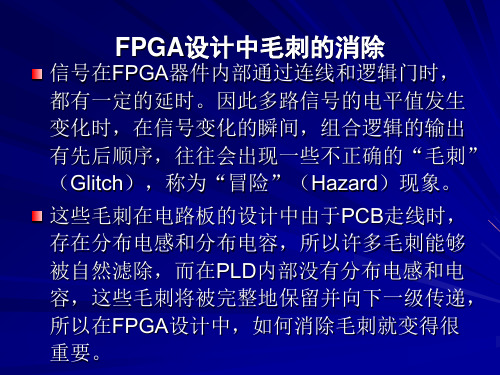

FPGA设计中毛刺的消除 FPGA设计中毛刺的消除

信号在FPGA器件内部通过连线和逻辑门时, 信号在FPGA器件内部通过连线和逻辑门时, 都有一定的延时。因此多路信号的电平值发生 变化时,在信号变化的瞬间,组合逻辑的输出 有先后顺序,往往会出现一些不正确的“毛刺” 有先后顺序,往往会出现一些不正确的“毛刺” (Glitch),称为“冒险”(Hazard)现象。 Glitch),称为“冒险” Hazard)现象。 这些毛刺在电路板的设计中由于PCB走线时, 这些毛刺在电路板的设计中由于PCB走线时, 存在分布电感和分布电容,所以许多毛刺能够 被自然滤除,而在PLD内部没有分布电感和电 被自然滤除,而在PLD内部没有分布电感和电 容,这些毛刺将被完整地保留并向下一级传递, 所以在FPGA设计中,如何消除毛刺就变得很 所以在FPGA设计中,如何消除毛刺就变得很 重要。

毛刺信号消除电路的研究与实现

第32卷第4期集宁师专学报Vol.32,No.42010年12月Journal of JiningTeachers College Dec.2010收稿日期:2010-06-13作者简介:聂阳,男,汉族,内蒙古乌兰察布市人,硕士,研究方向:系统级芯片设计、D SP 电路设计。

基金资助:2010年度内蒙古自治区高等学校科学研究项目:《基于FPG A 的数字电路教学方法变革与研究思路》(编号:N )毛刺信号消除电路的研究与实现聂阳,赵鹏宇,荆丽丽(集宁师范学院物理系,内蒙古乌兰察布012000)摘要:本文分析了毛刺信号的消除电路,以电路实例给出毛刺信号消除的三种电路解决方案,并利用FPG A 和ED A 仿真软件给出了仿真结果,具有一定的工程指导意义。

关键词:毛刺信号;延时电路;定时电路中图分类号:TN 492文献标识码:A 文章编号:1009-7171(2010)04-0011-051引言信号在数字系统内部传输时,都有一定的延时。

延时的大小不仅与连线的长短和逻辑单元的数目有关,还受器件的制造工艺、工作电压、温度等条件的影响;同时信号的高低电平转换也需要一定的过渡时间[]1。

当多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号,这些尖峰信号称为毛刺。

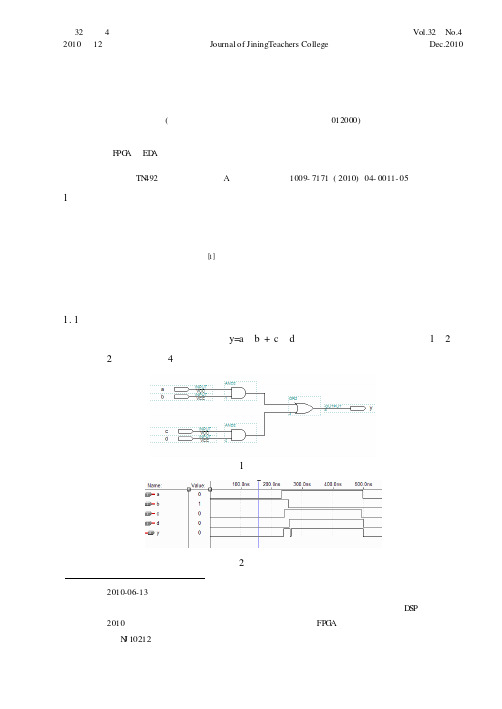

1.1电路理论分析根据理论分析,若实现如下电路y=ab +cd ,其电路原理图和仿真图如图1、2所示,从图2中可以看到4个信号都发生变化时,电路的输出产生毛刺。

图1电路原理图图2电路仿真图J 1021212集宁师专学报第32卷2毛刺信号消除电路解决方案2.1消除毛刺信号—增加冗余项函数式和真值表所描述的是静态逻辑,而竞争则是从一种稳态到另一种稳态的过程。

因此竞争是动态过程,它发生在输入变量变化时。

此时,若在两个卡诺图圆圈相切处增加一个冗余的卡诺图圈,即卡诺图的两圆相切处增加一个圆,可以消除逻辑冒险。

FPGA中的毛刺信号解析

FPGA设计中毛刺信号解析在FPGA的设计中,毛刺现象是长期困扰电子设计工程师的设计问题之一, 是影响工程师设计效率和数字系统设计有效性和可靠性的主要因素。

由于信号在FPGA的内部走线和通过逻辑单元时造成的延迟,在多路信号变化的瞬间,组合逻辑的输出常常产生一些小的尖峰,即毛刺信号,这是由FPGA 内部结构特性决定的。

毛刺现象在FPGA的设计中是不可避免的,有时任何一点毛刺就可以导致系统出错,尤其是对尖峰脉冲或脉冲边沿敏感的电路更是如此。

任何组合电路、反馈电路和计数器都可能是潜在的毛刺信号发生器,但毛刺并不是对所有输入都有危害,如触发器的D输入端,只要毛刺不出现在时钟的上升沿并满足数据的建立保持时间,就不会对系统造成危害。

而当毛刺信号成为系统的启动信号、控制信号、握手信号,触发器的清零信号(CLEAR)、预置信号(PRESET)、时钟输入信号(CLK)或锁存器的输入信号时就会产生逻辑错误。

在实际设计过程中,应尽量避免将带有毛刺的信号直接接入对毛刺敏感的输入端上,对于产生的毛刺,应仔细分析毛刺的来源和性质,针对不同的信号,采取不同的解决方法加以消除。

因此,克服和解决毛刺问题对现代数字系统设计尤为重要。

本文从FPGA的原理结构的角度探讨了产生毛刺的原因及产生的条件,在此基础上,总结了多种不同的消除方法,在最后结合具体的应用对解决方案进行深入的分析。

1毛刺产生的原因以图1的例子分析毛刺产生的起因:图1是一个3位同步加法计数器,当使能端为高电平时,在每个时钟上升沿时刻,QA ,QB,QC从000逐步变到111,进入到全1状态后,进位输出端输出半个时钟脉冲宽度的高电平,但从图2仿真结果中可以看到在011变化到100时刻ROC出现了尖脉冲,即毛刺。

以Xilinx的FPGA为例分析其内部结构,如图3所示[2]。

FPGA芯片是由可构造的输入输出块(Input/OutputBlock,IOB)、可构造逻辑块(Cinfigur able Logic Block,CLB)和可编程连线资源(Programmable Interconnect Array,PIA)3种可构造单元构成的。

数字电路毛刺消除问题

数字电路⽑刺消除问题参考博⽂:和1. ⽑刺的产⽣原因:冒险和竞争使⽤分⽴元件设计电路时,由于PCB在⾛线时,存在分布电容和电容,所以在⼏ns内⽑刺被⾃然滤除,⽽在PLD内部没有分布电感和电容,所以在PLD/FPGA设计中,竞争和冒险问题⽐较重要。

信号在FPGA器件内部通过连线和逻辑单元时,都有⼀定的延时。

延时的⼤⼩与连线的长短和逻辑单元的数⽬有关,同时还受器件的制造⼯艺、⼯作电压、温度等条件的影响。

信号的⾼低电平转换也需要⼀定的过渡时间。

由于存在这两⽅⾯因素,多路信号的电平值发⽣变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现⼀些不正确的尖峰信号,这些尖峰信号称为"⽑刺"。

如果⼀个组合逻辑电路中有"⽑刺"出现,就说明该电路存在"冒险"。

可以概括的讲,只要输⼊信号同时变化,(经过内部⾛线)组合逻辑必将产⽣⽑刺。

将它们的输出直接连接到时钟输⼊端、清零或置位端⼝的设计⽅法是错误的,这可能会导致严重的后果。

所以我们必须检查设计中所有时钟、清零和置位等对⽑刺敏感的输⼊端⼝,确保输⼊不会含有任何⽑刺。

存在逻辑冒险的电路:仿真波形:2. 判断是否存在冒险关于冒险的知识,数电书上有详细的说明,当时没有认真学,只了解个⼤概,现在⼜要重新看...还记得当年画卡诺图时的痛苦冒险按照产⽣⽅式分为静态冒险 & 动态冒险两⼤类。

静态冒险指输⼊有变化,⽽输出不应该变化时产⽣的窄脉冲;动态冒险指输⼊变化时,输出也应该变化时产⽣的冒险。

动态冒险是由静态冒险引起的,所以,存在动态冒险的电路也存在静态冒险。

静态冒险根据产⽣条件不同,分为功能冒险和逻辑冒险两种。

当有两个或两个以上的输⼊信号同时变化时,在输出端有⽑刺,称为功能冒险;如果只有⼀个输⼊变量变化时,出现的冒险称为逻辑冒险。

因为动态冒险是由静态冒险引起的,所以消除了静态冒险,也就消除了动态冒险。

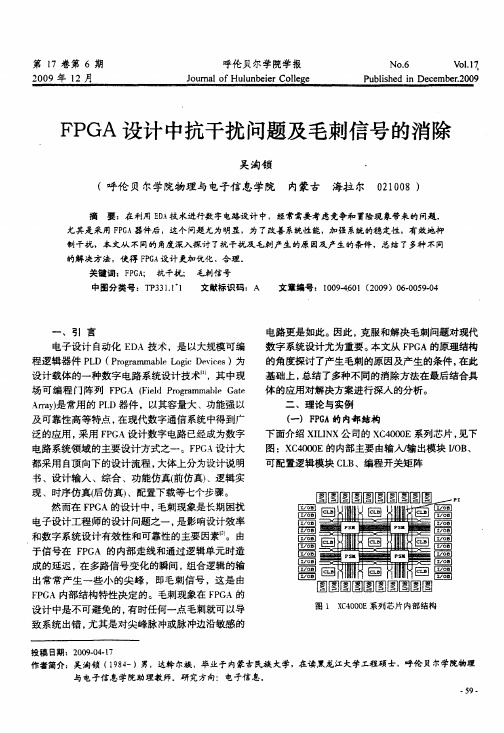

FPGA设计中抗干扰问题及毛刺信号的消除

制干 扰 ,本 文从 不 同 的 角度 深 入探 讨 了抗 干扰 及 毛刺 产 生 的原 因及 产 生 的条件 ,总 结 了多种 不 同

的解决方法,使得 F G 设计更加优化 ,合理。 PA

关键 词 :F G ; 抗 干扰 ; 毛刺信 号 PA 中图分 类号 :T 3 i1 P3. 1 文献标 识码 :A 文 章编 号 : 10 - 0 2 0 )0.090 0 94 1(0 9 60 5.4 6

器。

( )F G 二 P A中干 扰 的原 因

信号 在F G 器件 内部通过 连线 和逻 辑单元 PA 时, 都有一定 的延时。 延时的大小与连线的长短和

逻辑单元的数 目 有关 ,同时还受器件的制造工艺 、

在F G 设 计 中 ,设 计思 路一般 是 微处 理 器 和 PA F G 相 结合 的方 法 ,另外 ,还 有 电源 、信 号 的采 PA

第 l 卷 第 6 期 7 20 0 9年 1 2月

呼伦贝尔学院学报

J u n l f Hu u b ir Co l o r a l n e e l o e

No. 6

Voi1 .

P bih d i c mb r 0 9 u l e n De e e. 0 s 2

.

5 9.

P M、 S 可编程连线 P 组成 ,其中我们主要采用编 I

程 的方式 控制其 内部 门阵列 的连 接情况 。 另外 一种 较常用 的 F G P A为 Atr公 司生产 的 F E 0 E系 l a e L X1K

输的路径不同, 或是各种器件延迟时间不同 , 这种

现象也称为竞争 。 当然所以竞争都有可能造成输 出 波形产生不应有的尖脉冲 ( 俗称毛刺 ) 即产生毛 , 刺信号, 这种现象成为冒险。 如果布尔式中有相反 的信号则可能产生竞争和 冒险现象。

FPGA亚稳态和毛刺小结

FPGA亚稳态和毛刺小结1首先介绍一下建立时间和保持时间的基本概念:1.1建立时间和保持时间:图1.1tsh:建立时间,th:保持时间建立时间:是指时钟触发器上升沿到来之前,数据稳定不变的时间。

如果建立时间不够,则数据不能在这个时钟进入触发器。

保持时间:是指时钟触发器上升沿到来之后,数据保持不变的时间。

如果保持时间不够,则数据同样不能被打入触发器。

由于PCB走线时,存在分布电感和电容,所以几纳秒的毛刺将被自然滤除,而在PLD内部决无分布电感和电容,所以在PLD/FPGA设计中,竞争和冒险问题将变的较为突出。

2关于毛刺的基本概念:信号在FPGA内通过连线和逻辑单元时,都会产生延时。

延时产生的原因:①:连线的长短和逻辑单元的数目,②:受器件的制造工艺、工作电压、温度等条件的影响,所以在信号变化的瞬间,组合逻辑的输出有先后顺序,往往会产生一些尖峰的信号,这些信号称为毛刺。

如果有毛刺,该电路称为冒险电路。

只由内部电路决定。

看下面的例子:我们可以看到,A,B,C,D四个输入信号,最后导致输出出现毛刺。

原因是A,B,C,D信号输入不是同时发生。

(即使同时发生,它们各自由于连线和逻辑单元的原因,到达门电路的时间也不同。

)所以可以说,只要输入信号同时发生变化,由于走线的原因,必将产生毛刺。

所以我们不能直接将其输出,要进行一些措施。

方法一:格雷码代替二进制计数器,由于格雷码每次只有一位进行变化,不满足产生毛刺的条件。

所以可以减小错误方法二:另一种更常见的方法是利用D触发器的D输入端对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输出信号,这种方法类似于将异步电路转化为同步电路。

如图:由于异步输入不是总能满足所馈送的触发器满足建立时间和保持时间,所以常常会产生亚稳态。

3关于亚稳态知识的基本概念图1.2:采用一个时钟同步下的模型其中:tco为触发器数据输出延时;T delay=T comb 为经过组合逻辑的延时;Tsetup(tsu)为建立时间;Tpd为时钟延时,一般时钟延时可以忽略。

Verilog如何消除毛刺

Verilog如何消除毛刺?(VHDL也能同理消除毛刺)0 引言现场可编程门阵列(FPGA)是1985年由美国Xilinx公司首先推出的一种新型的PLD。

FPGA在结构上由逻辑功能模块排列成阵列,并由可编程的内部连线连接这些功能模块来实现一定的逻辑功能。

FPGA的功能由逻辑结构的配置数据决定,这些配置数据存放在片外的EPROM或其他存储器上。

由于FPGA规模大、集成度高、灵活性更强,实现的逻辑功能更广,因此已逐步成为复杂数字硬件电路设计的首选。

1 FPGA的基本结构FPGA通常由可编程逻辑单元 CLB、可编程输入输出单元lOB及可编程连线资源组成。

通常CLB包含组合逻辑部分和时序逻辑部分,组合逻辑一般又包括查询表(Look-up Table)和相关的多路选择器(Multiplexer)。

而时序逻辑部分则包含触发器(DFF)和一些相关的多路选择器。

lOB主要提供FPGA内部和外部的接口,连线资源则提供CLB与lOB之间以及各CLB之间的通讯功能。

FPGA芯片的基本结构如图1所示,其中开关盒可对水平和竖直连线资源进行切换,连接盒可将CLB的输入输出连接到连线资源中。

2 verilog HDL语言的特点与优化设计Verilog HDL语言是硬件描述语言的一种。

它能形式化地抽象表示电路的行为和结构,同时支持层次设计中逻辑和范围的描述。

设计时可借用高级语言的精巧结构来简化电路行为的描述。

此外,该语言还具有电路仿真与验证机制,可以保证设计的正确性,同时支持电路描述由高层到低层的综合转换,且硬件描述与实现工艺无关,便于文档管理,易于理解和设计重用。

由于Verilog HDL语言易于理解、设计灵活,因此,Verilog HDL语言已经成为目前FPGA编程最常用的工具之一。

然而,正是其设计灵活的特点使工程师必须面对采用哪种编程风格才能使逻辑电路精确工作的问题。

因为如果某些原因导致逻辑电路发生误动作,则有可能会造成系统无法正常工作。

FPGA毛刺产生的原因及其抑制方法

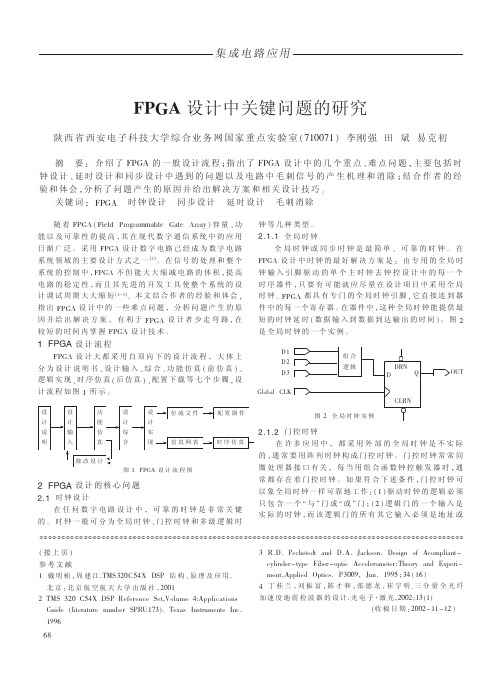

图 2给出 了一个逻 辑 冒险 的电路 ,从图 3的仿真 波形可

以看 出, “ A、B、C 、D ”4个输入 信号 经过布 线延时 以后 ,

高低 电平变换不 是同时发生 的,这导致输 出信号 “ U ”出现 OT

了毛刺 。可 以概括 地讲 ,只要输 入信号 同时变化 ,组合逻辑

必将产生毛刺 。 将 它们的输 出直接连接 到时钟输 入端 、清零

8 … A .

tu s

t — h

3 … B .

时 钟

t: s 建立时间 t: u h保持时间

8. . C .

… . .

D

图 1 建 立与 保 持 时 间

图 2 逻 辑 冒 险 的 电 路

D C B A ot u 0 。 0 O 0 O I , 一 l I 。 ; : i : ; :

2 竞争和 冒 险

在使用分立元件设计数字 系统时 ,由于 P B走 线时 ,存 C 在分布 电感 和电容 ,所 以几 纳秒 的毛刺将被 自然滤 除 ,而在

P D 内部 决无分 布 电感 和 电容 ,所 以在 P DF G 设计 中 , L L /P A 竞争和 冒险问题将变得较为突出 。 信号在 F G 器件 内部 通过连 线和逻辑 单元 时 ,都有 一 PA

电脑 编程技 巧与维护 பைடு நூலகம்

FG P A毛刺产生 的原 因及其抑制 方法

孙 晓东

( 山电视发射台 ,唐 山 0 3 0 ) 唐 60 0 摘 要 : 简单分析 了 P DF G L /P A内部产生毛刺 、影响和其产生过 程、原理 。通过改变毛刺产 生条件 ( 用格 雷码取 采

代 二 进 制 计 数 器) ,采 用 同步 电路 等 方 法 减 少其 危 害 。

FPGA设计中毛刺信号解析

FPGA设计中毛刺信号解析

在FPGA(Field-Programmable Gate Array)设计中,毛刺信号是一种不稳定的、短暂的、高频的信号噪声。

这种信号可能是由于电路中的突变或者切换引起的,通常会引起系统性能下降或者功能异常。

因此,解析和处理毛刺信号对于FPGA设计来说非常重要。

下面将介绍如何解析毛刺信号以及常见的解决方法。

一种常见的解决方法是通过信号滤波来降低毛刺的影响。

滤波可以通过数字滤波器实现,常见的滤波器包括低通滤波器、中通滤波器和带通滤波器。

根据毛刺信号的特征,选择适合的滤波器参数,可以有效地去除毛刺信号。

另一种方法是通过信号的去抖动处理来消除毛刺影响。

去抖动是一种通过延迟信号的上升或下降边沿的方法,以消除信号中的瞬时毛刺。

通过添加适当的延迟,我们可以使得毛刺信号在系统中不被处理,从而减少对系统性能的影响。

此外,我们还可以通过时序优化来减少毛刺问题。

时序优化包括调整时钟频率、优化时序路径和消除时序冲突等。

通过优化时序,我们可以使得信号在FPGA中的传输更加平稳和稳定,从而减少毛刺信号的出现。

在一些特殊情况下,信号毛刺可能需要通过硬件逻辑设计来解决。

例如,我们可以使用状态机、锁存器或者计数器等特殊电路来对毛刺信号进行抑制和消除。

综上所述,FPGA设计中毛刺信号解析是一个复杂的问题,需要综合考虑信号源、滤波、去抖动、时序优化和硬件逻辑等方面。

通过合理选择

解决方案,并借助模拟和数字混合仿真工具的帮助,我们可以有效地解析和处理毛刺信号,提高系统性能和功能稳定性。

FPGA设计中关键问题的研究

!"

集成电路应用

够" 数据同样不能被打入 触发器% 数据稳定传输必 须满足建立时间和保持时 间的要求" 否则电路就会 出现逻辑错误% 建立保持 时间时序图如图 A 所示% 例如"从 " 触发器的 # 输出端直 接 馈 给 另 一 触 发 器

图 ! 接 " 触发器后仿真结果

数据

! >?

时钟

!@

图 O 建立保持时间时序图

集成电路应用

!"#$ 设计中关键问题的研究

陕 西 省 西 安 电 子 科 技 大 学 综 合 业 务 网 国 家 重 点 实 验 室 ! N<77N< " 李 刚 强 田 斌 易 克 初

要 ! 介 绍 了 Z;*H 的 一 般 设 计 流 程 " 指 出 了 Z;*H 设 计 中 的 几 个 重 点 # 难 点 问 题 $ 主 要 包 括 时 钟设计%延时设计和同步设计中遇到的问题以及电路中毛刺信号的产生机理和消除 "结合作者的经 验和体会&分析了问题产生的原因并给出解决方案和相关设计技巧’ 关 键 词 ! Z;*H 时钟设计 同步设计 延时设计 毛刺消除 摘

电 路 模 块

!"#"$ 多 时 钟 系 统

许 多 应 用 要 求 在 同 一 个 #%&’ 内 采 用 多 个 时 钟 ! 比 如两个异步微处理器之间的接口或微处理器和异步通信 通道的接口" 由于两个时钟信号之间要求一定的建立和 保 持 时 间 !所 以 引 进 了 附 加 的 定 时 约 束 条 件 !将 某 些 异 步 信号同步化" 在许多系统中只将异步信号同步化是不够 的 !当系统中有两个或两个以 上 非 同 源 时 钟 的 时 候 !数 据 的建立和保持时间很难得到保证! 最好的解决办法是将 所 有 非 同 源 时 钟 同 步 化 " 使 用 #%&’ 内 部 的 锁 相 环 # %(( $ 模 块 是 一 个 很 好 的 方 法 % 如 果 不 用 %(( ! 当 两 个 时 钟的频率比是整数时!同步的 方 法 比 较 简 单 &当 两 个 时 钟 的频率比不为整数时!处理方法要复杂得 多% 这时需要使 用 带 使 能 端 的 " 触 发 器 !并 引 入 一 个 高 频 时 钟 来 实 现 %

线路的尖峰毛刺造成FPGA工作不正常

企业规范用工情况汇报尊敬的领导:根据公司要求,我对企业规范用工情况进行了汇报。

在过去的一段时间里,我们对企业规范用工情况进行了全面的调查和分析,现将情况汇报如下:一、用工结构情况我们公司目前共有员工XXX人,其中男性XXX人,女性XXX人。

在不同部门中,用工结构相对合理,各部门员工数量与工作需求基本匹配。

二、用工合同情况全公司员工的用工合同均已签订,合同期限和内容合乎法律规定,保障了员工的合法权益。

同时,公司也严格执行用工合同管理制度,确保用工合同的有效性和稳定性。

三、工资福利情况公司严格按照国家相关法律法规执行工资福利政策,确保员工的工资福利待遇合理、公平。

同时,公司还为员工提供了完善的社会保险和福利待遇,包括医疗保险、养老保险等,保障员工的基本生活需求。

四、劳动保护情况公司重视员工的劳动保护工作,建立了完善的安全生产管理制度,定期进行安全生产培训和演练,确保员工的人身安全。

同时,公司还加强了对员工的职业健康管理,定期进行体检,确保员工的身体健康。

五、员工培训情况公司注重员工的培训和提升,定期组织各类培训活动,提高员工的专业技能和综合素质。

同时,公司还鼓励员工参加外部培训和学习,提升员工的个人能力。

六、用工管理情况公司建立了完善的用工管理制度,严格执行各项规章制度,加强对员工的管理和监督。

同时,公司还加强了对员工的考核评价工作,激励员工的工作积极性和创造性。

七、用工风险防范情况公司加强了对用工风险的防范工作,建立了健全的风险评估和预警机制,及时发现和解决用工风险问题,确保公司用工的稳定和安全。

综上所述,公司的企业规范用工情况良好,各项工作得到了有效落实和执行。

但在日常管理中,我们也发现了一些问题和不足,下一步将进一步加强对企业规范用工情况的监管和管理,确保用工工作的规范和稳定。

谨此汇报,如有不足之处,敬请领导批评指正。

FPGA毛刺产生的原因及其抑制方法

FPGA毛刺产生的原因及其抑制方法作者:孙晓东, SUN Xiaodong作者单位:唐山电视发射台,唐山,063000刊名:电脑编程技巧与维护英文刊名:COMPUTER PROGRAMMING SKILLS & MAINTENANCE年,卷(期):2010,""(14)被引用次数:0次1.徐志军CPLD/FPGA的开发与运用2.褚振勇.翁木云FPGA设计及应用1.期刊论文曾宏布线后修复时序违规的方法研究-中国集成电路2010,19(4)90/65nm下后端设计中由于多模式-角落,以及布局布线工具和签收工具之间的误差性,布线后修复各种时序违规如渡越时间、负载、建立时间、保持时间、串扰等将是一项十分耗时的工作.如何快速修复各种违规,取得设计收敛是后端设计者所关注的.本丈分析了各种情况,提供了一些解决方案.2.期刊论文谢红筝设计高速数字电路应关注的问题及解决方法-中国科技博览2010,""(18)在高速数字电路的设计中,时序设计、信号完整性等是关乎系统性能的重要标志.在高速数字电路设计中较难把握,但在理解电路时序模型的基础上,采用合理的设计方法是行之有效的,通过许多设计实例证明采用这些方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平.3.期刊论文刘一平.叶媲舟.凌朝东.LIU Yi-ping.YE Pi-zhou.LING Chao-dong FPGA的可靠时钟设计方案-华侨大学学报(自然科学版)2009,30(6)对于现场可编程门阵列(FPGA)常见的6种时钟设计,根据建立时间和保持时间的要求,按照同步设计原则,分别给出可靠的时钟设计方案.利用这些方案来设计FPGA的时钟,可以更容易完成FPGA的项目设计,使得FPGA系统更稳定、更可靠.4.期刊论文王慧.Wang Hui一种借助时序检测系统进行时序验证的方法-信息安全与通信保密2007,""(1)论文介绍了在集成电路时序验证阶段如何借助时序检测系统对集成电路端口信号的建立时间和保持时间进行检测.5.期刊论文王海鹏.曾爱凤.Wang Haipeng.Zeng Aifeng基于公共时钟同步的系统时序分析与控制-电子测量技术2010,33(8)随着系统时钟频率不断提高,时序在高速数字系统设计中越来越复杂.为保证系统能正常稳定工作,必须在PCB设计之初就进行精确的时序分析和控制;同时信号完整性问题对时序的影响越来越严重,信号完整性问题需在时序设计的同时解决.对公共时钟同步系统的时序进行了详细的分析,并针对一嵌入式系统,采用Cadence 仿真工具SPECCTRAQuest进行信号完整性仿真优化及时序分析计算,得出了控制系统工作时序的约束.这一设计方法也适用于其他高速数字系统的时序设计.6.期刊论文陈俊.周正中.CHEN Jun.ZHOU Zheng-zhong高速、高精度频率采样中的量化误差分析-电子科技大学学报2007,36(1)讨论了高速、高精度频率采样的基本原理;分析了量化噪声对测量误差的影响;提出了采样器建立和保持时间对测量误差影响的问题;导出了考虑采样器建立和保持时间后时间量化误差的概率密度函数,为量化误差的校正奠定了理论基础.7.期刊论文杨波.高德远RTL电路的时序优化设计-小型微型计算机系统2001,22(9)时序设计是数字系统性能的关键,在高层设计方法中对时序的控制进一步抽象,我们在介绍电路时钟和时序的基础上分析了RTL电路的时序模型,该模型讨论了RTL电路的时延路径、建立保持时间以及系统正常工作的条件,并据此提出了相应的设计策略,通过实践证明这种设计方法是行之有效的.8.学位论文钱立旺0.6μm CMOS 622Mb/s高速分接器设计2004分接器是光纤通信网中的关键器件.它位于光纤接收机的末端,将接收到的一路高速信号重新恢复成多路的低速信号.该文简要介绍了分接器的实现工艺和设计流程,以及复接和分接的原理.分接器有三种主要结构:串型结构、并型结构和树型结构,该文分析了三种结构的工作原理及其优缺点.根据三种结构的各自特点和设计目标,选用树型结构作为分接器的基本结构.电路设计是分接器设计的基础.速度、功耗、面积是电路设计要考虑的主要因素,不同的电路形式具有不同的优缺点,如CMOS互补逻辑电路功耗低,面积小,速度相对较慢;SCFL(源极耦合FET逻辑)电路速度高,功耗和面积较大.所以要针对具体设计需要选用适当的电路形式或其组合结构,以满足设计要求.触发器是分接器的基本组成单元,建立时间和保持时间是影响电路速度的关键,所以减小建立时间和保持时间是触发器设计的主要目标,该文着重介绍了SCFL锁存器的设计和优化方法.该文介绍了分接器的版图设计考虑,并给出了仿真结果和芯片的晶圆级测试结果,并对测试结果进行了分析.该文设计的1:4分接器采用CSMC-HJ 0.6μmCMOS工艺实现,测试结果表明,芯片成功的实现了SDHSTM-4级别1:4分接器的功能,最高分接速率可达622Mb/s.9.期刊论文李胜朝.张江鑫.LI Sheng-chao.ZHANG Jiang-xing高速电路中时序问题的分析与处理-浙江工业大学学报2009,37(5)高速电路中信号完整性现象正变得越来越普遍,而时序问题又是信号完整性现象中最为关键的一个问题,所以时序分析及仿真对保证高速PCB设计的质量十分必要.文章从理论上分析了一个高速信号系统中时钟线与数据线之间正确读写所需满足的时序关系.采用Specctraquest工具分析处理了一个实例中的时序问题,并从中得出了进行时序系统设计时所必需遵循的准则.实验结果验证了运用Specctraquest工具处理时序问题的高效性和实用性,具有非常大的推广价值.10.学位论文陈智荣大屏幕TFT-LCD源极驱动器数据输入接口设计2007TFT-LCD已成为信息时代显示技术的主流。

高效能FPGA毛刺PUF设计与实现

第29卷第6期计算机辅助设计与图形学学报Vol. 29 No.6 2017年6月Journal of Computer-Aided Design & Computer Graphics Jun. 2017高效能FPGA毛刺PUF设计与实现庞子涵1,2), 周强2)*, 高文超1), 郭世一1), 钱旭1)1) (中国矿业大学(北京)机电与信息工程学院北京 100083)2) (清华大学计算机与科学技术系北京 100084)(zhouqiang@)摘要: 物理不可克隆函数(PUF)因其特有的唯一性和不可克隆性, 在诸多硬件安全领域有广泛应用前景. 针对仲裁器PUF和环形振荡器PUF硬件资源消耗大的弱点, 在毛刺PUF设计架构基础上, 充分利用FPGA中双路选择器转换时延和片(Slice)间配置开关矩阵特性, 提出一种高资源利用率的毛刺PUF电路设计方法. 根据可编程逻辑块(CLB)所含的不同类型Slice分别设计相应的布局布线方案, 通过改变双路选择器的输入状态和调整开关矩阵中路径分配的策略控制到达双路选择器的时延差, 确保产生的“毛刺”信号具有PUF特性. 该方法不仅将单位CLB输出响应最高提升至2比特, 还可以做到芯片Slice资源100%利用率. 实验结果表明, 利用Xilinx公司Virtex-5芯片实现128比特输出, 在保持原有的较高唯一性(49.61%)的前提下, 错误率降至2.51%; 较原有毛刺PUF设计在稳定性、芯片兼容性和硬件资源使用率方面都有显著提升.关键词:物理不可克隆函数; 硬件安全; 毛刺PUF中图法分类号:TP391.41Design and Implementation of High Efficiency PUF Circuit on FPGAPang Zihan1,2), Zhou Qiang2)*, Gao Wenchao1), Guo Shiyi1), and Qian Xu1)1) (School of Mechanical Electronic & Information Engineering, China University of Mining & Technology (Beijing),Beijing 100083)2) (Department of Computer Science and Technology, Tsinghua University,Beijing 100084)Abstract: Physical unclonable function (PUF) has an extensive prospect in hardware security applications for its unique and non-cloning characteristics. Motivated by the glitch PUF design architecture which uses the delay characteristics of multiplexer and switch matrix, this paper presents a type of high efficiency glitches PUF circuit design. By changing the input state of multiplexer and the distribution of the switching matrix, the switching latency of the multiplexer can be adjusted to ensure that the ʻglitchʼ signal has PUF characteristics. Compared to the large resource consumption of arbiter PUF and ring oscillator PUF, this de-sign increases a single CLB output to two bits and makes Slice resources utilization up to 100%. Experi-mental results show that the error rate decreases to 2.51% on the condition of maintaining the original high uniqueness (49.61%) when generating 128-bit outputs with Xilinxʼs Virtex-5 devices. And the compatibility and overhead are significantly improved.Key words: physical unclonable function; hardware security; glitch PUF收稿日期: 2016-09-13; 修回日期: 2017-01-04. 基金项目: 国家自然科学基金(61176035). 庞子涵(1989—), 男, 博士研究生, 主要研究方向为计算机硬件安全、物理不可克隆函数; 周 强(1961—), 男, 博士, 教授, 博士生导师, CCF高级会员, 论文通讯作者, 主要研究方向为系统集成、设计自动化和三维芯片设计; 高文超(1986—), 女, 博士, 讲师, CCF会员, 主要研究方向为集成电路布局算法; 郭世一(1987—), 男, 博士研究生, 主要研究方向为轻量级密钥加密算法; 钱 旭(1962—), 男, 博士, 教授, 博士生导师, 主要研究方向为数据融合.1136 计算机辅助设计与图形学学报第29卷伴随着数字集成电路的高速发展, 各种智能终端和交互设备融入到互联网中, 使得整个信息系统更加智能和便捷. 但随之带来的信息安全问题却经常被忽视, 由于智能硬件的普及以及使用环境的多样性和复杂性, 导致整个系统的风险抵御能力更加脆弱. 从硬件的生产加工到最后的购买使用, 各个环节都有可能受到监听、伪造和篡改等威胁[1]. 物理不可克隆函数(physical unclonable function, PUF)这一概念的提出, 正是利用集成电路在生产过程中的工艺特性, 每一个逻辑门电路的阈值电压以及氧化层厚度都不尽相同, 导致在相同条件下生产的芯片在物理构造之间具有不可避免的随机差异. 该随机差异具有唯一性和不可克隆性, 可以作为硬件的唯一标志来进行认证[2]. 目前, 在知识产权保护[3]、权限认证与管理[4-5]、密钥生成[6]等诸多领域, PUF技术有着更广泛的应用.现场可编程门阵列(field-programmable gate array, FPGA)在嵌入式应用当中扮演着重要角色, 它可以根据用户需要进行配置和编程, 具有丰富的逻辑资源以及可以反复擦写的极高灵活性, 使得其在信息处理、通讯以及逻辑控制等诸多领域具有广泛的应用前景[7]. 但是, 基于FPGA相关应用正在受到各种新兴攻击手段的威胁, 自身的安全性和稳定性问题受到极大关注. 利用FPGA实现PUF设计, 可以在增加极少的硬件开销前提下增强自身的安全保障, 不仅可以保护FPGA开发者的知识产权、有效防止伪造和篡改, 还可以应用到保密通信等诸多安全领域.作为FPGA PUF中一种重要的、基于时延的PUF电路结构, 毛刺PUF就是利用制造工艺特性产生的路径时延差异, 在信号电平发生变化瞬间, 不同逻辑门输出不同步容易产生异常的尖峰信号, 即“毛刺”. 毛刺信号出现的可能性受到路径时延差异的影响, 具有一定的随机性. 唯一性和稳定性是评价PUF性能的2个重要指标, 唯一性体现的是不同PUF在相同激励条件下产生的响应异同的概率, 越接近50%表明差异分布更加均匀, 具有更好的唯一性. 而稳定性则评估PUF在不同环境影响中相同激励条件下响应不发生变化的概率, 理想状态下该值应为100%. 现有的毛刺PUF电路结构虽然在唯一性方面能够接近50%, 但是稳定性上却只能达到96.8%, 并且实现的架构在硬件兼容性方面还有很多限制. 针对上述问题, 本文提出了一种高效能的毛刺PUF电路设计方法. 利用双路选择器转换时延差异设计出能够产生“毛刺”信号的冒险电路, 并通过配置开关矩阵中的路径分配控制和调整到达双路选择器的时延, 来保证响应具有良好唯一性, 在此基础上增强对温度变化的稳定性; 在提高硬件资源利用率的同时, 解决了硬件兼容性的问题.本文首先对基于FPGA PUF架构实现的相关研究工作进行论述, 并简要分析主流架构的特性; 然后从实现原理方面分析高效能毛刺PUF电路设计模型, 并详细阐述硬件电路布局布线方法; 最后给出该PUF电路主要性能测试与对比结果.1相关工作PUF概念由Pappu等[8]在2002年首次提出, 主要分为电子PUF和非电子PUF 2大类; 其中典型的非电子PUF包括光学PUF、纸PUF和CD PUF. 最早Pappu等提出的就是光学PUF, 其利用激光照射随机掺杂光散射粒子的小光透明令牌, 获得一个散斑图像, 经过滤波器之后再进行提取. 同样, 纸PUF[9]和CD PUF[10]都是利用光通过不规则的物理结构得到的散射图像作为防止伪造的“指纹”.电子PUF按照实现原理可分为模拟电路PUF, 基于存储的PUF和基于时延的PUF 3类. 模拟电子PUF以涂层PUF[11]为代表, 其将集成电路板喷上含有随机介质颗粒的特殊涂层, 利用集成电路顶部金属层上的电容式传感器, 得到由介质导致的随机电容测量结果, 并将其作为涂层PUF响应输出. 其他的模拟电路PUF包括类似于涂层PUF 的概念——LC-PUF[12]. Lofstrom等[13]通过芯片上的模拟测量电路直接测量MODFET的阈值电压变化来实现一个PUF的功能. Helinski等[14]介绍了一种基于电阻值来识别一个IC电源分配系统的方法.基于存储的PUF电路主要由2个逻辑稳定但状态不同的逻辑单元构成, 在上电或者复位时会通过竞争达到一种稳定状态. SRAM PUF[15]中6个晶体管构成交叉耦合存储单元, 在上电时该结构处于不稳定状态, 任何微小的电压变化都会造成输出状态向0或1的稳定状态转化. 由于在FPGA 中一些公司加入的强制复位的机制, 使得SRAM PUF不具有普适性. Kumar等[16]将SRAM PUF结构中的反向器替换为触发器, 提出了蝴蝶PUF这个概念; 该输出状态由激励信号传播时延和反馈路径时延2个因素决定, 不需要必须在上电时完成第6期庞子涵, 等: 高效能FPGA毛刺PUF设计与实现 1137测量, 因此避免了FPGA中上电强制清零的问题, 适用于所有类型FPGA.基于时延的PUF电路利用信号传送延迟的变化实现, 分为基于仲裁器的PUF、基于环形震荡的PUF和毛刺PUF 3类. Lim等[17]首次提出如图1所示的基于仲裁器PUF设计模型, 两路含有n个信号传播路径的单元首位相连, 共享相同输入, 输出端分别连接仲裁器D触发器的信号输入端和时钟输入端, 在第i级信号传播路径的单元中, 激励信号C[i]可以选择平行通路或交叉通路, 以此改变路径时延. 当输入端产生一个上升沿信号后, D触发器中如果连接信号输入端先到达则输出逻辑1, 反之时钟信号端会将输出锁定为逻辑0. 该PUF结构对两条路径的对称性要求非常高, 因此在FPGA中实现较为复杂. Majzoobi等[18]提出可编程时延线(programmable delay line, PDL)的概念. 利用FPGA 中查找表(lookup-table, LUT)结构的特性, 将数个LUT级联以控制的时延, 进一步抵消仲裁器内部延迟差所带来的影响. Gu等[19-20]则充分利用LUT 资源, 采用RS锁存器作为仲裁器, 测量2个D触发器的时延, 以提高硬件使用效率.图1 仲裁器PUF电路结构基于环形振荡器(ring oscillator, RO)的PUF电路由Suh等[21]在2007年首次提出, 其利用若干个反向器相连成环, 产生一个固定频率的振荡信号; 其振荡频率受到反向器内部时延和连接线时延影响, 具有一定的随机性和不可预测性, 它通过比较两路RO信号频率值输出2种状态: 逻辑0或者逻辑1. 图2所示电路中有N组RO电路, 可以产生平均N log N 比特的信息. 近期在消除系统性误差、提高随机性上有不少改进方法, 但是在硬件资源利用上, RO PUF平均输入1比特信息所消耗的资源比仲裁器PUF多, 且对布局布线有较高要求, 因此其不适用于轻量级PUF 设计.毛刺PUF由Suzuki等[22]利用路径时延差异设计的另一种架构PUF电路. Anderson[23]专门针对FPGA的结构特点提出对应的毛刺PUF模型, 利用状态转换的时延差产生脉冲信号, 通过检测有无脉冲信号或者宽度作为输出结果, 第2节将详细论述其实现原理. 相比上述2种PUF, 毛刺PUF不需要对称性要求, 并且利用FPGA单元中固有结构, 不需要额外的布局布线约束, 在稳定性和随机性上都具有优势.图2 带有激励响应模式的RO PUF电路结构2高效能毛刺PUF设计与实现2.1 毛刺PUF基本原理毛刺PUF的本质就是利用电路时延的差异导致在信号输出时产生毛刺信号. 该信号的产生是由多个路径时延共同决定, 因此受环境因素影响波动较小. 图3所示为Anderson设计的毛刺PUF 模型. 选取SliceM中的2个查找表A与B并设置成移位寄存器(shift register, SR)模式, LUT A初始化值设置为0x5555, LUT B设置为0xAAAA, LUT A与LUT B共用时钟信号, 数据输入端应和时钟信号振荡频率一致, 以确保2个SR输出信号在0和1之间稳定振荡. SR输出连接快速进位链中双路选择器的信号选择端, 双路选择器0输入端连接逻辑0, 底部双路选择器1输入端连接逻辑1, 输出的信号N1与顶部双路选择器的1输入端相连.图3 Anderson PUF电路结构理想状态下, 当LUT A输出由0变为1时, N2应输出N1的值, 此时LUT B由1转变为0, N1输出0, 则N2也输出0; 当LUT A输出由1变回0时, N2输出也是0, 因此在不考虑任何时延的情况下, N21138 计算机辅助设计与图形学学报第29卷始终保持逻辑0输出. 但是在实际情况中, LUT A 与LUT B以及2个双路选择器的时延并不完全相同, 由于不可避免的工艺偏差导致其完成状态转换所用时间有所差异. 考虑下述2种情况: 1) 如果连接LUT A的顶层双路选择器转换比底层选择器时延短, 当LUT A输出由逻辑0变为逻辑1时, LUT B连接的底层双路选择器还未完成由逻辑1变为逻辑0的转换, 此时N1端仍保持为逻辑1, 因此N2会输出1, 等底层选择器完成转换之后N1和N2会恢复为逻辑0. 2) 当底层选择器比顶层选择器时延短, LUT B从逻辑0转变为逻辑1时, N1会输出逻辑1, 而此时顶层选择器还未完成转换, N2仍输出N1的值, 即逻辑1; 只有当顶层选择器完成转换之后, N2才能恢复为逻辑0. 2种情况下N2输出端会形成一个脉冲信号, Anderson[23]利用触发器, 采用异步置位模式将N2连接至PRE端, 输出端Q 将信号反馈至输入端D, 其初始值为0. 如果N2端有脉冲信号产生, 触发器输出将恒定为逻辑1; 否则将保持逻辑0不变.SR A和相连的双路选择器, 与SR B和相连的双路选择器之间的时延差决定了N2输出端是否会出现脉冲信号以及脉冲信号的宽度. 时延差越小, 脉冲信号出现的概率也越小; 而在出现脉冲信号的前提下, 时延差越大, 脉冲信号的宽度也越大. 检测脉冲信号采用的是异步置位的触发器, 如果N2产生的脉冲信号过窄, 极有可能在到达置位端之前就被“过滤”掉. 之所以产生该现象是因为路径中存在的电阻和电容对脉冲信号形成衰减作用. 因此, 在毛刺PUF电路设计时, 需要确保脉冲信号在一个合适的范围之内, 不能过窄被衰减过滤, 也不能过宽导致绝大部分触发器输出1而失去随机性. N1信号端的时延可以通过增减双路选择器进行控制, 甚至可以采用多个Slice串联实现(此时双路选择器个数大于4). Anderson[23]通过实验发现, 采用7个双路选择器时能获得更加均匀的状态分布. LUT A处于上层Slice中的顶层位置, LUT B处于下层Slice中的第3层. 上下2层Slice中的双路选择器互联采用专用连线, 避免了采用互联矩阵导致加入过多时延. 而LUT A与LUT B之间的双路选择器统一输入逻辑1, 确保了N2输出端能够产生脉冲信号.架构中LUT A与LUT B直连的双路选择器, 其逻辑0输入端分别通过DX和BX端口输入逻辑0实现, 以确保整个架构仅用2个Slice就可实现. 然而在新一代的Xilinx FPGA芯片中(包括Virtex-7系列, Kintex-7 系列和Zynq-7000 系列等), 由于与Anderson[23]采用的Virtex-5系列在结构上的差异, 导致Anderson提出的PUF结构不能直接套用. Zhang等[24-25]利用CLB结构特性, 采用4个Slice 实现图4所示的毛刺PUF电路结构, 其中2个SliceM负责实现原结构中LUT A与LUT B的功能, 剩余2个SliceL实现双路选择器级联的设计, 而触发器可有8个位置随机选择. 实验采用Zynq-7000 XC7Z020 FPGA, 将芯片分为16个区域, 每个区域产生64比特数据. 唯一性方面平均汉明距离为31.75(输出宽度的49.6%), 稳定性方面分别测量40℃和70℃时生成的数据, 其平均汉明距离为2.38(输出宽度的3.7%). Huang等[26]和Barbareschi 等[27]则是从实现激励响应对的思路出发, 对LUT B部分进行如图5所示的改造, 激励信号连接2个双路选择器来实现对LUT A和LUT B间时延控制.Anderson实现毛刺PUF架构采用的是Xilinx 公司的Virtex-5芯片. 依据SliceM结构特点, 利用LUT和双路选择器状态转换的时延实现, 从图4所示图4 Zhang等PUF电路结构第6期庞子涵, 等: 高效能FPGA毛刺PUF设计与实现 1139图5 “激励响应”模式毛刺PUF电路结构Slice内部架构分析, 加法进位链中的每一个双路选择器都由一个LUT输出进行控制, 双路选择器纵向互联, 以实现快速加法运算, 每一个双路选择器的输出作为上一级的状态1输入; 而Slice中进位链最顶层的双路选择器又与上一级Slice中进位链底层的双路选择器相连. Anderson[23]正是利用多个双路选择器串联的结构对时延加以控制, 以保证输出响应均匀分布.在上述基于FPGA的毛刺PUF结构中, LUT A 与LUB B采用的是SR模式, 只有SliceM满足条件. 以Xilinx公司的芯片为例, SliceM与SliceL的比例介于1:2到1:4之间, 虽然在Virtex-5芯片中大约18000个SliceM, 但却有50000多个SliceL 不能使用, 而Zhang等[24-25]方法在输出同样比特的数据时却要多花费一倍的资源, 造成资源使用率不高.2.2高效能毛刺PUF电路模型分析在上节描述的毛刺PUF结构中, 为了确保PUF电路输出响应的均匀分布特性, 需要保证2个LUT连接的双路选择器之间插入4~6个额外的双路选择器. 虽然理论上并入链路中的双路选择器个数可随意增减, 但是每个Slice中的双路选择器个数为固定值, 个数的增加意味着更多硬件资源消耗, 而对应生成的比特数并没有改变. 因此, 在保证生成比特均匀性和随机性的前提下, 应尽量减少并入链路中的双路选择器的个数. 根据上节的论述, 时延链路中双路选择器的减少会导致顶层和底层双路选择器的转换时延差变小, 从而导致N2端的脉冲信号宽度变窄, 更加容易被衰减或过滤, 所以输出响应中逻辑0的状态会明显增多. 另外SliceL中的LUT不能设置为寄存器模式, 它不适用于上述结构. 如何既能充分利用芯片中所有的硬件资源, 又可以保证输出响应的随机性, 是下一步重点解决的问题.本文提出的PUF电路模型如图6所示, 此时LUT A和LUT B均为普通查找表模式, 输出端与输入端状态一致, 只需保证2个LUT输出的状态相异即可. LUT依旧与双路选择器相连, 与之前架构的区别在于, 2个双路选择器的0状态输入端分别与各自LUT输出端相连接.图6 高效能毛刺PUF电路结构针对原有电路单一、利用状态转换时延差异导致硬件资源利用率不高的问题, 本文设计的电路结构利用双路选择器状态转换时延差, 以及0输入端到输出端时延与状态转换时延的差异, 提高了PUF电路的灵活性. 从双路选择器状态转换时延开始分析: 1) 假设顶层双路选择器转换时延快于底层双路选择器, 如果0状态输入端到输出端时延快于状态转换时延, 当LUT A输出由逻辑0变为逻辑1、输出端N2在顶层选择器状态未完全转换时, 首先输出0输入端的状态, 即逻辑1; 转换完成之后, 1输入端状态此时也为逻辑1, 只有当底层双路选择器完成状态转换时才恢复为逻辑0. 反之, 如果0状态输入端到输出端时延慢于状态转换时延、LUT A输出由逻辑1变为逻辑0时, 由于顶层双路选择器完成状态转换时, 逻辑0输入端依旧保持逻辑1的状态, 因此N2会输出逻辑1, 直到0状态到达顶层双路选择器的输出端. 2) 假设底层双路选择器转换时延快于顶层双路选择器, 如果0状态输入端到输出端时延快于状态转换时延、当LUT B 输出由逻辑0变为逻辑1时, 从底层双路选择器输出端N1变为逻辑1开始, N2端一直保持逻辑1状态输出, 直到顶层双路选择器完成转换. 相比于现有的毛刺PUF电路结构, 该电路设计充分利用状态输出的时延差异, 增加了N2输出端产生逻辑状态1的可能性, 使得减少并入链路中的双路选择器个数成为可能.2.3高效能毛刺PUF电路结构实现针对原有毛刺PUF电路设计在现有FPGA芯片1140计算机辅助设计与图形学学报 第29卷实现时都会遇到可用CLB 资源受限的问题, 本节充分利用CLB 内部的可配置开关矩阵(switch ma-trix), 通过限制约束每个CLB 的相对物理位置, 设计并实现了高效能毛刺PUF 电路布局方案.Xilinx FPGA 芯片中, CLB 由SliceM 和SliceL 或者只有SliceL 构成. 可配置开关矩阵作为FPGA 中各种单元的沟通桥梁, 承载着电信号传递和分发的任务, 其任意2个端口都可以建立互联关系, 以满足FPGA 对电路灵活定制的要求. 同样, 可配置开关矩阵中布线路径的差异也会影响线路的时延, 即使是2个可配置开关矩阵中相同位置的2组端口互相连接, 2条路径长度也会有所不同, 导致两路信号具有时延差[28]. 根据高效能毛刺PUF 电路模型原理, 可配置开关矩阵的时延差异会直接影响2个LUT 输入端信号转换的同步性, 其解决方法就是调整2个LUT 连接的双路选择器之间插入的双路选择器的个数, 以确保该毛刺PUF 电路输出响应的均匀分布. 与此同时根据CLB 所包含的资源类型差异, 分类设计不同的布局方案, 在保证输出响应具有唯一性和均匀性的前提下, 实现可利用资源数最大化的目标.当CLB 中同时含有SliceM 和SliceL 时, 布线方案如图7所示. 将SliceM 中最顶端LUT 和第2层LUT 设置为SR 模式, 为方便叙述, 分别标号为SR A 和SR B . SR A 初始化值设置为0x5555, SR B 设置为0xAAAA, SR 输出信号不仅连接双路选择器的状态选择输入端, 还通过输出端口与可配置开关矩阵相连. 图8所示为利用FPGA 工具查看SliceM图7 含SliceM 与SliceL 的CLB 布线图图8 SliceM 中SR A 实际布线图中SR A 的实际布线图, 可以看到, SR A 在O 6端口通过端口D 将信号传递到SliceM 外部, SR B 与SR A 类似通过端口B 进行输出. 其他SliceL 则通过可配置开关矩阵获得2个SR 的激励信号, 实现如图6所示的电路结构. CLB 中的SliceL 在获得激励信号之后, SR A 路信号通过顶端LUT 连接双路选择器和0状态输入端, 而SR B 则依照相同的方法在第3层LUT 和双路选择器中进行连接配置. 只含有SliceL 的CLB 布线方案如图9所示, 该结构中含有2个CLB 共4个SliceL, 从可配置开关矩阵中获得SR A 和SR B 信号, SR A 信号分别接入底层CLB 中2个SliceL 的第3层LUT, 而SR B 则接入顶层CLB 中2个SliceL 中的顶层LUT. 图10所示为利用FPGA 工具查看SliceL 中的实际布线图, LUT 的2个输出端O 6和O 5分别接入双路选择器图9 只含SliceL 的CLB 布线图第6期庞子涵, 等: 高效能FPGA 毛刺PUF 设计与实现 1141和状态0的输入端.由于SR A 和SR B 信号在可配置开关矩阵中布线路径长度的差异, 导致SliceL 得到的两路信号存在时延差. 为了减少对毛刺PUF 电路随机性的影响, 通过调整CLB 之间的相对位置来保证输出响应更加均匀分布. 通过FPGA Editor 可观察到图11所示SR A 和SR B 实际布线路径, 图中蓝色填充的矩形代表Slice, 黑色矩形框为可配置开关矩阵. 假设SliceM 的位置为X i Y j , 则针对同时含有SliceM 和SliceL 的CLB, 对应的SliceL 的位置为X i +1Y j . 如果CLB 中只含有SliceL, 则4个SliceL 的位置分别是X i +2Y j +1, X i +3Y j +1, X i +2Y j +2和X i +3Y j +2.图10 SliceL 中LUT 实际布线图a. SR Ab. SR B图11 SR A 和SR B 在可配置开关矩阵中的布线路径3 实验测试与对照分析本文采用64个实例用来生成128比特数据. 实验平台采用Xilinx 公司的XUPV5-LX110T 开发板, 采用开发板自带的27MHz 时钟信号, 利用RS-232串口与计算机之间传输数据. 在比较芯片间PUF 输出差异时, 一般认为2个芯片之间的差异应比同一芯片不同区域之间差异大, 如果同一芯片不同区域PUF 输出差异较大, 那么有理由相信芯片间具有唯一性. 本文采用4个Virtex-5 FPGA 芯片, 将同一芯片按照3行2列划分为6个区域, 每个区域生成一组128比特PUF 数据, 因此共生成24组PUF 数据.3.1 硬件资源使用效率生成128比特PUF 响应数据的条件下, An- derson PUF 需要256个SliceM, 占Virtex-5 FPGA 芯片(XUPV5-LX110T 含17 280个Slice) 的1.48%,而本文设计的PUF 结构需要192个Slice(32个SliceM 和160个SliceL), 占比为1.11%. 同样在新一代Xilinx FPGA 芯片的环境中, Zhang 等[24-25]设计的PUF 结构需要512个Slice(256个SliceM 和256个SliceL), 占Zynq-7000 XC7Z020 (含有13 300个Slice)的 3.85%, 本文设计的PUF 结构则占比为1.44%. 值得注意的是, 由于芯片中SliceM 和SliceL 的个数比通常为1:3, 因此Anderson PUF 和Zhang PUF 由于过多使用SliceM, 导致部分SliceL 无法充分利用, 难以实现100%的硬件使用率; 而本文的毛刺PUF 电路设计利用SliceM 和SliceL 的比例介于1:1至1:5之间, 完全可以满足100%硬件使用率的目标.3.2 唯一性通过测量相同激励下不同电路产生响应比特间的汉明距离, 检验该PUF 结构是否具有唯一性[25]. k 组n 比特PUF 数据的平均汉明距离计算公式为111(,)2100%.(1)k k i j i j i D P P u k k n -==+=⨯-∑∑其中, ,,1(,)()ni j i m j m m D P P r r ==⊕∑,,i m r 表示n 比特响应i P 的第m 位比特信息. 24组PUF 共生成(24×23)/2=276组结果, 对应的概率统计直方图如图12所示. 其中最小与最大的汉明距离分别为44和80, 所有276组数据的平均值为63.5(128比特的49.61%), 与理想状态值64非常接近. 从图12所示直方图中可看出, 数据近似于高斯分布, 最大值靠近输出位数的一半即64. 图13所示为本方法与上1142计算机辅助设计与图形学学报 第29卷一节论述的2种毛刺PUF 方法在不同温度条件下响应比特间汉明距离对比, 可以看到, 采用本文所述的毛刺PUF 结构所产生的响应比特在多个温度环境中都更接近理想数值0.5, 进一步证明该PUF 架构具有很好的唯一性.图12 片间汉明距离密度分布图图13 3种方法不同温度唯一性对比3.3 稳定性采用完全相同配置, 通过在多次重复实验中是否能够保持相同输出来衡量其稳定性. 如果在大量重复实验生成的响应比特间差距越小, 说明该PUF 结构具有很好的稳定性. 响应比特间差距通常采用计算汉明距离来表征[25], 具体计算公式为,1(,)1100%.x i i y D R R r x n =⨯∑其中, ,(,)i i y D R R 表示原始响应i R 和第y 次测试的输出响应,i y R 之间的汉明距离; x 表示测试的总次数. 对24组PUF 进行2次实验, 之间的时间间隔为14天. 通过测量2次生成比特间的汉明距离, 分析该PUF 结构在时间变化方面的稳定性, 对应的概率统计直方图如图14所示. 汉明距离分布区间为0~5, 平均值为1.89(128比特的1.48%). 综合对照图12可以看到, 在6~40区间无数据, 说明片内汉明距离与片间汉明距离不重叠, 可以选择空白区间内的任意一处作为阈值进行无差错认证.图14 不同时间下片内汉明距离密度分布图在温度影响测试方面, 分别测量同一芯片在不同温度下生成的响应比特, 计算两者间的汉明距离作为温度稳定性的衡量标准. 利用Xilinx 公司提供的Chip-Scope 工具可以观察芯片实时温度. 在室温20℃条件下芯片正常运行温度为40℃左右, 利用恒温箱将芯片温度提高到70℃模拟高负荷环境. 2个温度条件下PUF 生成数据间的汉明距离概率直方图如图15所示, 平均值为3.21(128比特的2.51%), 分布区间为0~8. 以图12为参照, 虽然温度对芯片的影响更大, 但是无差错认证阈值依然可在11~40区间内选择. 同样在10℃~70℃区间内, 以10℃为间隔, 分别测量每个温度下电路生成的响应比特并与40℃时响应比特进行对比(40℃时采用连续2次生成响应进行对比), 如图16所示, 本文方法在不同温度环境下的稳定性都优于前文章节论述的2种毛刺PUF 方法.表1所示为本文设计实现的毛刺PUF 电路与文中介绍的其他类型PUF 在性能表现方面的对比.图15 不同温度下片内汉明距离密度分布图。

电路设计中的毛刺问题的研究

FPGA电路设计中的毛刺问题的研究目录1 引言 (1)2 FPGA的相关概念.................................. 错误!未定义书签。

2.1 FPGA的基本特点 (1)2.2 FPGA的工作原理 (1)3 简述FPGA电路中毛刺的产生 (2)3.1 毛刺产生的原因 (2)3.2 毛刺产生条件的分析......................... 错误!未定义书签。

4 毛刺的消除方法 (2)4.1 冗余项法................................... 错误!未定义书签。

4.2 采样法..................................... 错误!未定义书签。

4.3 吸收法..................................... 错误!未定义书签。

4.4 延迟法..................................... 错误!未定义书签。

4.5状态机控制法 (2)4.6 硬件描述语言法............................. 错误!未定义书签。

5 实例............................................. 错误!未定义书签。

5.1 输出加D触发器 (4)5.2在有限状态机的基础上采用时钟同步信号 (6)5.3直接把状态机的状态码作为输出信号 (8)6 结语 (10)参考文献 (11)致谢 (12)FPGA电路设计中的毛刺问题的研究摘要:目前,FPGA器件已经越来越广泛地应用在数字电路设计等领域,但它的毛刺问题却成为一个影响其可靠性和精确性的重要因素。

本文探讨了毛刺产生的原因及产生的条件,以计数器和乘法器为例对解决方案进行了深入具体地分析,总结了多种不同的解决方法,并且通过仿真说明这几种方法能够有效地消除或在一定程度上减少数字电路设计中出现的毛刺。

FPGA消除毛刺的方法

FPGA消除毛刺的方法1. 控制时钟边沿:毛刺往往是由于时钟边沿的不稳定引起的。

为了减少毛刺的发生,可以通过合理控制时钟边沿的稳定性来消除毛刺。

一种常见的方法是使用FPGA的Phase-Locked Loop(PLL)电路来锁定外部输入的时钟信号,并生成一个稳定的内部时钟信号。

通过合理设置PLL的参数,可以消除时钟边沿的抖动,进而减少毛刺现象的发生。

2.去除信号干扰:毛刺往往是由于信号干扰引起的。

为了消除毛刺,可以采取一些方法来去除信号干扰。

首先,可以通过布线的方式将敏感信号和噪声源进行物理隔离,减少信号之间的干扰。

其次,在设计时可以采用差分信号传输技术,利用差分传输的优势来抵消一部分共模干扰,减小信号受到噪声的影响。

还可以利用滤波器来消除高频噪声干扰,提高信号质量。

3.适当增加延时:毛刺往往是由于信号变化过快引起的。

为了减少毛刺的发生,可以适当增加信号的延时。

通过增加延时,可以使信号的变化更加平滑,避免毛刺的产生。

可以使用FPGA内部的延时线来实现增加延时的功能。

在选择延时线时,要根据信号的频率和变化情况来确定延时的大小,以达到最佳的消除毛刺效果。

4.信号滤波:毛刺往往是由于信号不稳定引起的。

为了减少毛刺的发生,可以通过信号滤波来稳定信号。

可以根据信号的特点选择合适的滤波器类型和参数,对信号进行滤波处理。

常用的滤波器包括低通滤波器、带通滤波器和带阻滤波器等。

通过对输入信号进行滤波处理,可以减少信号快速变化引起的毛刺现象。

5.引入缓冲器:毛刺往往是由于信号传输路径中的阻抗不匹配引起的。

为了消除毛刺,可以在信号传输路径中引入合适的缓冲器。

缓冲器可以提供合适的驱动能力,消除驱动能力不足或者驱动能力过强引起的毛刺现象。

在选择缓冲器时,要考虑信号的特点和传输路径的阻抗匹配情况,以达到最佳的消除毛刺效果。

总结起来,FPGA消除毛刺的方法包括控制时钟边沿、去除信号干扰、适当增加延时、信号滤波以及引入缓冲器等。

FPGA设计流程关键问题以及解决方案分析

FPGA的设计流程与关键问题以及解决方案分析摘要: fgpa的性能随着半导体技术的发展不断提高,并凭借高可靠性、方便的反复改写功能、灵活的用户现场编程功能等优点成为现代数字通信系统中的新宠。

本文首先介绍了fpga设计的一般设计流程,然后分析了设计中的关键问题产生的原因与影响,主要包括毛刺现象、时钟歪斜以及延迟效果不佳的现状三大点,最后对相应的问题提出解决方案。

abstract: fgpa performance is higher with the development of semiconductor technology. it is popular in the modern digital communication system with its high reliability,repeatedly rewritten function, and flexible field programming. the paper first describes the general design flow of fpga design, and then analyzes the key issue in design, including burr phenomena, clock skew, and poorly-delay situation, finally gives the appropriate solution.关键词: fpga设计流程;关键问题;解决方案key words: fpga design flow;key issues;solutions中图分类号:tn302 文献标识码:a 文章编号:1006-4311(2013)18-0196-020 引言应用fpga设计数字电路是数字电路系统领域的主要设计方法之一,不仅有助于改善电路的稳定性,减小pcb的面积,而且能缩短整个系统的设计调试周期。

高效能FPGA毛刺PUF设计与实现

高效能FPGA毛刺PUF设计与实现毛刺PUF(Physical Unclonable Function)可以利用随机性噪声提供一种额外的安全措施,用于硬件和软件的安全认证。

它是一种数字电路,可以利用毛刺效应(glitches)产生的噪声来生成一系列的随机比特串,来防止攻击者通过复制芯片或读取芯片状态来获取关键信息。

在FPGA(Field Programmable Gate Array)领域,毛刺PUF通常是通过设计和实施算法来利用FPGA的硬件特性实现的。

本文将介绍如何设计和实现一种高效能的毛刺PUF,并将介绍相关的设计和实施步骤。

一、毛刺PUF的设计思路在设计毛刺PUF时,需要将芯片的不同特性和毛刺效应考虑在内。

毛刺效应是由FPGA中的动态电流和电磁干扰引起的,这些电流和电磁干扰有时会导致芯片的输出值产生变化。

因此,如果将芯片的输入值稍稍改变一点,可能会导致芯片的输出值发生相对于输入的不可预测的变化,从而为PUF生成随机的比特串提供可能。

在毛刺PUF的设计中,需要考虑以下几个方面:(1)选择适当的FPGA芯片。

不同的FPGA芯片应该有不同的毛刺效应,因此需要根据所需的毛刺PUF规格选择适当的FPGA芯片。

(2)确定生成随机比特串的算法。

需要确定一个适当的算法,能够通过观察芯片在不同输入下的输出情况来生成一系列的随机比特串。

(3)实现算法。

需要通过编写代码和利用FPGA自适应电路来实现算法。

(4)性能评估。

需要对设计的毛刺PUF进行性能测试和评估,以确保其满足安全认证要求。

二、毛刺PUF的实现步骤2.1 选择合适的FPGA芯片在选择FPGA芯片时,需要考虑毛刺效应的强度和可观测性。

若一种芯片的毛刺效应不是很强,可能不足以产生随机信号,同理,如果输出值变化的规律性过强,不足以保证PUF的安全性,会降低PUF的可靠性,因此需要寻找尽可能具有随机性的毛刺效应强的FPGA,以提高毛刺PUF的可靠性和安全性。

FPGA毛刺的产生与消除

基于VerilogHDL语言的FPGA设计课程作业学院:电子工程学院专业班级:集电11级3班姓名:朱潮勇学号:05116079作业题目:FPGA毛刺的产生与消除完成日期:2013年11月25日一、设计要求 (2)二、规范说明 (3)三、顶层设计结构图 (3)四、模块详细设计......................................................................................... 错误!未定义书签。

1 功能说明............................................................................................. 错误!未定义书签。

2 端口定义............................................................................................. 错误!未定义书签。

3 设计代码............................................................................................. 错误!未定义书签。

4 激励代码............................................................................................. 错误!未定义书签。

5 仿真结果............................................................................................. 错误!未定义书签。

五、结论和问题: (5)前言:在FPGA的设计中,毛刺现象是长期困扰电子设计工程师的设计问题之一,是影响工程师设计效率和数字系统设计有效性和可靠性的主要因素。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA电路设计中的毛刺问题的研究引言

随着半导体技术的飞速发展,FPGA(Field Programmable Gate Array)的计算能力、容量以及可靠性也有了很大的提高。

它正以高度灵活的用户现场编程功能、灵活的反复改写功能、高可靠性等优点,成为数字电路设计、数字信号处理等领域的新宠。

但和所有的数字电路一样,毛刺也是FPGA电路中的棘手问题。

它的出现会影响电路工作的稳定性、可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。

因此,如何有效正确的解决设计中出现的毛刺,就成为整个设计中的关键一环。

本文就FPGA设计中出现的毛刺问题,根据笔者自己的经验和体会,提出了几种简单可行的解决方法和思路,供同行供交流与参考。

FPGA电路中毛刺的产生

我们知道,信号在FPGA器件中通过逻辑单元连线时,一定存在延时。

延时的大小不仅和连线的长短和逻辑单元的数目有关,而且也和器件的制造工艺、工作环境等有关。

因此,信号在器件中传输的时候,所需要的时间是不能精确估计的,当多路信号同时发生跳变的瞬间,就产生了“竞争冒险”。

这时,往往会出现一些不正确的尖峰信号,这些尖峰信号就是“毛刺”。

另外,由于FPGA以及其它的CPLD器件内部的分布电容和电感对电路中的毛刺基本没有什么过滤作用,因此这些毛刺信号就会被“保留”并传递到后一级,从而使得毛刺问题更加突出。

可见,即使是在最简单的逻辑运算中,如果出现多路信号同时跳变的情况,在通过内部走线之后,就一定会产生毛刺。

而现在使用在数字电路设计以及数字信号处理中的信号往往是由时钟控制的,多数据输入的复杂运算系统,甚至每个数据都由相当多的位数组成。

这时,每一级的毛刺都会对结果有严重的影响,如果是多级的设计,那么毛刺累加后甚至会影响整个设计的可靠性和精确性。

下面我们将以乘法运算电路来说明毛刺的产生以及去除,在实验中,我们使用的编程软件是Quartus II2.0,实验器件为Cyclone EP1CF400I7。

需要说明一点,由于示波器无法显示该整数运算的结果,我们这里将只给出软件仿真的结果。

而具体的编程以及程序的下载我们在这里也不再详述,可以参考相关的文献书籍。

毛刺的消除方法

首先,我们来设计一个简单的乘法运算电路。

运算电路如图1所示。

图 1 乘法运算运算电路及结果

如图1(c)所示,如果在不加任何的去除毛刺的措施的时候,我们可以看到结果c中含有大量的毛刺。

产生的原因就是在时钟的上升沿,每个输入(a和b)的各个数据线上的数据都不可能保证同时到达,也就是说在时钟读取数据线上的数据的时候,有的数据线上读取的已经是新的数据,而有的数据线上读取的仍然是上一个数据,这样无疑会产生毛刺信号,而当数据完全稳定的时候,毛刺信号也就自然消失了。

输出加D触发器

这是一种比较传统的去除毛刺的方法。

原理就是用一个D触发器去读带毛刺的信号,利用D触发器对输入信号的毛刺不敏感的特点,去除信号中的毛刺。

这种方法在简单的逻辑电路中是常见的一种方法,尤其是对信号中发生在非时钟跳变沿的毛刺信号去除效果非常的明显。

但是对于大多数的时序电路来说,毛刺信号往往发生在时钟信号的跳变沿,这样D触发器的效果就没有那么明显了(见图2,加D触发器以后的输出q,仍含有毛刺)。

另外,D 触发器的使用还会给系统带来一定的延时,特别是在系统级数较多的情况下,延时也将变大,因此在使用D触发器去除毛刺的时候,一定要视情况而定,并不是所有的毛刺都可以用D 触发器来消除。

图2 加D触发器后的运算电路及结果

信号同步法

在很多文章中都提到,设计数字电路的时候采用同步电路可以大大减少毛刺。

另外,由于大多数毛刺都比较短(大概几个纳秒),只要毛刺不出现在时钟跳变沿,毛刺信号就不会对系统造成危害了。

因此很多人认为,只要在整个系统中使用同一个时钟就可以达到系统同步的目标了。

但是这里面有一个非常严重的问题,就是时钟信号和其他所有的信号一样,在FPGA器件中传递的时候是有延时的,这样根本就无法预知时钟跳变沿的精确位置。

也就是说我们无法保证在某个时钟的跳变沿读取的数据是一个稳定的数据,尤其是在多级设计中,这个问题就更加突出了。

因此,做到真正的"同步"就是去除毛刺信号的关键问题。

我认为这里同步的关键就是保证在时钟的跳变沿读取的数据是稳定的数据而不是毛刺数据。

以这个思想为出发点,提出了以下几种具体的信号同步方法。

信号延时同步法

首先,我们给出了一个两级乘法(c=a b;q=d c)的运算结果(如图3所示,这里不再给出运算电路)。

可以看到,在没加任何处理过程的时候,两级结果c和q中都含有大量的毛刺信号。

其中毛刺信号产生的原因就是在计算时钟跳变时刻,数据信号同时发生了跳变。

另外,第一级信号c中含有大量的毛刺,在经过第二次乘法运算以后被明显放大了,从图3可以看出q中毛刺更加严重了。

但在很多实际工作中,我们最关心的往往是最后的输出结果(q),只要中间信号的毛刺对后面的输出没有什么影响我们就不需要对它们作任何处理了。

因此,这里所提出的信号同步的核心思想就是消除这些中间毛刺信号的影响。

图 3 两级乘法运算的结果仿真

信号延时法,它的原理就是在两级信号传递的过程中加一个延时环节,从而保证在下一个模块中读取到的数据是稳定后的数据,即不包含毛刺信号。

这里所指的信号延时可以是数据信号的延时,也可以是时钟信号的延时。

由于篇幅的关系,这里我们主要以对时钟信号的延时来说明信号延时法的原理。

对上述计算过程加时钟信号延时的原理及结果如图4所示。

图4 加了时钟延时的两级乘法运算及结果

图4中的clkdelay就是时钟延时环节。

在加这个环节以前的时钟信号是直接连到模块b 上的,这样两个模块使用同一时钟,好像已经做到了同步,但是如图3所示,结果中含有大量的毛刺,其原因就是产生毛刺的根本原因--“竞争冒险"现象没有得到根本性的消除。

加时钟延时环节的作用就是要从根本上消除“竞争冒险”,其过程是将控制模块b的时钟延时

一段时间,使得模块b的控制时钟在上跳变化时数据c已经达到了稳定,即不含毛刺信号的数据,而这时数据d也已达到稳定,这样竞争冒险现象消除了,从而毛刺信号也得到了有效的抑制,如图4 (c) 所示。

与时钟延时法的原理相同,我们也可以在数据信号加延时环节来消除竞争冒险的现象,达到真正的同步。

这里的延时环节可以使用Quartus Ⅱ提供的lcell实现,也可以使用D触发器和一个高频的计数脉冲灵活实现。

另外我们也可以从综合结果(图4 (c)所示)看到,所加的延时环节占用的芯片资源是很少的,是一种简单有效而且节约资源的方法。

时钟信号的灵活使用

和上述方法的原理相似,灵活使用时钟信号的目的也是尽可能的消除竞争冒险。

比如在时钟的第一个跳变沿触发模块a,下一个跳变沿控制触发模块b,这样时钟的交替控制也在一定程度上消除了竞争冒险,从而抑制了毛刺信号。

还比如分别使用时钟的上升沿或者下降沿控制不同的模块。

但是这些方法不适合使用在比较复杂的设计中,否则会使设计的条理非常的混乱,给以后的阅读修改带来很大的困难。

因此,在选用这种方法的时候一定要慎重。

状态机控制

对于大型的数字电路设计,状态机是一种非常理想的选择,能使运行性能和硬件资源的占用达到最佳的优化,另外灵活的使用状态机也可以实现信号的同步和消除毛刺的目的。

在数据传递比较复杂的多模块系统中,由状态机在特定的时刻分别发出控制特定模块的时钟信号或者模块使能信号,状态机的循环控制就可以使得整个系统协调运作,同时减少毛刺信号。

那么只要我们在状态机的触发时间上加以处理,就可以避免竞争冒险,从而抑制毛刺的产生。

原理如图5所示。

图 5 状态机控制原理

限于篇幅的原因,这里我们只讲述状态机控制的原理,提出一种新的思路。

总结

由于毛刺信号对FPGA器件的运行有很大的影响,如何有效抑制毛刺信号就成了一个非常突出的问题。

但是必须强调的一点就是,我们首先必须对程序设计本身进行优化和改进,使毛刺信号的产生降低到最小,比如将一些信号用变量代替来减小延时等。

另外,在实际应用中如何选用适合的方法也非常的重要,一定要慎重考虑。

比如延时环节的加入会使整个系统的延时增大,加入太多时就会影响系统的运行等。