英文翻译 原文

中英文翻译英文原文

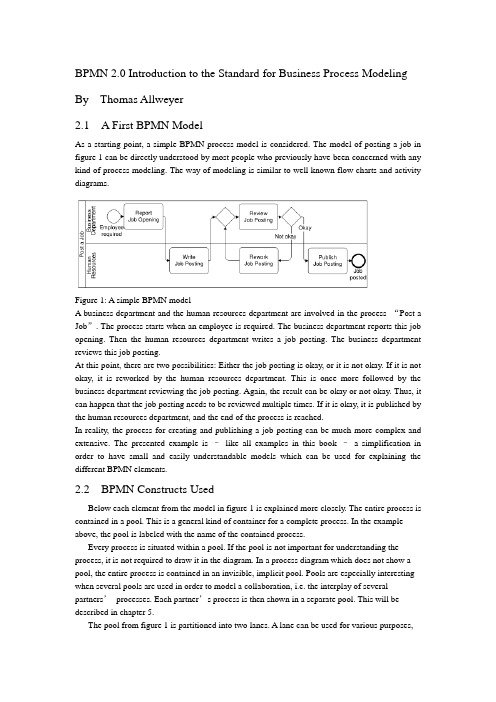

BPMN 2.0 Introduction to the Standard for Business Process Modeling By Thomas Allweyer2.1 A First BPMN ModelAs a starting point, a simple BPMN process model is considered. The model of posting a job in figure 1 can be directly understood by most people who previously have been concerned with any kind of process modeling. The way of modeling is similar to well known flow charts and activity diagrams.Figure 1: A simple BPMN modelA business department and the human resources department are involved in the process “Post a Job”. The process starts when an employee is required. The business department reports this job opening. Then the human resources department writes a job posting. The business department reviews this job posting.At this point, there are two possibilities: Either the job posting is okay, or it is not okay. If it is not okay, it is reworked by the human resources department. This is once more followed by the business department reviewing the job posting. Again, the result can be okay or not okay. Thus, it can happen that the job posting needs to be reviewed multiple times. If it is okay, it is published by the human resources department, and the end of the process is reached.In reality, the process for creating and publishing a job posting can be much more complex and extensive. The presented example is –like all examples in this book –a simplification in order to have small and easily understandable models which can be used for explaining the different BPMN elements.2.2 BPMN Constructs UsedBelow each element from the model in figure 1 is explained more closely. The entire process is contained in a pool. This is a general kind of container for a complete process. In the example above, the pool is labeled with the name of the contained process.Every process is situated within a pool. If the pool is not important for understanding the process, it is not required to draw it in the diagram. In a process diagram which does not show a pool, the entire process is contained in an invisible, implicit pool. Pools are especially interesting when several pools are used in order to model a collaboration, i.e. the interplay of several partners’processes. Each partner’s process is then shown in a separate pool. This will be described in chapter 5.The pool from figure 1 is partitioned into two lanes. A lane can be used for various purposes,e.g. for assigning organizational units, as in the example, or for representing different components within a technical system. In the example, the lanes show witch of the process’s activities are performed by the business department and which by the human resource department.Pools and lanes are also called “swimlanes”. They resemble the partitioning of swimming pools into lanes. Every participant of a competition swims only in his own lane.The process itself begins with the start event “Employee required”. Processes usually have such a start event. Its symbol is a simple circle. In most cases it makes sense to use only one start event, not several ones.A rounded rectangle represents an activity. In an activity something gets done. This is expressed by the activities’names, such as “Report Job Opening”or “Review Job Posting”.The connecting arrows are used for modeling the sequence flow. They represent the sequence in which the different events, activities, and further elements are traversed. Often this is called control flow, but in BPMN there is a second type of flow, the message flow, which influences the control of a process as well, and is therefore some kind of control flow, too. For that reason, the term “sequence flow”is used. For distinguishing it from other kinds of flow, it is important to draw sequence flows with solid lines and filled arrowheads.The process “Post a Job”contains a split: The activity “Review job posting”is followed by a gateway. A blank diamond shape stands for an exclusive gateway. This means that out of several outgoing sequence flows, exactly one must be selected. Every time the right gateway in the job posting-process is reached, a decision must be taken. Either the sequence flow to the right is followed, leading to the activity “Publish Job Posting”, or the one to the left is selected, triggering the activity “Rework Job Posting”. It is not possible to follow both paths simultaneously.The logic of such a decision is also called “exclusive OR”, abbreviated “XOR”. The conditions on the outgoing paths determine which path is selected. If a modeling tool is used and the process has to be executed or simulated by a software program, then it is usually possible to formally define exact conditions. Such formal descriptions, which may be expressed in a programming language, can be stored in special attributes of the sequence flows.If, on the other hand, the purpose of a model is to explain a process to other people,then it is advisable to write informal, but understandable, statements directly into the diagram, next to the sequence flows. The meaning of “okay”and “not okay”after the activity called “Review Job Posting”is clear to humans –a program could not make use of it.Gateways are also used for merging alternative paths. In the sample process, the gateway on the left of the activity “Review Job Posting”merges the two incoming sequence flows. Again, this is an exclusive gateway. It expects that either the activity“Write Job Posting”or “Rework Job Posting”is carried out before the gateway is reached –but not both at the same time. It should be taken care to use a gateway either for splitting or for joining, but not for a combination of both. The last element in the example process is the end event. Like the start event it has a circle as symbol –but with a thick border.2.3 Sequence Flow LogicThe flow logic of the job posting process above is rather easy to understand. In more complex models it is sometimes not clear how the modeled structure exactly is to be interpreted. Therefore it is helpful if the meaning of the sequence flow’s elements is defined in an unambiguous way.The logic of a process diagram’s sequence flow can be explained by “tokens”. Just as in a board game tokens are moved over the board according to the game’s rules, one can imagine moving tokens through a process model according to BPMN’s rules.Every time the process is started, the start event creates a token (cf. figure 2). Since the job posting process is carried out more than once, many tokens can be created in the course of time. Thereby it can happen that the process for one job posting is not yet finished, when the process for posting another job starts. As it moves through the process, each token is independent from the other tokens’movements.Figure 2: A start event creates a tokenThe token that has been created by the start event moves through the sequence flow to the first activity. This activity receives a token, performs its task (in this case it reports a job opening), and then releases it to the outgoing sequence flow (cf. figure 3).Figure 3: An activity receives a token and forwards it after completionThe following activity forwards the token. It then arrives at the merging exclusive gateway. The task of this gateway is simple: It just takes a token that arrives via any incoming sequence flow and moves it to the outgoing sequence flow. This is shown in figure 4. In case A, a token arrives from the left, in case B from below. In both cases the token is routed to the outgoing sequence flow to the right.Figure 4: Routing of a token by a merging exclusive gatewayThe task of the splitting exclusive gateway is more interesting. It takes one arriving token and decides according to the conditions, to which sequence flow it should be moved. In case A in figure 5, the condition “okay”is true, i.e. the preceding review activity has produced a positive result. In this case, the token is moved to the right. Otherwise, if the condition “not okay”is true, the token is moved to the downwards sequence flow (case B).The modeler must define the conditions in such a way that always exactly one of the conditions is true. The BPMN specification does not state how to define conditions and how to check whichconditions are true. Since the considered process is not executed by software, the rather simple statements used here are sufficient. Otherwise, it would be necessary to define the conditions according to the requirements and rules of the software tool.The token may travel several times through the loop for reworking the job posting. Finally it arrives at the end event. This simply removes any arriving token and thus finishes the entire process (figure 6).Figure 5: Routing of a token by a splitting exclusive gatewayThe sequence flow of every process diagram can be simulated in this way with the help of tokens. This allows for analyzing whether the flow logic of a process has been modeled correctly.It should be noted that a token does not represent such a thing as a data object or a document. In the case of the job posting process, it could be imagined to have a document “job posting”flowing through the process. This document could contain all required data, such as the result of the activity “Review Job Posting”. At the splitting gateway, the decision could then be based on this attribute value. However, the BPMN sequence flow is constrained to the pure order of execution. The tokens therefore do not carry any information, other than a unique identifier for distinguishing the tokens from each other. For data objects there are separate BPMN constructs which will be presented in chapter 10.2.4 Presentation OptionsUsually pools are drawn horizontally. The preferred direction of sequence flow is then from left to right. On the other hand, it is also possible to use vertical pools and to draw the sequence flow from top to bottom, as in the example in figure 7.It makes sense to decide for only one of these possibilities –horizontal or vertical. Nevertheless there are modeling tools which only support horizontal modelingFigure 6: An end event removes an arriving tokenFigure 7: Vertical swimlanes and nested lanesFigure 7 also shows an example of nested lanes. The lane labeled “Sales”is partitioned into the two lanes “Sales Force”and “Order Processing”. In principle it is possible to partition these lanes again, etc., although this only makes sense up to a certain level of depth.It is not prescribed where to place the names of pools and lanes. Typical are the variants selected for figure 1 and figure 7. Here the names are placed on the left of the pools or lanes, or at the top for the vertical style, respectively. The name of a pool is separated by a line. The names of the lanes, however, are placed directly within the lanes. A separation line is only used for a lane that is partitioned into further sub-lanes. Lanes can also be arranged as a matrix. The procurement process in figure 8 runs through a business department and the procurement department, both of which span a branch office and the headquarters. When a demand occurs in a branch’s business department, this department reports the demand. In the next step, the procurement is approved by the same department in the headquarters. The central part of the procurement department then closes a contract with a supplier, followed by the branch’s purchasing department carrying out the purchase locally.Although the BPMN specification explicitly describes the possibility of such a matrix presentation, it is hardly ever applied, so far.12.2 Message CorrelationThe contents of the message flows within one conversation are always related to each other. For example, all messages that are exchanged within one instance of the conversation “Process Order for Advertisement”relate to the same advertisement order. It is therefore possible to use the order ID for the correlation, i.e. the assignment of messages to a process instance. If a customer receives an advertisement for approval, he can determine the corresponding order –and thus the process instance –based on the order ID. All messages of a conversation have a common correlation.A simple conversation which is not broken down into other conversations is called communication. Therefore, the lines are called communication links (the specification draft at some places alsocalls them conversation links). A conversation has always communication links to two or more participants.If the end of a communication link is forked, multiple partners of the same type can be part of the communication, otherwise exactly one. “Process Order for Advertisement”has exactly one customer and one advertising agency as participants, but multiple designers. Therefore, the designer’s pool contains a multiple marker. However, having only the multiple marker in the pool is not sufficient. The conversation “Handle order for an illustration”, for example, has only one designer as participant. Therefore, the respective end of the communication link is not forked.12.3 Hierarchies of ConversationsBesides communications, it is also possible to use sub-conversations. Similar to sub-processes they are marked with a ‘+’-sign. The details of a sub-conversation can be described in another conversation diagram. The diagram of a sub-conversation can only contain those participants who are linked to the sub-conversation within the parent diagram.Figure 171 shows the detailed conversation diagram for the sub-conversation “Process Order for Advertisement”As can be seen from this diagram, it is also possible to draw message flows directly into the conversation diagram. Other than collaboration diagrams, conversation diagrams are not allowed to show processes in the pools or choreographies between the pools.Figure 171: Conversation diagram for sub-conversation “Process Order for Advertisement”The diagram contains those message flows that are related to the same order. To be more precise, they relate to the same inquiry. At the beginning, an order has not been placed yet, and not every inquiry turns into an order. Therefore, the common reference point is the inquiry.Besides the explicitly displayed message flows between customer and advertising agency, the diagram also contains the communication “Assignment of Graphics Design”. All message flows of this communication are also related to the same inquiry, but this information is not sufficient for the advertising agency in order to assign all incoming messages correctly. This is due to the fact that availability requests are sent to several designers. The advertising agency has to correctly assign each incoming availability notice to the correct availability request. Thus, additional information is required for correlating these messages, e.g. the IDs of the availability requests.Therefore it is possible to define a separate communication for the message flows between advertising agency and designer. The message exchanges of this communication can also be modeled in a collaboration diagram (figure 172) or in a choreography diagram (figure 173). Of course, it is also possible to show the message flows of the entire sub-conversation within a single diagram (figures 161 and 162 in the previous chapter).Figure 172: Collaboration diagram for communication “Assignment of Graphics Design”Like sub-processes, sub-conversations can also be expanded, i.e. the hexagon is enlarged, and the detailed conversation is shown in its interior. However, it is graphically not easy to include, for example, the contents of figure 171 into an expanded sub-conversation in figure 170. Unfortunately, the BPMN specification draft does not contain any examples for expandedsub-conversations either.。

带翻译的英文文章

带翻译的英文文章You must control and direct your emotions not abolish them. Besides, abolition would be antimissile task. Emotions are like a river. Their power can be dammed up and released under controland direction, but is cannot be held forever in check. Sooner or later the dam will burst, unleashing catastrophic destruction.你必须控制并导引你的情绪而非摧毁它,况且摧毁情绪是一件不可能的事情。

情绪就像河流一样,你可以筑一道堤防把它挡起来,并在控制和导引之下排放它,但却不能永远抑制它,否则那道堤防迟早会崩溃,并造成大灾难。

Your negative emotions can also be controlled and directed. PMA and self-discipline can remove their harmful effects and make them serve constructive purposes. Sometimes fear and anger willinspire intense action. But you must always submit your negative emotions--and you positive ones--to the examination of your reason before releasing them. Emotion without reason is a dreadfulenemy.你的消极心态同样也可被控制和导引,积极心态和自律可去除其中有害的部分,而使这些消极心态能为目标贡献力量。

人教版高中英语课文原文与翻译参考

⼈教版⾼中英语课⽂原⽂与翻译参考⼈教版⾼中英语课⽂原⽂与翻译参考 ⾼中英⽂课⽂⼀《⼈教版⾼中英语课⽂原⽂和翻译》 ANNE’S BEST FRIEND Do you want a friend whom you could tell everything to, like your deepest feelings and thoughts? Or are you afraid that your friend would laugh at you, or would not understand what you are going through? Anne Frank wanted the first kind, so she made her diary her best friend. 安妮最好的朋友 你想不想有⼀位⽆话不谈能推⼼置腹的朋友?或者你会不会担⼼你的朋友会嘲笑你,会不理解你⽬前的困境呢?安妮?弗兰克想要的是第⼀种类型的朋友,所以她把的⽇记视为⾃⼰最好的朋友。

Anne lived in Amsterdam in the Netherlands during World War II. Her family was Jewish so the had to hide or they would be caught by the German Nazis. She and her family hide away for two years before they were discovered. During that time the only true friend was her diary. She said, “I don’t want to set down a series of facts in a diary as most people do, but I want this diary itself to be my friend, and I shall call my friend Kitty.” Now read how she felt after being in the hiding place since July 1942. 在第⼆次世界⼤战期间,安妮住在荷兰的阿姆斯特丹。

高一英语课文翻译(人教版)

★以下是英⽂写作翻译频道为⼤家整理的《⾼⼀英语课⽂翻译(⼈教版)》,供⼤家参考。

第⼀课:好朋友 SPEAKING 课⽂翻译 JOHN:I’m 15 years old and I love football. I also like reading, especially 约翰:我15岁,我喜欢⾜球,我也喜欢读书,尤其 stories about people from other countries. I don’t enjoy singing, nor 是有关其他国家⼈的书。

我不喜欢唱歌,也 do I like computers. I think that rock music is terrible. 不喜欢电脑,我认为摇滚⾳乐很可怕。

ANN:Hi,I’m Ann. I’m 16 and I like dancing and computers. I also like 安妮:你们好,我是安妮。

我16岁,我喜欢跳舞和电脑。

我也喜欢 rock music. I hate hiking and I’m not /into/ classical music. I don’t 摇滚⾳乐。

我不喜徒步旅⾏,我对古典⾳乐⽆兴趣。

我不 enjoy reading too much. 太喜欢读书。

STEVE:I’m 14 years old and I love skiing. Other favourite hobbies are 史蒂夫:我14岁,我喜欢滑雪。

其他的嗜好是 reading and singing. I don’t like hiking. I think that rock music is 读书和唱歌。

我不喜欢徒步旅⾏。

我认为摇滚⾳乐 too loud, and I think that football is boring. 太吵闹,并且我认为⾜球很惹⼈烦。

PETER:I’m from Australia. I’m 15 and I’m fond of singing. I sing a lot, 彼得:我来⾃澳⼤利亚,我15岁,我喜欢唱歌,我不停地唱歌。

英文翻译资料原文及译文

The Architecture of the MySQL班级:10网工1 学号:1004031010 姓名:汪青松指导老师签字:Mysql’s architecture is best understood in the context of its history.Mysql history goes back to 1979 when Monty Widenius, working for a small company called TCX, created a reporting tool written in BASIC that ran on a 4 MHZ computer with 16 KB RAM. Over time, the tool was rewritten in C and ported to run on Unix. It was still just a low-level storage engine with a reporting front end. The tool was known by the name of Uniseg.Working under the adverse conditions of little computational resources, and perhaps building on his God-given talent, Monty developed a habit and ability to write very efficient code naturally. He also developed, or perhaps was gifted from the start, with an unusually acute vision of what needed to be done to the code to make it useful in future development—without knowing in advance much detail about what that future development would be.In addition to the above, with TCX being a very small company and Monty being one of the owners, he had a lot of say in what happened to his code. While there are perhaps a good number of programmers out there with Monty’s talent and ability, for a number of reasons, few get to carry their code around for more than 20 years. Monty did.Monty’s work, talents, and ownership of the code provided a foundation upon which the Miracle of MySQL could be built.Some times in the 1990s, TCX customers began to push for an SQL interface to their data. Several possibilities were considered. One was to load it into a commercial database .Monty was not satisfied with the speed. He tried borrowing mysql code for the SQL part and integrating it with his low-level storage engine. That did not work well either. Then came the classic move of a talented driven programmer: ―I’ve had enough of those tools that somebody else wrote that don’t work! I’m writing my own!‖Thus in May of 1996 MySQL version 1.0 was released to a limited group, followed by a public release in October 1996 of version 3.11.1. The initial public release provided only a binary distribution for Solaris. A month later, the source and the Linux binary were released.In the next two years, MySQL was ported to a number of other operating systems as thefeature set gradually increased. MySQL was originally released under a special license that allowed commercial use to those who were not redistributing it with their software. Special licenses were available for sale to those who wanted to bundle it with their product. Additionally, commercial support was also being sold. However, it still lacked support for transactions subquery foreign keys, stored procedures, and views. The locking happened only at a table level, which in some cases could slow it down to a grinding halt. Some programmers unable to get around its limitations still considered it a toy, while others were more than happy to dump their Oracle or SQL Server in favor of MySQL, and deal with the limitations in their code in exchange for improvement in performance and licensing cost savings.Around 1999–2000 a separate company named MySQL AB was established. It hired several developers and established a partnership with Sleepy cat to provide an SQL interface for the Berkeley DB data files. Since Berkeley DB had transaction capabilities, this would give MySQL support for transactions, which it previously lacked. After some changes in the code in preparation for integrating Berkeley DB, version 3.23 was released. source became equipped with hooks to add any type of storage engine, including a transactional one.By April of 2000, with some encouragement and sponsorship from Slashdot, masterslave replication capability was added. The old no transactional storage engine, ISAM, was reworked and released as My ISAM. Among a number of improvements, full-text search capabilities were now supported. A short-lived partnership with Nu Sphere to add Gemini, a transactional engine with row-level locking, ended in a lawsuit toward the end of 2001. However, around the same time, Heikki Tuuri approached MySQL AB with a proposal to integrate his own storage engine, InnoDB, which was also capable of transactions and row-level locking.Heikki’s contribution integrated much more smoothly with the new table handler interface already polished off by the Berkeley DB integration efforts. The MySQL/InnoDB combination became version 4.0, and was released as alpha in October of 2001. By early 2002 the MySQL/InnoDB combo was stable and instantly took MySQL to another level. Version 4.0 was finally declared production stable in March 2003.In April 2000, with some comes from Slashdot's encouragement and sponsorship, increase the ability of master slave copy. The old the things storage engines, shameless sad men of obscene nets. Learn, nets always copy six | d, theory-the nets, we no longer provide completecontent. And In no DB group gradually stability, make MySQL arrived at another level. In March 2003 announced formally entered the stable production version 4.0.Version of the upgrade is it but not because In no DB supplement the cause of the results. The developers have thought that MySQL In no DB is very important complement, but do not mean that is completely dependent on it and lead to success. At that time, even now, a new storage engines as a supplement would not change one version of the celebration. In fact, compared with the past version, 4.0 version not much added. Perhaps the most important supplement is increased cache lookup, this make lots of code running performances are being greatly enhanced. The code duplication and rewrite the use of two thread: one is to host to the network I/O, and the other is a deal with updated. And add some improved optimization. Client/server agreement be SSL ability.In March 2003, named for the alpha 4.1 release, and announced in June 2004 to the test. Different in version 4.0, it increases the many significant improvement. Perhaps the most important son inquires is, by many users a long-awaited function. The index function space directly has been increased to MySQL storage engines. The implementation of the support Unicode. Client/server agreement is getting a lot of change. It more resistant to the outside of the attack, and support to write report.In alpha4.. 1 release at the same time, another development branch in development still work: version 5.0, it increases the storage process, the server cursor, flip-flops, trying to, XA things, query optimizer have great improvement, and there is a lot of new features. Because the developers feel if MySQL if all the latest top function to join to version 4.1 will take a long time to stability, and they have to handle storage process, and decided to set up a separate development branch. Finally in the December 2003 alpha5.0 version released. For a while, because the alpha formed two branches caused great confusion. Having working experience when version 4.1 in October 2004 to achieve stability, chaos also solved.A year later, in October 2005 version 5.0 to a stable.Then in November 2005 the first alpha5.1 releases, it increased a lot of improvement, including the table data partition, based on done copy, event schedule, and standardization of the API plug-ins, this is helpful to other plug in and the integration of new storage engines.At this point, MySQL are positive development. 5.0 is the most stable version, although 5.1is a beta, but should quickly can achieve stability. The new function will be introduced to version 5.2.MySQL framework, and for most, the structure of the MySQL different from formal definition and norms. In the original code, not to become part of the system, but in order to solve some very specific questions.The core module: connection manager, thread management, thread connection, user identity authentication module, access control module, the parser, scheduling, inquires the cache module, optimization, table manager, table transformation module, table maintenance module, a status report module, led by analysis storage interface (standard procedures), storage engines achieve (My ISAM, In no DB, MEMORY, Berkeley DB), log records module, copy the main module, copy from the module, the client/server API, low level of agreement network I/O API, core API.The core function module, when the server in the command line next start operation, the initial module to control. It analytical configuration files and command line parameters, allocation of global memory buffer, the initial global variable and structure, load access control list, and performing other initialization tasks. Thread connection can create new, or from the thread cache and retrieval requirements of extracting old. Once the thread connection accept control, it first call user identity authentication module. In the user's identity information after verification, the client can request.Thread connection will request the data transmission to command scheduling. Some requirements in terms of MySQL code called command, can through the command scheduling run directly, but some of the more complex the need in the other modules. A typical commands can be required server and the query, change activities database, the report states, send continuously updated copy games, close the connection or perform some other operations.In MySQL server terms, there are two types of customer request statement: query and command. Through analysis of any enquiry is request. Command is a call of requests to perform without parser. We will use the internal range of long-term inquires MySQL. Therefore, it is not only a choice, and also have to delete and inserted in our terms just call inquires the. Sometimes we will also query called the SQL statement.If the opening of complete log records inquires the command of electricity management requirements log records module access or command call pure text. Thus, in the whole of thequery log configuration requirements will be shameless sadness mean of the men nets. Learn, nets always copy six | d, theory-the nets, we no longer provide complete content., the executive in this short circuit, the cache results returned to the user, thread connection accept control, and prepare to another order process. If inquires the cache module report out a mistake, a inquires to analyzer relay, it will be the basis of inquires on how to transfer control to decide.People can identify the following module, can continue to from that point: optimizer, table modify module, table maintenance module, copy module and a status report module. Choose queries to optimization, update, insert, and delete and table to create and mode, change to their table transformation inquiry module, inquires the, checking, maintenance, update the important statistical data, or ZhengLiBiao to table maintenance module; Inquires concerned copied to copy module; And the position of the request turned to a status report module. There are also a number of table transformation module: delete module, establish a module, update module.At this point, this module will receive from the parser control each relay in inquires involves access control list module list, and then, after the success, to the table manager, open the table and obtain the necessary lock. Now watch operation module is ready to perform its task, and will release quantity requirement of abstract storage engine modules of the low level such as insert or record update operation, retrieval based on record key value, or watch on the operation of the executive level, such as repair, or update the index statistical information.Abstract storage engine module will automatically switch to call the concrete method of storage engines, through the corresponding module object polymorphism. In other words, when a storage engine object, the caller think it in dealing with an abstract, but in fact the more concrete object types are: it storage engine object is corresponding to the given phenotype. The interface is a virtual method, it created a transparent effect. The correct method will be calls, call party of no need to know exactly the type of object storage engines object.When inquires is processed or order, after the corresponding module will be a part of the result set to the statement because they are available. It can also send a warning or false information. If the error message has been made, the client and server know, inquires the or command failed, and take appropriate measures. The client will not accept any more is given query result set, warning or false information data, the server will always control transfer after connected to thread sent a mistake. Note, for not using MySQL exception implementationstability and portability, in all levels of all the requirements of reason, must check and control fault is under the condition of appropriate transmission error.If low levels of module in some way more data have been modified, and if the binary renew log is enabled, module will be responsible for record recorded update module will be required of the events of the binary renew log, sometimes called copy logs, or, in the main users and developers MySQL, bin log. Once after completion, executive process returns to the links, it carries out the necessary cleaning and to the other inquires from client or waiting for the order. The meeting continue until the client from a command.In addition to the regular customer interaction, a server may receive a command from copying slaves of continuous read binary renew log. This command will copy stompers processing module.If the server as a copy from the configuration, the initial module will call copy from module, which will launch two thread, the so-called SQL thread and the I/O thread. They use the publicity occurred in the main module to update from module. It is in the same server can be configured to the main module and from module.Network communication with the customers through the client/server protocol modules, the packing in the appropriate format data is responsible, and depending on the connection Settings, compress it. Client/server protocol modules in turn use low-level network I/O modules, and this is responsible for sending and receiving in the data of the cross-platform about a socket level of portable way. It is also used to encrypt data using Open SSL library is responsible for call options if the connection is set correctly.When they perform their respective tasks, the core component of a lot depends on the server in the core API. Core API provides a rich set of functions, including file of I/O, memory management, string operation, the implementation of the data structure and algorithms, and many other useful functions. MySQL developers encourage to avoid a direct lib of calls, and use core API for citizens to travel to new port platform and the future of code optimization.MySQL的架构班级:10网工1 学号:1004031010 姓名:汪青松指导老师签字:MySQL的架构的最好的理解是从他的历史背景中去发现。

中英文对照翻译文章

中英文对照翻译文章不少英文文章都是带有翻译的,为的就是方便读者在不理解文章的时候能够找到对照的意思。

下面就是店铺给大家整理的中英文对照翻译文章,希望大家喜欢。

中英文对照翻译文章篇1:A Sailor's Christmas Gift一个水手的圣诞礼物William J·Lederer威廉·J·莱德勒Last year at Christmas time my wife,three boys,and I were in France,on our way from Paristo Nice.For five wretched days ererything had gone wrong.Our hotels were“touristtraps”;our rented car broke down;we were all restless and irritable in the crowded car.OnChristmas Eve,when we checked into a dingy hotel in Nice,there was no Christmas spirit inour hearts.去年,在圣诞节期间,我和我的妻子以及我们的三个孩子,从法国踏上由巴黎到尼斯的旅途。

由于接连五天的恶劣天气,旅途上一切很不顺心。

我们下榻的旅馆尽是些敲诈勒索旅客的“陷阱”;我们租用的那辆汽车老是发生故障,在拥挤不堪的车子上大家个个显得烦躁不安。

圣诞节前夕,我们住进了尼斯的一家旅店,这家旅店又脏又暗,我们打心眼里感觉不到丝毫的节日气氛。

It was raining and cold when we went out to eat.We found a drab littlejoint shoddily decoratedfor the holiday.It smelled greasy.Only five tables in the restaurant were occupied.Therewere two German couples,two French families,and an American sailor,by himself.In thecorner a piano player listlessly played Christmas music.我们外出就餐时,天正下着小雨,天气寒冷。

英文原文加中文翻译

英文原文:Rehabilitation of rectangular simply supported RC beams with shear deficienciesusing CFRP compositesAhmed Khalifa a,* , Antonio Nanni ba Department of Structural Engineering, University of Alexandria, Alexandria 21544, Egyptb Department of Civil Engineering, University of Missouri at Rolla, Rolla, MO 65409, USAReceived 28 April 1999; received in revised form 30 October 2001; accepted 10 January 2002AbstractThe present study examines the shear performance and modes of failure of rectangular simply supported reinforced concrete(RC) beams designed with shear deficiencies. These members were strengthened with externally bonded carbon fiber reinforced polymer (CFRP) sheets and evaluated in the laboratory. The experimental program consisted of twelve full-scale RC beams tested to fail in shear. The variables investigated within this program included steel stirrups, and the shear span-to-effective depth ratio, as well as amount and distribution of CFRP. The experimental results indicated that the contribution of externally bonded CFRP to the shear capacity was significant. The shear capacity was also shown to be dependent upon the variables investigated. Test results were used to validate a shear design approach, which showed conservative and acceptable predictions.○C2002 Elsevier Science Ltd. All rights reserved.Keywords: Rehabilitation; Shear; Carbon fiber reinforced polymer1. IntroductionFiber reinforced polymer (FRP) composite systems, composed of fibers embedded in a polymeric matrix, can be used for shear strengthening of reinforced con-crete (RC) members [1–7]. Many existing RC beams are deficient and in need of strengthening. The shear failure of an RC beam is clearly different from its flexural failure. In shear, the beam fails suddenly without sufficient warning and diagonal shear cracks are consid-erably wider than the flexural cracks [8].The objectives of this program were to:1. Investigate performance and mode of failure of simply supported rectangular RC beams with shear deficien-cies after strengthening with externally bonded CFRP sheets.2. Address the factors that influence shear capacity of strengthened beams such as: steel stirrups, shear span-to-effective depth ratio (a/d ratio), and amount and distribution of CFRP.3. Increase the experimental database on shear strength-ening with externally bonded FRP reinforcement.4. Validate the design approach previously proposed by the authors [9].For these objectives, 12 full-scale, RC beams designed to fail in shear were strengthened with different CFRP schemes. These members were tested as simple beams using a four-point loading configuration with two different a/d ratios.2. Experimental program2.1. Test specimens and materialsTwelve full-scale beam specimens with a total span of 3050 mm. and a rectangular cross-section of 150-mm-wide and 305-mm-deep were tested. The specimens were grouped into two main series designated SW and SO depending on the presence of steel stirrups in the shear span of interest.Series SW consisted of four specimens. The details and dimensions of the specimens designated series SW are illustrated in Fig. 1a. In this series, four 32-mm steel bars were used as longitudinal reinforcement with two at top and two at bottom face of the cross-section to induce a shear failure. The specimens were reinforced with 10-mm steel stirrups throughout their entire span. The stirrups spacing in the shear span of interest, right half, was selected to allow failure in that span.Series SO consisted of eight beam specimens, which had the same cross-section dimension and longitudinal steel reinforcement as for series SW. No stirrups were provided in the test half span as illustrated in Fig. 1b.Each main series (i.e. series SW and SO) was subdivided into two subgroups according to shear span-to-effective depth ratio. This was selected to be a/d = 3 and 4, resulting in the following four subgroups: SW3;SW4; SO3; and SO4.The mechanical properties of the materials used for manufacturing the test specimens are listed in Table 1.Fabrication of the specimens including surface preparation and CFRP installation is described elsewhere [10].Table 12.2. Strengthening schemesOne specimen from each series (SW3-1, SW4-1, SO3-1 and SO4-1) was left without strengthening as a control specimen, whereas eight beam specimens were strengthened with externally bonded CFRP sheets following three different schemes as illustrated in Fig. 2.In series SW3, specimen SW3-2 was strengthened with two CFRP plies having perpendicular fiber directions (90°/0°). The first ply was attached in the form of continuous U-wrap with the fiber direction oriented perpendicular to the longitudinal axis of the specimen (90°). The second ply was bonded on the two sides of the specimen with the fiber direction parallel to the beam axis(0°).This ply [i.e. 0°ply] was selected to investigate the impact of additional horizontal restraint on shear strength.In series SW4, specimen SW4-2 was strengthened with two CFRP plies having perpendicular fiber direction (90°/0°) as for specimen SW3-2.Four beam specimens were strengthened in series SO3. Specimen SO3-2 was strengthened with one-ply CFRP strips in the form of U-wrap with 90°-fiber orientation. The strip width was 50 mm with center-to-center spacing of 125 mm. Specimen SO3-3 was strengthened in a manner similar to that of specimen SO3-2, butwith strip width equal to 75 mm. Specimen SO3-4 was strengthened with one-ply continuous U-wrap (90°). Specimen SO3-5 was strengthened with twoCFRP plies (90°/0°) similar to specimens SW3-2 and SW4-2.In series SO4, two beam specimens were strengthened. Specimen SO4-2 was strengthened with one-ply CFRP strips in the form of U-wrap similar to specimen SO3-2. Specimen SO4-3 was strengthened with one-ply continuous U-wrap (90°) similar to SO3-4.2.3. Test set-up and instrumentationAll specimens were tested as simple span beams subjected to a four-point load as illustrated in Fig. 3. A universal testing machine with 1800 KN capacity was used in order to apply a concentrated load on a steel distribution beam used to generate the two concentrated loads. The load was applied progressively in cycles, usually one cycle before cracking followed by three cycles with the last one up to ultimate. The applied load vs. deflection curves shown in this paper are the envelopes of these load cycles.Four linear variable differential transformers (LVDTs) were used for each test to monitor vertical displacements at various locations as shown in Fig. 3. Two LVDTs were located at mid-span on each side of the specimen. The other two were located at the specimen supports to record support settlement.For each specimen of series SW, six strain gauges were attached to three stirrups to monitor the stirrup strain during loading as illustrated in Fig. 1a. Three strain gauges were attached directly to the FRP sheet on the sides of each strengthened beam to monitor strain variation in the FRP. The strain gauges were oriented in the vertical direction and located at the section mid-height with distances of 175, 300 and 425 mm, respectively, from the support for series SW3 and SO3. For beam specimens of series SW4 and SO4, the strain gauges were located at distance of 375, 500 and 625 mm, respectively, from the support.3. Results and discussionIn the following discussion, reference is always made to weak shear span or span of interest.3.1. Series SW3Shear cracks in the control specimen SW3-1 were observed close to the middle of the shear span when the load reached approximately 90 kN. As the load increased, additional shear cracks formed throughout, widening and propagating up to final failure at a load of 253 kN (see Fig. 4a).In specimen SW3-2 strengthened with CFRP (90°/0°), no cracks were visible on the sides or bottom of the test specimen due to the FRP wrapping. However,a longitudinal splitting crack initiated on the top surface of the beam at a high load of approximately 320 kN.The crack initiated at the location of applied load and extended towards the support. The specimen failed by concrete splitting (see Fig. 4b) at total load of 354 kN. This was an increase of 40% in ultimate capacity compared to the control specimen SW3-1. The splitting failure was due to the relatively high longitudinal compressive stress developed at top of the specimen, which created a transverse tension, led to the splitting failure. In addition, the relatively large amount of longitudinal steel reinforcement combined with over-strengthening for shear by CFRP wrap probably caused this mode of failure. The load vs. mid-span deflection curves for specimens SW3-1 and SW3-2 are illustrated in Fig. 5, to show the additional capacity gained by CFRP.The maximum CFRP vertical strain measured at failure in specimen SW3-2 was approximately 0.0023 mm/mm, which corresponded to 14% of the reported CFRP ultimate strain. This value is not an absolute because it greatly depends on the location of the strain gauges with respect to a crack. However, the recorded strain indicates that if the splitting did not occur, the shear capacity could have reached higher load.Comparison between measured local stirrup strains in specimens SW3-1 and SW3-2 are shown in Fig. 6. The stirrups 1, 2 and 3 were located at distance of 175, 300 and 425 mm from the support, respectively. The results showed that the stirrups 2 and 3 did not yield at ultimate for both specimens. The strains (and the forces) in the stirrups of specimen SW3-2 were, in general, smaller than those of specimen SW3-1 at the same level of loading due to the effect of CFRP.Fig. 6. Applied load vs. strain in the stirrups for specimens SW3-1 and SW3-2. 3.2. Series SW4In specimen SW4-1, the first diagonal crack was formed in the member at a totalapplied load of 75 kN. As the load increased, additional shear cracks appeared throughout the shear span. Failure of the beam occurred when the total applied load reached 200 kN. This was a decrease of 20% in shear capacity compared to the specimen SW3-1 with a/d ratio=3.In specimen SW4-2, the failure was controlled by concrete splitting similar to test specimen SW3-2. The total applied load at ultimate was 361 kN with an 80% increase in shear capacity compared to the control specimen SW4-1. In addition, the measured strains in the stirrups for specimen SW4-2 were less than those of specimen SW4-1. The applied load vs. mid-span deflection curves for beams SW4-1 and SW4-2 are illustrated in Fig. 7. It may be noted that specimen SW4-2 resulted in greater deflection when compared to specimen SW4-1.When comparing the test results of series SW3 specimens to that of series SW4, the ultimate failure load of specimen SW3-2 and SW4-2 was almost the same. However, the enhanced capacity of specimen SW3-2 (a/d=3) due to the addition of the CFRP reinforcement was 101 kN, while specimen SW4-2 (a/d=4) was 161 kN. This indicates that the contribution of external CFRP reinforcement may be influenced by the ayd ratio and appears to decrease with a decreasing a/d ratio. Further, for both strengthened specimens (SW3-2 and SW4-2), CFRP sheets did not fracture or debond from the concrete surface at ultimate and this indicates that CFRP could provide additional strength if the beams did not failed by splitting.3.3. Series SO3Fig. 8 illustrates the failure modes for series SO3 specimens. Fig. 9 details the applied load vs. mid-span deflection for the specimens.The failure mode of control specimen SO3-1 was shear compression. Failure of the specimen occurred at a total applied load of 154 kN. This load was a decrease of shear capacity by 54.5 kN compared to the specimen SW3-1 due to the absent of the steel stirrups. In addition, the crack pattern in specimen SW3-1 was different from of specimen SO3-1. In specimen SW3-1, the presence of stirrups provided a better distribution of diagonal cracks throughout the shear span.In specimen SO3-2, strengthened with 50-mm CFRP strips spaced at 125 mm, the first diagonal shear crack was observed at an applied load of 100 kN. The crackpropagated as the load increased in a similar manner to that of specimen SO3-1. Sudden failure occurred due to debonding of the CFRP strips over the diagonal shear crack, with spalled concrete attached to the CFRP strips. The total ultimate load was 262 kN with a 70% increase in shear capacity over the control specimen SO3-1. The maximum local CFRP vertical strain measured at failure in specimen SO3-2 was 0.0047 mm/mm (i.e. 28% of the ultimate strain), which indicated that the CFRP did not reach its ultimate.Specimen SO3-3, strengthened with 75-mm CFRP strips failed as a result of CFRP debonding at a total applied load of 266 kN. No significant increase in shear capacity was noted compared to specimen SO3-2. The maximum-recorded vertical CFRP strain at failure was 0.0052 mmymm (i.e. 31% of the ultimate strain).Specimen SO3-4, which was strengthened with a continuous CFRP U-wrap (908), failed as a result of CFRP debonding at an applied load of 289 kN. Results show that specimen SO3-4 exhibited increase in shear capacity of 87, 10 and 8.5% over specimens SO3-1,SO3-2 and SO3-3, respectively. Applied load vs. vertical CFRP strain for specimen SO3-4 is illustrated in Fig. 10 in which strain gauges sg1, sg2 and sg3 were located at mid-height with distances of 175, 300 and 425 mm from the support, respectively. Fig.10 shows that the CFRP strain was zero prior to diagonal crack formation, then increased slowly until the specimen reached a load in the neighborhood of the ultimate strength of the control specimen. At this point, the CFRP strain increased significantly until failure. The maximum local CFRP vertical strain measured at failure was approxi- mately 0.0045 mm/mm.When comparing the results of beams SO3-4 and SO3-2, the CFRP amount used to strengthen specimen SO3-4 was 250% of that used for specimen SO3-2. Only a 10% increase in shear capacity was achieved for the additional amount of CFRP used. This means that if an end anchor to control FRP debonding is not used, there is an optimum FRP quantity, beyond which the strengthening effect is questionable. A previous study [11] showed that by using an end anchor system, the failure mode of FRP debonding could be avoided. Reported findings are consistent with those of other research [7],which was based on a review of the experimental results available in the literature, and indicated that the contribution of FRP to the shear capacity increases almost linearly, with FRP axial rigidity expressed byf f E ρ(f ρ is the FRP area fraction and f E is the FRP elastic modulus) up to approximately 0.4 GPa. Beyond this value, the effectiveness of FRP ceases to be positive.In specimen SO3-5, the use of a horizontal ply over the continuous U-wrap (i.e. 90°/0°) resulted in a concrete splitting failure rather than a CFRP debonding failure. The failure occurred at total applied load of 339 kN with a 120% increase in the shear capacity compared to the control specimen SO3-1. The strengthening with two perpendicular plies (i.e. 90°/0°) resulted in a 17% increase in shear capacity compared to the specimen with only one CFRP ply in 90° orientation (i.e. specimen SO3-4). The maximum local CFRP vertical strain measured at failure was 0.0043 mm/mm.By comparing the test results of specimens SW3-2 and SO3-5, having the same a/d ratio and strengthening schemes but with different steel shear reinforcement, the shear strength (i.e. 177 and 169.5 kN for specimens SW3-2 and SO3-5, respectively), and the ductility are almost identical. One may conclude that the contribution of CFRP benefits the beam capacity to a greater degree for beams without steel shear reinforcement than for beams with adequate shear reinforcement.3.4. Series SO4Series SO4 exhibited the largest increase in shear capacity compared to the other series investigated with this research study. The experimental results in terms of applied load vs mid-span deflection for this series is illustrated in Fig. 11.The control specimen SO4-1 failed as a result of shear compression at a total applied load of 130 kN. Specimen SO4-2, strengthened with CFRP strips, the failure was controlled by CFRP debonding at a total load of 255 kN with 96% increase in shear capacity over the control specimen SO4-1. The maximum local CFRP vertical strain measured at failure was 0.0062mmymm.When comparing the test results of specimen SO4-2 to that of specimen SO3-2, theenhanced shear capacity of specimen SO4-2 (a/d=4) due to addition of CFRP strips was 62.5 kN, while specimen SO3-2 (a/d=3) resulted in added shear capacity of 54 kN. As expected, the contribution of CFRP reinforcement to resist the shear appeared to decrease with decreasing a/d ratio. Specimen SO4-3, strengthened with continuous U- wrap, failed as a result of concrete splitting at an applied load of 310 kN with a 138% increase in shear capacity compared to that of specimen SO4-1. The maximum local CFRP vertical strain measured at failure was 0.0037 mm/mm.4. Design approachThe design approach for computing the shear capacity of RC beams strengthened with externally bonded CFRP reinforcement, expressed in ACI design code [12] format, was proposed and published in 1998 [13]. The design model described two possible failure mechanisms of CFRP reinforcement namely: CFRP fracture; and CFRP debonding. Furthermore, two limits on the contribution of CFRP shear were proposed. The first limit was set to control the shear crack width and loss of aggregate interlock, and the second was to preclude web crushing. Also, the concrete strength and CFRP wrap- ping schemes were incorporated as design parameters. In recent study [9,10], modifications were proposed to the 1998 design approach to include results of a new study on bond mechanism between CFRP sheets and concrete surface [14]. In addition, the model was extended to provide the shear design equations in Eurocode as well as ACI format. Comparing with all test results available in the literature to date, 76 tests, the design approach showed acceptable and conservative estimates [10,13]. In this section, the summary of the design approach is presented. The comparison between experimental results and the calculated factored shear strength demonstrates the ability of the design approach to predict the shear capacity of the strengthened beams. demonstrates the ability of the design approach to predict the shear capacity of the strengthened beams.4.1. Summary of the shear design approach — ACI formatIn traditional shear design (including the ACI Code), the nominal shear strength of an RC section is the sum of the nominal shear strengths of concrete and steel shear reinforcement. For beams strengthened with externally bonded FRP reinforcement,the shear strength may be computed by the addition of a third term to account of the FRP contribution. This is expressed as follows:The design shear strength,n V φ, is obtained by multiplying the nominal shear strength by a strength reduction factor for shear,φ. It was suggested that the reduction factor φ=0.85 given in ACI [12] be main-tained for the concrete and steel terms. However, a more stringent strength reduction factor of 0.7 for the CFRP contribution was suggested w10x. This is due to the relative novelty of this repair technique. Thus, the design shear strength is expressed as follows.4.2. Contribution of CFRP reinforcement to the shear capacityThe expression used to compute shear contribution of CFRP reinforcement is given in Eq. (3). This equation is similar to that for shear contribution of steel stirrups and consistent with the ACI format.The area of CFRP shear reinforcement,f A , is the total thickness of the sheet (usually f t 2or sheets on both sides of the beam) times the width of the CFRP stripf ω. The dimensions used to define the area of CFRP in addition to the spacingf s and the effective depth of CFRP,f d , are shown in Fig. 12. Note that for continuous verticalshear reinforcement, the spacing of the strip,f s , and the width of the strip, f ω, areequal. In Eq. (3), an effective average CFRP stressfe f , smaller than its ultimate strength,fu f , was used to replace the yield stress of steel. At the ultimate limit state for the member in shear, it is not possible to attain the full strength of the FRP [7,13]. Failure is governed by either fracture of the FRP sheet at average stress levels wellbelow FRP ultimate capacity due to stress concentrations, debonding of the FRP sheet from the concrete surface, or a significant decrease in the post- cracking concrete shear strength from a loss of aggregate interlock. Thus, the effective average CFRP stress is computed by applying a reduction coefficient, R, to the CFRP ultimate strength as expressed in Eq. (4).The reduction coefficient depends on the possible failure modes (either CFRP fracture or CFRP debonding). In either case, an upper limit for the reduction coefficient is established in order to control shear crack width and loss of aggregate interlock.4.3. Reduction coefficient based on CFRP sheet fracture failureThe proposed reduction coefficient was calibrated on all available test results to date, 22 tests with failure controlled by CFRP fracture [10,13]. The reduction coefficient was established as a function off f E ρ (where f ρis the area fraction of CFRP) and expressed in Eq.(5) for ≤f f E ρ0.7 GPa.4.4. Reduction coefficient based on CFRP debonding failureThe shear capacity governed by CFRP debonding from the concrete surface was presented [9,10]as a function of CFRP axial rigidity, concrete strength, effective depth of CFRP reinforcement, and bonded surface configurations. In determining the reduction coefficient for bond, the effective bond length, e L , has to be determined first. Based on analytical and experimental data from bond tests, Miller [14] showed that the effective bond length slightly increases as CFRP axial rigidity,f f E t , increases. However, he suggested a constant conservative value e L for equal to 75 mm. The value may be modified when more bond tests data becomes available.After a shear crack develops, only that portion of the width of CFRP extending past the crack by the effective bonded length is assumed to be capable of carrying shear.[13] The effective width,fe W , based on the shear crack angle of 45°, and thewrapping scheme is expressed in Eqs. (6a) and (6b);if the sheet in the form of a U-wrap (6a)if the sheet is bonded only to the sides of the beam. (6b)The final expression for the reduction coefficient, R, for the mode of failure controlled by CFRP debonding is expressed in Eq. (8)Eq. (7) is applicable for CFRP axial rigidity, f f E t , ranging from 20 to 90 mm-GPa (kN/mm). Research into quantifying the bond characteristics for axial rigidities above 90 mm·GPa is being conducted at the University of Missouri, Rolla (UMR).4.5. Upper limit of the reduction coefficientIn order to control the shear crack width and loss of aggregate interlock, an upper limit of reduction coefficient, R, was suggested and calibrated with all of the available test results [10] to be equal to fu ε/006.0where fu εis the ultimate tensile CFRP strain. This limit is such that the average effective strain in CFRP materials at ultimate can not be greater than 0.006 mm/mm (without the strengthening reduction factor,φ).4.6. Controlling reduction coefficientThe final controlling reduction coefficient for the CFRP system is taken as the lowest value determined from the two possible modes of failure and the upper limit. Note that if the sheet is wrapped entirely around the beam or an effective end anchor is used, the failure mode of CFRP debonding is not to be considered. The reduction coefficient is only controlled by FRP fracture and the upper limit.4.7. CFRP spacing requirementsSimilar to steel shear reinforcement, and consistent with ACI provision for the stirrups spacing [12], the spacing of FRP strips should not be so wide as to allow the formation of a diagonal crack without intercepting a strip. For this reason, if strips are used, they should not be spaced by more than the maximum given in Eq. (8).4.8. Limit on total shear reinforcementACI 318M-95 [12] 11.5.6.7 and 11.5.6.8 set a limit on the total shear strength that may be provided by more than one type of shear reinforcement to preclude the webcrushing. FRP shear reinforcement should be included in this limit. A modification to ACI 318M-95 Section 11.5.6.8 was suggested as follows:4.9. Shear capacity of a CFRP strengthened section — Eurocode formatThe proposed design equation wEq. (3)x for computing the contribution of externally bonded CFRP reinforcement may be rewritten in Eurocode (EC2 1992) [15] format as Eq. (10).In this equation, the partial safety factor for CFRP materials,f , was suggestedequal to 1.3 [10].4.10. Comparison between the test results and calculated valuesThe test summary and the comparison between the test results and the calculated shear strength, using the design approach (ACI format), are detailed in Tables 2 and 3, respectively. For CFRP strengthened beams, the measured contribution of concrete, Vc , and steel stirrups, Vs, (when present) were considered equal to the shearstrength of a non-strengthened beam. The nominal shear strength provided by concrete and steel stirrups was computed using Equations (11-5) and (11-15) in ACI- 318-95 [12]. In Equation (11-5), the values of Vu and M u were taken at the point of application of the load. The comparison indicates that the design approach gives conservative results for the strengthened beams as illus-trated in Fig. 13.5. Conclusions and further recommendationAn experimental investigation was conducted to study the shear behavior and the modes of failure of simply supported rectangular section RC beams with shear deficiencies, strengthened with CFRP sheets. The parameters investigated in this program were existence of steel shear reinforcement, shear span-to-effective depth ratio (ayd ratio), and CFRP amount and distribution.The results confirm that the strengthening technique using CFRP sheets can be used toincrease significantly shear capacity, with efficiency that varies depending on the tested variables. For the beams tested in this program, increases in shear strength of 40–138% were achieved.Conclusions that emerged from this study may be summarized as follows:●The contribution of externally CFRP reinforcement to the shear capacity isinfluenced by the a/d ratio.●Increasing the amount of CFRP may not result in a proportional increase in theshear strength. The CFRP amount used to strengthen specimen SO3-4 was 250% of that used in specimen SO3-2, which resulted in a minimal (10%) increase in shear capacity. An end anchor is recommended if FRP debonding is to be avoided. Table2Table3●The test results indicated that contribution of CFRP benefits the shear capacity at agreater degree for beams without shear reinforcement than for beams with adequate shear reinforcement.●The results of series SO3 indicated that the 0° ply improved the shear capacity byproviding horizontal restraint.●The shear design algorithms provided acceptable and conservative estimates forthe strengthened beams. Recommendations for future research are as follows:●Experimental and analytical investigations are required to link the shearcontribution of FRP with the load condition. These studies have to consider both the longitudinal steel reinforcement ratio and the concrete strength as parameters.Laboratory specimens should maintain practical dimensions.●The strengthening effectiveness of FRP has to be addressed in the cases of shortand very short shear spans in which arch action governs failure.●The interaction between the contribution of external FRP and internal steel shearreinforcement has to be investigated.●To optimize design algorithms, additional specimens need to be tested withdifferent CFRP amount and configurations to create a large database of information.●Shear design algorithms need to be expanded to include strengthening with aramid。

英文翻译原文

a r t i c l e

i n f o

a b s t r a c t

The influence of cerium addition on tensile and creep properties of ZA104 and ZA104 + 0.3Ca magnesium alloys containing between 0 wt.% and 3.5 wt.% Ce were evaluated and compared to those of AZ91D alloy. It was shown that cerium slightly decreases the ductility but increases the yield strength of ZA104 alloy. The influence of cerium on room temperature properties remains modest for concentration up to 2.6 wt.% in ZA104 + 0.3Ca alloy. The creep strength of the ZA104 alloy is clearly improved by the addition of a minor amount of cerium. But this effect is much less pronounced for ZA104 + 0.3Ca alloy. Variations of the properties of alloys were discussed considering the presence of two new intermetallic phases (Al5 Zn3 Ce2 and Al6 Zn2 Ce2 ) in the microstructure and also the reactions that occurred during solidification. © 2010 Elsevier B.V. All rights reserved.

中英文互译文章

中英文互译文章翻译是在特定社会文化背景下的交流过程,是一种特殊创作。

不少中英文互译的文章对提高读者英语水平有一定的帮助。

下面就是店铺给大家整理的中英文互译文章,希望大家喜欢。

中英文互译文章篇1:On leadership论领导What is leadership?什么是领导?Its qualities are difficult to define. But they are not so difficult to identity.领导应具备什么样的素质,这很难精确的解说,但辨认直陈却也不难。

Leaders don’t force other people to go along with them. They bring them along. Leaders getcommitment from others by giving it themselves, by building an environment that encouragescreativity, and by operating with honesty and fairness.领导者不强制别人与自己协调一致,而是帮助他们跟上。

领导者让别人承担义务,首先自己承担义务,造成一种能鼓励创造的环境,待人诚恳,处事公正。

Leaders demand much of others, but also much of themselves. They are ambitions- not only forthemselves, but also for those who work with them. They seek to attract, retain and developother people to their full abilities.领导者对人要求很多,同时也给人很多。

他们有雄心壮志,不仅为自己,也为和他们一道工作的人。

英文翻译原文