第4章 几何设计规则

人教版七年级上册第4章《几何图形初步》填空题专项训练

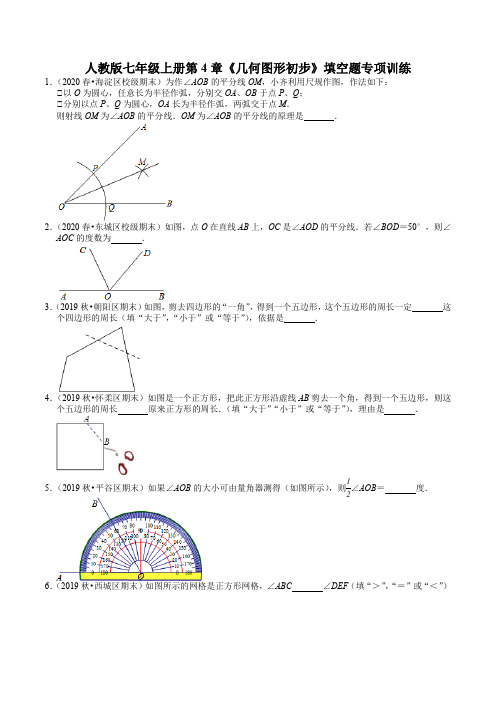

人教版七年级上册第4章《几何图形初步》填空题专项训练1.(2020春•海淀区校级期末)为作∠AOB 的平分线OM ,小齐利用尺规作图,作法如下: ①以O 为圆心,任意长为半径作弧,分别交OA 、OB 于点P 、Q ;①分别以点P 、Q 为圆心,OA 长为半径作弧,两弧交于点M .则射线OM 为∠AOB 的平分线.OM 为∠AOB 的平分线的原理是 .2.(2020春•东城区校级期末)如图,点O 在直线AB 上,OC 是∠AOD 的平分线.若∠BOD =50°,则∠AOC 的度数为 .3.(2019秋•朝阳区期末)如图,剪去四边形的“一角”,得到一个五边形,这个五边形的周长一定 这个四边形的周长(填“大于”,“小于”或“等于”),依据是 .4.(2019秋•怀柔区期末)如图是一个正方形,把此正方形沿虚线AB 剪去一个角,得到一个五边形,则这个五边形的周长 原来正方形的周长.(填“大于”“小于”或“等于”),理由是 .5.(2019秋•平谷区期末)如果∠AOB 的大小可由量角器测得(如图所示),则12∠AOB = 度. 6.(2019秋•西城区期末)如图所示的网格是正方形网格,∠ABC ∠DEF (填“>”,“=”或“<”)7.(2019秋•海淀区期末)如图,已知空间站A与星球B距离为a,信号飞船C在星球B附近沿圆形轨道行驶,B,C之间的距离为b.数据S表示飞船C与空间站A的实时距离,那么S的最大值是.8.(2019秋•北京期末)体育课上,小聪,小明,小智,小慧分别在点O处进行了一次铅球试投,铅球分别落在图中的点A,B,C,D处,则他们四人中,成绩最好的是.9.(2019秋•房山区期末)如图,OB平分∠AOC,OD平分∠COE,∠AOD=120°,∠BOD=70°,则∠COE的度数为.10.(2019秋•平谷区期末)计算:90°﹣18°35'=.11.(2019秋•朝阳区期末)如图,B是线段AC上一点,D,E分别是线段AB,AC的中点,若AB=1,BC =3,则DE=.12.(2019秋•东城区期末)如图,某海域有三个小岛A,B,O,在小岛O处观测到小岛A在它北偏东60°的方向上,观测到小岛B在它南偏东38°的方向上,则∠AOB的度数是.13.(2019秋•石景山区期末)如图,①~①展开图中,能围成三棱柱的是.14.(2019秋•丰台区期末)如图是某几何体的展开图,该几何体是.15.(2019秋•丰台区期末)如图所示的网格是正方形网格,∠BAC∠DAE.(填“>”,“=”或“<”)16.(2019秋•通州区期末)已知∠AOB=60°,以点O为端点作射线OC,使∠BOC=20°,再作∠AOC 的平分线OD,则∠AOD的度数为.17.(2019秋•延庆区期末)把56°36′换算成度的结果是.18.(2019春•海淀区校级期末)阅读下面材料.数学课上,老师提出如下问题:小明解答如图所示,其中他所画的弧MN是以E为圆心,以CD长为半径的弧老师说:“小明作法正确.”请回答小明的作图依据是:19.(2018秋•密云区期末)2018年是中国改革开放事业40周年,正在中国国家博物馆展出的《伟大的变革﹣﹣庆祝改革开放40周年大型展览》多角度、全景式集中展示中国改革开放40年的光辉历程、伟大成就和宝贵经验.小芳参展之后打算设计一个正方体装饰品,她在正方体的一个平面展开图上写下了“全面深化改革”几个字(如图所示),如果正方体上“深”所对的面为“改”,则“革”所对的面是.20.(2018秋•延庆区期末)如图所示,可以用量角器度量∠AOB的度数,那么∠AOB的度数为.21.(2018秋•昌平区期末)数学课上,老师要求同学们用一副三角板画一个钝角,并且画出它的角平分线.小丹的画法如下:①先按照图1的方式摆放一副三角板,画出∠AOB;①再按照图2的方式摆放一副三角板,画出射线OC;①图3是去掉三角板后得到的图形.老师说小丹的画法符合要求.请你回答:(1)小丹画的∠AOC的度数是;(2)射线OC是∠AOB的角平分线的依据是.22.(2018秋•丰台区期末)学习直线、射线、线段时,老师请同学们交流这样一个问题:直线上有三点A,B,C,若AB=6,BC=2,点D是线段AB的中点,请你求出线段CD的长.小华同学通过计算得到CD的长是5.你认为小华的答案是否正确(填“是”或“否”).你的理由是.23.(2018秋•房山区期末)将一副直角三角板如图所示摆放,则图中∠ABC的大小为°.24.(2018秋•石景山区期末)如图是一个长方体的图形,它的每条棱都是一条线段,请你从这些线段所在的直线中找出:(1)一对平行的线段:(写出一对即可);(2)一对不在同一平面内的线段:(写出一对即可).25.(2018秋•平谷区期末)如图,BD平分∠ABC,过点B作BE垂直BD,若∠ABC=40°,则∠ABE =°.26.(2018秋•通州区期末)从小华家去图书馆共有三条路,你认为第条路最短,理由是:.27.(2018秋•海淀区期末)图中A,B两点之间的距离是厘米(精确到厘米),点B在点A的南偏西°(精确到度).28.(2018秋•北京期末)如图是北京地铁的路线图,佳佳家住建国门,打算趁着新年放假去复兴门玩,看了路线图后,佳佳打算乘坐①号线地铁去,用几何知识解释他这样做的依据是.29.(2018秋•平谷区期末)将正方体骰子(相对面上的点数分别为1和6、2和5、3和4)放置于水平桌面上,如图1.将骰子向右翻滚90°,然后在桌面上按逆时针方向旋转90°,则完成一次变换.如图2.若骰子的初始位置为图1所示的状态,那么按上述规则连续完成2次变换后,骰子朝上一面的点数是;连续完成2019次变换后,骰子朝上一面的点数是.30.(2018秋•昌平区期末)现在人们锻炼身体的意识日渐增强,但是一些人保护环境的意识却很淡薄.如图是昌平滨河公园的一角,有人为了抄近道而避开横平竖直的路,走“捷径AC”,于是在草坪内走出了一条不该有的“路线AC”.请你用数学知识解释出现这一现象的原因是.31.(2018秋•海淀区期末)如图,点O在直线AB上,射线OD平分∠COA,∠DOF=∠AOE=90°,图中与∠1相等的角有(请写出所有答案).32.(2017秋•海淀区校级期末)如图,将一副三角板按如图所示位置摆放,请你选择一幅图,并写出α与β的数量关系,你选择的图是,此时α与β的数量关系是.33.(2017秋•海淀区校级期末)如图,将甲,乙两把尺子拼在一起,两端重合,如果甲尺经校订是直的,那么乙尺(填是或者不是)直的,判断依据是.34.(2017秋•海淀区校级期末)如图,点C,D,E在线段AB上,线段AB=12,C是线段AB上靠近点A 的三等分点.点E为线段BD的中点,且图中所有线段的长度和是线段AD的长度的10倍,则CD的长度为.35.(2017秋•海淀区校级期末)如图所示,O为直线AB上一点,OC平分∠AOE,∠DOE=90°,则以下结论正确的有.(只填序号)①∠AOD与∠BOE互为余角;①OD平分∠COA;①∠BOE=56°40′,则∠COE=61°40′;①∠BOE=2∠COD.36.(2018春•平谷区期末)在数学课上,老师提出如下问题:尺规作图:过直线外一点作已知直线的垂线.已知:如图1,直线l及其外一点A.求作:l的垂线,使它经过点A.小云的作法如下:(1)在直线l上任取一点B,连接AB;(2)以A为圆心,AB长为半径作弧,交直线l于点D;(3)分别以B、D为圆心,AB长为半径作弧,两弧相交于点C;(4)作直线AC.直线AC即为所求(如图2).小云作图的依据是.参考答案与试题解析一.填空题(共36小题)1.【解答】解:如图,连接PM ,PQ .∵OP =OQ ,PM =QM ,OM =OM ,∴△POM ≌△QOM (SSS ),∴∠POM =∠QOM ,即OM 是∠AOB 的角平分线.故答案为SSS .2.【解答】解:∵点O 在直线AB 上,∴∠AOD +∠BOD =180°,∵∠BOD =50°,∴∠AOD =180°﹣∠BOD =180°﹣50°=130°,∵OC 是∠AOD 的平分线,∴∠AOC =12∠AOD =12×130°=65°, 故答案为:65°.3.【解答】解:剪去四边形的“一角”,得到一个五边形,则这个五边形的周长一定小于这个四边形的周长, 理由是两点之间线段最短.故答案为:小于;两点之间线段最短.4.【解答】解:将正方形沿虚线裁去一个角得到五边形,则这个五边形的周长小于原来正方形的周长, 理由是两点之间线段最短.故答案为:小于;两点之间线段最短.5.【解答】解:由题可得,∠AOB =60°,∴12∠AOB =12×60°=30°,故答案为:30.6.【解答】解:由图可得,∠ABC =45°,∠DEF <45°,∴∠ABC >∠DEF ,故答案为:>.7.【解答】解:空间站A 与星球B 、飞船C 在同一直线上时,S 取到最大值a +b .故答案为:a +b .8.【解答】解:由图可得,OC >OD >OB >OA ,∴表示最好成绩的点是点C ,故答案为:小智(或点C ).9.【解答】解:∵∠AOD =120°,∠BOD =70°,∴∠AOB =∠AOD ﹣∠BOD =50°,∵OB 平分∠AOC ,∴∠BOC =∠AOB =50°,∴∠COD =∠BOD ﹣∠BOC =20°,∵OD 平分∠COE ,∴∠COE =2∠COD =40°.故答案为40°.10.【解答】解:90°﹣18°35'=71°25′.故答案是:71°25′.11.【解答】解:∵AB =1,BC =3,∴AC =AB +BC =1+3=4,∵D ,E 分别是线段AB ,AC 的中点,∴AD =12AB =12,AE =12AC =2,∴DE =AE ﹣AD =32,故答案为:32.12.【解答】解:∵OA 是表示北偏东60°方向的一条射线,OB 是表示南偏东38°方向的一条射线, ∴∠AOB =180°﹣60°﹣38°=82°,故答案是:82°.13.【解答】解:图①能围成圆锥;图①能围成三棱柱;图①能围成正方体;图①能围成四棱锥; 故答案为:①.14.【解答】解:观察图形可知,这个几何体是三棱柱.故答案为:三棱柱15.【解答】解:如图所示,连接DF ,AF ,则△ADF 是等腰直角三角形,∴∠DAF =45°>∠DAE ,又∵∠BAC =45°,∴∠BAC >∠DAE ,故答案为:>.16.【解答】解:(1)当OC 在∠AOB 的内部时,如图1所示:∵∠BOC =20°,∠AOB =60°,∠AOB =∠AOC +∠BOC ,∴∠AOC =60°﹣20°=40°,又∵OD 是∠AOC 的平分线,∴∠AOD =∠COD =12∠∠∠∠=20°;(2)当OC 在∠AOB 的外部时,如图2所示:∵∠AOC=∠AOB+∠BOC,∠AOB=60°,∠BOC=20°,∴AOC=80°,又∵OD是∠AOC的平分线,∴∠AOD=∠COD=12∠∠∠∠=40°;综合所述∠AOD的度数有两个,故答案为20°或40°.17.【解答】解:56°36′,=56°+(36÷60)°,=56.6°.18.【解答】解:由作法得OC=OD=BE=BF,EF=CD,所以△BEF≌△OCD(SSS).所以∠EBF=∠COD,故答案为SSS.19.【解答】解:∵正方体的平面展开图中,相对面的特点是之间一定相隔一个正方形,∴在此正方体上与字母“革”所对的面是全.故答案为:全.20.【解答】解:由图形所示,∠AOB的度数为55°,故答案为:55°21.【解答】解:∵(1)由图1可知∠AOB=60°+90°=150°,图2可知∠COB=30°+45°=75°,∴∠AOC=∠AOB﹣∠BOC=150°﹣75°=75°.故答案为75°.(2)由(1)可知∠AOC=∠BOC,根据角平分线的定义可知射线OC是∠AOB的角平分线.故答案为:角平分线定义.22.【解答】解:如图1,∵AB=6,点D是线段AB的中点,∴DB=3,又BC=2,∴DC=5;如图2,∵AB=6,点D是线段AB的中点,∴DB=3,又BC=2,∴DC=1,∴小华的答案不正确,因为线段DC的长为1或5,故答案为:否;当点C在线段AB上时,CD=1或5.23.【解答】解:∵∠ABD=45°,∠CBD=30°∴∠ABC=45°+30°=75°故答案为:75.24.【解答】解:(1)答案不唯一,如:AB∥FG;(2)答案不唯一,如:AD与BG.故答案为:AB∥FG;AD与BG.25.【解答】解:∵BD平分∠ABC,∠ABC=40°,∴∠ABD=12∠ABC=20°,∵BE垂直BD,∴∠DBE=90°,∴∠ABE=∠DBE﹣∠ABD=70°,故答案为:70.26.【解答】解:从小华家去图书馆共有三条路,选择第①条路最短,理由:两点之间线段最短.故答案为:①,两点之间线段最短.27.【解答】解:测量可得,图中A,B两点之间的距离是2厘米(精确到厘米),点B在点A的南偏西58°(精确到度).故答案为:2,58.28.【解答】解:由图可得,他这样做的依据是:两点之间,线段最短.故答案为:两点之间,线段最短.29.【解答】解:根据题意可知,连续3次变换是一循环.完成1次变换后,骰子朝上一面的点数是5;完成2次变换后,骰子朝上一面的点数是6;完成3次变换后,骰子朝上一面的点数是3,因为2019÷3=673,所以连续完成2019次变换后,骰子朝上一面的点数是3.故答案为:6,3.30.【解答】解:为了抄近道而避开横平竖直的路,走“捷径AC”,用数学知识解释出现这一现象的原因是两点之间,线段最短.故答案为两点之间,线段最短.31.【解答】解:∵射线OD平分∠COA,∴∠COD=∠1.∵∠DOF=∠AOE=90°,∴∠DOE+∠EOF=90°,∠DOE+∠1=90°,∴∠EOF=∠1.∴图中与∠1相等的角有∠COD,∠EOF.故答案为∠COD,∠EOF.32.【解答】解:图形(1)中,α+β=90°;图形(2)中,α+β=45°+30°=75°;图形(3)中,α=β;图形(4)中,α+β=180°.故答案为(1);α+β=90°.33.【解答】解:∵甲尺是直的,两尺拼在一起两端重合,∴甲尺经校订是直的,那么乙尺就一定不是直的,判断依据是:两点确定一条直线.故答案为:不是,两点确定一条直线.34.【解答】解:∵AB =12,C 是线段AB 上靠近点A 的三等分点. ∴AC =13AB =4,BC =8,设CD =x ,则AD =4+x ,BD =8﹣x , ∵点E 为线段BD 的中点, ∴DE =BE =12BD =4−12x ,∴AE =AD +DE =8+12x ,∴CE =CD +DE =4+12x ,∴AC +AD +AE +AB +CD +CE +CB +DE +BD +EB =4+4+x +8+12x +12+x +4+12x +8+4−12x +8﹣x +4−12x =10×(4+x ),解得:x =169, ∴CD 的长度为169. 故答案为:169.35.【解答】解:∵∠DOE =90°,∴∠COD +∠COE =90°,∴∠EOB +∠DOA =90°,故①正确;∵OC 平分∠AOE ,∴∠AOE =2∠COE =2∠AOC ;∵∠BOE =180°﹣2∠COE ,∵∠COD =90°﹣∠COE ,∴∠BOE =2∠COD ,∠AOD =90°﹣∠BOE ,故①不正确,①正确;若∠BOE =56°40′,∵∠AOE +∠BOE =180°,∴∠COE =12(180°﹣∠BOE )=12(180°−56°40′)=61°40′. 故①正确;∴①①①正确.故答案为:①①①.36.【解答】解:由作法得AB =AD =BC =DC ,则四边形ABCD 为菱形, 所以AC ⊥BD .故答案为:四条边都相等的四边形是菱形;菱形的对角线互相垂直.。

CMOS版图

第4章 CMOS版图

第4章 CMOS版图

利用spice去确定器件尺寸

电路设计规范specs——设计的起点,电路 的性能要求(例如:电流、频率、电压增益 等等) 根据采用的特定工艺的详细信息,电路设 计规范定义了基本器件尺寸。

4.2.8 焊盘层

焊盘提供了芯片内部信号到封装接脚的 连接,其尺寸通常定义为绑定导线需要的 最小尺寸。

第4章 CMOS版图

版图设计注意事项

1、无论在电路图中还是在版图中,PMOS晶体管都与VDD相连 接; 2、在电路图和版图中,NMOS晶体管都与VSS相连接;

3、在电路图和版图中,NMOS晶体管和PMOS晶体管的栅极有 相同的IN信号,而其漏极有相同的OUT信号;

第4章 CMOS版图

图4.7 第一层通孔的图示

第4章 CMOS版图

4.2.7 文字标注层

文字标注层用于版图中的文字标注,目 的是方便设计者对器件、信号线、电源线、 地线等进行标注,便于版图的查看,尤其 在进行验证的时候,便于查找错误的位置。 在进行版图制造的时候并不会生成相应的 掩膜层。

第4章 CMOS版图

第4章 CMOS版图

4.2 版图中的绘图层

绘图层是指完成集成电路的版图设计所需 要的最少分层数目。我们以N阱CMOS工艺为 例,通常情况下,绘图层的种类有:N阱层(N Well)、有源区层(Active)、多晶硅栅层(Poly)、 P选择层(P Select)、N选择层(N Select)、接触 孔层(Contact)、通孔层(Via)、金属层(Metal)、 文字标注层(Text)和焊盘层(Pad)。

初二数学:上册第四章几何图形初步直线射线与线段导学案新人教

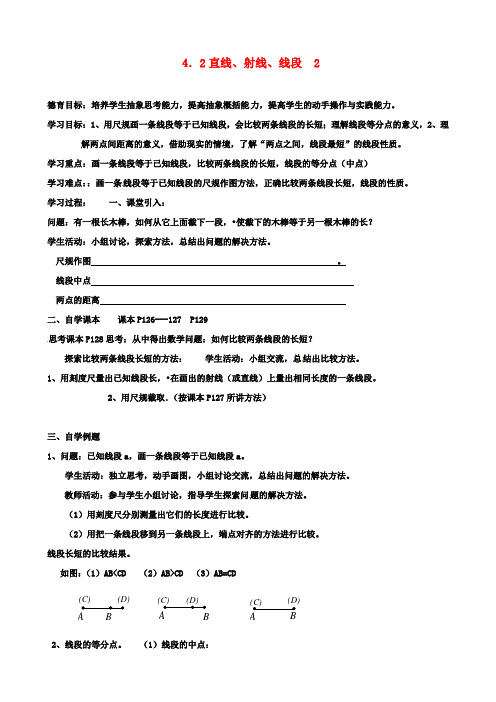

4.2直线、射线、线段 2德育目标:培养学生抽象思考能力,提高抽象概括能力,提高学生的动手操作与实践能力。

学习目标:1、用尺规画一条线段等于已知线段,会比较两条线段的长短;理解线段等分点的意义,2、理解两点间距离的意义,借助现实的情境,了解“两点之间,线段最短”的线段性质。

学习重点:画一条线段等于已知线段,比较两条线段的长短,线段的等分点(中点)学习难点::画一条线段等于已知线段的尺规作图方法,正确比较两条线段长短,线段的性质。

学习过程: 一、课堂引入:问题:有一根长木棒,如何从它上面截下一段,•使截下的木棒等于另一根木棒的长? 学生活动:小组讨论,探索方法,总结出问题的解决方法。

尺规作图 。

线段中点 两点的距离 二、自学课本 课本P126---127 P129思考课本P128思考:从中得出数学问题:如何比较两条线段的长短?探索比较两条线段长短的方法: 学生活动:小组交流,总结出比较方法。

1、用刻度尺量出已知线段长,•在画出的射线(或直线)上量出相同长度的一条线段。

2、用尺规截取.(按课本P127所讲方法)三、自学例题1、问题:已知线段a ,画一条线段等于已知线段a 。

学生活动:独立思考,动手画图,小组讨论交流,总结出问题的解决方法。

教师活动:参与学生小组讨论,指导学生探索问题的解决方法。

(1)用刻度尺分别测量出它们的长度进行比较。

(2)用把一条线段移到另一条线段上,端点对齐的方法进行比较。

线段长短的比较结果。

如图:(1)AB<CD (2)AB>CD (3)AB=CD(D)(C)BABA(D)(C)A2、线段的等分点。

(1)线段的中点:教师活动:取线段AB 上一点M ,移动线段AM 到线段MB 上,当AM•与MB 完全重合时,线段AM=MB ,此时点M 就叫做线段AB 的中点。

AM=MB=12AB(2)线段的等分点: 通过类比线段的中点,可得出线段的三等分点、四等分点.N MBAN MPBAAM=MN=NB=13 AB AM=MN=NP=PB=14AB3、线段的性质 (1)完成课本P128思考 由这个思考题,你能得出线段的性质? 小组讨论,得出线段的性质:两点之间,线段最短。

第四章pkpm绘制混凝土结构施工图

搭接长度 2Φ25角筋

搭接长度

2Φ22

2Φ12通长筋

2Φ25角筋 2Φ25

集中标注内容:

截面注写方式:在分标准层绘制的剪力墙平面布置图 上,以直接在墙柱、墙身、墙梁上注写截面尺寸和配 筋具体数值的方式来表达。

剪力墙平法施工图列表注写方式示例

剪力墙平法施工图列表注写方式示例

剪力墙平法施工图截面注写方式示例

梁侧面纵向构造钢筋或受扭钢筋配置: 当腹板高度hw≥450mm时,须根据规范规定配置纵向构造钢筋。

此项注写值以大写字母G打头,注写设置在梁两个侧面的总配筋值, 且对称配置。

当梁侧面须配置受扭纵筋时,此项注写以大写字母N打头,后 面注写设置在梁两个侧面的总配筋值,且对称配置。受扭纵筋和构 造纵筋不重复配置。

集中标内容:

梁箍筋:包括钢筋级别、直径、加密区与非加密区间距及肢距。 如:φ8@100/200(2)表示箍筋为φ8,加密区和非加密区间距分别 为100和200,均为双肢箍。

φ8@100 (4) /150(2)表示加密区间距为100,四肢箍,非加 密区间距为150,双肢箍。

集中标注内容:

梁上部通长筋或架力筋

平面注写与传统表示方法对比

梁平法施工图截面注写方式示例

3. 剪力墙平法施工图制图规则

列表注写方式:为表达清楚、简便,剪力墙可视为由 剪力墙柱、剪力墙身和剪力墙梁三类构件构成。分别 在剪力墙柱表、剪力墙身表、剪力墙梁表中,对应于 平面布置图上的编号,用绘制截面配筋图并注写几何 尺寸与配筋具体数值的方式来表达。

第114节课内部空间4-1,4-2-课件

▪ (1)决定空间组织的重要依据:人在建筑中的活动

▪ (2)按人的活动要求对空间分类:流通空间与滞留空间、 公共空间与私密空间、主导空间与从属空间

▪ 3)空间组织的形式:并列关系、序列关系、主从关系、 综合关系

空间组织的关系:并列关系

并列关系

空间组织的关系:序列关系

序列关系

空间组织的关系:主从关系

▪ 柏拉图体是简洁而完美的形势,具有高度的视觉可知性, 常为建筑创作的构成要素

②不规则形体

▪ 不规则形体多是打破平衡而显得 比规则体更富有动态,常是为间的比例和尺度

▪ 比例—是空间隔构成要素之间的数量关系;

▪ 尺度—是空间构成要素与人体之间的数量关系。

▪ 人们处在形状相同的空间中,由于比例和尺度的变化所 带来的视觉感受是不同的。建筑空间中包含大概五种不 同比例和尺度的空间类型:

主从关系

空间组织的关系:综合关系

综合关系

§4-2 单一空间

▪ 4.2.1空间的限定要素

▪ 4.2.2 空间形状

▪ 4.2.3空间的比例和尺度

▪ 4.2.4空间的围与透 ▪ 4.2.5空间界面的处理 ▪ 4.2.6 空间中的光

4.2.1 空间的限定要素

▪ 在同样的功能要求下,采用不同的空间处 理手法,可表现为不同的结果和不同的性 格特点。

1、亲和空间

2、高狭空间 3、轴向空间

4、开阔空间

5、巨型空间

▪ 室内空间的尺度要与房间的功能性质相一致;房间的高 度对于尺度的影响要比宽度和长度的影响强烈,顶棚的 相对高度更能决定空间的视觉品质。

1、亲和空间

接近人体尺度的低小空间,有一种亲切感和可居性,具有宁静、亲切地感觉。

2、高狭空间

机械测量技术-几何公差形状、方向、位置和跳动公差

第四章 几何公差 形状、方向、位置和跳动公差

二、形位公差项目及符号 国家标准规定了14项形位公差,其名称、符号以及分类见表4⁃1。

表4-1 形位公差的分类与基本符号(GB/T 1182—2008)

第四章 几何公差 形状、方向、位置和跳动公差

三、形位公差的意义和要素 对产品的功能要求,除尺寸公差外,还要对产品的形位公差提出

态,且其对应中心要素的形状或位置误差等于图样上标注的形位公差时 的综合极限状态。

最大实体实效状态对应的体外作用尺寸称为最大实体实效尺寸MMVS。 轴和孔的最大实体实效尺寸分别用符号dMV和DMV表示。 dMV= dmax+t M DMV=Dmin-t M

• 6、最小实体实效状态和最小实体实效尺寸 最小实体实效状态MMVC是指实际要素在给定长度上处于

要求。 1)公差带的形状常用的有9种,见表4-2。 2)公差带的大小指公差带的宽度t或直径ϕt,如表4-2中所示,t即公差 值;取值大小取决于被测要素的形状和功能要求。 3)公差带的方向即评定被测要素误差的方向。 4)公差带的位置,形状公差带没有位置要求,只用来限制被测要素 的形状误差。

第四章 几何公差 形状、方向、位置和跳动公差

(2)实际(组成)要素。由接近实际(组成)要素所限定的工件实际 表面的组成要素部分。 如图(b)所示。 实际(组成)要素是实际存在并将整个工件与周围介质分隔的要素。它由

无数个连续点构成,为非理想要素。

几何要素定义之间的相互关系

4.提取组成要素与提取导出要素 (1)提取组成要素。按规定方法,由实际(组成)要素提取有限数目 的点所形成的实际(组成)要素的近似替代,如图(c)所示。 (2)提取导出要素。由一个或几个提取组成要素得到的中心点、中心 线或中心面,如图(c)所示。 提取(组成、导出)要素是根据特定的规则,通过对非理想要素提取

自由度几何组成分析规则

§2-1 几何构成份析基本概念

Structural Mechanics

y

y

B

A(x y)

A(x y)

x

x

3.联络(约束):限制非自由体运动装置

体系旳自由度因加入约束装置而降低,使体系 降低一种自由度旳装置称为一种约束,或叫做一种 联络,降低n个自由度旳装置,叫n个联络。→加入 足够联络,可变体系将成为几何不变。

4.固定支座或刚结点:降低三个自由度。

§2-1 几何构成份析基本概念

5.单刚结 、复刚结(P.15)

A

B

C

E

B

D

CF

Structural Mechanics

A

联结n个刚片间旳刚结点相当于(n-1)个单刚结点(P.16)

6.单链杆、复链杆 一般来说,联结n个点旳复链杆相当于(2n-3)个单链

杆(P.16)

§2-3 几何构成构成规则

5.三刚片规则旳本质: (三角形规则)

三根杆件用三个铰连接而成旳铰接三角形是几何

Structural Mechanics

不变体系。这种三角形往往是以“虚”旳形式出现,

因为有虚铰。

A

A

A

A

例1:试用三条构成规 则,阐明三条构成规则 是相通旳。

II

II III

B CB CB CB C

可变P 1 4

2 P1 34

2

P2

P2

31

31

3

P2

1

3

P1 4

2 P1 34

2

P2

P2

31

31

3

《余角和补角》说课稿(精选6篇)

《余角和补角》说课稿《余角和补角》说课稿(精选6篇)作为一名辛苦耕耘的教育工作者,编写说课稿是必不可少的,借助说课稿可以更好地组织教学活动。

那么问题来了,说课稿应该怎么写?下面是小编收集整理的《余角和补角》说课稿,欢迎阅读与收藏。

《余角和补角》说课稿篇1一、说教材1、教材的地位和作用本节教材是华东师大版标准实验教科书初中数学七年级第四章的内容。

一方面,这是在学习了角的大小比较的基础上,对角之间关系的进一步深入和拓展;同时又为今后证明角的相等提供了一种依据和方法,起着承前启后的作用。

本节教材的编排特点是从生活中的实际问题体验数学问题,归纳数学理论,同时利用理论解决实际问题。

2、学情分析学生学习缺乏主动性,独立思维能力较差,动手操作能力相对稍强,能在教师引导下低起点、小步距进行探究。

整体逻辑思维能力正在从经验型逐步向理论型发展,初步具备了观察、思维以及想象的学习能力,爱发表见解,在教学中应抓住这些特点,一方面运用直观生动的形象,引发学生的兴趣;另一方面,要创造条件和机会,让学生发表见解,发挥学生学习的主动性。

二、教学目标知识目标:了解余角、补角的概念,掌握余角和补角的性质。

能力目标:使学生初步接触和体会演绎推理的方法和表述,使学生能用方程思想来处理图形的数量关系。

情感目标:通过探索互余、互补角的性质,培养学生积极的情感态度,促进良好的数学观的养成。

教学重难点教学重点:余角与补角的概念及性质教学难点:余角与补角的性质应用三、教学教法1、教法:本节课采用“学案导学法”教学。

这种教学方法遵循以“学生为主体,教师为主导,数学活动为主线”的指导思想,变被动学习为主动学习,并同时直观动态演示以突破学习难点。

2、学法:教师将预先编写好的导学学案,在课前发给学生,根据所教班级的学生的特点,采用“参照学案,自主阅读,独立思考,提出疑问,分组探究,合作学习,知识总结”的学习方式。

3、教学手段:采用多媒体课件辅助教学,增加课堂容量,提高教学效果。

材料力学第四章截面的几何性质

在材料力学中,剪切中心是剪切应力作用下截面 发生剪切变形的点。通过计算截面的形心,可以 近似确定剪切中心的位置。

确定截面的质心

质心是截面质量的中心点,通过计算截面的形心, 可以近似确定质心的位置,这对于动力学分析和 稳定性分析非常重要。

03 主轴和主惯性矩

主轴的定义与计算

主轴

截面上的各点处到截面形心距离最大的方向。

预测物体的变形和破坏

通过分析截面的几何性质,可以预测 物体在不同受力条件下的变形和破坏 行为,为工程实践提供指导。

02 截面的面积和形心

截面面积的定义与计算

截面面积的定义

截面面积是指通过截面边界轮廓 线围成的区域面积。

截面面积的计算

可以通过测量截面轮廓线的长度 ,然后使用公式计算面积。对于 不规则形状,可以使用微元法或 积分法计算。

截面几何性质的应用前景

随着科技的发展和工程需求的提高,截面几何性质在材料力学中的重要性将更加凸 显,其在航空航天、交通运输、建筑等领域的应用将更加广泛。

随着新型材料的不断涌现,截面几何性质的研究将有助于深入了解这些材料的力学 行为,为新型材料的优化和应用提供理论支持。

随着数值模拟和计算机技术的发展,截面几何性质的研究将更加精确和深入,有助 于提高工程结构的分析和设计水平。

在实际工程中,主轴和主惯性矩也是 进行有限元分析时的重要输入参数, 用于模拟结构的力学行为并优化设计。

在结构设计时,根据主轴和主惯性矩 可以合理地选择材料的类型和截面的 形状,以提高结构的刚度和稳定性。

04 极惯性矩和惯性积

极惯性矩的定义与计算

极惯性矩

截面对任意直径的极惯性矩等于截面 面积与该直径的平方的乘积。

截面是确定物体受力分布和变形程度 的关键因素,通过研究截面的几何性 质,可以深入了解物体的力学性能, 为工程设计和安全评估提供依据。

幼儿园大班《几何图形》教案(通用10篇)

幼儿园大班《几何图形》教案幼儿园大班《几何图形》教案(通用10篇)作为一名为他人授业解惑的教育工作者,往往需要进行教案编写工作,教案有助于顺利而有效地开展教学活动。

我们应该怎么写教案呢?以下是小编为大家整理的幼儿园大班《几何图形》教案(通用10篇),欢迎大家借鉴与参考,希望对大家有所帮助。

幼儿园大班《几何图形》教案篇1教学目标:1、进一步掌握几何图形的特征。

2、发展观察力、想象力和灵活的思维能力。

3、引导幼儿初步掌握日常生活中的几何图形。

4、能大胆、清楚地表达自己的见解,体验数学的快乐。

教学准备:1、三张白纸上分别画好几何图形。

2、儿人手一支铅笔、一个几何图形、一把剪刀、一张空白的纸以及一张画有几何图形的作业纸;每桌几何图形若干;擦手毛巾;糨糊。

3、用的几何图形一套(长方形、正方形、梯形、三角形、圆形、半圆形、椭圆形)教学过程:一、兴趣激发:1、师:今天,齐请来了一些朋友要来我们班作客,它们是谁呢?(师出示正方形、圆形)问:正方形有什么特点?圆形有什么特点?2、咦!有什么事让正方形、圆形娃娃这么高兴呢?原来今天它们要一起过生日。

许多朋友要来祝贺。

你们看!它们是谁?(师分别出示长方形、正方形、梯形、三角形、圆形、半圆形、椭圆形)3、师:哟!这么多客人,你们看看谁长得和正方形有些象呢?你们帮正方形娃娃找到了相象的朋友,那跟圆形相象的朋友在哪儿呢?我们也来帮它找找。

二、兴趣体验:(一)观察探索1、捉迷藏三角形虽然没有相象的朋友,但大家都愿意和它一起玩。

这会儿它们玩起了捉迷藏的游戏。

(1)找图形并填表格。

师巡回指导。

(2)说一说找到什么图形有几个。

师:小朋友真能干,躲在一起的长方形、正方形、梯形、三角形、圆形、半圆形、椭圆形都被你们找出来了。

(3)说一说在生活中这些几何图形喜欢躲在哪里?(二)趣味游戏1、变魔术现在齐要请小朋友来当魔术师,用这些图形变出许多小图形娃娃来。

(1)变魔术(大图形变小图形)(2)问:你能告诉我你用什么图形变成哪些小图形?2、拼图案师:你们变出这么多的图形娃娃,今天是正方形、圆形娃娃的生日。

2024秋八年级数学上册第4章实数4.1平方根3平方根教案(新版)苏科版

⑥ 课堂小结:回顾本节课的主要内容,强调平方根的重要性和意义,布置课后作业巩固学习效果。

教学评价与反馈

1. 课堂表现:

- 学生参与度:大部分学生能够积极参与课堂讨论,提出问题和建议。

- 学生理解度:学生对于平方根的定义和性质有较好的理解,能够运用到实际问题中。

2. 课程平台:学校提供的教学管理系统,如学习通、智慧课堂等。

3. 信息化资源:教学PPT、教学视频、在线练习平台、数学软件工具。

4. 教学手段:小组讨论、合作学习、问题引导、实例分析、练习巩固。

教学过程设计

1. 导入新课(5分钟)

目标:引起学生对平方根的兴趣,激发其探索欲望。

过程:

开场提问:“你们知道什么是平方根吗?它与我们的生活有什么关系?”

根据学生的学习者分析,教师可以针对学生的兴趣和能力进行教学设计,提供清晰的实例和练习,帮助学生克服困难和挑战,提高学生对平方根概念和性质的理解和应用能力。

学具准备

多媒体

课型

新授课

教法学法

讲授法

课时

第一课时

步骤

师生互动设计

二次备课

教学资源

1. 软硬件资源:多媒体投影仪、白板、黑板、粉笔、教学卡片、计算器。

过程:

简要回顾本节课的学习内容,包括平方根的基本概念、求法、性质及案例分析等。

强调平方根在现实生活或学习中的价值和作用,鼓励学生进一步探索和应用平方根。

布置课后作业:让学生撰写一篇关于平方根的应用案例报告,以巩固学习效果。

知识点梳理

1. 平方根的定义:一个正数的平方根是另一个数,它的平方等于这个正数。同样,一个负数的平方根也是一个数,它的平方等于这个负数。0的平方根是0。

画法几何与机械制图教案

画法几何与机械制图教案第一章:画法几何基础1.1 点、线、面的基本概念与性质点的定义与表示方法线的定义与表示方法面的定义与表示方法点、线、面的基本性质1.2 点、线、面的相互关系点与线的关系线与面的关系点与面的关系1.3 平行公理及其推论平行公理的定义与证明平行公理的推论与应用1.4 画法几何图形的绘制方法与技巧画点的方法与技巧画线的方法与技巧画面的方法与技巧第二章:机械制图基础2.1 制图标准与规范图纸的幅面与比例图线的类型与宽度文字、数字的书写要求2.2 视图与投影视图的分类与画法投影变换与投影规律组合体的投影与表达2.3 机械图样的标注与说明尺寸的标注与规则公差的表示与标注表面粗糙度的表示与标注2.4 机械制图的绘制方法与技巧绘制视图的方法与技巧标注的方法与技巧整洁与美观的制图习惯第三章:简单几何体的绘制3.1 平面几何体的绘制圆的绘制方法与技巧矩形的绘制方法与技巧正方形的绘制方法与技巧3.2 立体几何体的绘制圆柱的绘制方法与技巧圆锥的绘制方法与技巧长方体的绘制方法与技巧3.3 组合体的绘制与表达组合体的组成与分析绘制组合体的方法与技巧组合体的投影与表达3.4 几何体的轴测图绘制轴测图的基本概念与性质轴测图的绘制方法与技巧轴测图的应用与实践第四章:机械零件图的绘制4.1 零件图的概述与内容零件图的定义与作用零件图的内容与要求零件图的绘制步骤与方法4.2 零件图的视图选择与绘制视图的选择与表达绘制零件图的方法与技巧零件图的标注与说明4.3 常见机械零件的绘制轴的绘制方法与技巧齿轮的绘制方法与技巧螺纹的绘制方法与技巧4.4 零件图的修改与完善零件图的常见错误与修改零件图的完善与优化零件图的审查与评价第五章:装配图的绘制5.1 装配图的概述与内容装配图的定义与作用装配图的内容与要求装配图的绘制步骤与方法5.2 装配图的视图选择与绘制装配图的视图选择与表达绘制装配图的方法与技巧装配图的标注与说明5.3 常见机械装置的装配图绘制简单机械装置的装配图绘制复杂机械装置的装配图绘制装配图的组装与调整5.4 装配图的修改与完善装配图的常见错误与修改装配图的完善与优化装配图的审查与评价第六章:建筑图样的绘制6.1 建筑平面图的绘制建筑平面图的定义与内容建筑平面图的绘制步骤与方法建筑平面图的标注与说明6.2 建筑立面图的绘制建筑立面图的定义与内容建筑立面图的绘制步骤与方法建筑立面图的标注与说明6.3 建筑剖面图的绘制建筑剖面图的定义与内容建筑剖面图的绘制步骤与方法建筑剖面图的标注与说明6.4 建筑细部图的绘制建筑细部图的定义与内容建筑细部图的绘制步骤与方法建筑细部图的标注与说明第七章:电气图样的绘制7.1 电气图样的概述与内容电气图样的定义与作用电气图样的内容与要求电气图样的绘制步骤与方法7.2 电气原理图的绘制电气原理图的定义与内容电气原理图的绘制步骤与方法电气原理图的标注与说明7.3 电气安装图的绘制电气安装图的定义与内容电气安装图的绘制步骤与方法电气安装图的标注与说明7.4 电气设备接线图的绘制电气设备接线图的定义与内容电气设备接线图的绘制步骤与方法电气设备接线图的标注与说明第八章:计算机辅助绘图8.1 计算机辅助绘图概述计算机辅助绘图的定义与作用计算机辅助绘图系统的组成与功能计算机辅助绘图软件的选择与使用8.2 AutoCAD软件的基本操作AutoCAD软件的界面与操作界面AutoCAD软件的基本操作命令与技巧AutoCAD软件的绘图与编辑功能8.3 计算机辅助绘图的应用计算机辅助绘图在工程设计中的应用计算机辅助绘图在制造行业中的应用计算机辅助绘图在其他领域的应用8.4 计算机辅助绘图的实践与训练计算机辅助绘图的实际操作与练习计算机辅助绘图的技巧与提高计算机辅助绘图的评估与反馈第九章:图样常见的错误与纠正9.1 图样常见的错误分析尺寸标注错误符号使用错误图形表达错误文字说明错误9.2 图样错误的纠正方法尺寸标注错误的纠正符号使用错误的纠正图形表达错误的纠正文字说明错误的纠正9.3 图样修改与完善图样修改的原则与方法图样完善的技巧与建议图样审查与评价9.4 图样常见问题的解答与讨论图样绘制中的疑问与解答图样修改中的问题与讨论图样应用中的经验与交流第十章:图样制作的实践与考核10.1 实践项目的设计与制作实践项目的选择与分析实践项目的制作步骤与方法实践项目的成果评价与反馈10.2 考核方式与评分标准实践考核的方式与要求理论考核的内容与形式综合评价与成绩评定10.3 实践考核的注意事项实践考核的安全与规范实践考核的时间与进度安排实践考核的资料整理与提交10.4 优秀作品的展示与评价优秀作品的选拔与展示优秀作品的评价与分析优秀作品的借鉴与学习重点和难点解析:1. 第一章至第五章主要介绍画法几何与机械制图的基础知识,包括点的定义与表示方法,线的分类与画法,面的性质和相互关系,以及视图与投影的基本概念。

集成电路设计基础_华中科技大学中国大学mooc课后章节答案期末考试题库2023年

集成电路设计基础_华中科技大学中国大学mooc课后章节答案期末考试题库2023年1.画小信号等效电路时,恒定电流源视为。

答案:开路2.模拟集成电路设计中可使用小信号分析方法的是。

答案:增益3.模拟集成电路设计中可使用大信号分析方法的是()。

答案:输出摆幅4.题1-1-1 中国高端芯片联盟正式成立时间是:。

答案:2016年7月5.题1-1-2 如下不是集成电路产业特性的是:。

答案:低风险6.题1-1-3 摩尔定律是指集成电路上可容纳的晶体管数目,约每隔:个月便会增加一倍,性能也将提升一倍。

答案:187.MOS管的小信号模型中,体现沟长调制效应的参数是()。

答案:8.工作在饱和区的MOS管,可以被看作是一个。

答案:电压控制电流源9.下图中的MOS管工作在区(假定Vth=0.7V)。

【图片】答案:饱和区10.一个MOS管的本征增益表述错误的是。

答案:与MOS管电流无关11.工作在区的MOS管,其跨导是恒定值。

答案:饱和12.MOS管中相对最大的寄生电容是。

答案:栅极氧化层电容13.MOS管的小信号输出电阻【图片】是由MOS管的效应产生的。

答案:沟长调制14.题1-1-4 摩尔定律之后,集成电路发展有三条主线,以下不是集成电路发展主线的是:。

答案:SoC15.题1-1-5 单个芯片上集成约50万个器件,按照规模划分,该芯片为:。

答案:VLSI16.题1-1-6 年发明了世界上第一个点接触型晶体管。

答案:194717.题1-1-7 年发明了世界上第一块集成电路。

答案:195818.题1-1-8 FinFET等多种新结构器件的发明人是:。

答案:胡正明19.题1-1-9 集成电路代工产业的缔造者:。

答案:张忠谋20.题1-1-10 世界第一块集成电路发明者:。

答案:基尔比21.MOS管一旦出现现象,此时的MOS管将进入饱和区。

答案:夹断22.MOS管从不导通到导通过程中,最先出现的是。

答案:耗尽23.在CMOS模拟集成电路设计中,我们一般让MOS管工作在区。

第四章根轨迹分析法

闭环系统的阶次为3 ,有3条根轨迹 。

规则三、

证明:(1)连续性 从代数方程的性质可知,当方程中的系数连续变化 时,方程的根也连续,因此特征方程的根轨迹是连 续的。

证明:(2)对称性 因为特征方程的根或为实数,或为共轭复数,所以 根轨迹对称于实轴。

法则三、渐近线:根轨迹有n-m条渐进线。

渐近线与实轴的夹角为: (2k 1)1800 k 0,1,2,..

nm

n

m

pi z j

渐近线与实轴的交点为: i1

j 1

nm

l 它们是针对n-m条趋向无穷远点的根轨迹而设立的

l 如果知道了渐近线,可以马上画出根轨迹的大致形状

法则四、实轴上的根轨迹:在实轴上某线段右侧的实数 开环零、极点个数之和为奇数,则该线段为根轨迹。

对于例题,在实轴上的根轨迹: G(s)H (s) K*(s 5)

若当根轨迹出现在两相邻开环零点间(包括无穷

远处)时,必有一分离点。 分

离 点

K=∞

K=∞

分 离 点

××

K=0

K=0

它们可以利用代数重根法或极值法求出。(介绍后者)

由求极值的公式求出:

1 H (s)G(s) 1 K * N (s) 0 D(s)

K* D(s) N (s)

在实轴根轨迹上,求使K*达到最大(最小)值的s 值:

令虚轴的交点: s j 代入上式,得

( j)3 3( j)2 2 j K ( j 5) 0 Re 5K 3 2 0 Im (2 K ) 3 0 解得: 0,K 0;

本章主要内容

以K*为变量的常规根轨迹的绘制方法 以其它参数为变量的广义根轨迹的绘制方法 根轨迹分析方法的应用

-利用根轨迹分析和设计控制系统

第4章几何图形初步-余角和补角(教案)

举例:如果一个角的余角是30°,则这个角为60°;如果一个角的补角是100°,则这个角为80°。

(3)余角和补角的应用:学会将余角和补角知识应用于解决实际问题,如角度计算、图形拼接等。

举例:在计算不规则多边形内角和时,运用补角性质简化计算过程。

本节课的核心素养目标旨在培养学生具备空间观念、逻辑推理、数学应用和团队协作等方面的能力,为学生的终身发展奠定基础。

三、教学难点与重点

1.教学重点

(1)余角和补角的概念:理解余角和补角的定义,掌握两个角的和为90°时称它们互为余角,和为180°时称它们互为补角。

举例:直角三角形中的两个锐角互为余角;任意一个角与其补角相加等于180°。

突破方法:设计不同难度的练习题,由浅入深地引导学生掌握计算方法,并进行针对性讲解。

(3)解决实际问题时角度的转换:在解决实际问题时,学生可能难以将问题中的角度关系转化为余角和补角的关系,从而解决问题。

突破方法:通过具体案例分析,让学生学会将实际问题抽象为余角和补角问题,并运用所学知识解决。

本节课的教学难点与重点是理解余角和补角的概念、性质,以及在实际问题中的应用。教师应针对这些重点和难点内容,采用合适的教学方法和策略,确保学生能够透彻理解并掌握相关知识。

在学生小组讨论环节,我尽量让自己成为一个引导者和协助者,而不是知识的传递者。我提出了开放性的问题,鼓励学生们思考和创新。看到他们在黑板上展示自己的成果,我感到非常欣慰。但我也意识到,对于一些难度较大的问题,我可能需要提供更多的提示和支架,帮助学生逐步解决问题。

最后,我会在课后收集学生的反馈,了解他们在学习过程中遇到的具体困难,以便在接下来的课程中进行针对性的辅导。教学是一个不断学习和改进的过程,我会继续努力,让我的课堂更加生动有趣,让学生们真正爱上数学。

第4章 集成电路版图设计与工具

问题讨论: (1)阱的间距和间隔的规则

N阱通常是深扩散,必须使N阱边缘与邻近的N +扩散区之间留有足够的间隙,从而保证N阱 边缘不与P型衬底中的N+扩散区短接。内部间 隙由沿阱周围的场区氧化层的渐变区所决定。 虽然有些工艺允许内部的间隙为零,但“鸟嘴” 效应等问题导致了规则1.4(N阱外N阱到N+距 离)的设计要求,这是一种保守的估算。

电学设计规则还为合理选择版图布线层提供了 依据。集成电路工艺为设计者提供了多层布线 的手段,最常用的布线有金属、多晶硅、硅化 物以及扩散区。但这些布线层的电学性能大不 相同。

随着器件尺寸的减小,线宽和线间距也在减小, 多层布线层之间的介质层也在变薄,这将大大 增加走线电阻和耦合电容,特别是发展到深亚 微米级和纳米之后,与门延迟相比,布线延迟 变得越来越不可忽略。因此,版图布线必须合 理选择布线层,尽可能地避免布线层电学参数 的影响。

反相器版图与电路原理图

反相器版图及工艺层表示

反相器版图及剖面图

4.4 晶体管的版图设计

一、双极型晶体管的版图设计 1、 双极型集成电路版图设计的特点 双极型集成电路设计中首先要考虑的问题是 元器件之间的隔离。目前常用的隔离方法有PN 结隔离和介质隔离,设计者可以根据不同的设 计要求,选择适当的隔离方式。此外,还要注 意减小寄生效应如寄生PNP管、寄生电容效应 等。注意了这些问题,就可以比较顺利地完成 版图设计并制造出合格的电路。

集成电路设计技术与工具

第四章 集成电路版图设计与工具

基本要求

了解版图设计的主要方法, 掌握工艺层和几何设计规则, 掌握电学设计规则和布线,

掌握双极型晶体管和MOS晶体管的版图设计,

掌握掌握DRC、ERC、LVS和后仿真的定义

集成电路版图设计基础第4章:标准单元技术

school of phye

basics of ic layout design

16

网格式布线系统要求的库设计规则 对齐输入输出:

• 输入A和输出Z不能随意放置。它们必须像所有的连线一样位于同 样的网格上。 • 保证标准单元的所有输入输出不仅在x网格上,还要在y网格上。 要保证自动布线软件在水平方向和垂直方向都能找到它们。 • 保证所有的库单元以及库单元内部的器件符合网格规则。

school of phye

basics of ic layout design

7

标准网格

- 网格式布线器

grid-based router

• techfile - PHYSICAL RULES • 最小间距minSpacing:各几何图形外边界之间的距离。

school of phye

basics of ic layout design

school of phye basics of ic layout design 11

标准网格

- 网格式布线器

grid-based router

• coarse grid example:

1 microns 2 microns

1 microns

1 microns

Minimum wire is 1 micron, minimum spacing is 1 micron, therefore, our two wires use 3 microns, and we have established center-to-center grid spacing of 2 microns for this process.

• 数字库:高度固定,宽度可变。(fixed height, variable width.) 大多数库都是这样的。 对于数字版图,特别是标准单元版图,是唯一可行的方式。 在模拟版图设计中也非常有用,甚至是全定制的AIC。

七年级数学上册第四章几何图形初步认识4.1.1 立体图形与平面图形 第2课时(图文详解)

人教版七年级数学上册第四章几何图形初步认识

5.长方形、正方形、圆等都是 平面 图形. 6.写出下列几何体的名称.

棱柱

棱锥

圆锥

人教版七年级数学上册第四章几何图形初步认识

7.下列图形中为圆柱的是( D ).

8.埃及金字塔类似于几何体( C ).

(A)圆锥 (B)圆柱 (C)棱锥 (D)棱柱

人教版七年级数学上册第四章几何图形初步认识

你做对了吗?

人教版七年级数学上册第四章几何图形初步认识

1.下面是由六个正方形连在一起的图形,经折叠后能围 成正方体的图形有哪几个?

A

B

C

D

E

F

G

人教版七年级数学上册第四章几何图形初步认识

2.(武汉中考)如图所示,李老师办公桌上放着一个圆柱 形茶叶盒和一个正方体的墨水盒,小芳从上面看,看到的 图形是( )

人教版七年级数学上册第四章几何图形初步认识

9.下列图形中不是立体图形的是( D ).

(A)球

(B)圆柱

(C)圆锥 (D)圆

人教版七年级数学上册第四章几何图形初步认识

10.小明为班级专栏设计了一个图案,如图所示,主 题是“我们喜爱合作学习”,请你也尝试用圆、扇形、 三角形、四边形、直线等为环保专栏设计一个图案, 并标明你的主题.

人教版七年级数学上册第四章几何图形初步认识

4.(宁波中考)骰子是一种特别的数字立方体(如图),它

符合以下规则:相对两面的点数之和总是7.下面四幅图中

可以折成符合规则的骰子的是( )

(A)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

大尺寸MOS管的版图一般也采用并联结构, 或称作梳状栅结构,并且相邻的MOS管共用源 区或漏区。这种版图并联结构不但减小了版图 面积而且减小了源端和漏端的耗尽层电容.

源极S/漏极D 栅极G

源极S/漏极D 栅极G

漏极D/源极S

漏极D/源极S

4叉指MOS管

3叉指MOS管

漏极D/源极S

N阱层相关的设计规则及其示意图

P+、N+有源区层相关的设计规则及其示意图

Poly层相关的设计规则及其示意图

Contact层相关的设计规则及其示意图

Metal层相关的设计规则及其示意图

Pad层相关的设计规则及其示意图

二、几何设计规则 -举例及问题讨论

1)建立工艺文件

首先要建立版图的工艺文件,确定该工艺版 工艺层名称,各层的图案和颜色,以及用于版 工艺文件中最重要的就是每层的层号(Level或 Number)。同一个工艺,其工艺层的颜色、图 案甚至名称可以改变,但每层的层号却是唯一 的。

图的工艺层信息,例如对应各层掩膜版的层号、

图器件提取的标识层的名称、图案以及颜色等。

倾角引起的注入阴影

M1

M2

(a)简单布局

1 M 2 1

1 M 2 2

1 M 2 2

1 M 2 1(b)同心布局

R

两 个 叉 指 的 差 分 对 管 版 图

R

R

R

R R

总之,与分立元件电路设计相比,集成电路设 计的一个显著特点在于:设计者能够充分利用 集成电路特点,通过改变晶体管等元器件的图 形结构和几何尺寸,设计出最合理的晶体管来 满足整体电路的要求。但这要求设计者在设计 版图前,首先要搞清楚电路中各个晶体管的作 用,再决定采用哪种图形的晶体管。设计时, 既要考虑工作电流、特征频率、最高振荡频率 以及噪声等电学参数,又要兼顾光刻精度、套 准精度等工艺水平,以及占用面积、电路成品 率等因素。

问题讨论: (3)接触 版图设计中通常需要有多种接触,例如,金 属和P型扩散区接触、金属和N型扩散区接触、 金属和多晶硅的接触以及衬底接触等。根据工 艺不同,还有“隐埋”型多晶硅-扩散区接触和 拼合接触。 通常,制作芯片的衬底被划分成多个“阱” 区,每个孤立的阱必须利用衬底接触来接合适 的电源电压。将两个或多个金属和扩散区接触 用金属连通起来,称为合并接触。

集成电路设计技术与工具

第四章 集成电路版图设计与工具

内容பைடு நூலகம்要

4.1 4.2 4.3 4.4 4.5 4.6 4.7

引言 版图几何设计规则 电学设计规则与布线 晶体管的版图设计 九天软件下的版图编辑 九天软件下的版图验证 本章小结

4.1 引 言

版图(Layout)包含了器件尺寸、各层拓扑定义等 器件相关的物理信息数据,是集成电路从设计走向 制造的桥梁。 由于器件的物理特性和工艺的限制,芯片上物理层 的尺寸进而版图的设计必须遵守特定的规则。这些 规则是各集成电路制造厂家根据本身的工艺特点和 技术水平而制定的,因此,不同的工艺就有不同的 设计规则。设计者只能根据厂家提供的设计规则进 行版图设计 。

2.5

2 1.5 8 3.5 1.0 1.5 3 1.5

2.0 3.5 10

问题讨论: (1)阱的间距和间隔的规则

N阱通常是深扩散,必须使N阱边缘与邻近的N +扩散区之间留有足够的间隙,从而保证N阱 边缘不与P型衬底中的N+扩散区短接。内部间 隙由沿阱周围的场区氧化层的渐变区所决定。 虽然有些工艺允许内部的间隙为零,但“鸟嘴” 效应等问题导致了规则1.4(N阱外N阱到N+距 离)的设计要求,这是一种保守的估算。

问题讨论: (2)MOS管的规则

在多晶硅穿过有源区的地方,源和漏扩散区被多晶硅 区所掩蔽。因而,源、漏和沟道是自对准于栅极的。 重要的是,多晶硅必须完全穿过有源区,否则制成的 MOS管就会被源、漏之间的扩散通路所短路。为确保 这一条件得到满足,多晶硅必须超出扩散区边界,例 如该硅栅工艺中规则3.4中规定的1.5μm,这常常称 为“栅伸展”。同时,有源区也必须在多晶硅栅两边 扩 展,这样才能有扩散区存在,使载流子进入和流出沟 道,例如规则3.5规定的3.0μm就是保持源区和漏区 所必需的。

建立工艺文件界面示意图

2)建立版图数据库

Zeni4DM集成环境下,通过NewLibrary(新 建库命令)建立新的数据库。

3)设置全局参数 在新建的版图库中开始编辑一个版图单元时, 往往需要首先设置好版图设计所必须的一些全局 参数,如版图的最大、最小显示格点,命令菜单 对话框的弹出方式等。其中,版图设计的最小尺 寸或分辨率设置应该根据使用工艺能达到的分辨 来合理设置。对于深亚微米的版图设计,版图分 辨率设置与制造工艺分辨率的不一致,有可能引 起整个电路失效。因此,版图设计前要了解工艺 水平,合理设置版图格点和尺寸分辨率。

一、工艺层(Layer)

人们把集成电路版图设计过程抽象成若干易

于处理的概念性版图层次,也就是版图设计中

的工艺层,这些层次代表电路转换成硅芯片时

所必需的掩膜图形。版图的不同层次可以用不 同的形式来区分,例如不同的颜色、不同的线 型和不同的填充图案等。

某N阱硅栅工艺的部分工艺层

二、几何设计规则 -规则介绍

1)一般双极型晶体管的设计 (1)单基极条图形

隔离槽 发射区 基极引线孔(B) 基区 集电区 集电极引线孔(C) 发射极引线孔(E)

(2)双基极条图形

B C

E

(3)马蹄形结构

E

B

C

B

E

C

(4)梳形结构

E

B

C

2)多发射极晶体管的设计

3)集成电路中的PNP管

(a)顶视图

E C B

B N+

C

E P

4.5 九天软件下的版图编辑

九天(Zeni)系统软件为IC设计者提供了交 互式版图设计环境。交互式版图设计是指利用 集成电路CAD版图编辑工具,通过人工参与的 方式完成的电路版图设计。由于使用了交互式 环境,设计者可以根据所设计电路的各种性能 要求,对图形反复进行布置和连线,达到较佳 的布局效果,从而最大限度地利用芯片面积、 提高成品率,因而广泛应用于全定制集成电路 的版图设计中。

对于大尺寸器件

还可以采用折叠

的方式以减小一

栅 极 G 源极S/漏极D

维方向上的尺 寸。

漏极D/源极S

折叠式梳状栅MOS管版图示意

2)器件的失配问题

M1 M2

(a)电路图

(b)管子方向不对称

(c)垂直对称水平栅极

(d)垂直对称垂直栅极

MOS差分对管的版图分布形式

源漏离子注入

S/D

阴影区

D/S

(a)离子注入方向性(b)形成的不对称源漏结构

为了工艺上按比例缩小或版图编辑的需要, 合并接触采用图4.9(a)所示的分离式接触结 构,而不采用图4.9(b)的合并长孔结构。

4.3 电学设计规则与布线

电学设计规则给出的是由具体工艺参数抽象 出的器件电学参数,是晶体管级集成电路模拟 的依据。与几何设计规则一样,对于不同的工 艺和不同的设计要求,电学设计规则将有所不 同。通常,特定工艺会给出电学参数的最小值、 典型值和最大值。上述N阱硅栅CMOS工艺的 部分电学设计规则的参数名称及其意义如表4.8 所示。

除了选择合理的布线层外,版图布线还应该 注意以下几点: 1)电源线和地线应尽可能地避免用扩散区和多 晶硅走线,特别是通过较大电流的那部分电源线 和地线。集成电路的版图设计中电源线和地线多 采用梳状走线,避免交叉,或者用多层金属工艺, 提高设计布线的灵活性。 2)禁止在一条金属走线的长信号线下平行走过 另一条用多晶硅或扩散区走线的长信号线。 3)压焊点离芯片内部图形的距离应不少于20 m, 以避免芯片键合时,因应力而造成电路损坏。

电学设计规则还为合理选择版图布线层提供了 依据。集成电路工艺为设计者提供了多层布线 的手段,最常用的布线有金属、多晶硅、硅化 物以及扩散区。但这些布线层的电学性能大不 相同。

随着器件尺寸的减小,线宽和线间距也在减小, 多层布线层之间的介质层也在变薄,这将大大 增加走线电阻和耦合电容,特别是发展到深亚 微米级和纳米之后,与门延迟相比,布线延迟 变得越来越不可忽略。因此,版图布线必须合 理选择布线层,尽可能地避免布线层电学参数 的影响。

4.4 晶体管的版图设计

一、双极型晶体管的版图设计 1、 双极型集成电路版图设计的特点 双极型集成电路设计中首先要考虑的问题是 元器件之间的隔离。目前常用的隔离方法有PN 结隔离和介质隔离,设计者可以根据不同的设 计要求,选择适当的隔离方式。此外,还要注 意减小寄生效应如寄生PNP管、寄生电容效应 等。注意了这些问题,就可以比较顺利地完成 版图设计并制造出合格的电路。

在设计电路中的某一管子时,应首先弄清该

管在电路中的作用,抓住主要矛盾,设计出符 合要求的管子。例如,对于逻辑电路设计,电 路的输出管就应该着重考虑能承受电流,并具 有较快的开关速度和较低的饱和压降;而对反 相管则应着重考虑有较快的开关速度和较高的 特征频率。 不同的晶体管图形在集成电路中所起的作用 不同,因此版图设计中一块掩模版上往往就有 几种晶体管的图形。下面首先介绍一般双极型 晶体管的图形及其各自的特点。

根据双极型晶体管的版图特点,其版图设计 的一般原则包括以下几个方面的内容: 1)划分隔离区(岛)

2)几何对称设计

3)热对称设计 4)图形尺寸选择

2、 双极型晶体管的图形设计 版图设计工作决不能脱离工艺实际,离开工 艺来谈设计是没有意义的。版图设计者的任务 是在目前工艺许可的条件下,尽可能设计出各 种符合要求的晶体管。集成电路中对双极型晶 体管的要求主要是: (1)有一定的特征频率fT; (2)满足要求的开关时间; (3)能承受一定的电流; (4)具有较低的噪声系数; (5)具有一定的耐压。