数字锁相环参数设计与仿真

一种数字锁相环的参数设计方法

本 文研究 数 字锁相 环 的环 路参 数设 计 问题 , 反正 切 载 波 恢 复 环 为 例 给 出一 种 环 路 参 数 设 计 方 法 。 以

数 字锁 相环 易 于集 成 , 耗低 , 积小 , 能可靠 , 用 灵活 且 性 价 比较 高 , 实 际 通信 系统 中得 到 了 功 体 性 应 在

广泛 应用 … 。然 而 , 比于模 拟锁 相环 , 字 锁 相环 的环 路 参 数 设 计 较 为 困难 , 实 际 工 程 实现 中 , 相 数 在 所需 参数 一般依 据经 验 给定 , 精度 较低 , 可靠 性 也不 高 。因此 , 究 数字 锁 相 环 的环 路 参 数设 计 方 法 具 有 重要 研

的工程 意义 。 目前对 P K 信 号进行 相 干解调 时 最为 常用 的数 字锁 相环 是传 统 的 C s s S ot 环 , 环 路 的鉴 a 其

相特 性为 s ( 0) 线 性范 围窄 。文 献 [ ] 绍 了一 种反 正切 载 波恢 复环 , C s s i 2 , n 3介 与 ot 环相 比 , a 该环 直接 通过

e , i i i c l o d sg h o p p r m ee r c s l . To d a t h r blm ,t e pa e r p — r t sd f u tt e in t e l o a a trp e ie y i e lwi t e p o e h h p rp o o s s a lo a a ee e i n meh d tki a l c a re e o e o p a n e a e o p p r m tr d sg to a ng a t n o k c rir r c v r lo s a x mpl e,wh c c ih a — c mp ih spaa ee e i n i g tlp a e l c o p c o d n o t e c n e to ewe n a ao o ls e r m tr d sg n diia h s o k l o s a c r i g t h o n ci n b t e n lg lo s a d d g tllo s S mu ai n r s lss o t a h to sf a il o p n i i o p . i l t e ut h w h tt e meh d i e sb e. a o K e o ds: iia h s o k lo s;lo a a trde in diia ;t n o k c rirr c v r yw r dg tlp a e l c o p o p p r me e sg g tl a lc a re e o e

三阶数字锁相环设计与仿真

通 过 对 传 递 函 数 进 行 分 析 ,得 到 三 阶锁 相 环 稳 定 工 作 和 快 速 捕 获 所 需 要 的 相 关 条 件 , 给 出 三 阶 数 字 锁 相 环 参 数 计 算 方 法 和 实 现 框 图 。 利 用 m tb仿 真 工 具 ,构 造 出 实 际 工 程 系 统 模 型 , 对 三 阶 数 字 锁 相 环 路 进 行 了 仿 真 。 验 证 了 该 构 aa l 成 形 式 和 计 算 方 法 能 够 保 证 三 阶 锁 相 环 快 速 捕 获 和 稳 定 工 作 ,可 以 在 实 际 工 程 中 得 到 广 泛 应 用 。 关键词 传 递 函数 ; 轨 迹 ; 尼 系数 ; 路 带 宽 根 阻 环

Z HANG n s e L U h n .i Xi .h . I S e g 1

( . h 4hR s r stt o E C, h i h a gH b 5 0 1 C i 1 T e5 t e ac I tu e h n i e fC T S i zu n e i 0 8 , hn j a e0 a; 2 B l gIstt o Tak g a d Tl o m n ai ehooy B in 0 0 4 C i ) . e n tu r i n e cm u i t nTc nl , e i 10 9 , hn i t ni e f cn e c o g jg a

e gn e n n i e r g. i

Ke r s ta se u cin ;o tlc s d mpngfco ;o p b d dh y wo d r n frf n t s ro o u ; a i a tr lo a wi t o n

数字锁相环

摘要本设计是在FPGA上设计数字锁相环。

选用的是ALTERA公司开发的的QuartusⅡ7.0作为软件开发平台,采用自上而下的设计方法,将数字锁相环(DPLL)分成了鉴相器(DPD)模块,数字环路滤波器(DLP)模块,数控振荡器(DCO)模块和除N分频。

最后将用VHDL语言编写好的程序通过QuartusⅡ7.0软件仿真,验证设计的正确性。

关键词:数字鉴相器(DPLL),数字环路滤波器(DLP),数字压控振荡器(DCO),除N分频计数器;VHDL.。

Digital Phase-Locked LoopAbstract:This design is designed in the FPGA digital phase-locked loop. ALTERA selection is developed in the Quartus Ⅱ7.0 as a software development platform, using top-down design method, digital PLL (DPLL) is divided into a phase detector (DPD) module, digital loop filter (DLP ) module, numerical controlled oscillator (DCO) module and inter-N frequency. Finally a good use of VHDL language program through the Quartus Ⅱ 7.0 software simulation, design verification.Keywords:digital phase detector (DPLL), digital loop filter (DLP), Digital voltage controlled oscillator (DCO), except N frequency Counter;VHDL。

自适应锁相环的设计与仿真

理论算法2021.07自适应锁相环的设计与仿真何琦(安徽理工大学电气与信息工程学院,安徽淮南,232001)摘要:在三相电压不平衡时,负序分量会在Park变换后产生一个2倍基频的波动,进而影响对基频分量相位的提取。

针对一般的锁相环在电网三相不平衡时无法准确锁定电网的相位,本文提出一种基于陷波器的自适应锁相环,利用自适应陷波器(ANF)能够输出两个相互正交分量的特点,生成两个能抵消dq坐标系的负序分量,这样就实现了基波的正序负序分离。

在Matlab/Simulink中建立仿真模型进行验证,结果表明了文中所提的方法在电网不平衡时可以准确地锁定电网的相位。

关键词:三相电压不平衡;锁相环;自适应陷波器;正序负序分离Design and Simulation of Adaptive Phase-locked LoopHe Qi(School of Electrical and Information Engineering,Anhui University of Science and Technology,Huainan Anhui,232001)Abstract:When the fundamental frequency of the three-phase is not balanced,a negative componentof the volt a ge will be ext r ac ted.In view of the fac t that the general phase-locked loop(PLL)cannot accurately lock the phase of the power grid when the three-phase power grid is unbalanced,this paper proposes an adaptive phase-locked loop based on notch f订ter.The adaptive notch filter(ANF) can output two mutually orthogonal components to generate two negative sequence components which can offset the dq coordinate system.Thus,the separation of positive sequence and negative sequenceof fundamental wave is realized.The simulation model is established in Matlab/SIMULINK for verifica t ion.The resu Its show that the proposed met h od can accura t ely lock the phase of power grid when the power grid is unbalanced.Keywords:Three-phase voltage unbalance;PLL;Adaptive notch f订ter;Positive sequence negative sequence separation0引言随着新能源技术的快速发展,并网逆变器在分布式发电中得到广泛应用。

基于广义二阶积分的数字锁相环设计

基于广义二阶积分的数字锁相环设计与实现王 鹏(国网江苏省电力有限公司扬州市江都区供电分公司)摘 要:电力系统110kV三相供电,为了保证供电网的电源品质,必须对供电网电流进行锁相控制,以保证输入电流相位与电网电压相位的同步性。

本文提出一种基于广义二阶积分器的数字锁相环,在旋转坐标系下得到电网电压的相位信息,利用现有的广义二阶积分器构造出与电网电压正交的网压,再进行坐标变换。

文中对同步坐标系下的单相锁相环的锁相原理及数学模型进行推导,经过仿真验证,本文提出基于广义二阶积分器的数字锁相环能够对电网相位进行快速、精确的锁定,具有较好的控制性能,具备进行大规模推广应用的价值。

关键词:广义二阶积分器;数字锁相环;电网相位0 引言由于电网电压非常容易受到外部干扰及电压谐波的影响,在单相四象限整流器工作的时候,四象限输入电流和电网电压的相位一旦存在一定程度的差异,则会对电网造成冲击和污染。

锁相环控制技术是网侧变流器控制的一项关键技术,单相四象限整流器就是一种网侧变流器,锁相环控制技术通过检测电网电压信号的特性,保证四象限输入电流信号的相位始终对电网电压信号的相位进行跟踪,实现二者的同步。

对于单相四象限整流器来说,最为常规的锁相方法是电网电压的过零点检测,电网电压过零点的锁相方法虽然简单实用,但其缺点同样明显,由于是通过硬件电路对电网电压的过零点信号进行捕获,因此非常容易受到电压谐波和网压突变的影响,并且锁相环的调节速度也比较慢,每个过零点信号到来的时候才会进行相位的重新调节,一旦在过零点之间发生相位变化,控制软件无法实时检测到,会造成控制失效。

1 广义二阶积分器原理基于Park变换的锁相环采用闭环调节,动态性能好,抗干扰能力强,响应速度快,在三相系统中有非常广泛的应用。

在三相系统中,能够在同一时刻采集三相电网电压信号,这三相电网电压信号包括相位、幅值、频率信息,通过Clark变换和Park变换能够很容易提取到相位信息,在同步坐标系下,d轴是幅值信号,q轴是相位信号,再通过相应的调节、计算,就能够得到最终可用的相位信号。

锁相环工作原理及仿真分析

滤波器的传递函数 F ) ,所以 : =1

O() S i +K

微分算子 。

,

O( P+ t)

,

0 ( +KO( =0 ( t ) t ) ) 设环路输入为固 定频率信号, :O ) m , 则 =A 0

图1锁相环的组成框 图

所

。

0 ( +K =A o ( ) t ) 0( ) m 3

1 +Ho S F()( ) () +K s 2

通常 将采 用 C 积分滤 波器 、无 源比例积 分滤 波器 、 有 源 比例积分 滤波器 作为环 路滤波 器的二 阶环分 别 叫作 典型二 阶环 ,非理 想二 阶环 和理 想二 阶环 。

振荡 器 (C ) 部分所组成 。为研究 问题 的方便 ,一般在 V O3 锁相环领 域 中的环路 的输入 信号 、 出信 号都为 正弦 类 输 信 号 。这样 ,输入 和 输 出信 号 的 相位 会 产生 相 位 误差

环路的开环传递函数为 :

Ho = )

d s K s F() F()

: 一

S

( ) 1

如 所 假设U = fn(t 0() 图l 示, i) U ( f), s i+ i ) U : oi 0t O() 0) U n ) + 0 )。 s (0

式 中 :Ui 为输 入信号 的振幅 ; 1 为输 入信号 的载 ( ) 波角频率 ; 角频 率。 模拟 锁相环 由鉴相器 (D 、环 路滤波 器 (F 、 控 P) L) 压 为输出信号的振幅 , 为输出信号的载波 ∞0

误差比较小时 ,环路才能稳定工作 。

2 式可得 : 对参数加以 调整就得到控制信号 () 控制信号再经 进行环路的定量分析。由 ( ) r,

基于FPGA的数字锁相环设计与仿真分析

i f c M 墼兰鳖塑矍H 墼兰婆鎏

字 锁 相 环设 计 , 对 相 关 参数 进 行 了 仿 真 与 分 析 。 并

2 数 字 锁 相 环 的 特 点 和 原 理

2 1 触 发 型 数 字 锁 相 环 基 本 原 理 .

f 本 文 采 用 触 发 型 数 字 锁 相 环 如 图 1所 示 : 数 字 鉴 相 由 滤 波 器 看 成 一 个 分 频 器 , 分 频 比为 , 出 频 率 为 f一 则 输 器 、 字 滤 波 器 和 数 控 振 荡 器 组 成 。 其 中 数 控 滤 波 器 的 输 数 入 时 钟 频 率 为 ( 晶 振 电路 产 生 ) 其 值 为 1 3 6 Hz 由 , 4 3 k 。数 控 2 l k @Mf '  ̄ 全 坚 数 控 振 荡 器 的 输 出 频 率 f : f + 百A 只 振荡 器的输入频 率为 2 。通 常 M 和 N 为 2的 整 数 幂 。 时 钟 要 合 理 选 择 K值 , 能 使 输 出信 号 V2的 相 位 较 好 地 跟 踪 输 就 2经 除 计 数 器 得 到 。 入 V1的 相 位 , 达 到 锁 定 的 目 的 。如 果 K 值 选 的太 大 以 环

,

。

1、

‘\ 1

锚 杆 钻 机 的 发 展 也 进 入 了 一 个 崭 新 的 阶 段 。近 十 多 年 来 , 岩 设 备 的 研 究 工 作 集 中 在 新 型 的 液 压 凿 岩 机 及 与 其 凿 配 套 的 液 压 钻 车 , 般 认 为 当 前 风 动 凿 岩 设 备 的 发 展 水 平 一 已达 到 上 限 效 率 , 且 噪 音 和 污 染 是 难 以 克 服 的 。 液 压 凿 并 岩 机 具 有 功 率 大 、 率 高 、 眼 速 度 快 、 音 小 、 气 污 染 小 效 钻 噪 空 等优 点 , 此获得 了很快发展 。 因 是 非 常 重 要 的 , 进 设 备 的 结 构 、 形 和 重 量 应 适 应 掘 进 工 掘 外

基于dq变换的锁相环设计与仿真

基于dq变换的锁相环设计与仿真何攀;席自强【摘要】针对一般锁相环在电网电压波动时存在锁相误差的问题,提出了一种基于dq变换的锁相环新方案,并对锁相环参数进行了整定.对于电网电压频率变化、相位变化以及谐波注入的影响,利用matlab进行了仿真分析.仿真结果表明,新方案有很好的跟踪效果,跟踪速度快,精度高,能较好实现相位锁定.【期刊名称】《湖北工业大学学报》【年(卷),期】2017(032)005【总页数】3页(P93-95)【关键词】电压波动;dq变换;锁相环【作者】何攀;席自强【作者单位】湖北工业大学太阳能高效利用湖北省协同创新中心,湖北武汉430068;湖北工业大学太阳能高效利用湖北省协同创新中心,湖北武汉 430068【正文语种】中文【中图分类】TM464新能源技术的不断发展,使得越来越多的分布式电源接入电网中,能精确快速锁定电网电压的相位,对于需要并网运行的设备也变得越来越重要。

锁相主要分为硬件锁相和软件锁相两种,由于硬件锁相精确度不高,容易受到干扰,所以现在广泛采用软件锁相技术,数字处理器的大规模发展,也使得软件锁相技术更易于实现[1-4]。

传统的锁相环采用过零锁相的方法,但在电压存在畸变的情况下,锁相效果不太理想;电压不平衡的状态下,可以通过傅里叶变换将基波成分和谐波成分分别提取出来,但必须采集完整的周期数据,不能实时计算[5-7]。

因此,本文根据坐标变换的原理[8],建立了三相电网电压在同步旋转坐标系下的系统模型,详细阐述了锁相环的结构及原理。

并通过仿真验证了锁相环在电压波动时的跟踪效果。

在三相电网电压平衡的情况下,三相电网电压全部为正序分量,其在abc坐标系下的表达式如下:其中,Um为各相电压幅值,ω为电网电压角频率,φ为初始相角。

利用Clark变换,将式(1)中三相电压变换到两相静止αβ坐标系:再利用Park变换,最终转换为dq坐标系下的直流分量Ud、Uq:1.1 同步坐标系锁相环原理根据瞬时无功功率理论,将三相电压合成矢量在同步坐标系下进行分解,图1所示为同步旋转坐标系示意图,图中Us为三相电压合成矢量,与坐标轴的夹角为θ(θ=ωt),θ′为锁相环实际输出电压矢量与坐标轴的夹角,Ud、Uq分别为三相合成矢量在同步旋转坐标系下的d轴和q轴上的直流分量。

PLL设计关键基础及基本参数确定方法

PLL设计关键基础及基本参数确定方法PLL(锁相环)是一种电路设计技术,用于将输入信号的频率和相位合成为与参考信号相同的输出信号。

它在各种应用领域中具有广泛的应用,包括通信系统、数据传输、时钟发生器、频率合成器等。

1.建立模型:确定所需的频率范围和准确度,并选择适当的振荡器作为参考信号源。

建立时钟和相位比较器的模型,以及低通滤波器等组成部分的模型。

2.频率范围和准确度:确定PLL所需的输出频率范围和准确度。

这取决于具体的应用需求,如通信系统中需要的频率范围和准确度。

一般来说,更高的频率范围和准确度要求会导致设计更复杂的PLL电路。

3.反馈环:选择适当的反馈环型式,如基本PLL、全数字PLL或混合模拟数字PLL。

这取决于应用需求和设计复杂度。

基本PLL适用于频率较低的应用,但对相位噪声较敏感。

全数字PLL则采用数字环路滤波器,具有更高的鲁棒性和可控性。

4. 相位锁定范围(Phase Locked Loop Range):确定PLL的相位锁定范围,即输入信号的相位偏移量。

这取决于具体应用中的信号变化范围和要求。

较大的相位锁定范围会导致更高的设计复杂度。

5.闭环带宽:确定PLL的闭环带宽,即相位比较器输出与输出信号的相位偏差之间的关系。

较大的闭环带宽可以提供更高的锁定速度,但可能会导致更高的相位噪声。

6. 电源抑制比(Power Supply Rejection Ratio,PSRR):确定PLL对电源噪声的抑制能力。

电源噪声可能会影响PLL的性能,因此需要设计合适的滤波器和抑制电源噪声的能力。

7.噪声性能:确定PLL对输入信号噪声和环路滤波器自身噪声的敏感度。

这取决于环路滤波器的设计和反馈环的类型。

一般来说,全数字PLL 具有更好的噪声性能。

8.稳定性和抖动:确定PLL的稳定性和抖动性能。

PLL需要能够在各种工作条件下保持稳定,不受温度、电源变化等因素的影响。

抖动性能衡量了PLL输出信号的时钟稳定性。

adisimpll锁相环设计过程

adisimpll锁相环设计过程锁相环(Phase-Locked Loop,PLL)是一种常用于时钟和信号恢复的电子电路。

它可以将输入信号的频率、相位和幅度与参考信号进行比较,然后通过调整其内部振荡器的频率和相位来保持与参考信号的同步。

在现代电子系统中,锁相环已成为许多应用的核心部件,例如通信系统、数据转换和数字信号处理等。

锁相环的设计过程通常包括以下几个主要步骤:1.确定锁相环的规格要求:首先需要确定系统的特定需求,包括输入和输出信号的频率范围、带宽、相位噪声要求以及抖动限制等。

这些规格要求将直接影响锁相环的设计参数和性能。

2.选择合适的锁相环架构:根据系统的特定需求,选择适合的锁相环架构。

常见的锁相环架构包括基于电压控制振荡器(Voltage-Controlled Oscillator,VCO)的基本锁相环、带自由运行振荡器(Free-Running Oscillator)的环-环(Ring-Oscillator)锁相环和数字控制振荡器(Digital-Controlled Oscillator,DCO)的混合锁相环等。

3.设计相位频率检测器:锁相环中的相位频率检测器(Phase-Frequency Detector,PFD)用于比较参考信号和反馈信号的相位和频率差异,并将其转化为控制信号。

常见的PFD电路包括EXOR门和带有多频偏的PFD等。

4.设计环路滤波器:设计环路滤波器用于平稳化锁相环的控制信号。

环路滤波器通常采用低通滤波器结构,能够滤除高频噪声和不稳定性。

5.设计振荡器:根据系统的频率范围和性能要求,设计合适的振荡器。

常见的VCO设计包括压控晶体振荡器(Voltage-Controlled Crystal Oscillator,VCXO)和频率可调振荡器(Voltage-Controlled Oscillator,VCO)。

6.设计控制电路:根据锁相环的设计需求,设计合适的控制电路。

数字锁相放大器原理及其Matlab仿真

数字锁相放大器原理及其Matlab仿真摘要:数字锁相放大器作为一种新型的放大器,其原理和应用逐渐受到人们的关注。

本文主要介绍数字锁相放大器的基本工作原理和Matlab仿真的方法。

基于数字信号处理技术,数字锁相放大器通过数字积分器和数字锁相环的组合实现了高精度的信号放大和相位锁定。

在Matlab环境下,仿真过程首先建立数字锁相放大器的模型,然后进行参数设置和仿真测试。

通过多次调整模型参数,并对仿真结果进行分析,得到最优的数字锁相放大器设计方案。

本文的研究可以为数字锁相放大器的实际应用提供参考。

关键词:数字锁相放大器、数字信号处理、数字积分器、数字锁相环、Matlab仿真正文:一、引言数字锁相放大器作为一种新型的放大器,其应用范围涉及多个领域,如精密测量、生物医学、材料科学等。

与传统的电子放大器相比,数字锁相放大器具有响应速度快、抗干扰性强、精度高等优点。

为了更好地掌握数字锁相放大器的原理和应用,本文通过Matlab仿真的方法进行研究,以期发现数字锁相放大器的最佳设计方案。

二、数字锁相放大器原理数字锁相放大器基于数字信号处理技术实现了高精度的信号放大和相位锁定。

其基本工作原理是:将待放大信号与参考信号做乘积,再将乘积信号通过数字积分器得到直流分量和交流分量。

然后将交流分量输入数字锁相环进行相位锁定,最后从数字锁相放大器的输出端可以获得相位锁定后的信号。

数字锁相放大器的电路图如下所示:图1 数字锁相放大器的电路图其中,$u_i$表示待放大信号,$u_{ref}$为参考信号,$v$为输出端信号,$n_i$,$n_{ref}$,$n$为噪声信号。

数字积分器的计算公式为:$$y(n)=y(n-1)+\frac{T}{2}\left(x(n)+x(n-1)\right)$$其中,$x(n)$为输入信号,$y(n)$为输出信号,$T$为采样周期。

数字锁相环的计算公式为:$$\theta_{n}=\theta_{n-1}+K_{p} \Delta \varphi_{n}+K_{i}\sum_{j=0}^{n} \Delta \varphi_{j}$$其中,$\theta_{n}$为相位偏差,$\Delta \varphi_{n}=2 \pif_{ref} T$为相位差,$K_{p}$和$K_{i}$为比例常数和积分常数。

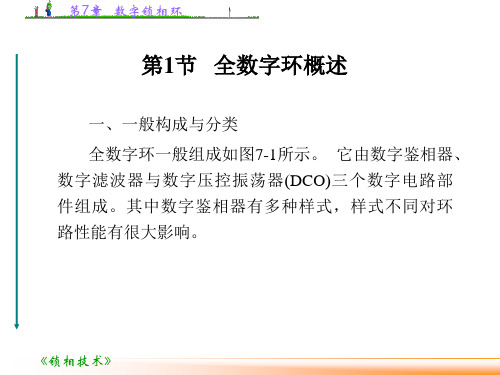

第7章数字锁相环

第7章 数字锁相环

《锁相技术》

图7-11 数字环路滤波器一般形式

第7章 数字锁相环

3. 数字压控振荡器(DCO)数字压控振荡器的基本组 成如图7-13所示。它由频率稳定的信号钟、计数器与 比较器组成,其输出是一取样脉冲序列,脉冲周期受数字 环路滤波器送来的校正电压控制。前一个取样时刻的 校正电压将改变下一个取样时刻的脉冲时间的位置。 DCO在环路中又被称为本地受控时钟或本地参考时钟 信号。

第7章 数字锁相环

《锁相技术》

图7-2 触发器型鉴相器

第7章 数字锁相环

(2) 奈奎斯特速率抽样鉴相器。该型鉴相器组成如 图7-3所示。模数变换器(A/D)的抽样率按带通信号的取 样定理选择,以使取样后信号含有充分的输入信号相 位信息。

《锁相技术》

第7章 数字锁相环

《锁相技术》

图7-3 奈奎斯特速率抽样鉴相器

图7-15 超前—滞后数字锁相环基本组成 《锁相技术》

第7章 数字锁相环

一、电路组成与说明 电路实例是数字通信中常用的一种简单的超前—滞 后位同步环路,未用序列滤波器,电路组成如图7-16所示。

《锁相技术》

第7章 数字锁相环

《锁相技术》

图7-16 位同步数字环组成电路

第7章 数字锁相环

二、环路位同步原理 图7-18为图7-16方案内各点的波形图,这里为分析 简便,以均匀变换的数字脉冲序列作为输入信号,它与随 机的数字脉冲序列作用下环路取得位同步的原理是一 样的。

《锁相技术》

第7章 数字锁相环

《锁相技术》

图7-7 简单二元鉴相器

第7章 数字锁相环

图 7-8 上 的 中 相 积 分 — 抽 样 — 清 除 电 路 是 用 来 判 断 DCO输出与码元转换边沿之间相位关系的。例如,中相 积分区间跨在从正到负的两个码元之间,而积分结果为 正,说明DCO时钟超前;积分结果为负,说明DCO时钟滞 后;积分结果为零,相位准确对准。

基于锁相环的滞后超前环路滤波器的设计与仿真

基于锁相环的滞后超前环路滤波器的设计与仿真滞后超前环路滤波器是一种基于锁相环的滤波器,用于对输入信号进行滤波和延迟等处理。

它在电子学、通信等领域广泛应用,并且具有较高的性能和稳定性。

滞后超前环路滤波器的设计和仿真需要以下步骤:第一步,确定系统要求:根据实际应用需求,确定滞后超前环路滤波器的设计参数,如增益、频率范围、相位延迟等。

第二步,选择锁相环类型:根据系统要求,选择合适的锁相环类型,如整数型锁相环、分数型锁相环等。

整数型锁相环适用于要求精度不高的场景,而分数型锁相环适用于要求更高精度的场景。

第三步,确定锁相环参数:根据系统要求和所选锁相环类型,确定锁相环的参数,包括比例增益、积分时间常数等。

这些参数决定了滤波器的性能和稳定性。

第四步,进行仿真:使用专业的电子设计自动化工具,如SPICE软件等,进行滞后超前环路滤波器的仿真。

在仿真中,可以设置输入信号,观察滤波器的输出信号,并且根据需求进行参数调整和优化。

第五步,性能评估:根据仿真结果,对滞后超前环路滤波器的性能进行评估。

通过观察信号的波形、频谱等指标,来评估滤波器对输入信号的处理效果和延迟情况。

第六步,优化设计:根据性能评估的结果,对滞后超前环路滤波器的设计进行优化。

可以调整参数、改变电路拓扑等方式进行优化,以提高滤波器的性能和稳定性。

第七步,验证实现:通过硬件实现或集成电路设计等方式,将设计好的滞后超前环路滤波器实现,并进行验证。

可以通过实际信号输入测试、频率响应测试等方式来验证滤波器的性能。

综上所述,基于锁相环的滞后超前环路滤波器的设计与仿真是一个多步骤的过程,需要根据系统要求、选择合适的锁相环类型和参数,进行仿真、性能评估和优化设计,最后通过实际验证来完成。

通过这一过程,可以得到满足实际需求的滞后超前环路滤波器。

基于MATLAB数字锁相环仿真设计

本科生毕业设计(申请学士学位)论文题目基于Matlab的数字锁相环的仿真设计作者专业名称电子信息工程指导教师2014年5月学生:(签字)学号:答辩日期:2014 年 5 月24 日指导教师:(签字)目录摘要 (1)Abstract (1)1 绪论 (2)1.1 本文研究背景 (2)1.2 本文研究意义 (2)1.3 锁相环和仿真方式 (2)1.3.1 锁相环 (2) (2)3 2 模拟锁相环Matlab仿真 (3)2.1 模拟锁相环方案 (3)2.1.1 模拟鉴相器 (3)2.1.2 模拟低通滤波器 (6)2.1.3 模拟压控振荡器 (7)2.2 模拟锁相环仿真 (8)2.3 本章小结 (9)3 数字锁相环Matlab仿真 (10)3.1 数字锁相环方案 (10)3.1.1 数字鉴相器 (10)3.1.2 数字滤波器 (12)3.1.3 数字压控振荡器 (13)3.2 数字锁相环仿真 (14)3.3 本章小结 (15)4 总结与展望 (15)参考文献 (16)致 (18)基于Matlab的数字锁相环的仿真设计摘要:锁相环是一种能够自动跟踪信号相位并达到锁频目的的闭环负反馈系统。

数字锁相环在无线电领域得到较广泛的应用和发展。

而且已经成为雷达、通信、导航等各类电子信号产品不可替代的元器件之一。

锁相环的窄带跟踪性能使其得到较广泛应用。

因为锁相技术在实际应用中较为复杂,所以锁相环的设计通常采用仿真设计这种方式。

本次设计采用Matlab这一软件进行辅助仿真设计,完全能达到设计预期的目标。

Matlab中的Simulink仿真软件,具有很强的灵活性和直观性。

本次设计所采用的方法是在simulink中搭建模拟锁相的模型,并对模拟锁相环的组成、结构、设计进行不断的分析和改进。

然后根据模拟锁相环的原理进行改进,并搭建数字锁相环。

关键词:锁相环;自动跟踪;matlab;simulinkSimulative design of digital phase-locked loop based onMatlabAbstract:PLL is the automatic tracking system of close loop atracking signal phase. It is widely used in various fields of radio. It has become an irreplaceable part of radar, communication, navigation and all kinds of electronicsignal device. PLL is able to be widely used. Because, it has unique narrow-band tracking performance. However, because of the complexity of phase lock technique, for the design of PLL have brought great difficulty. This design uses Matlab, the simulative software for design assistance, can completely meet the design expectations. Simulink simulative software on Matlab, has strong flexibility and intuitive. Methods used by this project is to build the analog phase locked in the Simulink model, and the composition, structure, design of analog phase-locked loop of continuous improvement and analysis. It improved according to the principle of analog PLL, build digital phase-locked loop in Simulink, and then reach the simulation design of digitalphase-locked loop based on Matlab the design objective .Key words: PLL, Automatic tracking, Matlab, simulink1 绪论1.1 本文研究背景19世纪30年代法国H.de Bellescize首次提出同步检波这一概念,并且设计出锁相环电路这一划时代的研究成果[1]。

simulink锁相环pll用法

simulink锁相环pll用法

Simulink中的锁相环(Phase-Locked Loop,PLL)是一种常用的信号处理器件,用于频率和相位同步。

它可以用于许多应用中,例如通信系统、数据转换、时钟恢复和信号重构等。

在Simulink中使用PLL有几个关键的步骤:

1.模拟输入信号:首先需要生成或获取输入信号,这通常是

一个模拟信号或数字信号。

2.创建PLL模块:打开Simulink环境,创建一个新的模型,

在模型中添加PLL模块。

对于PLL模块的创建,可以在

Simulink库中搜索PLL模块并将其拖放到模型中。

3.设置参数:对于PLL模块,需要设置一些关键参数,例如

参考频率(Reference Frequency)、带宽(Loop Bandwidth)、初始相位(Initial Phase)等。

这些参数决定了PLL的性能

和工作方式。

4.连接信号和参考:将输入信号连接到PLL模块,并指定参

考信号。

参考信号可以是外部提供的,也可以是由PLL根

据输入信号生成的稳定参考。

5.仿真和分析:设置好参数并连接信号后,运行模型进行仿

真。

可以观察输出信号的频率和相位与参考信号的同步情

况,并进行性能分析和优化。

需要注意的是,PLL的具体用法和设置参数会因应用和设计需求而有所差异。

Simulink提供了丰富的库和模块,可以根据具体

应用需求选择和配置适当的PLL模块。

还可以通过自定义模块或编写MATLAB脚本来实现更高级的PLL功能。

锁相环HMC832的设计与实现

0 引言HMC832是Hittite 公司继HMC830之后推出的又一款25MHz 到3GHz 的频率合成芯片。

该芯片拥有单电源供电、宽带、超低噪声、超低杂散的特性[1]。

具备小数N 分频,内部集成1500 MHz ~3000 MHz 的压控振荡器(VCO),输出分频比1/2/4/6.../60/62,输出频率范围为25 MHz 至3000 MHz。

内部集成相位检波器(PD)和Δ-Σ型调制器能以高达100 MHz 的频率工作,实现更宽的环路带宽和更快的频率调谐,并具备出色的频谱性能。

该器件以其优异的低相位噪声和低杂散性能,广泛应用于无线通信系统中。

1 硬件设计HMC832 的内部功能结构主要包括以下几个部分:参考信号从XREFP 输入到参考支路R 分频器、PFD 鉴频鉴相器、CP 电荷泵,再通过外部环路滤波器,从VTUNE 引脚输入到VCO,通过N 分频器反馈到PFD 鉴频鉴相器形成锁相环路。

其中N 分频器上的Δ-Σ 调制器可以提供小数分频的功能。

VCO 通过CAL 模块获得校准的能力,最后VCO 通过可编程的末级分频器将需要的频率输出到RF 引脚。

其内部系统功能框图如图1。

外围硬件电路主要有参考时钟、环路滤波电路、电源供电三部分。

1.1 晶振的选择为保证频率稳定度和低相噪,本设计采用恒温晶振,在全温度范围内稳定度为±50ppb,频率调整范围为±2ppm ;且具有极好相噪指标。

HMC832时钟参考Reference 输入管脚对时钟输入幅度要求见表1所示。

purity� The paper introduces the basic working principle of HMC832, and provides the software and hardware design in practical application� The experimental results show that the device has excellent performance and good application value�Key words : HMC832; PLL; Phase Noise ; Spurious ; VCO图1 系统功能框图图2 参考输入内部等效电路图1.2 环路滤波环路滤波器件设计主要考虑相位裕度和环路带带宽。

数字锁相环的参数设计及其应用

・!"・

" 数字环路滤波器的参数设计

"$ ! 最小等效噪声带宽方案 当锁相环处于跟踪状态时, 环路的相位误差是 不大的。此时, 鉴相器可作为一个线性器件, 整个 环路就是一个线性系统。假设输入信号中伴有零 均值的高斯白噪声, 且噪声与信号不相关。设其功 率谱密度函数为 " %&% ’ # $! ( ) % * + # ,根据线性系统 理论,仅由噪声引起的环路输出相位误差的方差

/,

’$ $ $

/I

./ ( G1ABC 提供 ) 理论计算值 #- !# #- #"J #- #,$ #- #!K #- ##J #- ##" #- ##!4K #- #444 #- #"J" #- #,$# #- #!DJ #- ##IJ #- ##,4 #- ##!4D

很容易看出该方程有不动点 $$ . #5 *!5 其中 * 为自然数。 $$ . # 处就即锁相环锁定输入信号的状 态。 进一步分析必须将式( 变换成两个等价的一阶 4) 差分方程,即写成 !# 0 ! . ! ( !# ) 的标准非线性递推 !"# !"# $ $( #) 形式。 为此设 !# $ , 其中 5 于是, ( ( !# ! # $ $( # & !)

出 相 位 误 差 的 方 差 可 简 单 的 表 示 为 〈 & )%・%* * #。 直接计算 )% - 通常比较困难, 如果 "## 〉 将其转化为 + 平面上的闭合曲线积分,则可以利用 留数法求出 )% 的解析表达式。做 , ) #$! 的变量代 代入, 经过运算后可以得到, 换, 并将式( !) # !! ( " !! ・ !# - !# - # ! # )% & ( ( ) ( # ! ! - !# . / ) !! ! # (

基于PI控制的全数字锁相环设计

基于PI控制的全数字锁相环设计蒋小军;单长虹;原华;盛臻【摘要】To solve the problems of complex circuit, difficult design and poor performance existing in previous, systems, a new design method of all digital phase-locked loop (ADPLL) is proposed in this paper. The new ADPLL is realized by propor-tional-integral (PI) method rather than by conventional digital loop filtering control methods. The whole system is designed by using EDA technology and simulated by using computer. Simulation results shows, in certain frequency range, the longest time for the loop arriving its locked state is less then 15 cycles of the input signal, and the phase jitters is less than 5% of the output signal cycle. In addition, it has characteristics of simple structure, excellent loop performance, easy integration, etc.%针对以往全数字锁相环研究中所存在电路结构复杂、设计难度较大和系统性能欠佳等问题,提出了一种实现全数字锁相环的新方法.该锁相环以数字比例积分控制的设计结构取代了传统的一些数字环路滤波控制方法.应用EDA技术完成系统设计,并进行计算机仿真.仿真结果表明:在一定的频率范围内,该锁相环锁定时问最长小于15个输入信号周期,相位抖动小于输出信号周期的5%,且具有电路结构简单、环路性能好和易于集成的特点.【期刊名称】《现代电子技术》【年(卷),期】2013(036)002【总页数】3页(P141-143)【关键词】比列积分控制;全数字锁相环;超高速集成电路硬件描述语言;现场可编程门阵列【作者】蒋小军;单长虹;原华;盛臻【作者单位】南华大学电气工程学院,湖南衡阳421001;南华大学电气工程学院,湖南衡阳421001;南华大学电气工程学院,湖南衡阳421001;南华大学电气工程学院,湖南衡阳421001【正文语种】中文【中图分类】TN402-34锁相环在通信、无线电电子学和自动控制等领域得到了极为广泛的应用,它已成为各类电子系统中一个十分重要的部件。

基于Multisim的锁相环应用电路仿真

第30卷 第3期2008年6月电气电子教学学报J OU RNAL OF EEEVol.30 No.3J un.2008基于Multisim 的锁相环应用电路仿真王 刚,王艳芬,于洪珍(中国矿业大学信息与电气工程学院,江苏徐州221008)收稿日期:2008201203;修回日期:2008204220第一作者:王 刚(19772),男,硕士生,讲师,主要从事信号分析与处理方向的教学与研究。

E 2mail :wanggang77@摘 要:锁相环及其应用电路是“通信电子电路”课程教学中的重点内容。

本文设计了基于Multisim 的锁相环应用仿真电路,并将其引入课堂教学和课后实验。

文中首先给出了锁相环的仿真模型,然后构建了由其构成的锁相环调频、鉴频和接收仿真电路,并给出了仿真波形。

实践证明,采用这种方式可以帮助学生对相关内容的理解,并为今后进行系统设计工作打下良好的基础。

关键词:锁相环;Multisim ;调频电路;鉴频电路;接收电路中图分类号:TP391.9 文献标识码:A 文章编号:100820686(2008)0320067203The Simulation of PLL and Its Application Circuit B ased on MultisimWANG G ang ,WANG Yan 2fen ,Y U H ong 2zhen(School of I nf ormation &Engineering ,China universit y of Mine &Technology ,X uz hou 221008,China )Abstract :The p hase 2locked loop and it s application circuit are key content in t he teaching of Communication Elect ronic Circuit.This article designs some PLL application circuit based o n Multisim and int roduces it into teaching in class and experiment after class.First ,it gives t he PLL simulation model.Then it gives t he simulation model of f requency modulator ,frequency detector and receiver circuit based on Multisim.Finally ,it gives t he simulation profile .The p ractice proved t hat ,t his met hod can help t he st udent s to understand correlation content ,and build good foundation for f urt her system design work.K eyw ords :PLL ;Multisim ;frequency modulator ;frequency detector ;receiver circuit 锁相环是一种自动相位控制系统,广泛应用于通信、雷达、导航以及各种测量仪器中。

三阶数字锁相环环路参数的设计方法

2 三阶数字锁相环环路参数设计

三 阶数字锁相环路参数设计推导思路如下 : 由于三阶环是条件稳定 的, 先推导出三阶模拟 锁相环稳定条件 , 并计算出在稳定条件下 三阶模拟 锁相环的等效噪声带宽, 以等效噪声带宽为根据 , 将 模拟锁相环进行数字化 , 推导出三 阶数字锁相环 并

DP L, d g v s t e bo k d a r m f lo l r i lt n r s l s o h t t e d s n d t i r e L a i e h lc i g a o o p f t .Smu ai e u t h ws t a e i e r o d r n i e o h g h d DP L s t f st e r q i me ta d h s s b e p r r n e L a i e e u r s i h e n n a t l ef ma c . a o Ke r s: &C s se ;o p f tr y wo d Tr y tm l l ;DP L;l p p r me e ; e in i e L o a a tr d sg

三阶数字 锁相环环路参 数的设 计方法

杜 瑜

( 中国西南 电子技术研究所 , 成都 6 0 3 ) 10 6

摘

要: 为实现卫星移动环境下的精 密测距、 测速 , 分析 了三阶数字锁相环跟踪卫星多普勒频 率变化

的能力。利用理想二阶锁相环构造 了三阶环 , 对三阶环路的参数设计方法进行 了数学推导和仿真研 究, 分析 了三阶环的参数选择的原则, 并给 出了环路 滤波器的数字实现框图。仿真结果表明, 用推 利

来较大的误差。在这种情况下 , 三阶环或者更 高阶

1 引 言