S2M中文规格书

超快恢复二极管 ES2M SMB(DO-214AA)系列规格书推荐

CCLeoaamsdepFlMiareanette.FrSiianelis:ehMo/RordoldehersidnCgPoilnmafsoptrliimca.natti(oUNnLo) tFel1a)m("mPa"Sbuiliftfyix designates

VRMS 35 70 105 140 210 280 420 560 700

Maximum DC blocking voltage

VDC 50 100 150 200 300 400 600 800 1000

Maximum average forward rectified current

I(AV)

MAX 2.95 2.25 .20 .51 1.40 2.32 5.69 4.57 3.94

NOTE

MECHANICAL DATA

Case: JEDEC DO-214AA molded plastic body over passivated chip Terminals: Solder plated, solderable per MIL-STD-750, Method 2026 Polarity: Color band denotes cathode end Mounting Position: Any Weight :0.005 ounce, 0.138 grams

Cycles

Peak Forward Surge Current - Amperesversus Number Of Cycles At 60Hz - Cycles

Figure 5 New SMB Assembly

Round Lead Process

Figure 6 Reverse Recovery Time Characteristic And Test Circuit Diagram

2S2M-A资料

1998©Document No. D13535EJ2V0DS00 (2nf edition)Date Published April 2002 N CP(K)Printed in JapanTHYRISTORS2S2M, 2S4M2 A HIGH-SPEED SWITCHING SCRDATA SHEET2002The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.The 2S2M and 2S4M are P-gate fully diffused mold SCRs with an average on-current of 2 A. The repeat peak off-voltages (and reverse voltages) are 200 V and 400 V.FEATURES•This transistor is designed for high-speed switching and is deal for use in commercial frequencies, high-frequency pulse applications, and inverter applications.•This transistor features a small and lightweight package and is easy to handle even on the mounting surface due to its TO-202AA dimensions. Processing of lead wires and heatsink (tablet) using jigs is also possible.•Employs flame-retardant epoxy resin (UL94V-0).APPLICATIONSConsumer electronic euipments, ignitors of devices for light indutry, inverter, and solenoid valve drivesPACKAGE DRAWING (UNIT: mm)ABSOLUTE MAXIMUM RATINGS (Ta = 25°C)ParameterSymbol 2S2M 2S4M Ratings Unit Non-repetitive peak reverse voltage V RSM 300500V R GK = 1 k ΩNon-repetitive peak off-state voltage V DSM 300500V R GK = 1 k ΩRepetitive peak reverse voltage V RRM 200400V R GK = 1 k ΩRepetitive peak off-voltage V DRM 200400V R GK = 1 k ΩAverage on-state current I T(AV) 2 (Tc = 77°C, Single half-wave, θ = 180°)A Refer to Figure 6 snd 7.Surge on-state currentI TSM 20 (f = 50 Hz, Sine half-wave, 1 cycle)A Refer to Figure 2.High-frequency peak on-state current I TRM 15 (Tc = 65°C, f = 10 kp.p.s, t p = 10 µs)A −Fusing current∫ i t 2dt 1.6 (1 ms ≤t ≤10 ms)A 2s −Critical rate of rise of on-state current dI T /dt 50A/µs −Peak gate power dissipation P GM 0.5 (f ≥50 Hz, Duty ≤10%)W −Average gate power dissipation P G(AV)0.1W Peak gate forward current I FGM 0.2 (f ≥50 Hz, Duty ≤10%)A −Peak gate reverse voltage V RGM 6V −Junction temperature T j −40 to +125°C −Storage temperatureT stg−55 tp +150°C−Electrode connection <1>Cathode <2>Anode <3>GateStandard weight: 1.4*TC test bench-markData Sheet D13535EJ2V0DS2ELECTRICAL CHARACTERISTICS (T j = 25°C, R GK = 1 k Ω)TYPICAL CHARACTERISTICS (Ta = 25°C)Data Sheet D13535EJ2V0DS34Data Sheet D13535EJ2V0DS[MEMO]Data Sheet D13535EJ2V0DS5M8E 00. 4The information in this document is current as of July, 2001. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.N o part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. N EC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in N EC semiconductor products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment, and anti-failure features.NEC semiconductor products are classified into the following three quality grades:"Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application."Standard":Computers, office equipment, communications equipment, test and measurement equipment, audioand visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots"Special":Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disastersystems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)"Specific":Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, lifesupport systems and medical equipment for life support, etc.The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use N EC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.(Note)(1)"NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.(2)"NEC semiconductor products" means any semiconductor product developed or manufactured by or forNEC (as defined above).••••••。

MMPQ2222A;FFB2222A;中文规格书,Datasheet资料

ON CHARACTERISTICS

hFE DC Current Gain IC = 0.1 mA, VCE = 10 V IC = 1.0 mA, VCE = 10 V IC = 10 mA, VCE = 10 V IC = 150 mA, VCE = 10 V* IC = 150 mA, VCE = 1.0 V* IC = 500 mA, VCE = 10 V* IC = 150 mA, IB = 15 mA IC = 500 mA, IB = 50 mA IC = 150 mA, IB = 15 mA IC = 500 mA, IB = 50 mA 35 50 75 100 50 40

*Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2.0%

Spice Model

NPN (Is=14.34f Xti=3 Eg=1.11 Vaf=74.03 Bf=255.9 Ne=1.307 Ise=14.34f Ikf=.2847 Xtb=1.5 Br=6.092 Nc=2 Isc=0 Ikr=0 Rc=1 Cjc=7.306p Mjc=.3416 Vjc=.75 Fc=.5 Cje=22.01p Mje=.377 Vje=.75 Tr=46.91n Tf=411.1p Itf=.6 Vtf=1.7 Xtf=3 Rb=10)

Thermal Characteristics

Symbol

PD RθJA

TA = 25°C unless otherwise noted

Characteristic

Total Device Dissipation Derate above 25°C Thermal Resistance, Junction to Ambient Effective 4 Die Each Die FFB2222A 300 2.4 415

超快恢复二极管 ES2K SMB(DO-214AA)系列规格书推荐

CJ

25.0

Typical thermal resistance (NOTE 3)

RθJA

Operating junction and storage temperature range TJ T, STG

20.0 -50 to +150

Note:1.Reverse recovery condition IF=0.5A,IR=1.0A,Irr=0.25A 2.Measured at 1MHz and applied reverse voltage of 4.0V D.C. 3.Pulse test: Pulse width 200 sec, Duty cycle 2%

Cycles

Peak Forward Surge Current - Amperesversus Number Of Cycles At 60Hz - Cycles

Figure 5 New SMB Assembly

Round Lead Process

Figure 6 Reverse Recovery Time Characteristic And Test Circuit Diagram

FEATURES

CCLeoaamsdepFlMiareanette.FrSiianelis:ehMo/RordoldehersidnCgPoilnmafsoptrliimca.natti(oUNnLo) tFel1a)m("mPa"Sbuiliftfyix designates

MAX 2.95 2.25 .20 .51 1.40 2.32 5.69 4.57 3.94

NOTE

MECHANICAL DATA

Case: JEDEC DO-214AA molded plastic body over passivated chip Terminals: Solder plated, solderable per MIL-STD-750, Method 2026 Polarity: Color band denotes cathode end Mounting Position: Any Weight :0.005 ounce, 0.138 grams

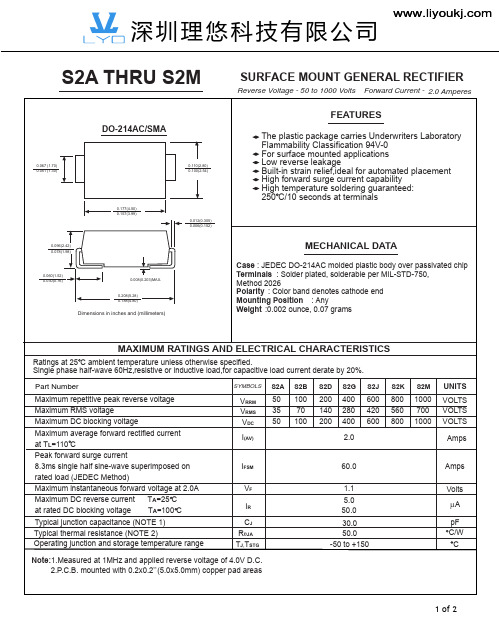

通用二极管S2A-S2M DO-214AC SMA系列规格书推荐

0.060(1.52) 0.030(0.76)

0.008(0.203)MAX.

0.208(5.28) 0.188(4.80)

Dimensions in inches and (millimeters)

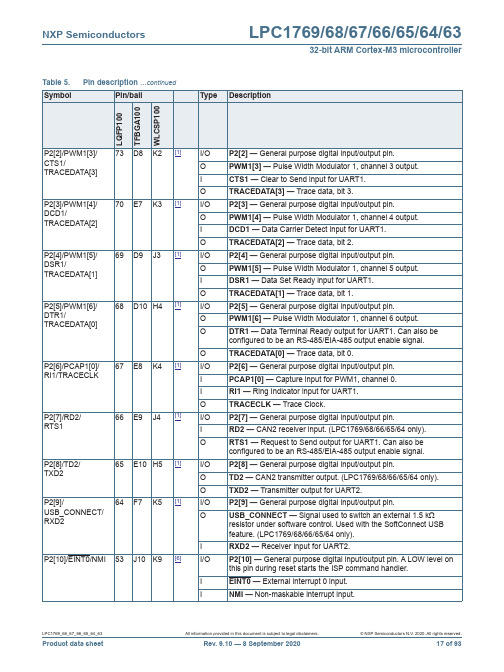

MAXIMUM RATINGS AND ELECTRICAL CHARACTERISTICS

Ratings at 25 C ambient temperature unless otherwise specified. Single phase half-wave 60Hz,resistive or inductive load,for capacitive load current derate by 20%. Part Number Maximum repetitive peak reverse voltage Maximum RMS voltage Maximum DC blocking voltage Maximum average forward rectified current at TL=110 C Peak forward surge current 8.3ms single half sine-wave superimposed on rated load (JEDEC Method) Maximum instantaneous forward voltage at 2.0A Maximum DC reverse current TA=25 C at rated DC blocking voltage TA=100 C Typical junction capacitance (NOTE 1) Typical thermal resistance (NOTE 2) Operating junction and storage temperature range

MEMORY存储芯片TMS320X2APJ中文规格书

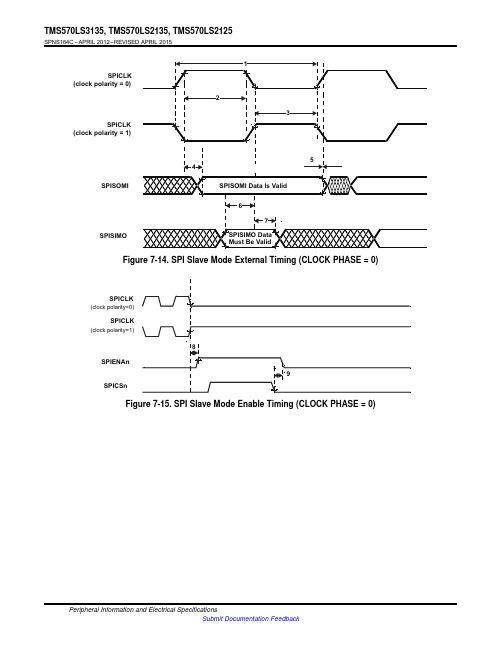

(clock polarity=1)SPIENAn 9SPISOMI SPICLK(clock polarity = 1)SPICLK (clock polarity = 0)Must Be ValidSPISOMI Data Is ValidSPISIMO TMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C –APRIL 2012–REVISED APRIL 2015Figure 7-14.SPI Slave Mode External Timing (CLOCK PHASE =0)Figure 7-15.SPI Slave Mode Enable Timing (CLOCK PHASE =0)Peripheral Information and Electrical SpecificationsTMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C–APRIL2012–REVISED APRIL2015 Table7-27.SPI Slave Mode External Timing Parameters(CLOCK PHASE=1,SPICLK=input,SPISIMO=input,and SPISOMI=output)(1)(2)(3)(4)NO.PARAMETER MIN MAX UNIT1t c(SPC)S Cycle time,SPICLK(5)40nst w(SPCH)S Pulse duration,SPICLK high(clock polarity=0)142(6)ns t w(SPCL)S Pulse duration,SPICLK low(clock polarity=1)14t w(SPCL)S Pulse duration,SPICLK low(clock polarity=0)143(6)ns t w(SPCH)S Pulse duration,SPICLK high(clock polarity=1)14Dealy time,SPISOMI data valid after SPICLK lowt d(SOMI-SPCL)S t rf(SOMI)+20(clock polarity=0)4(6)ns Delay time,SPISOMI data valid after SPICLK hight d(SOMI-SPCH)S t rf(SOMI)+20(clock polarity=1)Hold time,SPISOMI data valid after SPICLK hight h(SPCL-SOMI)S2(clock polarity=0)5(6)ns Hold time,SPISOMI data valid after SPICLK low(clockt h(SPCH-SOMI)S2polarity=1)Setup time,SPISIMO before SPICLK high(clockt su(SIMO-SPCH)S4polarity=0)6(6)ns Setup time,SPISIMO before SPICLK low(clock polarityt su(SIMO-SPCL)S4=1)High time,SPISIMO data valid after SPICLK hight v(SPCH-SIMO)S2(clock polarity=0)7(6)ns High time,SPISIMO data valid after SPICLK low(clockt v(SPCL-SIMO)S2polarity=1)Delay time,SPIENAn high after last SPICLK hight d(SPCH-SENAH)S 1.5t c(VCLK) 2.5t c(VCLK)+t r(ENAn)+22(clock polarity=0)8ns Delay time,SPIENAn high after last SPICLK low(clockt d(SPCL-SENAH)S 1.5t c(VCLK) 2.5t c(VCLK)+t r(ENAn)+22polarity=1)Delay time,SPIENAn low after SPICSn low(if new data9t d(SCSL-SENAL)S t f(ENAn)t c(VCLK)+t f(ENAn)+27ns has been written to the SPI buffer)Delay time,SOMI valid after SPICSn low(if new data10t d(SCSL-SOMI)S t c(VCLK)2t c(VCLK)+t rf(SOMI)+28ns has been written to the SPI buffer)(1)The MASTER bit(SPIGCR1.0)is cleared and the CLOCK PHASE bit(SPIFMTx.16)is set.(2)If the SPI is in slave mode,the following must be true:tc(SPC)S≤(PS+1)tc(VCLK),where PS=prescale value set in SPIFMTx.[15:8].(3)For rise and fall timings,see Table5-7.(4)t c(VCLK)=interface clock cycle time=1/f(VCLK)(5)When the SPI is in Slave mode,the following must be true:For PS values from1to255:t c(SPC)S≥(PS+1)t c(VCLK)≥40ns,where PS is the prescale value set in the SPIFMTx.[15:8]register bits.For PS values of0:t c(SPC)S=2t c(VCLK)≥40ns.(6)The active edge of the SPICLK signal referenced is controlled by the CLOCK POLARITY bit(SPIFMTx.17).Peripheral Information and Electrical SpecificationsSPISOMI Slave Out Data Is ValidSPICLK(clock polarity=1)SPIENAn9SPISIMOSPISOMIMust Be ValidSPISOMI Data Is ValidSPICLK (clock polarity = 1)SPICLK (clock polarity = 0)TMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C –APRIL 2012–REVISED APRIL 2015Figure 7-16.SPI Slave Mode External Timing (CLOCK PHASE =1)Figure 7-17.SPI Slave Mode Enable Timing (CLOCK PHASE =1)Peripheral Information and Electrical Specifications。

S2A;S2M;S2G;S2J;S2D;中文规格书,Datasheet资料

AccuPower¥Auto-SPM¥AX-CAP¥*BitSiC®Build it Now¥CorePLUS¥CorePOWER¥CROSSVOLT¥CTL¥Current Transfer Logic¥DEUXPEED®Dual Cool™ EcoSPARK®EfficientMax¥ESBC¥®Fairchild®Fairchild Semiconductor®FACT Quiet Series¥FACT®FAST®FastvCore¥FETBench¥FPS¥F-PFS¥FRFET®Global Power Resource SMGreen FPS¥Green FPS¥ e-Series¥G max¥GTO¥IntelliMAX¥ISOPLANAR¥Making Small Speakers Sound Louderand Better™MegaBuck¥MICROCOUPLER¥MicroFET¥MicroPak¥MicroPak2¥MillerDrive¥MotionMax¥Motion-SPM¥mWSaver¥OptoHiT¥OPTOLOGIC®OPTOPLANAR®®PDP SPM¥Power-SPM¥PowerTrench®PowerXS™Programmable Active Droop¥QFET®QS¥Quiet Series¥RapidConfigure¥¥Saving our world, 1mW/W/kW at a time™SignalWise¥SmartMax¥SMART START¥Solutions for Your Success™SPM®STEALTH¥SuperFET®SuperSOT¥-3SuperSOT¥-6SuperSOT¥-8SupreMOS®SyncFET¥Sync-Lock™®*The Power Franchise®TinyBoost¥TinyBuck¥TinyCalc¥TinyLogic®TINYOPTO¥TinyPower¥TinyPWM¥TinyWire¥TranSiC®TriFault Detect¥TRUECURRENT®*P SerDes¥UHC®Ultra FRFET¥UniFET¥VCX¥VisualMax¥XS™* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a)are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, orsystem whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.ANTI-COUNTERFEITING POLICYFairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website,, under Sales Support.Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.PRODUCT STATUS DEFINITIONSDefinition of TermsDatasheet Identification Product Status Definition分销商库存信息:FAIRCHILDS2A S2M S2G S2J S2D S2B S2K。

MEMORY存储芯片TMS27C512-20JL中文规格书

TPC10 SERIESCMOS FIELD-PROGRAMMABLE GATE ARRAYSSRFS001F D3864, DECEMBER 1989-REVISED FEBRUARY 1993package pin assignments (continued)0日且星星星星兰f毒S草草星星星807978777675 74 737271706968676665646362 61创595857565554535251NC 81NC 82838485GND 86GND 878889 CLK。

r1/0 9091 M。

DE92Ve e 93Ve e 94Ne95Ne96Ne 97 SDI。

r1/0 98 oeLK。

r1/0 99 PRA。

r1/0 100CCDDFMFMFMFUFMMHMHFUFUPU-MHMHMHMVMVRUFUMHMHMHmm咽锦衍MWH”“ωMM们MWM拥抱衍衍ma饵”招引1 2 3 4 5 6 7 8 9101112131415161718192021纽23242526272829302υ() ()()。

C8 星()()()zzzz;:, z o zzzz旨C,::,;-I iNOTES: A. All pins marked GND are ground connections and must be c。

nnected t。

circuit ground.B.生.e_mus巴巴erminated to V ee except during programming.e. PRA and PRB, the diagnostic probe outputs, should remain open if not used as I/Os.D.MODE must be terminated to circuit ground except during programming.tE.SDI and oeLK should be terminated to circuit ground during n。

MEMORY存储芯片MT48LC2M32B2TG-6A中文规格书

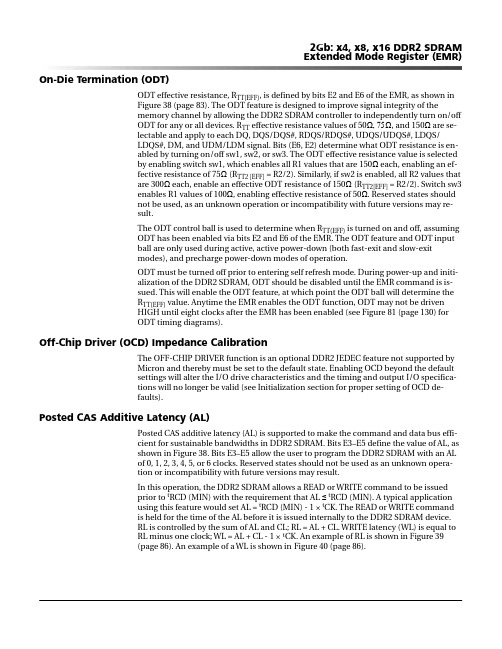

On-Die Termination (ODT)ODT effective resistance, R TT(EFF), is defined by bits E2 and E6 of the EMR, as shown in Figure 38 (page 83). The ODT feature is designed to improve signal integrity of thememory channel by allowing the DDR2 SDRAM controller to independently turn on/off ODT for any or all devices. R TT effective resistance values of 50˖ ˖, and 150˖ are se-lectable and apply to each DQ, DQS/DQS#, RDQS/RDQS#, UDQS/UDQS#, LDQS/LDQS#, DM, and UDM/LDM signal. Bits (E6, E2) determine what ODT resistance is en-abled by turning on/off sw1, sw2, or sw3. The ODT effective resistance value is selected by enabling switch sw1, which enables all R1 values that are 150˖ each, enabling an ef-fective resistance of 75˖ (R TT2 [EFF] = R2/2). Similarly, if sw2 is enabled, all R2 values that are 300˖ each, enable an effective ODT resistance of 150˖ (R TT2[EFF] = R2/2). Switch sw3enables R1 values of 100˖, enabling effective resistance of 50˖. Reserved states should not be used, as an unknown operation or incompatibility with future versions may re-sult.The ODT control ball is used to determine when R TT(EFF) is turned on and off, assuming ODT has been enabled via bits E2 and E6 of the EMR. The ODT feature and ODT input ball are only used during active, active power-down (both fast-exit and slow-exit modes), and precharge power-down modes of operation.ODT must be turned off prior to entering self refresh mode. During power-up and initi-alization of the DDR2 SDRAM, ODT should be disabled until the EMR command is is-sued. This will enable the ODT feature, at which point the ODT ball will determine the R TT(EFF) value. Anytime the EMR enables the ODT function, ODT may not be driven HIGH until eight clocks after the EMR has been enabled (see Figure 81 (page 130) for ODT timing diagrams).Off-Chip Driver (OCD) Impedance CalibrationThe OFF-CHIP DRIVER function is an optional DDR2 JEDEC feature not supported by Micron and thereby must be set to the default state. Enabling OCD beyond the default settings will alter the I/O drive characteristics and the timing and output I/O specifica-tions will no longer be valid (see Initialization section for proper setting of OCD de-faults).Posted CAS Additive Latency (AL)Posted CAS additive latency (AL) is supported to make the command and data bus effi-cient for sustainable bandwidths in DDR2 SDRAM. Bits E3–E5 define the value of AL, as shown in Figure 38. Bits E3–E5 allow the user to program the DDR2 SDRAM with an AL of 0, 1, 2, 3, 4, 5, or 6 clocks. Reserved states should not be used as an unknown opera-tion or incompatibility with future versions may result.In this operation, the DDR2 SDRAM allows a READ or WRITE command to be issued prior to t RCD (MIN) with the requirement that AL ื t RCD (MIN). A typical application using this feature would set AL = t RCD (MIN) - 1 × t CK. The READ or WRITE command is held for the time of the AL before it is issued internally to the DDR2 SDRAM device.RL is controlled by the sum of AL and CL; RL = AL + CL. WRITE latency (WL) is equal to RL minus one clock; WL = AL + CL - 1 × t CK. An example of RL is shown in Figure 39(page 86). An example of a WL is shown in Figure 40 (page 86).2Gb: x4, x8, x16 DDR2 SDRAM Extended Mode Register (EMR)Extended Mode Register (EMR)The extended mode register controls functions beyond those controlled by the mode register; these additional functions are DLL enable/disable, output drive strength, on-die termination (ODT), posted AL, off-chip driver impedance calibration (OCD), DQS#enable/disable, RDQS/RDQS# enable/disable, and output disable/enable. These func-tions are controlled via the bits shown in Figure 38. The EMR is programmed via the LM command and will retain the stored information until it is programmed again or the de-vice loses power. Reprogramming the EMR will not alter the contents of the memory ar-ray, provided it is performed correctly.The EMR must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time t MRD before initiating any subsequent opera-tion. Violating either of these requirements could result in an unspecified operation.Figure 38: EMR Definition21Notes: 1.E16 (BA2) is only applicable for densities ุ1Gb, reserved for future use, and must be pro-grammed to 0.2.Mode bits (E n ) with corresponding address balls (A n ) greater than E12 (A12) are re-served for future use and must be programmed to 0.3.Not all listed AL options are supported in any individual speed grade.4.As detailed in the Initialization section notes, during initialization of the OCD operation,all three bits must be set to 1 for the OCD default state, then set to 0 before initializa-tion is finished.2Gb: x4, x8, x16 DDR2 SDRAM Extended Mode Register (EMR)。

MEMORY存储芯片MT48H16M32L2B5-8IT中文规格书

Figure 16: RESET Procedure at Power Stable ConditionCKE R TTBG, BACK_t, CK_c Command Td Tc Don’t CareODT Th Ti Tj TkRESET_nTe TaTb Tf V DD , V DDQV PPTg Notes: 1.From time point Td until Tk, a DES command must be applied between MRS and ZQCLcommands.2.MRS commands must be issued to all mode registers that have defined settings.3.In general, there is no specific sequence for setting the MRS locations (except for de-pendent or co-related features, such as ENABLE DLL in MR1 prior to RESET DLL in MR0,for example).4.TEN is not shown; however, it is assumed to be held LOW.Uncontrolled Power-Down SequenceIn the event of an uncontrolled ramping down of V PP supply, V PP is allowed to be less than V DD provided the following conditions are met:•Condition A: V PP and V DD /V DDQ are ramping down (as part of turning off) from nor-mal operating levels.•Condition B: The amount that V PP may be less than V DD /V DDQ is less than or equal to 500mV .•Condition C: The time V PP may be less than V DD is ื10ms per occurrence with a total accumulated time in this state ื100ms.8Gb: x4, x8, x16 DDR4 SDRAM RESET and Initialization Procedure•Condition D: The time V PP may be less than 2.0V and above V SS while turning off is ื15ms per occurrence with a total accumulated time in this state ื150ms.Programming Mode RegistersFor application flexibility, various functions, features, and modes are programmable in seven mode registers (MR n ) provided by the device as user defined variables that must be programmed via a MODE REGISTER SET (MRS) command. Because the default val-ues of the mode registers are not defined, contents of mode registers must be fully ini-tialized and/or re-initialized; that is, they must be written after power-up and/or reset for proper operation. The contents of the mode registers can be altered by re-executing the MRS command during normal operation. When programming the mode registers,even if the user chooses to modify only a sub-set of the MRS fields, all address fields within the accessed mode register must be redefined when the MRS command is is-sued. MRS and DLL RESET commands do not affect array contents, which means these commands can be executed any time after power-up without affecting the array con-tents.The MRS command cycle time, t MRD, is required to complete the WRITE operation to the mode register and is the minimum time required between the two MRS commands shown in the t MRD Timing figure.Some of the mode register settings affect address/command/control input functionali-ty. In these cases, the next MRS command can be allowed when the function being up-dated by the current MRS command is completed. These MRS commands don’t apply t MRD timing to the next MRS command; however, the input cases have unique MR set-ting procedures, so refer to individual function descriptions:•Gear-down mode •Per-DRAM addressability •CMD address latency •CA parity latency mode •V REFDQ training value •V REFDQ training mode•V REFDQ training rangeSome mode register settings may not be supported because they are not required by certain speed bins.8Gb: x4, x8, x16 DDR4 SDRAM Programming Mode RegistersFigure 17: t MRD TimingDon’t CareCK_tCK_cCommand Settings CKEAddressNotes: 1.This timing diagram depicts CA parity mode “disabled” case.2.t MRD applies to all MRS commands with the following exceptions:Gear-down modeCA parity latency modeCMD address latencyPer-DRAM addressability modeV REFDQ training value, V REFDQ training mode, and V REFDQ training rangeThe MRS command to nonMRS command delay, t MOD, is required for the DRAM to update features, except for those noted in note 2 in figure below where the individual function descriptions may specify a different requirement. t MOD is the minimum time required from an MRS command to a nonMRS command, excluding DES, as shown in the t MOD Timing figure.Figure 18: tMOD TimingDon’t CareCK_tCK_cCommand Settings CKEAddress Notes: 1.This timing diagram depicts CA parity mode “disabled” case.2.t MOD applies to all MRS commands with the following exceptions:DLL enable, DLL RESET, Gear-down modeV REFDQ training value, internal V REF training monitor, V REFDQ training mode, and V REFDQ training range8Gb: x4, x8, x16 DDR4 SDRAM Programming Mode Registers。

MEMORY存储芯片MT48H16M32LFCM-6IT中文规格书

–

275

–

110

–

200

–

535

–

CK

28

ps

29, 30, 44

ps

20, 30

ps

29, 30, 44

ps

20, 30

ps

29, 30

ps

20, 30

ps

41

8Gb: x4, x8, x16 DDR3L SDRAM Electrical Characteristics and AC Operating Conditions

DQS, DQS# differential WRITE preamble

DQS, DQS# differential WRITE postamble

DQ Strobe Output Timing

DQS, DQS# rising to/from rising CK, CK#

DQS, DQS# rising to/from rising CK, CK# when DLL is disabled

DQS, DQS# differential input low pulse width

DQS, DQS# differential input high pulse width

DQS, DQS# falling setup to CK, CK# rising

DQS, DQS# falling hold from CK, CK# rising

Power-down entry period: ODT either synchronous or asynchronous

Power-down exit period: ODT either synchronous or asynchronous Power-Down Entry Minimum Timing ACTIVATE command to power-down entry

2DS M.2 模块 - 数据手册说明书

Copyright 2021 © Embedded Artists ABDocument status: Preliminary2DS M.2 Module DatasheetGet Up-and-Running Quickly andStart Developing Your Application On Day 1!Embedded Artists ABRundelsgatan 14211 36 MalmöSwedenhttps://Copyright 2021 © Embedded Artists AB. All rights reserved.No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of Embedded Artists AB.DisclaimerEmbedded Artists AB makes no representation or warranties with respect to the contents hereof and specifically disclaim any implied warranties or merchantability or fitness for any particular purpose. The information has been carefully checked and is believed to be accurate, however, no responsibility is assumed for inaccuracies.Information in this publication is subject to change without notice and does not represent a commitment on the part of Embedded Artists AB.FeedbackWe appreciate any feedback you may have for improvements on this document.TrademarksAll brand and product names mentioned herein are trademarks, services marks, registered trademarks, or registered service marks of their respective owners and should be treated as such.Table of Contents1Document Revision History4 2Introduction5 2.1Benefits of Using an M.2 Module to get Wi-Fi Connectivity5 2.2More M.2 Related Information5 2.3ESD Precaution and Handling5 2.4Product Compliance5 3Specification6 3.1Power Up Sequence7 3.2External Sleep Clock7 3.3Mechanical Dimensions7 3.4M.2 Pinning9 3.5VDDIO Override Feature12 3.6Test Points13 3.7Wi-Fi Interface Selection14 3.8Current Consumption Measurements15 4Antenna16 5Support17 6Regulatory18 7Disclaimers19 7.1Definition of Document Status201 Document Revision History2 IntroductionThis document is a datasheet that specifies and describes the 2DS M.2 module mainly from a hardware point of view. Software related issues, like the Linux and WICED drivers, are not addressed. There are separate documents for that.2.1 Benefits of Using an M.2 Module to get Wi-Fi ConnectivityThere are several benefits to use an M.2 module to add connectivity to an embedded design:∙Drop-in, certified solution!∙Modular and flexible approach to evaluate different Wi-Fi solutions - with different trade-offs around performance, cost, power consumption, longevity, etc.∙Access to maintained software drivers (Linux and SDK) with responsive support from Murata.∙Supported by Embedded Artists' Developer's Kits for i.MX RT/6/7/8 development, including advanced debugging support on carrier boards∙One component to buy, instead of 40+∙No RF expertise is required∙Developed in close collaboration with Murata and NXP2.2 More M.2 Related InformationFor more information about the M.2 standard and Embedded Artists' adaptation, see: M.2 PrimerFor more general information about the M.2 standard, see: https:///wiki/M.2The official M.2 specification (PCI Express M.2 Specification) is available from: 2.3 ESD Precaution and HandlingPlease note that the M.2 module come without any case/box and allcomponents are exposed for finger touches – and therefore extra attention mustbe paid to ESD (electrostatic discharge) precaution, for example use of static-free workstation and grounding strap. Only qualified personnel shall handle theproduct.Make it a habit always to first touch the mounting hole (which is grounded)for a few seconds with both hands before touching any other parts of theboards. That way, you will have the same potential as the board and therefore minimize the risk for ESD.In general touch as little as possible on the boards in order to minimize the risk of ESD damage. The only reasons to touch the board are when mounting/unmounting it on a carrier board.Note that Embedded Artists does not replace modules that have been damaged by ESD.2.4 Product ComplianceVisit Embedded Artists' website at /product_compliance for up to date information about product compliances such as CE, RoHS2, Conflict Minerals, REACH, etc.3 SpecificationThis chapter lists some of the more important characteristics of the M.2 module, but it is not a full specification of performance and timing. The main component in the design is Murata's 2DS module (full part number: LBWA0ZZ2DS), which in turn is based around NXP’s 88W8801 chipset.For a full specification, see Murata's 2DS Module (LBWA0ZZ2DS) product page:https:///type-2ds.html and the LBWA0ZZ2DS datasheet:https:///datasheet?/RFM/data/type2ds.pdf3.1 Power Up SequenceThe supply voltage shall not rise (10 - 90%) faster than 40 microseconds and not slower than 100 milliseconds.There is no specific timing requirement on the M.2 signal W_DISABLE1# (chipset signal PDN) during power-up, but it is recommended to keep the signal low until the module shall be initialized.Before initializing the module, and after the supply voltage has reached specification level, it is recommended to pull the M.2 signal W_DISABLE1# low for at least 10 milliseconds and then high.3.2 External Sleep ClockNo sleep clock signals is needed for the 2DS M.2 module.3.3 Mechanical DimensionsThe M.2 module is of type: 2230-S3-E according to the M.2 nomenclature. This means width 22 mm, length 30mm, top side component height 1.5 mm and key-E connector. Note that the length is not the standard 30mm, but rather a non-standard 59mm. The table below lists the different dimensions and weight.Embedded Artists has added a non-standard feature to the 2230 M.2 modules designed together with Murata, NXP and Infineon (former Cypress). The pictures below illustrates how the standard module size has been extended by 29 mm in the length direction in order to make room for the 2DS module "above" the GND mounting hole in the middle of the PCB.Figure 1 – M.2 Module Dimensions22 mm3.4 M.2 PinningThis section presents the pinning used for the M.2 module. It is essentially M.2 Key-E compliant with enhancements to support additional debug signals and 3.3V VDDIO override. The pin assignment for specific control and debug signals has been jointly defined by Embedded Artists, Murata, NXP and Infineon/Cypress.The picture below illustrates the edge pin numbering. It starts on the right edge and alternates between top and bottom side. The removed pads in the keying notch count (but are obviously non-existing).Figure 2 – M.2 Module Pin NumberingThe Wi-Fi interface uses the SDIO interface (and the 2DS module does not have a Bluetooth interface). The table below lists the pin usage for the 2DS M.2 modules. The column "When is signal needed" signals four different categories:∙Always: These signals shall always be connected.∙Wi-Fi: These signals shall always be connected then the Wi-Fi interface is used.∙Optional: These signals are optional to connect.3.5 VDDIO Override FeatureThe M.2 standard specify 1.8V logic level on several of the data and control signals. It is possible to override the voltage level for the 1.8V signals via pin 64. Apply a 3.3V / 100 mA supply to pin 64 in order to get 3.3V voltage level on all data and control signals.3.6 Test PointsThere are some test points that can be of interest to probe for debugging purposes, as illustrated in the picture below.Figure 3 – 2DS M.2 Module Test Points3.7 Wi-Fi Interface SelectionIt is possible to configure the Wi-Fi interface of the module; either SDIO (default) or USB. The picture below illustrates the location of the controlling resistor. Note that there is no publicly available driver that supports the USB interface. It is currently only available for specific high-volume customers (and this is out of control of Embedded Artists).Figure 4 – 2DS M.2 Module Wi-Fi Interface Selector3.8 Current Consumption MeasurementsIt is possible to measure the currents of the power supplies to the 2DS module, VBAT andVIO/VIO_SD. VBAT is the 3.3V the is supplied to the M.2 interface and VIO/VIO_SD is an on-board generated 1.8V. VIO/VIO_SD is generated from the supplied 3.3V.Note that zero ohm resistors are mounted by default. Select a series resistor with as low resistance as possible to keep the voltage drop to a minimum. Keep the drop below 100mV. VBAT can be slightly above 1 Amp in peak which means that maximum series resistance is 100 milliOhm for the VBAT resistor. For VIO/VIO_SD the current is lower so a 1 ohm resistor can be a suitable value.Figure 5 – Current Measurement4 AntennaThis chapter addresses the antenna side of the module. The 2DS module contains an on-board, reference certified pcb trace antenna. This antenna is the one that is used in the final product. For details, consult the 2DS datasheet from Murata.5 SupportEmbedded Artists supports customers that use our M.2 module in combination with Embedded Artists' Computer-on-Modules, (u)COM, based on NXP's i.MX RT/6/7/8 families.For other platforms, support is provided by Murata via their Community Support Forum:https:///s/topic/0TO5F0000002TLWWA2/connectivity-modules6 RegulatoryThe Murata 2DS module is reference certified. For details, consult the 2DS datasheet from Murata.7 DisclaimersEmbedded Artists reserves the right to make changes to information published in this document, including, without limitation, specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Customer is responsible for the design and operation of their applications and products using Embedded Artists’ products, and Embedded Artists acce pts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the Embedded Artists’ product is suitable and fit for the customer’s applications and products planned, as well as f or the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. Customer is required to have expertise in electrical engineering and computer engineering for the installation and use of Embedded Artists’ products.Embedded Artists does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the cus tomer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using Embedded Artists’ products in order to avoid a def ault of the applications and the products or of the application or use by customer’s third party customer(s). Embedded Artists does not accept any liability in this respect.Embedded Artists does not accept any liability for errata on individual components. Customer is responsible to make sure all errata published by the manufacturer of each component are taken note of. The manufacturer's advice should be followed.Embedded Artists does not accept any liability and no warranty is given for any unexpected software behavior due to deficient components.Customer is required to take note of manufacturer's specification of used components. Such specifications, if applicable, contain additional information that must be taken note of for the safe and reliable operation.All Embedded Artists’ products are sold pursuant to Embedded Artists’ terms and conditions of sale: /sites/default/files/docs/General_Terms_and_Conditions.pdfNo license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by Embedded Artists for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN EMBEDDED ARTISTS’ TERM S AND CONDITIONS OF SALE EMBEDDED ARTISTS DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF EMBEDDED ARTISTS PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY THE CEO OF EMBEDDED ARTISTS, PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, NUCLEAR, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE.Resale of Embedded Artis ts’ products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by Embedded Artistsfor the Embedded Artists’ product or service described herein and shall not crea te or extend in any manner whatsoever, any liability of Embedded Artists.This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.7.1 Definition of Document StatusPreliminary– The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Embedded Artists does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information. The document is in this state until the product has passed Embedded Artists product qualification tests.Approved– The information and data provided define the specification of the product as agreed between Embedded Artists and its customer, unless Embedded Artists and customer have explicitly agreed otherwise in writing.。

MEMORY存储芯片MAX202ECSE+T中文规格书

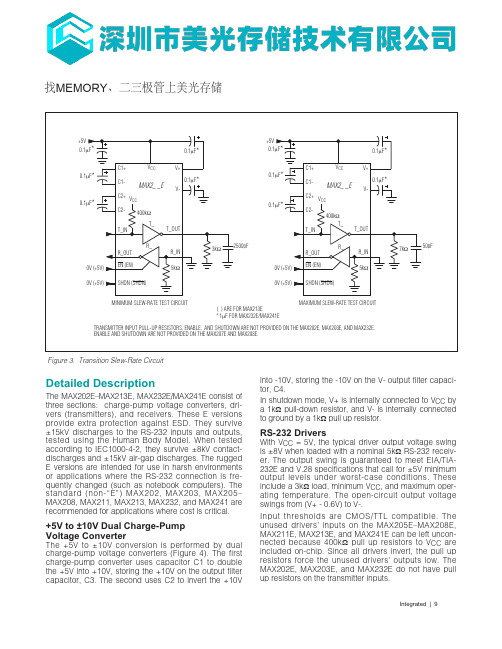

Figure 3. Transition Slew-Rate CircuitDetailed DescriptionThe MAX202E–MAX213E, MAX232E/MAX241E consist of three sections: charge-pump voltage converters, dri-vers (transmitters), and receivers. These E versions provide extra protection against ESD. They survive ±15kV discharges to the RS-232 inputs and outputs, tested using the Human Body Model. When tested according to IEC1000-4-2, they survive ±8kV contact-discharges and ±15kV air-gap discharges. The rugged E versions are intended for use in harsh environments or applications where the RS-232 connection is fre-quently changed (such as notebook computers). The standard (non-“E”) MAX202, MAX203, MAX205–MAX208, MAX211, MAX213, MAX232, and MAX241 are recommended for applications where cost is critical.+5V to ±10V Dual Charge-PumpVoltage ConverterThe +5V to ±10V conversion is performed by dual charge-pump voltage converters (F igure 4). The first charge-pump converter uses capacitor C1 to double the +5V into +10V, storing the +10V on the output filter capacitor, C3. The second uses C2 to invert the +10V into -10V, storing the -10V on the V- output filter capaci-tor, C4.In shutdown mode, V+ is internally connected to V CC by a 1kΩpull-down resistor, and V- is internally connected to ground by a 1kΩpull up resistor.RS-232 DriversWith V CC= 5V, the typical driver output voltage swing is ±8V when loaded with a nominal 5kΩRS-232 receiv-er. The output swing is guaranteed to meet EIA/TIA-232E and V.28 specifications that call for ±5V minimum output levels under worst-case conditions. These include a 3kΩload, minimum V CC, and maximum oper-ating temperature. The open-circuit output voltage swings from (V+ - 0.6V) to V-.Input thresholds are CMOS/TTL compatible. The unused drivers’ inputs on the MAX205E–MAX208E, MAX211E, MAX213E, and MAX241E can be left uncon-nected because 400kΩpull up resistors to V CC are included on-chip. Since all drivers invert, the pull up resistors force the unused drivers’ outputs low. The MAX202E, MAX203E, and MAX232E do not have pull up resistors on the transmitter inputs.找MEMORY、二三极管上美光存储Integrated | 9MAX202E–MAX213E, MAX232E/MAX241E±15kV ESD-Protected,5V RS-232 TransceiversShutdown and Enable Control(MAX205E/MAX206E/MAX211E/MAX213E/MAX241E)In shutdown mode, the charge pumps are turned off, V+ is pulled down to V CC, V- is pulled to ground, and the transmitter outputs are disabled. This reduces sup-ply current typically to 1µA (15µA for the MAX213E). The time required to exit shutdown is under 1ms, as shown in Figure 5.ReceiversAll MAX213E receivers, except R4 and R5, are put into a high-impedance state in shutdown mode (see Tables 1a and 1b). The MAX213E’s R4 and R5 receivers still function in shutdown mode. These two awake-in-shut-down receivers can monitor external activity while main-taining minimal power consumption.The enable control is used to put the receiver outputs into a high-impedance state, to allow wire-OR connection of two EIA/TIA-232E ports (or ports of different types) at the UART. It has no effect on the RS-232 drivers or the charge pumps.Note: The enable c ontrol pin is ac tive low for the MAX211E/MAX241E (EN), but is ac tive high for the MAX213E (EN). The shutdown control pin is active highFigure 4. Charge-Pump DiagramWhen in low-power shutdown mode, the MAX205E/MAX206E/MAX211E/MAX213E/MAX241E driver outputsare turned off and draw only leakage currents—even ifthey are back-driven with voltages between 0V and12V. Below -0.5V in shutdown, the transmitter output isdiode-clamped to ground with a 1kΩseries imped-ance.RS-232 ReceiversThe receivers convert the RS-232 signals to CMOS-logicoutput levels. The guaranteed 0.8V and 2.4V receiverinput thresholds are significantly tighter than the ±3Vthresholds required by the EIA/TIA-232E specification.This allows the receiver inputs to respond to TTL/CMOS-logic levels, as well as RS-232 levels.The guaranteed 0.8V input low threshold ensures thatreceivers shorted to ground have a logic 1 output. The5kΩinput resistance to ground ensures that a receiverwith its input left open will also have a logic 1 output.Receiver inputs have approximately 0.5V hysteresis.This provides clean output transitions, even with slowrise/fall-time signals with moderate amounts of noiseand ringing.In shutdown, the MAX213E’s R4 and R5 receivers haveno hysteresis.Integrated | 10。

MEMORY存储芯片LPC2210FBD144中文规格书

only).

O

MAT2[1] — Match output for Timer 2, channel 1.

I

RXD3 — Receiver input for UART3.

O

TRACEDATA[1] — Trace data, bit 1.

P2[5]/PWM1[6]/

68 D10 H4 [1]

I/O

P2[5] — General purpose digital input/output pin.

DTR1/ TRACEDATA[0]

O

PWM1[6] — Pulse Width Modulator 1, channel 6 output.

I/O

P2[4] — General purpose digital input/output pin.

DSR1/ TRACEDATA[1]

O

PWM1[5] — Pulse Width Modulator 1, channel 5 output.

I

DSR1 — Data Set Ready input for UART1.

specification. (LPC1769/68/67/66/65/63 only).

P2[12]/EINT2/ I2STX_WS

51 K10 K10 [6]

I/O

P2[12] — General purpose digital input/output pin.

I

EINT2 — External interrupt 2 input.

configured to be an RS-485/EIA-485 output enable signal.

P2[8]/TD2/ TXD2

丝印对照表

品牌物料编码物料名称规格样品表面印字备注扬杰14002313091贴片开关二极管YJ/SW-DI SOD-123FL 1N4148W LF T4扬杰14004710131快速恢复整流二极管YJ/RECT-DI DO-41 1A/1000V FR107 编带 LF FR107扬杰14028911011贴片开关二极管YJ/SW-DI LL-35 LL4148 LF无丝印没有杨杰的规格书扬杰14100103011贴片整流桥YJ/RECT-BR MBS 0.8A/600V MB06S LF MB6S扬杰14029802021整流二极管YJ/RECT-DI R-6 6A/1000V 6A10 LF6A10扬杰14011800131整流二极管YJ/RECT-DI DO-41 1A/1000V HER103 编带LF HER103丝印对照表扬杰14031162021超快速恢复整流二极管YJ/RECT-DI TO-220AC 10A/200V MUR1020 LF MUR1020扬杰14004300031肖特基二极管YJ/SCHOTTKY-DI DO-201AD 3A/100V SR3100 LF SR3100扬杰14027200041快速恢复整流二极管YJ/RECT-DI DO-15 2A/200V HER203 编带 LF HER203扬杰14029805011整流二极管YJ(杨杰)/RECT-DI DO-201AD 6A/1000V 6A10 编带LF6A10扬杰14001600021整流二极管YJ/RECT-DI DO-201AD 3A/1000V 1N5408 LF1N5408扬杰14001800011整流二极管YJ/RECT-DI DO-41 1A/1000V UF4007 LF UF4007扬杰14107510021贴片整流桥YJ/RECT-BR 0.8A/1000V MB10S LF MB10S扬杰14023360031贴片快速恢复整流二极管YJ/RECT-DI SMA-W 1A/1000V RS1M LF RS1M扬杰14216303011贴片快速恢复整流二极管YJ/RECT-DI SMA-W 1A/200V RS1D LF RS1D扬杰14007500011快速恢复整流二极管YJ/RECT-DI DO-41 1A/200V FR103 LF FR103无规格书扬杰14001500031整流二极管YJ/RECT-DI DO-41 1N4004 LF1N4004无规格书扬杰14002203131贴片整流二极管YJ/RECT-DI SOD-123FL 1A/1000V G1M LF G1M扬杰14029700021肖特基二极管YJ(杨杰)/RECT-DI DO-41 2A/100V SR2100 编带LFSR2100扬杰14031861011贴片二极管YJ/DI SOD-123 200mA/250V BAV20W LF H2扬杰14000660021超快速恢复整流二极管YJ/RECT-DI DO-204AL(DO-41) 1A/600V BYV26C LF BYV26C扬杰14002200021整流二极管YJ/RECT-DI DO-41 1N4007 编带 LF1N4007扬杰14031961011贴片开关二极管YJ/DI SOD-123 200mA/250V BAV21W LF H3扬杰14027900031整流二极管YJ/RECT-DI DO-15(DO-204AC) 2A/1000V RL207 LF RL207扬杰14000200031肖特基二极管YJ/SCHOTTKY-DI DO-41 1A/60V SR160 编带 LF SR160扬杰14031803021肖特基二极管YJ/SCHOTTKY-DI DO-201AD 3A/40V SR340 LF SR340扬杰14031852031贴片肖特基二极管YJ/SCHOTTKY-DI DO-214AA(SMB) 2A/100V SS210LFSS210商贸通14008323011贴片稳压二极管NXP/ZEN-DI SOT-23 4V7 5% BZX84-C4V7 LF Z1W详见附录四商贸通14003523041贴片稳压二极管NXP/ZEN-DI SOD80C 30V±5% 1/2W BZV55-C30 LF无丝印商贸通14013953011贴片二极管NXP/DI SOT-23 PESD2CAN LF6R*商贸通14028003011贴片肖特基二极管ST/SCHOTTKY-DI DPAK STPS15L45CB LF S15L45C商贸通14031223031贴片稳压二极管NXP/ZEN-DI SOD80C 6V2±5% 1/2W BZV55-C6V2LF无丝印商贸通14032023011贴片稳压二极管ON/ZEN-I SOD-123 5V1 1/2W MMSZ5231BT1G LF E1Y ·商贸通14008223011贴片稳压二极管NXP/ZEN-DI SOT-23 5V1 5% BZX84-C5V1 LF Z2W详见附录四商贸通14032342011贴片稳压二极管NXP/ZEN-DI SOT-23 30V 5% BZX84-C30 LF W T5详见附录四商贸通14007043011贴片双向瞬态电压抑制二极管ONSEMI/TVS-DI DO-214AA(SMB) P6SMB30AT3 LFC2430A·商贸通14002313161贴片开关二极管ON/SW-DI SOD-123 MMSD4148T1G-D LF 51 6·商贸通14006323011贴片稳压二极管NXP/ZEN-DI SOT-23 33V 5% BZX84-C33 LF W T6详见附录四正力泰电子14000423041贴片稳压二极管SEMTECH/ZEN-DI LL-41 5V1±5% 1W ZM4733A LF无丝印正力泰电子14002313071贴片开关二极管SEMTECH/SW-DI SOD-80 LL4148 LF无丝印正力泰电子14032432011贴片稳压二极管SEMTECH/ZEN-DI SOD-123 12V 1/2W MM1Z12V LF5D无规格书正力泰电子14004710051快速恢复整流二极管SIYU/RECT-DI DO-41 1A/1000V FR107 编带 LF FR107正力泰电子14033701011快速恢复整流二极管SIYU/RECT-DI DO-15 2A/600V SF28 编带LF SF28正力泰电子14002200041整流二极管SIYU/RECT-DI DO-41 1N4007 编带 LF1N4007正力泰电子14000920131稳压二极管SEMTECH/ZEN-DI DO-35 12V 1/2W BZX55C12 LF C12无规格书大昌14031803011肖特基二极管SIYU/SCHOTTKY-DI DO-27 3A/40V SB340 LF SB340正力泰电子14031162011超快速恢复整流二极管SIYU/RECT-DI TO-220AC 10A/200V DFR10A20 LF DFR10A20聚泉鑫14029403011贴片整流二极管SIYU/RECT-DI SMB (DO-214AA) S2M LF S2M SEMTECH14001120021稳压二极管SEMTECH/ZEN-DI DO-41 24V 5% 1W 1N4749A LF1N4749A正力泰电子14030820021稳压二极管SEMTECH/ZEN-DI DO-35 3V9 2% 1/2W BZX55B3V9LFB3V9SEMTECH14003522021稳压二极管SEMTECH/ZEN-DI DO-35 30V 1/2W 1N5256B 编带LFC30正力泰电子14000523031贴片稳压二极管SEMTECH/ZEN-DI LL-34 5V6 1/2W ZMM5V6 LF无丝印无规格书正力泰电子14002310051开关二极管SEMTECH/SW-DI DO-35 1N4148 编带 LF4148正力泰电子140005201A1稳压二极管SEMTECH/ZEN-DI DO-41 5V6 1W 1N4734A LF1N4734A正力泰电子14000420311稳压二极管SEMTECH/ZEN-DI DO-41 5V1 2W BZX2C5V1RL LF C5V1正力泰电子14005803011快速恢复整流二极管SIYU/RECT-DI DO-41 1A/400V FR104 LF FR104正力泰电子14027320011稳压二极管SEMTECH/ZEN-DI DO-41 11V 1W 1N4741 LF1N4741SEMTECH14009623031贴片稳压二极管SEMTECH/ZEN-DI LL-34 11V±5% 1/2W BZV55C11LF无丝印无规格书闽达14033502011贴片稳压二极管江苏长电/ZEN-DI SOD-123 28V/0.35WMMSZ5255B(丝印:K5) LFK5详见附录2聚泉鑫14000920061稳压二极管SEMTECH/ZEN-DI DO-41 12V 1W 1N4742A LF1N4742A 闽达14007713041贴片开关二极管江苏长电/SW-DI(双管) SOT-23 BAV99 LF A7正力泰电子14000660081超快速恢复整流二极管SIYU/RECT-DI DO-41 1A/600V BYV26C LF BYV26C闽达14000920211稳压二极管SEMTECH/ZEN-DI DO-41 12V 2W BZX2C12 LF C12正力泰电子14023370061贴片快速恢复整流二极管SIYU/RECT-DI SMA-W 1A/1000V RS1M LF RS1M正力泰电子14030720011稳压二极管SEMTECH/ZEN-DI DO-35 16V 1/2W 1N5246B 编带LF1N5246B 聚泉鑫14002313131贴片开关二极管SEMTECH/SW-DI SOD-123 1N4148W LF W1正力泰电子14024161021贴片超快速恢复整流二极管SIYU/RECT-DI SOD123FL 1A/1000V US1ML LF UM正力泰电子14002310011开关二极管SIYU/SW-DI DO-35 1N4148 编带 LF1N4148正力泰电子14005500031肖特基二极管SIYU/SCHOTTKY-DI DO-27 3A/150V SB3150 LF SB315聚泉鑫14000120111稳压二极管SEMTECH/ZEN-DI DO-41 20V 5% 1W 1N4747A LF1N4747A正力泰电子14016503011稳压二极管SEMTECH/ZEN-DI DO-35 11V±5% 1/2W 1N5241BLF1N5241B正力泰电子14024160021贴片超快速恢复整流二极管SIYU/RECT-DI SMA 1A/1000V US1M LF US1M聚泉鑫14031603031肖特基二极管SIYU/RECT-DI DO-27 SB5200 LF SB5200。

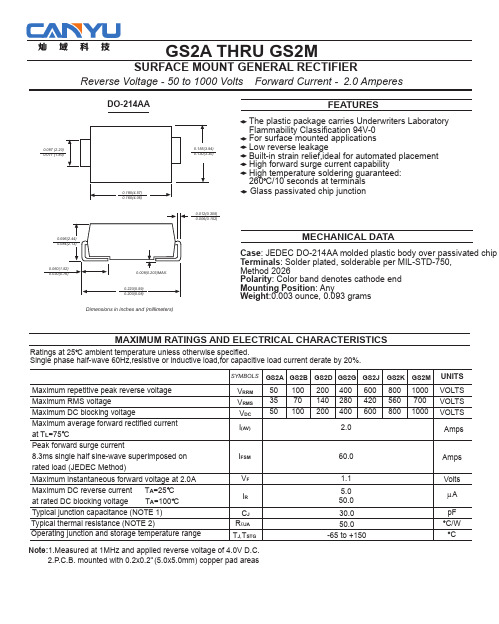

GS2A-GS2M PDF规格书

0.012(0.305) 0.006(0.152)

FEATURES The plastic package carries Underwriters Laboratory Flammability Classification 94V-0 For surface mounted applications Low reverse leakage Built-in strain relief,ideal for automated placement High forward surge current capability High temperature soldering guaranteed: 260 C/10 seconds at terminals Glass passivated chip junction

1

0.1 TJ=25 C

0.01 0

20

40

60

80

100

PERCENT OF PEAK REVERSE VOLTAGE,%

FIG. 6-TYPICAL TRANSIENT THERMAL IMPEDANCE

100

10

1

0.1

0.01

0.1

1

10

100

t,PULSE DURATION,sec.

JUNCTION CAPACITANCE, pF

0.155(3.94) 0.130(3.30)

0.180(4.57) 0.160(4.06)

0.096(2.44) 0.084(2.13)

0.060(1.52) 0.030(0.76)

0.008(0.203)MAX.

0.220(5.59) 0.200(5.08)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

To learn more about ON Semiconductor, please visit our website atPlease note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor’s system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (_), the underscore (_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can befound at . Please email any questions regarding the system integration to Fairchild_questions@.ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at /site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changeswithout further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of theapplication or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. “Typical” parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associatedS2A - S2M — General-Purpose Rectifiers (Glass Passivated)S2A - S2MGeneral-Purpose Rectifiers (Glass Passivated)Features•High-Current Capability, 2 A Rated•Fast Response: 2 μs T rr•Low-Forward Voltage Drop, 1.15 V V F Max at 2 A•High-Surge Current Capability, 50 A 2s I FSM•Glass Passivated Junction•RoHS Compliant•UL Certified, UL #E258596Applications•Power Supplies•AC to DC Rectification•Bypass Diodes Ordering InformationPart NumberMarking Package Packing Method S2AS2A DO-214AA (SMB)Tape and ReelS2BS2B S2DS2D S2GS2G S2JS2J S2KS2K S2M S2M Description The S2 family of devices are general-purpose 2 A rated rectifiers with voltage ratings ranging from 50 to 1000 V.They are implemented in traditional SMB packages and are well known to the industry. For advanced or special requirements, please contact a Fairchild Semiconductor representative.SMB/DO-214AA COLOR BAND DENOTES CATHODE2.202.504.70 2.65MAX2.451.90B 0.2030.0500.300.052.15 1.65A0.13M C B AC 3.953.30B2.201.91B5.605.08B4.754.050.13M C B ABA0.410.151.600.75R0.15 4X8°0°0.450-8°DETAIL ASCALE 20 : 1LAND PATTERN RECOMMENDATIONGAUGEPLANENOTES:A.EXCEPT WHERE NOTED CONFORMS TOJEDEC DO214 VARIATION AA.B DOES NOT COMPLY JEDEC STD. VALUE.C.ALL DIMENSIONS ARE IN MILLIMETERS.D.DIMENSIONS ARE EXCLUSIVE OF BURRS,MOLD FLASH AND TIE BAR PROTRUSIONS.E.DIMENSION AND TOLERANCE AS PER ASMEY14.5-1994.ND PATTERN STD. DIOM5336X240M.G.DRAWING FILE NAME: DO214AAREV1S2A - S2M — General-Purpose Rectifiers (Glass Passivated) Figure 6. 2-LEAD, SMB, JEDEC DO-214, VARIATION AA。