Cadence 后端实验系列19_版图验证_ Assura

Cadence数字集成电路版图设计与验证 实验指导书 (电子科技大学)

数字集成电路版图设计与验证实验指导书电子科技大学微电子与固体电子学院实验名称数字集成电路版图设计与验证一、实验目的与意义随着IT产业的迅猛发展,微电子集成电路在通讯、计算机及其他消费类电子产品中的重要地位日益突出,而IC的生产和设计技术水平是决定IC芯片性能的两大要素。

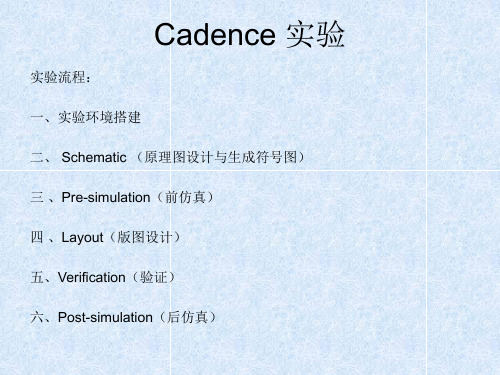

该实验是正向设计中电路仿真完成之后、工艺制版之前的必须环节,与其他实验相结合,可以使学生对当前国际主流的IC设计技术流程有较完整的认识。

本实验是基于微电子技术应用背景和《微电子集成电路》课程设置及其特点而设置,为IC设计性实验。

其目的在于:•根据实验任务要求,综合运用课程所学知识自主完成相应的数字集成电路版图设计,掌握基本的IC版图布局布线技巧。

•学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的自动布局布线设计与验证。

通过该实验,使学生掌握数字专用集成电路版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力,掌握自主进行数字集成电路版图设计与验证的基本方法,进而为今后从事科研、开发工作打下良好基础。

二、实验原理2. 1 Cadence 环境的调入1、在UNIX 操作系统的Terminal窗口下→ cd user/userxxx/studname/Project→ icms& 或icfb&2、出现CIW(command Interpreter window)命令解释画面3、点选在CIW窗口的上面工具列Tools→Library Manager,会出现LM窗口LM(Library Manager)2. 2 建立新的Library1.点选LM窗口上面的工具列File→New→Library2.会产生New Library画面3.出现下图画面1.在name填上Library名称2.点选下面的OK4.出现Load Technology File窗口,添加工艺文件2.3 电路版图的自动布局布线2.3.1 启动Automatic Layout Tool1.打开已经设计完成的电路图Schemic2.点选 Tools --> Design Synthesis --> Device-Level Editor ,将弹出对话框,定义版图名,最好取与前面cell view 相同的名字。

assura(for mixed signal)

• Verilog netlist cross-probing • New Short Locator user interface simplifies locating errors • Support for mixed netlist methodologies (DFII schematic, Verilog, CDL) • Extracted view created after LVS run for simulation and probing purposes

• Rule files targeted for .25µm and below: logic, MS/RF, and SiGe • Rule Decks provided by Cadence to the foundries

– Foundry decks available for Assura DRC, LVS, and RCX for major merchant foundries – Supporting Dracula and Diva decks as well for .25 and below

– hypertexted report to locate shorts and opens faster – net and device probing for tracing connections – new rewire function reports required changes to correct the layout

– user selectable sorting mechanisms for error reports – improved error visibility (easy color and stipple pattern customization) – improved error hiding and exception handling (individual or by area)

芯片后端验证

layout view 上亦會以閃動方式顯示錯 誤。

1芯4 片后端验证

版图验证工具-DIVA

分析错误(Explain)

1芯5 片后端验证

版图验证工具-DIVA

click 於閃動處以得悉所違犯 rule 的說明

在 CIW 上所看到違犯 rule 的 項目

2芯片后端验证

版图验证工具-DIVA

❖ Diva -Design Interactive Verification Automation

DIVA 是 Cadence软件中的验证工具集, 用它可以找出并纠正设计中的错误.它除了可 以处理物理版图和准备好的电气数据,从而进 行版图和线路图的对查(LVS)外。还可以在 设计的初期就进行版图检查,尽早发现错误并 互动地把错误显示出来,有利于及时发现错误 所在,易于纠正。

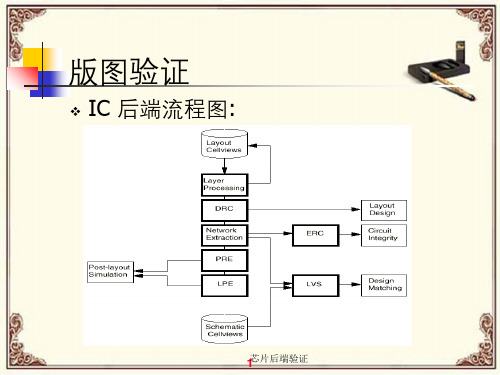

版图验证

❖ IC 后端流程图:

1芯片后端验证

Cadence 版图验证工具

Diva

Diva 是 Cadence 的版图编辑大师Virtuoso集 成的交互式版图验证工具,具有使用方便、操 作快捷的特点,非常适合中小规模单元的版图 验证。

Dracula

Dracula(吸血鬼)是 Cadence 的一个独立的 版图验证工具,按批处理方式工作,功能十分 强大,目前是完整芯片验证的标准。

❖ 提取层次

Flat Hierarchical Micro

1芯8 片后端验证

版图验证工具-DIVA

Extractor 界面

1芯9 片后端验证

版图验证工具-DIVA

Extract 主要 是抽取出一 些參數來提 供 LVS 時做 比對用。

查看 CIW 上出現 no error 後再到 library browser 就可看到一個 extracted view

cadence_实验

• 4、vi .cdsinit 在文件的最后一行的上面添加如下 内容(添加内容的前面没有分号) : • load(“/opt/mentor/caliber/lib/caliber.skl”) • load(“/opt/mentor/caliber/lib/caliber.4.3.skl”) • 主要用于版图的验证使用 • 如图所示:

• 接着添加vdd 与gnd

• 添加管脚,使用快捷键p,Pin Names 为in,Direction 为input, Usage 为schematic,然后在原理图编辑窗口空白处点击一下鼠标, 会出现输入管脚in 。

• 使用相同的方法,添加输出管脚out,此时Pin Names 为out, Direction 为output,Usage 为schematic 。

•

• 创建视图单元/原理图(cell view):在主 窗口中Tools->Library Manager,在 Library 中单击 wo(刚才建立的新库),在 Library Manager 窗口,然后选择File->New->Cell View,设置Cell Name为inv,View Name 为Schematic,Tool为ComposerSchematic,点击OK ,弹出Schematic Editing的空白窗口。

一、实验环境搭建

• 1、解压TSMC0.35.tgz 使用命令:tar –xzf TSMC0.35.tgz • 2、新建一个工作目录:mkdir jiang 将用到的工艺文件和 显示文件(在TSMC035/Virtuoso 下面)拷贝至工作目录 jiang下 。 • 工艺文件:035ms.tf 显示文件:display.drf • 3、拷贝IC工具自带的.cdsinit文件到工作目录jiang下面 3 IC .cdsinit jiang • cp /opt/asic_labs/apps/IC5141/tools.lnx86/dfII/cdsuser/.cdsi nit ./ • 这样,在原理图和版图界面中就可以使用快捷键了。

Cadence版图设计环境的建立及设计规则的验证

Cadence 版图设计环境的建立及设计规则的验证王翠霞,范学峰,许维胜,余有灵,王子君(同济大学半导体与信息技术研究所 上海 200092)摘 要:对版图设计需要的工艺库(techno logy file )文件、显示(disp lay )文件的书写进行了详细分析,并对设计规则验证(DRC )中遇到的问题进行了解释。

关键词:工艺库;显示文件;设计规则验证;版图中图分类号:TN 919181 文献标识码:B 文章编号:1004373X (2004)1501803Env ironm en t Setup of Layout and Ver if ica tion of D esign Rules i n CadenceW AN G Cu ix ia ,FAN Xuefeng ,XU W eisheng ,YU You ling ,W AN G Zijun(Institute of Se m iconducto r &Info r m ati on Techno l ogy ,TongjiU niversity ,Shanghai ,200092,Ch ina )Abstract :In th is paper ,the techno logy file and disp lay file w ere elabo rated exp lained befo re layou t ,and the p rob lem s of design ru le checker w ere dealed 1Keywords :techno logy file ;disp lay file ;design ru le checker ;territo ry收稿日期:20040402基金项目:AM 基金项目(0101) Cadence 提供的V irtuo so 版图设计及其验证工具强大的功能是任何其他EDA 工具所无法比拟的,故一直以来都受到了广大EDA 工程师的青睐[1],然而V irtuo so 工具的工艺库的建立和D racula 的版图验证比较繁琐。

cadence简介

现在需要设置元件参数,有三种方法,①菜单栏-> Edit-> Properties-> Objects,再点击要修改参数的元件,②先选中器件,再键入快捷键q,③选中器件,再点击工具栏Propertiy。

参数可以是以下三种形式的各种数学组合表达式,①变量,②常量,③skill语言函数。变量作参数会在仿真时用到。常量和skill语言函数作参数,在下面就会用到。

同样的方法继续设置NMOS参数,只是模型名为n18,栅长为固定值0.18u,栅宽设为pPar(“wn”)。设置好参数后的电路图如图3.9所示。

注意:①设置参数时不要自己输入单位,系统会自动加上。比如0.18uM是错误的写法。如果非要自己写单位,也要和数值之间留一个空格,否则系统会把M识别为变量。

2.

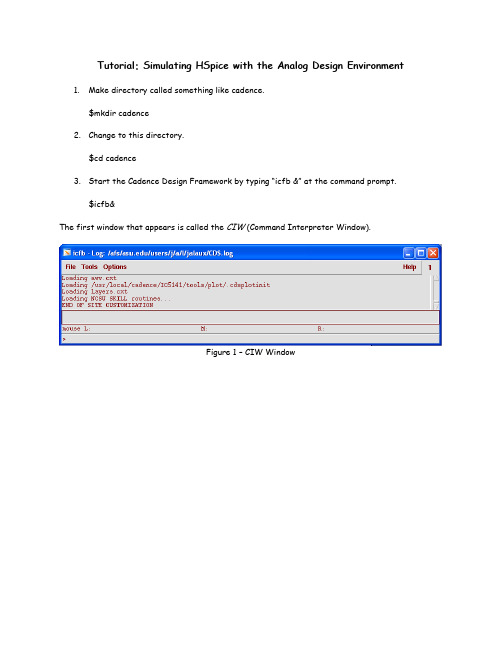

现在,我们可以启动Cadence了。在终端中输入命令

icfb&

出现Cadence初始界面,如图2.1所示。

然后就会打开Cadence的主控窗口CIW(Command Interpreter Window)。如图2.2所示:

这就是Cadence的集成设计环境,Cadence的大部分工具都可以从这里打开。其中最上方是标题栏,第二行是菜单栏。中间部分是输出区域,许多命令的结果在这里显示。一些出错信息也在这里显示,要学会从输出区域中获取相应的信息。接下来一行是命令输入行。Cadence的许多操作可以通过鼠标执行,也可以通过输入命令来执行。

进入连线命令后,于起点单击左键,再于终点单击左键。画完一段导线后,此时并没有退出画线命令,可以继续画连接线,直到画完所所有的连接线后,按ESC退出画线命令。连好线的电路图如图3.7所示。其中左右两条水平导线是后面连连接端口用的。

还可以对画好的线进行命名,键入快捷键l,在弹出的对话框中输入线名,比如a,点击Hide,然后将字母a移动到要命名的线附近点击左键放下,如果名字离线较远,则要求再单击所要命名的线。

cadence版图使用说明

目录目录 (1)设计环境介绍 (2)工作站常用命令 (2)运行Cadence (6)运行Layout (10)运行schematic的编辑 (15)生成schematic symbol (18)运行Artist的仿真环境 (20)设计示例的简单介绍 (21)设计环境介绍典型的全定制Full-Custom模拟集成电路设计环境1. 集成的设计环境-Cadence Design Framework II是众多Cadence 工具集成在一起的统一的界面,通过这个架构,不用繁琐的数据格式转换,就可以方便的从一个工具转到另一个工具。

其中包括很多软件,如:原理图编辑工具-Composer布局编辑工具-Candence virtuoso布局验证编辑工具-Diva, Dracula2. 电路网表或原理图编辑环境-Text editor / schematic editor3. 电路模拟软件-spice操作系统环境和硬件平台1.SUN工作站;UNIX系统2.运行Linux的PC3.作为终端的PC工作站常用命令一、在terminal窗口键入的基本命令:1. ls:列出目录下所有文件。

2. clear:清除terminal窗口里的内容。

3. pwd:显示目前工作的目录。

4. cd:改变当前目录。

5. rm:刪除文件。

6. cp:复制文件。

7. mv:移动文件。

8. mkdir:建立目录。

9. rmdir:刪除目录。

10. find:寻找文件。

11. passwd:改变当前用户密码。

12. finger:显示当前用户信息。

二、基本操作和命令的使用介绍:1.从PC登录工作站,一般使用exeed或Xmanager。

login :___________(输入username)password:___________(输入密码)2.登出步骤:点击exit3.在线命令说明(以下的example% 表示系统的提示符)example% man [command-name]4. 改变当前目录example% cd [name]Example:example% cd dir1 改变目录位置,至dir1目录下。

cadence版图仿真教程

Tutorial: Simulating HSpice with the Analog Design Environment1.Make directory called something like cadence.$mkdir cadence2.Change to this directory.$cd cadence3.Start the Cadence Design Framework by typing “icfb &” at the command prompt.$icfb&The first window that appears is called the CIW (Command Interpreter Window).Figure 1 – CIW WindowAnother window that appears is the Library Manager. This window allows you to browse the available libraries and create your own.Figure 2 – Library Manager WindowIn the Library Manager, create a new library called EEE534. Select File->New->Library. This will open a new dialog window, in which you need to enter the name of your library, library path, and "Attach to existing tech library." Fill out the form as shown below, then select OK.Figure 3 – Create Library FormYou should see the library "EEE534" appear in the Library Manager.Figure 4 – Library Manager display newly created libraryNext, select the library you just created in the Library Manager and select File->New->Cell View.... We will create a schematic view of an inverter cell. Simply type in "INV" under cell-name and "schematic" under view. Click OK or hit the Enter key. Note: that the "Tool" is automatically set to "Composer-Schematic", the schematic editor.Figure 5 – Create New File FormAlternatively, you could select the "Composer-Schematic" tool, instead of typing out the view name. This will automatically set the view name to "schematic".After you hit "OK", the blank Composer screen will appear.Figure 6 – Virtuoso Schematic EditorTo generate a schematic, you will need to go through the following steps:•From the Schematic Window, choose Add->instance. The Component Browser, will then pop up.•In the Library field, select NCSU_Analog_Parts. We will place the pmos, nmos, vdd, gnd, vdc, vpulse andcap instances in the Schematic Window from the NCSU_Analog_Parts library asinstructed below.Note: pay special attention to the parameters specified in vdc, vpulse, and cap. These parameters are very important in simulation.Place pmos instance•In Component Browser, select P_Transistors and then pmos.•Place it in the Schematic WindowFigure 7 – Add pmos InstancePlace nmos instance•In Component Browser, select N_Transistors and then nmos.•Place it in the Schematic Window.Figure 8 – Add nmos InstancePlace gnd instance•In Component Browser, select Supply_Nets and then gnd.•Place it in the Schematic Window.Figure 9 – Add gnd Instance Place vdd instance•In Component Browser, select Supply_Nets and then vdd •Place it in the Schematic Window.Figure 10 – Add vdd InstancePlace IN pin•From the Schematic Window menu, select Add -> Pin...•In the Pin Name field , enter IN•In the Direction field, select input•Place it in the Schematic WindowFigure 11 – Add Input PinPlace OUT pin•From the Schematic Window menu, select Add -> Pin...•In the Pin Name field , enter OUT•In the Direction field, select output•Place it in the Schematic WindowFigure 12 – Add Output PinPlace vdc instance•In the Component Browser, select Voltage Sources and then vdc •In the DC voltage field, enter 5 V•Place it in the Schematic WindowFigure 13 – Add vdc SourcePlace vpulse instance•In the Component Browser, select Voltage_Sources and then vpulse •Enter the following values in the form:Figure 14 Edit Object vpulse SourcePlace cap instance•In Component Browser, select R_L_C and then cap•In the Capacitance field, enter OutCap F. (This Design Variable will be used in Artist.) •Place it in the Schematic WindowFigure 15 – Add cap InstancePlace wires•In the Schematic Window menu, select Add -> Wire (narrow)•Place wires to connect all the instances•Select Design -> Check and Save.Look at the CIW. You should see a message that says:Extracting “INV schematic”Schematic check completed with no errors.“EEE534 INV schematic” saved.If you do have some errors or warnings, the CIW will give a short explanation of what those errors are. Errors will also be marked on the schematic with a yellow or white box. Errors must be fixed for your circuit to simulate properly. When you find a warning it is up to you to decide if you shouldfix it or not. The most common warnings occur when there is a floating node or when there are wires that cross but are not connected. Just be sure that you know what effect each of these warning will have on your circuit when you simulate.Your schematic should look like the one shown below.Figure 16 – Completed SchematicIf you would like to learn more about the schematic editor, you can work through chapters 1-5 of the Composer Tutorial that comes with the Cadence documentation. Start the documentation browser by typingcdnshelp &at the command prompt. If you find that you cannot view the figures correctly in the web browser, you can click the View/Print PDF link at the top of the page to launch a PDF viewer for the tutorial. This documentation browser offers many more links for you to learn about the Cadence Design Framework.Simulate the Schematic with HSPICE within Virtuoso Analog Design EnvironmentSet up the Simulation EnvironmentYou are now prepared to simulate your circuit.From the Schematic Window menu, select Tools -> Analog Environment. A window will pop-up. This window is the Analog Design Environment Window.Figure 17 - Analog Design Environment WindowChoose a SimulatorFrom the Analog Design Environment menu, select Setup -> Simulator/Directory/Host. Enter the fields as shown below. Choose hspiceS as your simulator. Your simulation will run in the specified Project Directory. You may choose any valid pathname and filename that you like.Figure 18 Choosing Simulator/Directory/Host FormChoose AnalysisWe will setup to do a Transient Analysis on the circuit that we just produced.From the Analog Design Environment menu, select Analyses -> Choose... Fill out the form with the following values:Figure 19 – Choosing AnalysesAdd a VariableFrom the Analog Design Environment menu, select Variables -> Edit. The Editing Design Variables form will appear. Fill out the form as shown below, and then click Add to send this Variable to the Table of Design Variables.(Recall that we entered the OutCap Design Variable in the Capacitor component while editing the schematic in the previous section.)Figure 20 – Editing Design Variables FormSetup OutputWhen using Transient Analysis, the transient voltage will be saved automatically. We can save the current through capacitor C0 in the schematic by doing the following:From the Analog Design Environment menu, select Outputs -> To be Saved -> Select On Schematic In the Schematic Window, click on the lower terminal (not the wire) of capacitor C0.After you click on the terminal, the Analog Design Environment Window should look like this:Figure 21 Analog Design Environment WindownRun SimulationFrom the Analog Design Environment menu, select Simulation -> Run, Look at the echoing information in the CIW window. If the simulation succeeds, the window will display “...successful.”Figure 22 – CIW after simulationIf the simulation is unsuccessful, then one of the error messages should provide a clue as to what went wrong. Remember that you can move elements around in your schematic by clicking and dragging them. You can delete them by selecting them and pressing the “delete” key. You modify the properties of the elements by selecting them and pressing the “q” key.If you would like to learn more about the Analog Design Environment, select Analog Design Environment->Cadence Analog Design Environment User Guide in the cdnshelp browser window.View WaveformsFrom the Analog Design Environment menu, select Results -> Direct Plot -> Transient Signal. The Waveform Window will then pop up. In the Schematic Window, click on the IN wire and then Click on the OUT wire, then press ESC on your keyboard.The two curves (IN and OUT) will then be displayed in this window:Figure 23 – Waveform ViewerPress the Strip Chart Mode icon (4th icon from right) on the Waveform WindowThe waveforms will then be displayed separately as shown below:Figure 24 – Waveform Viewer, Strip Chart ModeIf you would like to learn more about the Waveform Viewer, select Analog Design Environment->Waveform User Guide in the cdnshelp browser window.Use CalculatorIn Analog Design Environment Window, go to Tools -> Calculator. The Calculator Window will then pop up, as shown below:Figure 25 – CalculatorIn Calculator Window, go to Options -> uncheck RPN. We are going to use the calculator to plot both the current through the capacitor and the absolute value of the capacitor current.In the Calculator Window, click on the tran tab then click the it radio button. In the Schematic Window, click on the lower terminal of the capacitor. Returning to the Calculator Window, the text area at the top should like this:Figure 26 – Calculator after selecting lower capacitor terminalIn the Calculator Window, press the plot icon to plot this waveform in the Waveform Window. In the Calculator Window, select the New Subwindow. In the Calculator Window, press the clear button to erase the text area, select abs, press the “(“ symbol and press the it radio button. In the Schematic Window, click on the lower terminal of the capacitor. Returning to the Calculator Window, press the “)” symbol, the text area at the top should like this:Figure 27 - Calculator after selecting lower capacitor terminalIn the Calculator Window, press the plot button to plot this waveform in the Waveform Window. Your Waveform Window should now look like this:Figure 28 – Waveform Display with current through the capacitor and the absolute value of thecapacitor current。

cadence 实验指导书

cadence 实验指导书哈尔滨理工大学开放性实验指导书Virtuoso Analog Design Environment中文实验手册Version 5.1.41哈尔滨理工大学开放性实验指导书实验一、熟悉Virtuoso Analog Design Environment............................................................. (2)实验二、SchematicEntry .................................................................. . (6)实验三、模拟仿真 ..................................................................... . (13)实验四、显示仿真结果 ..................................................................... .. (22)实验五、仿真结果分析 ..................................................................... .. (31)实验六、参数分析 ..................................................................... . (43)实验七、使用OCEAN 和SKILL语言(略) ................................................................. .......... 46 实验八、使用Corner分析工具 ..................................................................... . (47)实验九、Monte Carlo 分析 ..................................................................... . (50)实验十、优化分析 ..................................................................... . (59)实验十一、Component Description Format(CDF)参数 .......................................................... 64 实验十二、Macromodels、Subcircuits和InlineSubcircuits (67)实验十三、HierarchyEditor ................................................................. .. (73)实验十四、继承连接 ..................................................................... (77)哈尔滨理工大学开放性实验指导书Virtuoso Analog Design Environment 实验步骤:一、登录Linux操作系统,用安装软件的用户登录,最好不要用root用户。

基于Cadence的电路版图绘制及验证PPT文档30页

16、自己选择的路、跪着也要把它走 完。 17、一般情况下)不想三年以后的事, 只想现 在的事 。现在 有成就 ,以后 才能更 辉煌。

18、敢于向黑暗宣战的人,心里必须 充满光 明。 19、学习的关键--重复。

20、懦弱的人只会裹足不前,莽撞的 人只能 引为烧 身,只 有真正 勇敢的 人才能 所向披 靡。

谢谢你的阅读

❖ 知识就是财富 ❖ 丰富你的人生

71、既然我已经踏上这条道路,那么,任何东西都不应妨碍我沿着这条路走下去。——康德 72、家庭成为快乐的种子在外也不致成为障碍物但在旅行之际却是夜间的伴侣。——西塞罗 73、坚持意志伟大的事业需要始终不渝的精神。——伏尔泰 74、路漫漫其修道远ห้องสมุดไป่ตู้吾将上下而求索。——屈原 75、内外相应,言行相称。——韩非

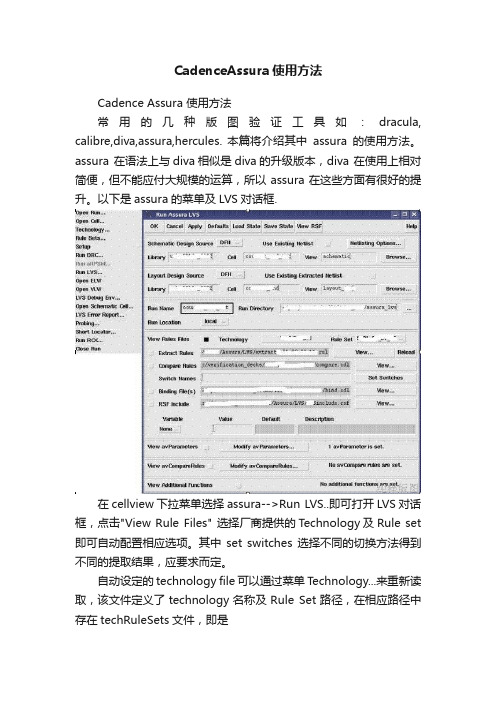

CadenceAssura使用方法

CadenceAssura使用方法Cadence Assura 使用方法常用的几种版图验证工具如:dracula, calibre,diva,assura,hercules. 本篇将介绍其中assura的使用方法。

assura 在语法上与diva相似是diva的升级版本,diva 在使用上相对简便,但不能应付大规模的运算,所以assura在这些方面有很好的提升。

以下是assura的菜单及LVS对话框.在cellview下拉菜单选择assura-->Run LVS..即可打开LVS对话框,点击"View Rule Files" 选择厂商提供的Technology及Rule set 即可自动配置相应选项。

其中set switches选择不同的切换方法得到不同的提取结果,应要求而定。

自动设定的technology file可以通过菜单Technology...来重新读取,该文件定义了technology名称及Rule Set路径,在相应路径中存在techRuleSets文件,即是具体文件设定。

extract rules是主体提取程序. compare rules说明版图电路器件对比.Binding files 说明相应的器件. RSF files设定及本地设定.DFII方式是版图及电路cellview直接对比,也可选择netlisting 使用netlist进行比对。

其中注意将Netlisting Options..中auLVS修改为auCdl即可。

LVS运行完成后会自动跳出debug窗口及其他窗口,如果没有自动跳出可以用菜单来打开,当然要注意是直接打开cellview,如果以Edit in place可能无法打开这些窗口。

此外,assura也不支持相同cell name不同view name的调用。

多余的avParame ter打开也可能引起对比的错误。

因为assura 采用hierarchy 检查方式,所以邻近cell的层的重叠可能引起比对错误。

Cadence实验教程

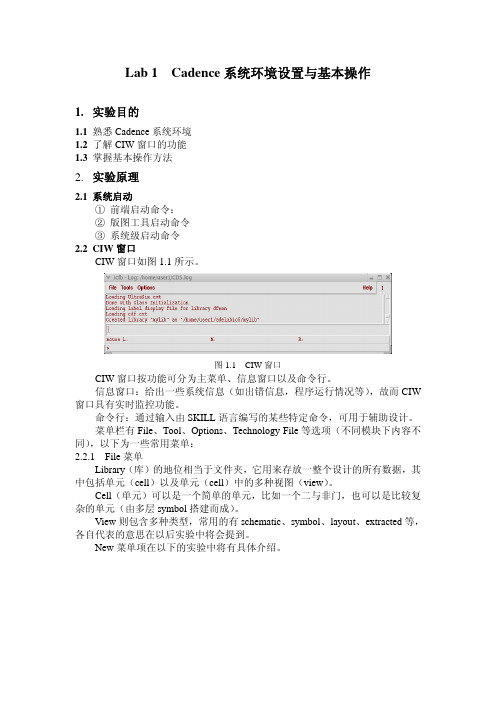

Lab 1 Cadence系统环境设置与基本操作1.实验目的1.1熟悉Cadence系统环境1.2了解CIW窗口的功能1.3掌握基本操作方法2.实验原理2.1系统启动① 前端启动命令:② 版图工具启动命令③ 系统级启动命令2.2CIW窗口CIW窗口如图1.1所示。

图1.1 CIW窗口CIW窗口按功能可分为主菜单、信息窗口以及命令行。

信息窗口:给出一些系统信息(如出错信息,程序运行情况等),故而CIW 窗口具有实时监控功能。

命令行:通过输入由SKILL语言编写的某些特定命令,可用于辅助设计。

菜单栏有File、Tool、Options、Technology File等选项(不同模块下内容不同),以下为一些常用菜单:2.2.1File菜单Library(库)的地位相当于文件夹,它用来存放一整个设计的所有数据,其中包括单元(cell)以及单元(cell)中的多种视图(view)。

Cell(单元)可以是一个简单的单元,比如一个二与非门,也可以是比较复杂的单元(由多层symbol搭建而成)。

View则包含多种类型,常用的有schematic、symbol、layout、extracted等,各自代表的意思在以后实验中将会提到。

New菜单项在以下的实验中将有具体介绍。

图1.2 New Library窗口图1.3 Create New File Library窗口分为Library和Technology File两部分。

Library部分有Name和Directory两项,分别对应要建立的Library名称和路径,Library名称可以自定义。

一般Technology部分选择Don’t need a techfile选项。

如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的工艺文件)或Attach to an existing techfile(使用原有的工艺文件)。

cadence讲义版图设计验证

绘制反相器版图

Stage 5:

contact

绘制反相器版图

Stage 6:

Metal 1

绘制反相器版图

Stage 7:

via

绘制反相器版图

Stage 8:

Metal 2

绘制反相器版图

版图编辑工具使用

OK!!!

器件加工工艺流程

绘制反相器版图

1

绘制反相器版图

2

绘制反相器版图

3

绘制反相器版图

版图验证工具-Diva 版图验证工具-Dracula

设计流程

版图验证

版图验证的必要性?

确保版图绘制满足设计规则 确保版图与实际电路图一致 确保版图没有违反电气规则 可供参数提取以便进行后模拟

版图验证

❖IC 后端流程图:

Cadence 版图验证工具

Diva

Diva 是 Cadence 的版图编辑大师Virtuoso集成 的交互式版图验证工具,具有使用方便、操作 快捷的特点,非常适合中小规模单元的版图验 证。

版图验证工具-DIVA

Diva 工具集组成:

1.设计规则检查(iDRC) 2.版图寄生参数提取(iLPE) 3.寄生电阻提取(iPRE) 4.电气规则检查(iERC) 5.版图与电路图一致比较(iLVS)

版图验证工具-DIVA

❖ Remark:

1. Diva中各个组件之间是互相联系的,有时候 一个组件的执行要依赖另一个组件先执行。 例如:要执行LVS就先要执行DRC。

6 显示文件(display.drf)

系统启动

❖ 系统启动 1 前端启动命令

命令

规模

icde

s

icds

s

icms

IC设计虚拟仿真实验项目

IC设计虚拟仿真实验项目课程介绍与课件本实验项目切实贯彻“加强基础,强化应用,提高素质,注重创新,激励个性,体现特色”的人才培养思路,努力强化学生IC设计的实践能力的培养。

本实验项目的教学内容包括ASIC设计的基础,注重使学生理解ASIC设计的基本流程与关键技术,重点在于通过具体的UART控制器芯片的设计,介绍ASIC设计流程中最主要的几种专业EDA软件的使用,包括逻辑仿真、逻辑综合、静态时序分析、版图综合与验证、测试向量生成与故障模拟、形式验证等。

实验教学中主要包括课内和课外两种教学。

一是课内实验教学指导,通过老师随堂演示、指导及相配套的实验报告的完成使学生能够基本掌握ASIC设计中不同EDA软件的功能与使用;二是开放的网络教学,注重特色人才培养,使对实验内容有兴趣的学生有条件进行深入的、综合性的实验培训,配备专门老师进行在线或离线指导。

本实验项目及实验环境对本校学生开放,接收国内高校及信息学科研究机构业务技术人员进修访问。

实验项目的虚拟资源放置在专用服务器上,不仅对相关专业学生开放,而且对社会各个单位和个人开放,实验项目的所有资源均可以上网对公众开发,课件、实践指南等都可以通过互联网自由下载。

利用虚拟技术构建交互式的实验教学与管理信息平台,建立自觉式、协作式的“学习共同体”的虚拟仿真实验教学模型,可以是校内、校外个人或者单位注册账号,登陆本实验平台网站,浏览,并进行实际操作,最大化资源利用效果。

本实验教学对学生的评价主要包括四个方面:课程实验的出勤率、平时实验过程(实验报告)的完成情况、上机操作考核情况及学生在课堂之外的实验情况。

对实验指导老师的评价主要包括三个方面,包括对实验内容的设计与更新、实验的过程管理及在线指导情况。

通过这些客观的评测,强化提高学生学生进行ASIC。

Cadence版图设计

第 6 页 共 97 页

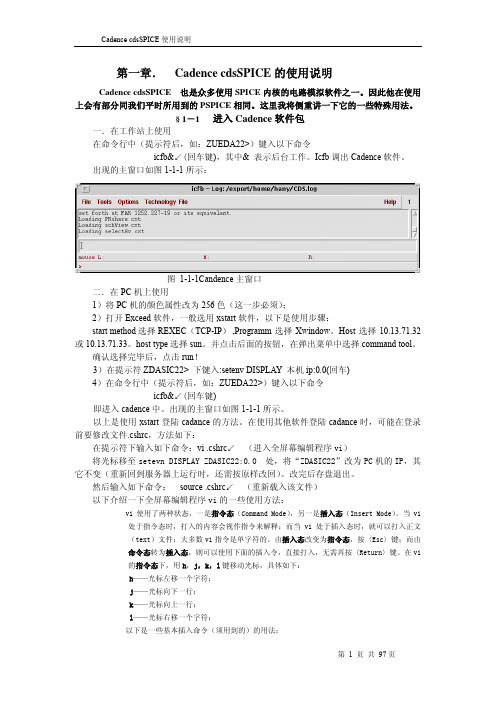

Cadence cdsSPICE 使用说明

图 1-4-2 Save State 窗口 参数。如图 1-4-2 所示。窗口中的两项分别为状态名和选择需保存的内容。 Load State 打开相应的窗口,加载已经保存的状态。 Reset 重置 analog artist。相当于重新打开一个模拟窗口。 二.Setup 菜单 包括 Design、Simulator/directory/host、Temperature、Model Path 等菜单项: Design 项选择所要模拟的线路图。 Simulator/directory/host 项选择模拟使用的模型,系统提供的选项有 cdsSpice、hspiceS、 spectreS 等等。我们一般用到的是 cdsSpice 和 spectreS。其中采用 spectreS 进行的模拟更加 精确。下面我们只以这两种工具为例说明。 Temperature 打开如图 1-4-3 的窗口,可以设置模拟时的温度。

icfb&↙(回车键) 即进入 cadence 中。出现的主窗口如图 1-1-1 所示。 以上是使用 xstart 登陆 cadance 的方法。在使用其他软件登陆 cadance 时,可能在登录 前要修改文件.cshrc,方法如下: 在提示符下输入如下命令:vi .cshrc↙ (进入全屏幕编辑程序 vi) 将光标移至 setevn DISPLAY ZDASIC22:0.0 处,将“ZDASIC22”改为 PC 机的 IP,其 它不变(重新回到服务器上运行时,还需按原样改回)。改完后存盘退出。 然后输入如下命令: source .cshrc↙ (重新载入该文件) 以下介绍一下全屏幕编辑程序 vi 的一些使用方法:

cadence实验报告文档

2020 cadence实验报告文档Contract Templatecadence实验报告文档前言语料:温馨提醒,报告一般是指适用于下级向上级机关汇报工作,反映情况,答复上级机关的询问。

按性质的不同,报告可划分为:综合报告和专题报告;按行文的直接目的不同,可将报告划分为:呈报性报告和呈转性报告。

体会指的是接触一件事、一篇文章、或者其他什么东西之后,对你接触的事物产生的一些内心的想法和自己的理解本文内容如下:【下载该文档后使用Word打开】篇一:CadencePSpice实例(实验报告)6PSpiceSimulationExperience620xx0xx21236张双林Workrequirement:pleasereadtheexerciseofpage117fromthespicebook,butsimulat ethedevicemodelparametersandoperationalpointat30degreeand100degree.PleaseRuntheTEMPanalysiswithPspiceandanswerthequestionoft heexercisePleasehandoutae-reportaboutyourworkI.Net-listsandcircuitfigure:Andthenet-listfilegoes:EX3DCAnalysysexapal1.2.MODELMELQNPNBF=100IS=1E-16Q1210MELQRB31200KRC321KVCC30DC5.temp30100.OP.ENDII.Simulationresult:Accordingtotheoutputfile,wecandrawatabletocontrastthediff erence:a.b.III.Conclusion:Withaninspectionofthecircuitparametersindifferenttemperat ures,wecanfindthatthevalueofISchangeslargely,about1000tim es,andGM,about16percent,whileabout500mvdecreasingonVCEcau sed.SothebehaviorofTransistorscanbeaffectedbytemperatures largely.篇二:Cadence报告Cadence2-10进制加减计数器设计报告一、实验目的:1、掌握2-10进制加减CMOS计数器的逻辑设计;2、了解和掌握使用Cadence进行集成电路的设计过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

The RSF contains an rcxParameters section if the RSF is for an RCX run.

rcxParameters( ?runName"peakDetect" ?extract"cap" ?minR0.001 ?maxFractureLength"infinite" ?fractureLengthUnits"microns" ?capExtractMode"decoupled" ?capGround"vss!" ?capCouplingFactor1.0 ?type"full" ?netNameSpace"layout" ?outputFormat"spice" ?output"peakDetect.sp" ?groundNets ("vss!" "gnd!") ?powerNets ("vdd!") ?tempdir "/tmp" ?parasiticResModels "comment"

RCX Graphical User Interface Run Guide

Demonstration

The Assura verification suite is optimized for large, hierarchical, repetitive designs such as memory, microprocessor, and mixed-signal circuits. The software upholds the Cadence verification tradition of accuracy established by its Dracula® and Diva® products. The Assura tools ensure accuracy and leverage the layout hierarchy of leading-edge designs to provide faster physical verification runtimes.

The Assura RSF must end with one or more Assura tool invocation commands that launch the appropriate verification tasks. When an Assura tool is run from the GUI, the appropriate invocation command is placed at the end of the RSF. If you create your own RSF, you can nest parameter sections within the invocation command to specify parameters that apply to that command only.

• • • • Assura Physical Verification Tool Suite Assura Task and Data Flow Assura Input Files Running Assura

DRC Graphical User Interface Run Guide LVS Graphical User Interface Run Guide

The Assura RSF consists of several sections: • A mandatory avParameters section • One or more avCompareRules sections for an LVS run • An rcxParameters section for an RCX run • Optional statements outside the above sections • One or more mandatory Assura tool invocation commands

Cadence 后端实验系列19_版图ቤተ መጻሕፍቲ ባይዱ证_ Assura

Introduction to Assura Physical Verification

• • • • Assura Physical Verification Tool Suite Assura Task and Data Flow Assura Input Files Running Assura

avParameters( ?workingDirectory "/usr1/drc/“ ?runName "peakDetect" ?inputLayout ( "df2" "design" ) ?cellName "peakDetect" ?technology “gold“ ?techLib "/usr1/amancuso/rcx/assura_tech.lib“ )

The Assura RSF contains a mandatory avParameters section that specifies the input layout and rules file associated with the Assura run, plus various global RSF options. Below is an example of an avParameters section.

Schematic Netlists

Layout Geometry Data

RunSpecific File (RSF)

Rule File

• The Assura RSF is a required control file in text format that directs the Assura DRC, LVS, or RCX run. It specifies input data files, rule files, run-specific options, and commands to invoke the tool. The Assura RSF follows Cadence SKILL language syntax. Options in an RSF are specified as parameters, which begin with a “?” followed by a keyword.

• When you use the Assura Graphical User Interface (GUI), the GUI creates the RSF for you using the settings you specified in the forms, and invokes an Assura tool using this RSF. • Alternatively you can create your own RSF. You can specify the RSF file name in the GUI run form, or you can specify the RSF file name on the command line if you run an Assura tool in batch mode.

DRC Graphical User Interface Run Guide LVS Graphical User Interface Run Guide RCX Graphical User Interface Run Guide Demonstration

Introduction to Assura Physical Verification

?subNodeChar "#" ?outputNetNameSpace "schematic" ?parasiticCapModels "yes" ?capModels "no" ?hierarchyDelimiter "/" ?resModels "no" )

You can place optional statements in the RSF outside an avParameters, avCompareRules or rcxParameters section. These statements include several Assura rules that can optionally be placed in an RSF, usersupplied SKILL functions, and Assura tool invocation commands.

Assura DRC – Assura DRC (Design Rule Checking) checks the layout against geometric spacing, width, and other rules. Typical checks include material spacing, enclosure, coverage, and overlap. Assura DRC displays design rule violations graphically as an additional graphics layer on the layout, and lists them in text files. Assura LVS – Assura LVS (Layout Versus Schematic) comparison extracts devices and connectivity from the layout according to device extraction rules, then creates a layout netlist according to netlist rules, then finally compares the layout netlist to the schematic netlist according to comparison rules. Assura LVS displays mismatches between the layout and the schematic both textually and graphically. Assura RCX – Assura RCX (Resistance, Capacitance and Inductance Extraction) extracts parasitic resistance, capacitance, and inductance from the layout for analysis and input to post-layout simulators.