SoC设计第10章

高级片上系统设计知到章节答案智慧树2023年上海电力大学

高级片上系统设计知到章节测试答案智慧树2023年最新上海电力大学第一章测试1.SoC是一种单硅芯片,可用于实现整个系统的功能参考答案:对2.SoC的缺点有哪些?参考答案:复杂的设计过程3.以下哪项陈述不正确?参考答案:SoC通常用于基本嵌入式应用,而MCU 用于智能手机等复杂应用;MCU 能够运行多个操作系统,而 SoC 通常不具有此功能4.在 SoC 设计过程中,包含以下哪些阶段?参考答案:软件模拟;布线;综合5.SoC 的基本组件包含哪些参考答案:系统总线;CPU;系统外设和协处理器第二章测试1.ZYNQ-7000系列FPGA通常采用Vivado软件进行电路设计参考答案:对2.PS的全称是Processing System参考答案:对3.本次实验不仅使用了ZYNQ-7000中的PS部分,还使用了PL部分参考答案:错4.本次实验中用到的PS部分的组件包括哪些参考答案:DDR3控制器;UART;ARM Cortex A9 核5.xc7z010clg400-1中的400表示什么意思参考答案:芯片封装的400个对外引脚第三章测试1.以下哪些是系统总线的功能?参考答案:将 ALU 单元连接到寄存器;控制处理器和内存块之间的数据传输;为控制信号提供临时缓冲器2.SoC 的以下哪些特性通常受其总线设计的影响?参考答案:功耗;可靠性;性能3.以下哪些 AMBA 总线系列用于与外围设备的通信?参考答案:APB4.AMBA 是芯片总线标准架构中应用最广泛的技术之一参考答案:对5.AXI4-Lite 是 AXI4 接口的轻量级变体,其数据位宽度限制为 16 位参考答案:错第四章测试1.IP在Vivado中指具有知识产权的具有一定电路功能的设计模块参考答案:对2.GPIO的全称是:General Processing I/O.参考答案:错3.32b GP AXI Master Ports是将PS部分模块作为master参考答案:对4.本次实验中用到的时钟是哪个部分提供的参考答案:PS5.本次实验需要生成Bitstream的原因是什么参考答案:因为用到了PL部分的FPGA第五章测试1.片上内存过小,会导致SoC的性能降低。

微电子技术与计算机技术的发展历史是一个不断创新的过...

第1章绪论1.1 概述微电子技术与计算机技术的发展历史是一个不断创新的过程,这种创新包括原始创新、技术创新和应用创新等。

每一项创新都能开拓出一个新的领域,带来新的巨大的市场,对我们的生产、生活方式产生重大的影响。

自集成电路发明以后,集成电路芯片的发展基本上遵循了Intel公司创始人之一的Gordon EMoore 1965年预言的摩尔定律,即每隔3年集成度增加4倍,特征尺寸缩小1.4倍。

在集成电路(IC)发展初期,电路设计都是从器件的物理版图设计入手。

后来出现了集成电路单元库(Cell-Lib),使得集成电路设计从器件级进入逻辑级,极大地推动了IC产业的发展。

不过,集成电路只有安装在整机系统中才能发挥它的作用。

IC芯片是通过印刷电路板(PCB)等技术实现整机系统的。

尽管IC的速度可以很高,功耗可以很小,但由于PCB板中IC芯片之间的连线延时、PCB板可靠性及重量等因素的限制,整机系统的性能受到了很大的限制。

随着系统向高速度、低功耗、低电压和多媒体、网络化、移动化的发展,系统对电路的要求越来越高。

传统集成电路设计技术已无法满足性能日益提高的整机系统的要求。

同时,由于IC设计与工艺技术水平提高,集成电路规模越来越大,复杂程度越来越高,整个系统已可以集成在一个芯片上。

目前已经可以在一个芯片上集成108~109个晶体管。

SOC(System on Chip:片上系统)就是在这种条件下应运而生的。

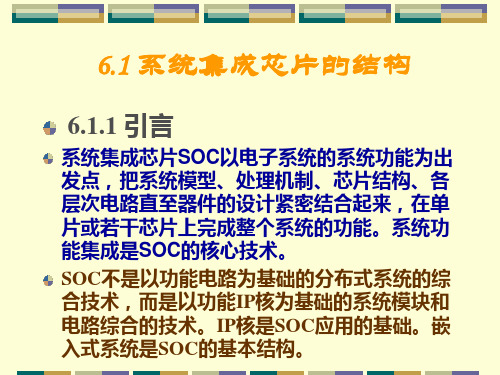

SOC从整个系统的角度出发,把处理机制、模型算法、芯片结构、各层次电路,直至器件的设计紧密结合起来,在单个(或少数几个)芯片上完成整个系统的功能。

SOC的设计以IP核为基础,以分层次的硬件描述语言为系统功能和结构的主要描述手段,借助于以计算机为平台的EDA工具进行。

研究表明,与IC组成的系统相比,由于SOC设计能够综合并全盘考虑整个系统的各种情况,因而可以在同样的工艺技术条件下,实现更高性能的系统指标。

SOC技术,也大大促进了软硬件协同设计及计算机系统设计自动化的发展。

同济大学 软件学院 嵌入式系统导论复习提纲

n 北桥芯片:主导作用,也称为主桥,负责与 CPU 的联系并控制内存、AGP、PCI 数据在北内部传输。确定 CPU 的类型、主板的系统总线频率,内存类型、容量 和性能,显卡插槽规格。

n 南桥芯片:负责外部设备的数据处理与传输,确定扩展槽的种类与数量、扩展接 口的类型和数量等。

4. ARM 处理器体系架构 ,简单了解之。(课件) 5. 了解 ARM7TDMI 处理器特点,工作模式等。

三个阶段:取指、译码、执行 三级流水 两种工作状态:ARM(32bit),Thumb(16bit)

工作模式:

除了用户模式外其他全都是特权模式。特权模式可以访问硬件、寄存器等,并可以在模式 间切换,用户模式不可以。 后五种模式是异常模式,可由程序切入,也可由特定异常切入。每个模式有独立存储器。 用户模式和系统模式公用寄存器

p UEFI 优点

n 提供了一个连接操作系统载入程序与固件之间稳定的接口; n 为独立软件开发商和制造商提供了一个清晰的预启动编程环境; n 延长了传统硬件的使用寿命; n 启动速度快 p 不足之处

UEFI 在安全问题并没有作出改善

第四章:嵌入式系统硬件设计 1. 图示嵌入式系统体系结构。简单介绍每部分。

2. 优势 p 降低耗电量 p 减少体积 p 丰富系统功能 p 提高速度 p 节省成本

3. 构成 IP 是构成的基本单元

4. IP 核以及分类 IP 核具备比较复杂的功能,且经过验证。设计资料内不仅仅包含一些物理功能和

技术特性,更重要的是包含了设计者的创造性思维,具有很强的知识内涵。这些资料被 称为具有知识产权的内核(Intellectual Property Core),简称 IP 核。

第章sopc技术概述

Nios II /f (快速)

Nios II /s (标准) Nios II /e (经济)

针对最佳性能优化 平衡性能和尺寸 针对逻辑资源占用优化

6级 1 周期 动态 可设置 可设置

5级 3 周期 静态 可设置 无

无 软件仿真实现 无 无 无

256

256

256

1.3 Nios II软核简介

❖ 外设的可定制性

Altera公司NIOS和NIOS II Xilinx的MicroBlaze

1.3 Nios II软核简介

❖ Nios II是Altera公司2004年6月推出的第二代软核处理器。 ❖ 相对于Nios,Nios II 性能更高,占用FPGA的资源更少,

而与之配套的开发环境更先进,有更多的资源可供用户使用。 ❖ Nios II系列32位RISC嵌入式处理器具有超过200 DMIP的性

1.2 基本概念

❖ 软核

IP软核通常是用HDL文本形式提交给用户,它经过 RTL级设计优化和功能验证,但其中不含有任何具 体的物理信息。据此,用户可以综合出正确的门电 路级设计网表,并可以进行后续的结构设计,具有 很大的灵活性,借助于EDA综合工具可以很容易地 与其他外部逻辑电路合成一体,根据各种不同半导 体工艺,设计成具有不同性能的器件。软IP内核也 称为虚拟组件(VC-Virtual Component)。

1.3 Nios II软核简介

定时器/计数器 用户逻辑接口 外部SRAM接口

SDR SDRAM

PCI DDR2 SDRAM

SHA-1

外部三态桥接 EPCS串行闪存控制 器

JTAG UARTC S8900 10Base-T接口

片内ROM

直接存储器通道 (DMA)

拉扎维模拟CMOS集成电路设计 前十章全部课件

重邮光电工程学院

同一衬底上的NMOS和PMOS器件

MOS管所有pn结必须反偏: *N-SUB接VDD! *P-SUB接VSS! *阱中MOSFET衬底常接源极S

重邮光电工程学院

MOS器件符号

MOS管等效于一个开关!

重邮光电工程学院

MOS器件的阈值电压VTN(P)

(a)栅压控制的MOSFET (c)反型的开始

nCox

W L

[(VGS

VTH)VDS

)v(x) 1 2

1 VDS2 2

v(x)

]

2

)]vDS 0

重邮光电工程学院

I/V特性的推导(4)

ID

nCox

W L

[(VGS

VTH)VDS

1 VDS2 ] 2

三极管区(线性区)

每条曲线在VDS=VGS-VTH时

取最大值,且大小为:

ID nCox W (VGS VTH )2

。

t ≈ 50A, C

ox

ox

t ≈ 0.02 m, C

ox ox

6.9 fF/ m 2 1.75fF/ m 2

t ≈ 0.1 m, C 0.35fF/ m 2

ox

ox

重邮光电工程学院

MOS器件电容

模拟集成电路设计绪论 Ch.1# 45

重邮光电工程学院

减小MOS器件电容的版图结构

对于图a:CDB=CSB = WECj + 2(W+E)Cjsw 对于图b: CDB=(W/2)ECj+2((W/2)+E)Cjsw CSB=2((W/2)ECj+2((W/2)+E)Cjsw= = WECj +2(W+2E)Cjsw

soc课程设计

soc课程设计一、课程目标知识目标:1. 学生能够理解并掌握soc(社会学科)基本概念,如社会结构、文化差异和社会制度等;2. 学生能够描述并分析我国及世界各地的社会现象,了解不同文化背景下的社会行为规范;3. 学生能够运用所学知识,对现实生活中的社会问题进行思考,提出合理的观点和建议。

技能目标:1. 学生通过小组合作、讨论等方式,提高沟通协作能力;2. 学生能够运用批判性思维,对社会现象进行分析和评价;3. 学生掌握基本的社会调查方法,能够独立完成简单的调查报告。

情感态度价值观目标:1. 培养学生对社会学科的兴趣,激发学习热情;2. 增强学生的社会责任感和公民意识,使其关注社会问题,积极参与社会公益活动;3. 培养学生的包容性和尊重多元文化的态度,使其形成正确的价值观。

本课程针对年级特点,结合学科性质,注重培养学生的实践能力和综合素质。

课程目标具体、可衡量,旨在帮助学生掌握基础知识,提高分析问题和解决问题的能力,同时培养其情感态度价值观,使其成为具有社会责任感和创新精神的优秀学子。

二、教学内容1. 社会结构:介绍社会阶层、家庭、社会组织等基本概念,分析其功能和作用。

教材章节:第一章《社会学的基本概念》内容列举:社会阶层的形成与功能;家庭结构与功能;社会组织类型及作用。

2. 文化差异:探讨世界各地的文化现象,分析文化差异的原因及其影响。

教材章节:第二章《文化人类学》内容列举:文化概念及其分类;文化差异的表现与原因;跨文化交流的意义与挑战。

3. 社会制度:讲解社会制度的基本类型,分析其对个体和社会的影响。

教材章节:第三章《社会制度》内容列举:社会制度的定义与功能;现代社会制度类型及运作机制;社会制度的变革与影响。

4. 社会问题:探讨现实生活中的社会问题,分析其原因、影响及解决办法。

教材章节:第四章《社会问题》内容列举:社会问题的概念与分类;我国当前的主要社会问题;解决社会问题的策略与方法。

5. 社会调查方法:介绍社会调查的基本方法,培养学生实际操作能力。

SoC 简介

第1 章SoC 简介近10 年来,无论是消费类产品如电视、录像机,还是通信类产品如电话、网络设备,这些产品的核心部分都开始采用芯片作为它们的“功能中枢”,这一切都是以嵌入式系统技术得到飞速发展作为基础的。

SoC (System on Chip,片上系统) 是ASIC(Application Specific Integrated Circuits) 设计方法学中的新技术,是指以嵌入式系统为核心,以IP 复用技术为基础,集软、硬件于一体,并追求产品系统最大包容的集成芯片。

狭意些理解,可以将它翻译为“系统集成芯片”,指在一个芯片上实现信号采集、转换、存储、处理和I/O 等功能,包含嵌入软件及整个系统的全部内容;广义些理解,可以将它翻译为“系统芯片集成”,指一种芯片设计技术,可以实现从确定系统功能开始,到软硬件划分,并完成设计的整个过程。

1.1 SoC1.1.1 SoC 概述SoC 最早出现在20 世纪90 年代中期,1994 年MOTOROLA 公司发布的Flex CoreTM 系统,用来制作基于68000TM 和Power PCTM 的定制微处理器。

1995 年,LSILogic 公司为SONY 公司设计的SoC,可能是基于IP ( Intellectual Property)核进行SoC 设计的最早报道。

由于SoC 可以利用已有的设计,显著地提高设计效率,因此发展非常迅速。

SoC 是市场和技术共同推动的结果。

从市场层面上看,人们对集成系统的需求也在提高。

计算机、通信、消费类电子产品及军事等领域都需要集成电路。

例如,在军舰、战车、飞机、导弹和航天器中集成电路的成本分别占到总成本SOC 设计初级培训(Altera篇)2的22%、24%、33%、45%和66%。

随着通讯行业的迅猛发展和信息家电的迅速普及,迫使集成电路产商不断发展IC 新品种,扩大IC 规模,增强IC 性能,提高IC 的上市时间(Time to maeket) ,同时还需要实现品种的通用性和标准化,以利于批量生产,降低成本。

SoC设计方法与实现 第11章-低功耗设计 课件PPT

使用多种功耗状态的存储器管理。

低功耗SoC设计技术的综合考虑

低功耗技术对功耗与设计复杂度的影响

低功耗技术 漏电功耗的减小 静态功耗的减小 时序影响

面积优化

10%

10%

0%

多阙值工艺

CMOS工艺的发展与功耗的变化

各层次低功耗设计的效果

低功耗反馈的前向设计方法

SoC设计方法与实现

第十一章

低功耗

设计(2)

低功耗技术

内容大纲

减少静态功耗的技术 减少动态功耗的技术

减少静态功耗的技术

多阈值设计(Multi-Vt Design) 电源门控(Power Gating) 体偏置(Body Bias)

80%

0%

0%

时钟门控

0

20%

0%

多电压

50%

40%~50%

0%

电源门控

动态电压及动 态频率缩放

体偏置

90%~98% 50%~70%

90%

~0% 40%~70%

-

4%~8% 0% 10%

面积影响 -10% 2% 2% <10%

5%~15% <10% <10%

设计方法影响 无 低 低 中 中 高 高

验证复杂度影响 低 低 低 中 高 高 高

多阈值工艺

MOS管的阈值电压越小,速度越快,但漏电越大。

MOS管的阈值电压(Vt)与漏电流的关系

多阈值的设计流程

一种使用多阈值的设计流程

电源门控方法

用逻辑门电路控制模块电压的打开或关闭

电源门控方法

体偏置

微处理器系统结构与嵌入式系统设计答案

“微处理器系统结构与嵌入式系统设计”第一章习题解答1.2 以集成电路级别而言,计算机系统的三个主要组成部分是什么?中央处理器、存储器芯片、总线接口芯片1.3 阐述摩尔定律。

每18个月,芯片的晶体管密度提高一倍,运算性能提高一倍,而价格下降一半。

1.5 什么是SoC?什么是IP核,它有哪几种实现形式?SoC:系统级芯片、片上系统、系统芯片、系统集成芯片或系统芯片集等,从应用开发角度出发,其主要含义是指单芯片上集成微电子应用产品所需的所有功能系统。

IP核:满足特定的规范和要求,并且能够在设计中反复进行复用的功能模块。

它有软核、硬核和固核三种实现形式。

1.8 什么是嵌入式系统?嵌入式系统的主要特点有哪些?概念:以应用为中心,以计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积和功耗的严格要求的专用计算机系统,即“嵌入到应用对象体系中的专用计算机系统”。

特点:1、嵌入式系统通常是面向特定应用的。

2、嵌入式系统式将先进的计算机技术、半导体技术和电子技术与各个行业的具体应用相结合的产物。

3、嵌入式系统的硬件和软件都必须高效率地设计,量体裁衣、去除冗余,力争在同样的硅片面积上实现更高的性能。

4、嵌入式处理器的应用软件是实现嵌入式系统功能的关键,对嵌入式处理器系统软件和应用软件的要求也和通用计算机有以下不同点。

①软件要求固体化,大多数嵌入式系统的软件固化在只读存储器中;②要求高质量、高可靠性的软件代码;③许多应用中要求系统软件具有实时处理能力。

5、嵌入式系统和具体应用有机的结合在一起,它的升级换代也是和具体产品同步进行的,因此嵌入式系统产品一旦进入市场,就具有较长的生命周期。

6、嵌入式系统本身不具备自开发能力,设计完成以后用户通常也不能对其中的程序功能进行修改,必须有一套开发工具和环境才能进行开发。

第二章习题答案2.2 完成下列逻辑运算(1)101+1.01 = 110.01(2)1010.001-10.1 = 111.101(3)-1011.0110 1-1.1001 = -1100.1111 1(4)10.1101-1.1001 = 1.01(5)110011/11 = 10001(6)(-101.01)/(-0.1) = 1010.12.3 完成下列逻辑运算(1)1011 0101∨1111 0000 = 1111 0101(2)1101 0001∧1010 1011 = 1000 0001(3)1010 1011⊕0001 1100 = 1011 01112.4 选择题(1)下列无符号数中最小的数是( A )。

第十章 Hub, Host Downstream Port, and Device(10.6~10.12)

Enabled U0,U2 PM timer disable U1_Enable=0 U2_Enable=1

Enabled U0,U1,U2 PM timer disable U1_Enable=1 U2_Enable=1

U1 PM timer resets

Attempt U0-U2 Transition

U2

U2

4

© 2010 Renesas Electronics Corporation. All rights reserved.

Hub Header Packet Forwarder and Data Repeater

综述 Hub对Header Packet使用存储和发送模型,对Data使用repeater模型,来 实现以下功能 DS方向

Link states in U1 or lower

SetFeature

ClearFeature

Enabled U0

(U1_ENABLE) ClearFeature (U1_ENABLE)

ClearFeature

(U2_ENABLE)

(U2_ENABLE) SetFeature

(U2_ENABLE)

3

© 2010 Renesas Electronics Corporation. All rights reserved.

Hub Upstream Port Power Management

SetFeature

Enabled U0 only PM timer disable U1_Enable=0 U2_Enable=0

DS Port Rx

DS Port Rx状态描述 Rx Default DS port接收器处于处理接收的symbol,并查找 DPPSTART/HPSTART/LCSTART ordered set以开始packet或link command接收的活跃状态。 Rx Header DS port接收器处于处理接收的symbol,并查找DPPEND/DPPABORT ordered set的活跃状态。 Rx Header DS port接收器处于处理接收的symbol直到收到最后一个Header Packet symbol的活跃状态。 Rx Link Command DS port接收器处于处理接收的symbol并查找link command结束的活跃状 态。

第十章氨基羟基的保护与脱保护

MeO OMe NH COOMe

S ynth. C om m un.; 1989, 3139-3142.

BocHN

S iO 2, h e atin g TB S O Tf, Lutidine

H 2N

G

N

Z nB r2 , C H 2C l2

G N

R

ZnB r2, R S H , C H 2C l2

R

O

S

Cbz-Cl

O

NH2.HCl

K2CO 3

98%

O S

O NHCbz

Org. Syn., 70, 29

1.1.2 苄氧羰基的脱去 苄氧羰基的脱去主要有以下几种方法

1). 催化氢解 2). 酸解裂解(HBr, TMSI) 3). Na/NH3(液)还原 实验室常用简洁的方法是催化氢解(用H2或其它供氢体,一般常温常压氢化即可); 当分子中存在 对催化氢解敏感(有苄醚,氯溴碘等)或钝化催化剂的基团(硫醚等)时,我们就需要采用化学方法 如酸解裂解HBr或Na/NH3(液)还原等。

OTBS O

H2N

1.3.2 笏甲氧羰基的引入示例

Fmoc-Cl

sat. NaHCO3 CH2Cl2 79%

OTBS O

HN Fmoc

T etr ahedron: Asymmetr y, 2003, 12, 1645

O OH Boc

N

H2N

O

O O ON

OO

NaHCO3, DMF (Fmoc-OSu) 78%

H2/10%Pd-C

(Boc)2O 54%

BocHN ON H WO2004092166

H

O

N

N

N

大学课件-数字电子技术-俞阿龙(完整)

阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发

展起来的。 FPGA的基本特点:

(1)采用FPGA设计ASIC电路(专用集成电路),用户不需要投片

生产,就能得到合用的芯片。

(2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

(3)FPGA内部有丰富的触发器和I/O引脚。

(4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险

退出

淮阴师范学院物理与电子电气工程学院

10.1 概述

PLD是作为通用型器件生产的,具有批量大、成本低的特点, 它的逻辑功能可由用户通过对器件编程自行设定,且具有体积小、

可靠性高的优点。有些PLD的集成度很高,足以满足设计一般数 字系统的需要。这就可由设计人员自行编程将一个数字系统“集

成”在一片PLD上,做成“片上系统(System on Chip, SOC)”,而不必由芯片制造商设计和制造专用集成芯片。

退出

淮阴师范学院物理与电子电气工程学院

XC4000系列FPGA基本结构

图10.5.2 程序控制的 数据选择器

退出

淮阴师范学院物理与电子电气工程学院

10.5.2 FPGA

1. CLB

CLB是FPGA的重要组

成部分,每个CLB由2个触

发器、3个独立的4输入组合

逻辑函数发生器、程序控制

的数据选择器(符号如图

退出PAL的算淮术阴选师通范反学馈院物结理构与电子电气工程学院

在 组 成 PA L 的 与 阵

列、或阵列、输出单元

和I/O端的4部分中,与

阵列和或阵列是核心部

分;输出单元的主要功

能是决定输出极性、是

否有寄存器作为存储单

元、组织各种输出并决

SOPC系统设计与实践-要点归纳

《现代电子设计技术》课程要点归纳第1章概述1 SOPC名词解释2 VHDL名词解释:Very-High-Speed Integrated Circuit HardwareDescription Language超高速集成电路硬件描述语言3 集成电路发展的6个阶段:晶体管,小规模集成电路(SSI),中规模集成电路(MSI),大规模集成电路(LSI),超大规模集成电路(VSLI),片上可编程系统(SOC)4 片上系统(SOC)基本概念:SoC (System on Chip,片上系统) 是ASIC(Application Specific IntegratedCircuits) 设计方法学中的新技术,是指以嵌入式系统为核心,以IP 复用技术为基础,集软、硬件于一体,并追求产品系统最大包容的集成芯片.狭意些理解,可以将它翻译为“系统集成芯片”,指在一个芯片上实现信号采集、转换、存储、处理和I/O 等功能,包含嵌入软件及整个系统的全部内容;广义些理解,可以将它翻译为“系统芯片集成”,指一种芯片设计技术,可以实现从确定系统功能开始,到软硬件划分,并完成设计的整个过程.5 SOC设计方法学中的系统集成芯片技术包括的三个方面:设计重用技术,软硬件协同设计技术,纳米级电路设计技术6 SOC设计重用技术的概念、特点、构成及要求:主要指的是IP重用技术,重用预先设计并经验证的模块(可从第三方获得),以达到缩短设计周期、加快投入市场的目的;它由IP的设计和IP的使用两个部分构成,要求所设计的IP可重用、可配置和可升级,目标是IP能即插即用。

7 软硬协同技术的概念及其构成:一般来说,面向SOC的软硬件协同设计理论是从一个给定的系统描述着手,通过有效地分析系统任务和所需的资源,采用一系列变换方法并遵循特定的准则自动生成符合系统功能要求、符合系统约束的硬件和软件架构。

软硬协同主要包括系统描述、软硬件划分、软硬件协同综合以及软硬件协同模拟与验证。

集成电路实现策略

2 全定制

实例:微处理器

Intel 4004:全定制设计,1972年,NMOS 工艺,1000个晶体管,1MHz主频)

Intel Pentium 4:半定制设计为主,最关键模块(如锁相

环、时钟缓冲器)全定制设计,2003年,0.18umCMOS1工3 艺,4200万个晶体管,1.5GHz时钟频率

适用 产量极大的标准电路:微处理器、存储器、通用逻辑电路等,成 本≈投片成本 可复用模块:标准单元、库单元、具有重复性结构的单元(如 ROM、RAM、乘法器等 大部分模拟电路:结构复杂而无规则 不计成本的设计:如超级计算机、巨型计算机 反向设计的电路

不适用 规模很大的ASIC:人工设计需数年 规模大、批量不大的IC:成本~设计成本 要求设计周期短、设计成本低的电路 版图规则性差的电路:随机逻辑占50%以上

3

1 概述

数字IC的实现方式 全定制 门阵列、标准单元、宏单元 FPGA、DSP

模拟IC的实现方式 全定制 IP

SoC的实现方式 CPU/DSP/MCU+其它IP ASSP+其它IP

IC的实现方式

4

1 概述

数字IC的实现:传统方式

Digital Circuit Implementation Approaches

流程(常用软件)

10

2 全定制

底层最优化 元器件→最佳尺寸→最优性能 拓扑结构→最佳布局→最小面积 连线→最短路径→最快速度

设计成本高 周期长 人力投入大 一次成功率低(人工难免出错) 设计复用性差

自动化程度低 电路与版图规则性差 逻辑综合难以实现

特点

11

2 全定制

适用电路范围

降低了研发成本

缩短了设计周期 降低了制造成本

微处理器系统结构与嵌入式系统设计教学大纲教案

《微处理器系统结构与嵌入式系统设计》教学大纲教案课程英文名称:Microcomputer System Theory and Embedded System Design课程代码:E0130340 学时数:64 学分数:4课程类型:学科基础课程适用学科专业:工学,仪器仪表类、电气类、电子信息类、自动化类、计算机类各专业以及机械类、测绘类、航空航天类、能源动力类、交通运输类、生物医疗工程类各相关专业先修课程:数字逻辑设计及应用,高级语言程序设计,软件技术基础执笔者:编写日期:审核人:一、课程简介本课程是工学电子电气信息工程及相关专业的学科基础课程,与实践类课程《微处理器系统与嵌入式系统综合设计》(课程代码:K0175010)互为配套课程。

本课程在阐述通用微处理器系统的架构、组成及工作原理的基础上,介绍了基于ARM CPU的、现代嵌入式微系统的设计与实现技术。

课程全面涵盖了微处理器、存储器、总线及接口等计算机子系统,重点体现了嵌入式系统/片上系统中硬件电路和软件程序的协同工作原理与设计方法,具体讲述了微处理器中数据通路、控制部件及指令的实现技术、分层存储器设计技术、输入/输出接口控制技术,以及ARM微处理器程序设计技术、异常处理技术,嵌入式系统引导程序设计、接口驱动程序设计及操作系统移植等内容。

This course is a basic subject-centered course in electrical and electronic information engineering and other related specialties. It will be helpful to understand the knowledge of the co-requisite experimental course K0175010 - Microprocessor and Embedded System Laboratory.The architecture, organization and operation principles of general-purpose microprocessor systems will be elaborated, as well as the design and implementation technology for current embedded microsystems based on ARM CPU. The subsystems in a computer, including microprocessor, memories, buses, input/output interfaces and others, will be completely involved. The primary goal of this course is to studying the cooperated relationship between the hardware and software in an embedded system or a System-on-Chip, by discussing in detail on the design method for data path and the controller inside CPU, the implementation technology for hierarchy storage system, the control mode for peripherals, and the program skill for APPs, exception handlers, boot codes, drivers and operating system transplantation, and so on.二、课程目标本课程旨在培养学生深入理解微处理器芯片与嵌入式系统的架构、组成及工作原理,熟练掌握现代嵌入式微系统中硬件电路和软件程序的基本分析、设计与实现方法。

第6章SOC的体系结构

超流水线技术

提高流水线处理效率的另一个方法是缩短机器周期。 一般是将一个机器周期划分为若干个子周期,每个子 周期均发射一条新的指令,亦即每个机器周期发射多 条指令,从而提高计算机的性能。这种处理方式称为 超流水线处理技术。

取指1 取指2 译码 执行 存贮1 存贮2 检查标志 写结果 取指3 取指4 译码 执行 存贮3 存贮4 检查标志

(2) 可扩展性:所有的数据结构和接口应能方便加入新 的模块。

(3) 可综合性:处理器核的描述应该能够综合,以得到 实际电路的实现。

(4) 可测试性:处理器核的设计应该便于进行系统测试 和性能分析。

(5) 分布性:处理器的控制设计成分布式控制,便于指 令集扩展和处理器适应新的应用要求。分布式控制主要 负责流水级管理和每个流水级之间的状态通信。

微指令的结构限制了CISC CPU速度的进一步提 高。

CISC结构不利于并行处理方法。

6.1.3 嵌入式软件

有些SOC需要嵌入式实时操作系统(Real Time Operational System,简称为RTOS)的支持。

嵌入式实时操作系统是计算机操作系统的技术 和设计理念在嵌入式系统中的应用。

6.2 SOC中的嵌入式精简指令集处理 器RISC

CPU核

地址产生电路

运算电路

时序控制电路

指令译码 取指电路

DSP核

地址产生电路

运算电路

指令译码

CPU与DSP同指令流、同地址

CPU核

地址产生电路

运算电路

时序控制电路

指令译码 取指电路

DSP核 运算电路 指令译码

6.2.6 RISC核的设计

RISC核的设计原则:

(1) 模块化:若需加入新的指令,只需要修改相关的部 分,系统结构不应变化。

soc课程设计

soc课程设计一、教学目标本课程的教学目标是使学生掌握XX学科的基本概念、原理和方法,能够运用所学知识解决实际问题。

具体来说,知识目标包括:了解XX学科的基本概念和原理,掌握XX学科的基本方法,了解XX学科的发展趋势。

技能目标包括:能够运用XX学科的基本方法分析问题和解决问题,能够运用XX学科的知识进行创新性研究。

情感态度价值观目标包括:形成对XX学科的兴趣和热情,培养科学精神和探索精神,增强社会责任感和使命感。

二、教学内容根据课程目标,本课程的教学内容主要包括XX学科的基本概念、原理和方法。

具体来说,教学大纲如下:第一章:XX学科的基本概念和原理1.1 XX学科的定义和发展历程1.2 XX学科的基本原理1.3 XX学科的基本概念第二章:XX学科的基本方法2.1 XX学科方法的含义和特点2.2 XX学科的基本研究方法2.3 XX学科方法的应用案例第三章:XX学科知识的应用3.1 XX学科在实际问题中的应用3.2 XX学科在创新性研究中的应用3.3 XX学科在解决社会问题中的应用三、教学方法为了实现课程目标,本课程将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法等。

具体来说:1.讲授法:通过教师的讲解,使学生了解和掌握XX学科的基本概念、原理和方法。

2.讨论法:通过分组讨论,培养学生的思考能力和团队协作能力。

3.案例分析法:通过分析实际案例,使学生了解XX学科知识在实际问题中的应用。

4.实验法:通过实验操作,培养学生的动手能力和实践能力。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将选择和准备以下教学资源:1.教材:选用权威、实用的XX学科教材,作为学生学习的主要参考资料。

2.参考书:推荐学生阅读相关的XX学科参考书籍,拓展知识面。

3.多媒体资料:制作教学PPT、视频等多媒体资料,提高学生的学习兴趣。

4.实验设备:准备必要的实验设备,为学生提供动手实践的机会。

五、教学评估本课程的评估方式将包括平时表现、作业、考试等多个方面,以全面、客观地评价学生的学习成果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

扫描测试原理

扫描设计规则

• 扫描测试要求电路中每个节点处于可控制和可观测

的状态,只有这样才能保证其可替换为相应的扫描 单元,并且保证故障覆盖率。 • 为了保证电路中的每个节点都符合设计需求,在扫 描链插入之前会进行扫描设计规则的检查。

基本扫描规则

• 使用同种类扫描单元进行替换,通常选择带多路选

Boundary SCAN)

缺陷、故障、误差和漏洞

• 缺陷是指在集成电路制造过程中,在硅片上所产生的

物理异常,如某些器件多余或被遗漏了。 • 故障是指由于缺陷所表现出的不同于正常功能的现象 ,如电路的逻辑功能固定为1或0。 • 误差是指由于故障而造成的系统功能的偏差和错误。 • 漏洞是指由于一些设计问题而造成的功能错误,也就 是常说的bug。

测试向量举例说明

• 功能测试向量

•

以74181ALU为例,只需要448个测试矢量,但是目前 没有算法去计算矢量是否覆盖了芯片的所有功能。 结构测试向量 74181ALU只需要47个测试矢量。这类测试矢量的缺点 是有时候工具无法检测所有的故障类型。

SoC测试的目的

• 寻找最小的测试向量集去覆盖更多的芯片以及

• 扫描插入工具:Synopsys的DFT Compiler、

Mentor的DFTAdvisor。 • ATPG工具:Synopsys的TetraMAX、 Mentor的Fastscan。 • 测试矢量验证:Synopsys的TetraMAX。

扫描设计流程

存储器内建自测

• 存储器本身的物理结构密度很大。通常对存储器的测试将

整体DFT实现及性能上考虑

• 避免过长的扫描链; • 考虑到测试模式下功耗过高所造成的问题,可将扫

描测试分成数个部分,分开进行插入,在不同的扫 描测试模式下,测试不同的部分; • 尽量减少额外逻辑带来的面积、功耗的增大;

• 通过复用外围引脚,减少扫描测试对引脚的要求。

常用的测试综合和ATPG工具

这是一种基于故障模型的测试矢量,它的最大好 处是可以利用电子设计自动化(EDA)工具自动 对电路产生测试向量,并且能够有效地评估测试 效果。

测试向量举例说明

• 例如,如果要测试74181ALU,其有14个输入端

口

穷举测试向量 就需要214=16384个测试矢量,对于一个有38个输 入端口的16位的ALU来说,以10 MHz的速度运行完 所有的测试矢量需要7.64个小时

可控制性

• 把激励施加到被测单元的能力

B=0

C=0 测试 向量 = 0011 D=1

G1

0

s.a.1

A G3

1

G2

B

E=1

可观察性

• 故障传播到原始输出端的能力

A= 0

0 s.a.1

Y

A G3 B G4

期望 : 0 故障响应 : 1

故障传播

固定型故障检测举例

固定型故障检测举例

• 寻找图中故障点的测试向量

内容大纲

• 测试的概念和原理 • 故障建模 • 自动测试向量生成 • 可测性设计 • 可测性方法(SCAN、MEMORY BIST、

Boundary SCAN)

可测性设计基础

• 所谓可测性设计是指设计人员在设计系统和电路的

同时,考虑到测试的要求,通过增加一定的硬件开 销,获得最大可测性的设计过程。

常用的ATPG算法有伪随机算法和AD-Hoc算法 对于组合逻辑来说还有D算法、PODEM算法和FAN 算法

ATPG 算法步骤

• 故障类型的选择

• 检测故障

ATPG可以处理的故障类型不仅仅是阻塞型故障,还有延时故障和 路径延时故障等,一旦所有需要检测的故障类型被列举,ATPG将 对这些故障进行合理的排序,可能是按字母顺序、按层次结构排序 ,或者随机排序。

• 目前,主要的可测性设计方法有:

扫描通路测试(Scan) 内建自测试(BIST) 边界扫描测试(Boundary Scan)

可测性设计的优势和不足

优

势

不

足

可以利用EDA工具进行测试矢量的生成

增大了芯片的面积、提高了出错概率

便于故障的诊断和调试

增加设计的复杂程度

可以提高芯片的成品率并衡量其品质

带多路选择器的D型触发器

D

Q

Scan-in D Scan-enable

1

D

0

Q

Scan-out

正常工作模式:scan_enable为0,此时数据从D端输 入,从Q端输出。 扫描移位模式:scan_enable为1,此时数据从 scan_in输入,从scan_out端输出。

带扫描端的锁存器

全扫描和部分扫描

常见故障模型

• 固定型故障 • 晶体管固定开/短路故障 • 桥接故障 • 延迟故障 • 存储单元故障 • 模拟故障

固定型故障

• 这是在集成电路测试中使用最早和最普遍的故

障模型,它假设电路或系统中某个信号永久地 固定为逻辑0或者逻辑1,简记为SA0( Stuck-At-0)和SA1(Stuck-At-1)

固定型故障举例

• 共包含2×(Npins + Nports) = 2×(11+5)

= 32个固定型故障

故障合并

• 端口A的SA0故障和端口Z的SA0故障等效,同样

的端口A的SA1故障和端口Z的SA1故障等效,因 此在考虑测试矢量集的时候可以合并故障,只需要 从子故障集合{A:SA0,Z:SA0}和{A:SA1 ,Z:SA1}中各选择一个故障类型。

SoC设计方法与实现

第十章

可测性设计

内容大纲

• 测试的概念和原理 • 故障建模 • 自动测试向量生成 • 可测性设计 • 可测性方法(SCAN、MEMORY BIST、

Boundary SCAN)

内容大纲

• 测试的概念和原理 • 故障建模 • 自动测试向量生成 • 可测性设计 • 可测性方法(SCAN、MEMORY BIST、

G工具的使用步骤

• 将含扫描结构的门级网表输入到ATPG工具。 • 输入库文件。必须与门级网表相对应并且能被ATPG工具 • • • • • •

识别。 建立ATPG模型。输入库文件后,ATPG工具将根据库文 件和网表文件建立模型。 根据STIL文件做DRC检测。STIL文件是标准测试接口文 件,包含扫描结构的一系列信息和信号的约束。 生成向量。这里需要选择建立哪种故障模型。 压缩向量。这一步骤可以节约将来芯片测试时候的工作站 资源和测试时间。 转换ATPG模式的向量为ATE所需要格式的测试向量。 输出测试向量和故障列表。

基于某种故障类型,确定当前测试矢量能够覆盖多少物 理缺陷; 对于特定的抽象电路,工具能够自动选择能够匹配的故 障模型。

ATPG 算法

• 在抽象出有效故障模型的基础上,就可以开发

各 种 自 动 测 试 产 生 ( ATPG , Automatic Test Pattern Generation)向量了。

需要额外的引脚,增加了硅片面积

减少测试成本

影响了芯片的功耗、速度和其他性能

内容大纲

• 测试的概念和原理 • 故障建模 • 自动测试向量生成 • 可测性设计 • 可测性方法(SCAN、MEMORY BIST、

Boundary SCAN)

Scan

• 可测试性 • Scan的基本概念 • 扫描测试设计规则

择器的扫描触发器; • 在原始输入端必须能够对所有触发器的时钟端和异 步复位端进行控制; • 时钟信号不能作为触发器的输入信号; • 三态总线在扫描测试模式必须处于非活跃状态; • ATPG无法识别的逻辑应加以屏蔽和旁路。

三态总线

• 为了避免扫描模式(scan_mode)下的总线竞争

,必须控制其控制端,通常的做法是在控制端加入 多路选择器,使其固定在逻辑0或者逻辑1

门控时钟或者门控异步输入端

• 为了避免扫描模式下resetn不可控制,处理方法

和三态总线一样,加入额外逻辑,让异步输入端处 于非有效状态

ATPG工具不识别的逻辑

• 旁路黑盒

整体DFT实现及性能上考虑

•尽量避免异步时钟设计; •限制不同时钟域的数量; •对于多时钟域的设计,处于同一时钟域的触

发器最好连在同一根扫描链上; •注意扇出比较多的端口,如scan_enable 信号,尤其在综合的时候需要特别注意; •对于存储器、模拟电路等不可综合的逻辑加 入适当的隔离旁路结构;

晶体管开路故障

晶体管短路故障

存储器故障模型

• 单元固定故障(SAF,Stuck-At Fault)

•

单元固定故障指的是存储器单元固定在0或1。为了检测 这类故障需要对每个存储单元和传输线进行读/写0和1 的操作。 状态跳变故障(TF,Transition Delay Fault) 状态跳变故障是固定故障的特殊类型,发生在对存储单 元进行写操作的时候,不发生正常的跳变。这里需要指 出的是跳变故障和固定故障不可相互替代,因为跳变故 障可能在发生耦合故障时发生跳变,但是固定故障永远 不可能改变。为了检测此类故障必须对每个单元进行01和1-0的读/写操作,并且要在写入相反值后立刻读出 当前值。

• 检测故障传输路径

在确定了故障类型后,ATPG将决定如何对这类故障进行检测,并 且需要考虑施加激励向量的测试点,需要计算所有会影响目标节点 的可控制点。

寻找传输路径可以说是向量生成中最困难的,需要花很多时间去寻 找故障的观测点的传播。因为通常一个故障拥有很多的可观测点, 一些工具一般会找到最近的那一个。不同目标节点的传输路径可能 会造成重叠和冲突,当然这在扫描结构中是不会出现的。

制造缺陷和故障表现形式

制造过程中的缺陷 线与线之间的短路 电源与电源之间的短路 逻辑电路的开路 线开路 MOS管源漏端的开路 MOS管源漏端的短路 栅级氧化短路 PN结漏电