芯片24C01C的说明文档

如何使用单片机模拟读写24C01EEPROM数据

voidi2c_writedata(ucharaddr,uchar*ptt)

{

uchari;

i2c_start();//产生启动信号

i2c_writebyte(0XA0);//I2C写指令和IC地址

i2c_writebyte(addr);//写EEPROM地址

for(i=0;i《8;i++,ptt++)//写8个数据

//出口参数:无

//函数作用:微妙延时

//说明:

voiddelayus(ucharTIme)

{

while(TIme--)

{

asm(“nop”);

}

}

//函数名:delayms(ucharTIme);

//入口参数:time

//出口参数:无

//函数作用:延时

//说明:

//***********************************************

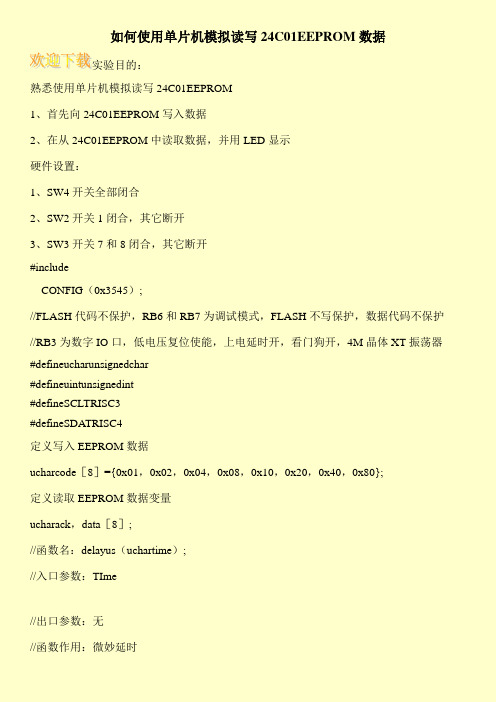

如何使用单片机模拟读写24C01EEPROM数据

实验目的:

熟悉使用单片机模拟读写24C01EEPROM

1、首先向24C01EEPROM写入数据

2、在从24C01EEPROM中读取数据,并用LED显示

硬件设置:

1、SW4开关全部闭合

2、SW2开关1闭合,其它断开

3、SW3开关7和8闭合,其它断开

#include

#defineSDATRISC4

定义写入EEPROM数据

ucharcode[8]={0x01,0x02,0x04,0x08,0x10,0x20,0x40,0x80};

定义读取EEPROM数据变量

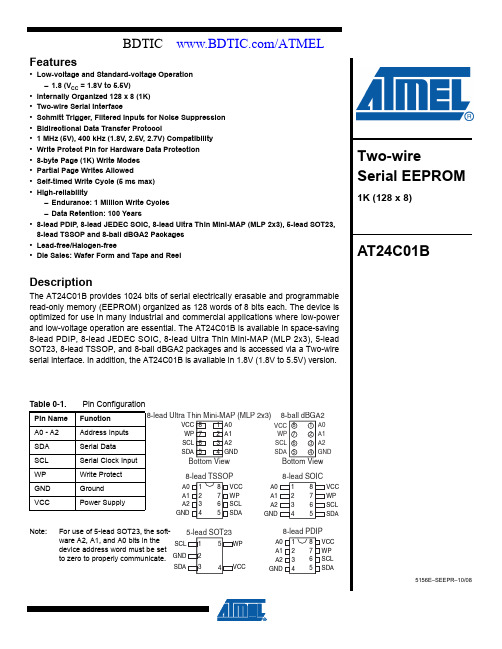

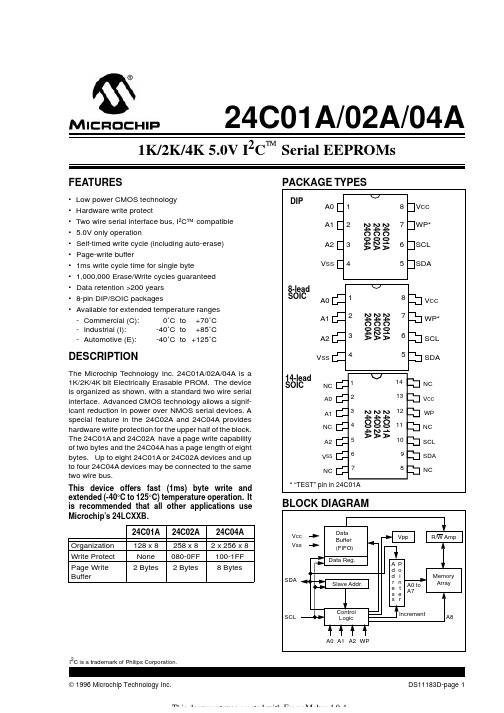

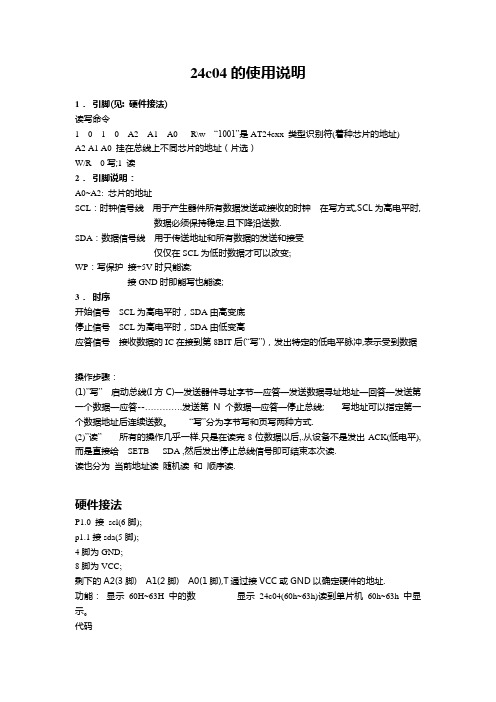

ATMEL AT24C01B 说明书

Features•Low-voltage and Standard-voltage Operation –1.8 (V CC = 1.8V to 5.5V)•Internally Organized 128 x 8 (1K)•Two-wire Serial Interface•Schmitt Trigger, Filtered Inputs for Noise Suppression •Bidirectional Data Transfer Protocol• 1 MHz (5V), 400 kHz (1.8V, 2.5V, 2.7V) Compatibility •Write Protect Pin for Hardware Data Protection •8-byte Page (1K) Write Modes •Partial Page Writes Allowed•Self-timed Write Cycle (5 ms max)•High-reliability–Endurance: 1 Million Write Cycles –Data Retention: 100 Years•8-lead PDIP , 8-lead JEDEC SOIC, 8-lead Ultra Thin Mini-MAP (MLP 2x3), 5-lead SOT23,8-lead TSSOP and 8-ball dBGA2 Packages •Lead-free/Halogen-free•Die Sales: Wafer Form and Tape and ReelDescriptionThe AT24C01B provides 1024 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 128 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The AT24C01B is available in space-saving 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead Ultra Thin Mini-MAP (MLP 2x3), 5-lead SOT23, 8-lead TSSOP, and 8-ball dBGA2 packages and is accessed via a Two-wire serial interface. In addition, the AT24C01B is available in 1.8V (1.8V to 5.5V) version.Table 0-1.Pin ConfigurationTwo-wireSerial EEPROM1K (128 x 8)AT24C01B5156E–SEEPR–10/08BDTIC www.BDTIC .com/ATMEL25156E–SEEPR–10/08AT24C01BFigure 0-1.Block DiagramAbsolute Maximum RatingsOperating Temperature..................................–55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Storage Temperature.....................................–65°C to +150°C Voltage on Any Pinwith Respect to Ground....................................–1.0V to +7.0V Maximum Operating Voltage..........................................6.25V DC Output Current........................................................5.0 mA35156E–SEEPR–10/08AT24C01B1.Pin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.DEVICE/PAGE ADDRESSES (A2, A1, A0): The A2, A1 and A0 pins are device address inputs that are hard wired for the AT24C01B. As many as eight 1K devices may be addressed on a sin-gle bus system (device addressing is discussed in detail under the Device Addressing section).WRITE PROTECT (WP): The AT24C01B has a write protect pin that provides hardware data protection. The write protect pin allows normal read/write operations when connected to ground (GND). When the write protect pin is connected to V CC , the write protection feature is enabled and operates as shown in Table 1-1.Table 1-1.Write Protect2.Memory OrganizationAT24C01B, 1K SERIAL EEPROM: Internally organized with 16 pages of 8 bytes each, the 1K requires an 7-bit data word address for random word addressing. (See Figure 8-2 on page 10)WP Pin Status Part of the Array Protected24C01BAt V CC Full (1K) ArrayAt GNDNormal Read/Write Operations45156E–SEEPR–10/08AT24C01BNote:1.This parameter is characterized and is not 100% tested.Note:1.V IL min and V IH max are reference only and are not tested.Table 2-1.Pin Capacitance (1)Applicable over recommended operating range from T A = 25°C, f = 1.0 MHz, V CC = +1.8VSymbol Test ConditionMax Units Conditions C I/O Input/Output Capacitance (SDA)8pF V I/O = 0V C IN Input Capacitance (A 0, A 1, A 2, SCL)6pFV IN = 0VTable 2-2.DC CharacteristicsApplicable over recommended operating range from: T AI = –40°C to +85°C, V CC = +1.8V to +5.5V, V CC =+1.8V to +5.5V (unless otherwise noted)Symbol Parameter Test ConditionMin TypMax Units V CC1Supply Voltage 1.8 5.5V V CC2Supply Voltage 2.5 5.5V V CC3Supply Voltage 2.7 5.5V V CC4Supply Voltage4.55.5V I CC Supply Current V CC = 5.0V READ at 100 kHz 0.4 1.0mA I CC Supply Current V CC = 5.0V WRITE at 100 kHz 2.0 3.0mA I SB1Standby Current V CC = 1.8V V IN = V CC or V SS 0.6 3.0µA I SB2Standby Current V CC = 2.5V V IN = V CC or V SS 1.4 4.0µA I SB3Standby Current V CC = 2.7V V IN = V CC or V SS 1.6 4.0µA I SB4Standby Current V CC = 5.0V V IN = V CC or V SS 8.018.0µA I LI Input Leakage Current V IN = V CC or V SS 0.10 3.0µA I LO Output Leakage Current V OUT = V CC or V SS0.05 3.0µA V IL Input Low Level (1)–0.6V CC x 0.3V V IH Input High Level (1)V CC x 0.7V CC + 0.5V V OL2Output Low Level V CC = 3.0V I OL = 2.1 mA 0.4V V OL1Output Low Level V CC = 1.8VI OL = 0.15 mA 0.2V55156E–SEEPR–10/08AT24C01BNote:1.This parameter is ensured by characterization only.Table 2-3.AC CharacteristicsApplicable over recommended operating range from T AI = –40°C to +85°C, V CC = +1.8V to +5.5V, CL = 1 TTL Gate and 100pF (unless otherwise noted)Symbol Parameter1.8,2.5, 2.75.0-volt Units MinMax MinMax f SCL Clock Frequency, SCL 4001000kHz t LOW Clock Pulse Width Low 1.20.4µs t HIGH Clock Pulse Width High 0.60.4µs t I Noise Suppression Time 5040ns t AA Clock Low to Data Out Valid0.10.90.050.55µs t BUF Time the bus must be free before a new transmission can start 1.20.5µs t HD.STA Start Hold Time 0.60.25µs t SU.STA Start Setup Time 0.60.25µs t HD.DAT Data In Hold Time 00µs t SU.DAT Data In Setup Time 100100ns t R Inputs Rise Time (1)0.30.3µs t F Inputs Fall Time (1)300100ns t SU.STO Stop Setup Time 0.6.25µs t DH Data Out Hold Time 5050ns t WRWrite Cycle Time 55ms Endurance (1) 5.0V, 25°C, Byte Mode1 MillionWrite Cycles65156E–SEEPR–10/08AT24C01B3.Device OperationCLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (see Figure 5-2 on page 8). Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 5-3 on page 8).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (see Fig-ure 5-3 on page 8).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it has received each word. This happens during the ninth clock cycle.STANDBY MODE: The AT24C01B features a low-power standby mode which is enabled: (a)upon power-up and (b) after the receipt of the STOP bit and the completion of any internal operations.2-WIRE SOFTWARE RESET: After an interruption in protocol, power loss or system reset, any 2-wire part can be protocol reset by following these steps: (a) Create a start bit condition, (b)Clock 9 cycles, (c) Create another start bit followed by a stop bit condition as shown below. Thedevice is ready for next communication after above steps have been completed.75156E–SEEPR–10/08AT24C01B4.Bus TimingFigure 4-1.SCL: Serial Clock, SDA: Serial Data I/O ®5.Write Cycle TimingFigure 5-1.SCL: Serial Clock, SDA: Serial Data I/ONote:1.The write cycle time t WRis the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.85156E–SEEPR–10/08AT24C01BFigure 5-2.Data ValidityFigure 5-3.Start and Stop DefinitionFigure 5-4.Output Acknowledge95156E–SEEPR–10/08AT24C01B6.Device AddressingThe 1K EEPROM device requires an 8-bit device address word following a start condition to enable the chip for a read or write operation (refer to Figure 8-1).The device address word consists of a mandatory one, zero sequence for the first four most sig-nificant bits as shown. This is common to all the EEPROM devices.The next 3 bits are the A2, A1 and A0 device address bits for the 1K EEPROM. These 3 bits must compare to their corresponding hard-wired input pins.The eighth bit of the device address is the read/write operation select bit. A read operation is ini-tiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a zero. If a compare is not made, the chip will return to a standby state.7.Write OperationsBYTE WRITE: A write operation requires an 8-bit data word address following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a zero and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a zero and the addressing device, such as a microcontroller,must terminate the write sequence with a stop condition. At this time the EEPROM enters an internally timed write cycle, t WR , to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 8-2 on page 10).PAGE WRITE: The 1K EEPROM is capable of an 8-byte page write.A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to seven data words. The EEPROM will respond with a zero after each data word received. The microcontroller must ter-minate the page write sequence with a stop condition (see Figure 8-3 on page 11).The data word address lower three bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the fol-lowing byte is placed at the beginning of the same page. If more than eight data words are transmitted to the EEPROM, the data word address will “roll over” and previous data will be overwritten.ACKNOWLEDGE POLLING: Once the internally timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a zero allowing the read or write sequence to continue.105156E–SEEPR–10/08AT24C01B8.Read OperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one. There are three read operations:current address read, random address read and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address “roll over”during read is from the last byte of the last memory page to the first byte of the first page. The address “roll over” during write is from the last byte of the current page to the first byte of the same page.Once the device address with the read/write select bit set to one is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input zero but does generate a following stop condition (see Figure 8-4 on page 11).RANDOM READ: A random read requires a “dummy” byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a zero but does generate a follow-ing stop condition (see Figure 8-5 on page 11).SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a ran-dom address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will “roll over” and the sequential read will continue. The sequential read operation is terminated when the microcontroller does not respond with a zero but does generate a following stop condition (see Figure 8-6 on page 12).Figure 8-1.Device AddressFigure 8-2.Byte Write115156E–SEEPR–10/08AT24C01BFigure 8-3.Page WriteFigure 8-4.Current Address ReadFigure 8-5.Random Read125156E–SEEPR–10/08AT24C01BFigure 8-6.Sequential Read135156E–SEEPR–10/08AT24C01BNotes:1.“-B” denotes bulk.2.“-T” denotes tape and reel. SOIC = 4K per reel. TSSOP , Ultra Thin Mini MAP , SOT 23 and dBGA2 = 5K per reel.3.Available in tape and reel and wafer form; order as SL788 for inkless wafer form. Please contact Serial Interface Marketing.AT24C01B Ordering InformationOrdering CodePackage Voltage Range Operation RangeAT24C01B-PU (Bulk form only)8P3 1.8V to 5.5V Lead-free/Halogen-free/Industrial Temperature (–40°C to 85°C)AT24C01BN-SH-B (1) (NiPdAu Lead Finish)8S1 1.8V to 5.5V AT24C01BN-SH-T (2) (NiPdAu Lead Finish)8S1 1.8V to 5.5V AT24C01B-TH-B (1) (NiPdAu Lead Finish)8A2 1.8V to 5.5V AT24C01B-TH-T (2) (NiPdAu Lead Finish)8A2 1.8V to 5.5V AT24C01BY6-YH -T(2) (NiPdAu Lead Finish)8Y6 1.8V to 5.5V AT24C01B-TSU -T(2)5TS1 1.8V to 5.5V AT24C01BU3-UU -T(2)8U3-1 1.8V to 5.5V AT24C01B-W-11(3)Die Sale1.8V to 5.5VIndustrial Temperature (–40°C to 85°C)Package Type8P38-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)8Y68-lead, 2.0 mm x 3.00 mm Body, 0.50 mm Pitch, Ultra Thin Mini-MAP , Dual No Lead Package (DFN), (MLP 2x3 mm)5TS15-lead, 2.90 mm x 1.60 mm Body, Plastic Thin Shrink Small Outline Package (SOT23)8U3-18-ball, die Ball Grid Array Package (dBGA2)145156E–SEEPR–10/08AT24C01B9.Part Marking Scheme8-PDIPSeal Year TOP MARK| Seal Week | | ||---|---|---|---|---|---|---|---| A T M L U Y W W |---|---|---|---|---|---|---|---| 0 1 B 1|---|---|---|---|---|---|---|---| * Lot Number|---|---|---|---|---|---|---|---| |Pin 1 Indicator (Dot)U = Material Set Y = Seal Year WW = Seal Week 01B = DeviceV = Voltage Indicator*Lot Number to Use ALL Characters in Marking BOTTOM MARKNo Bottom Mark155156E–SEEPR–10/08AT24C01B8-SOICSeal Year TOP MARK | Seal Week| | ||---|---|---|---|---|---|---|---| A T M L H Y W W |---|---|---|---|---|---|---|---| 0 1 B 1|---|---|---|---|---|---|---|---| * Lot Number|---|---|---|---|---|---|---|---| |Pin 1 Indicator (Dot)H = Material Set Y = Seal Year WW = Seal Week 01B = Device 1 = Voltage Indicator*Lot Number to Use ALL Characters in Marking BOTTOM MARKNo Bottom Mark8-TSSOPTOP MARKPin 1 Indicator (Dot) ||---|---|---|---| * H Y W W |---|---|---|---|---|01B 1 |---|---|---|---|---|H = Material Set Y = Seal Year WW = Seal Week 01B = Device 1 = Voltage Indicator165156E–SEEPR–10/08AT24C01BBOTTOM MARK|---|---|---|---|---|---|---| X X|---|---|---|---|---|---|---| A A A A A A A |---|---|---|---|---|---|---| <- Pin 1 IndicatorLot NumberXX = Country of Origin AAAAAA = Lot NumberSOT23TOP MARK|---|---|---|---|---|Line 1 -----------> 1 B 1 W U|---|---|---|---|---| *| Pin 1 Indicator (Dot)1B = Device1 = Voltage IndicatorW = Write Protect Feature U = Material SetBOTTOM MARK|---|---|---|---| Y M T C |---|---|---|---|Y = One Digit Year Code M = Seal Month TC = Trace Code175156E–SEEPR–10/08AT24C01BULTRA THIN MINI MAPTOP MARK|---|---|---| 0 1 B |---|---|---| H 1 |---|---|---|Y T C |---|---|---| * |Pin 1 Indicator (Dot) 01B = Device H = Material Set1 = Voltage Indicator Y = Year of Assembly TC = Trace CodedBGA2TOP MARKLINE 1-------> 01BU LINE 2-------> YMTC|<-- Pin 1 This Corner 01B = DeviceU = Material SetY = One Digit Year Code M = Seal Month TC = Trace Code185156E–SEEPR–10/08AT24C01B10.Packaging Information10.18P3 – PDIP195156E–SEEPR–10/08AT24C01B10.28S1 – JEDEC SOIC205156E–SEEPR–10/08AT24C01B10.38A2 – TSSOPAT24C01B12.5TS1 – SOT23AT24C01B 13.8U3-1 – dBGA2Revision HistoryDoc. Rev.Date Comments5156E10/2008Modified Ordering Information5156D8/2007Added Part Marking Scheme5156C4/2007Removed NC and GND from Pin Configuration; Removed Preliminary from page 1 and all headers/footers; Added 2-wire Software Reset; Removed LSB and MSB from figures; Removed waffle pack from die sale order information5156B5/2006Ordering information changed; added -B denotes bulk; added bulk ordering codes; added tape and reel ordering codes5156A4/2006Initial document release。

24c芯片

24c芯片24C芯片是一种串行电可擦写非易失性存储器芯片,由美国Microchip科技公司推出。

24C芯片采用2线串行I2C总线协议进行通信,具有低功耗、高可靠性和大容量的特点。

本文将介绍24C芯片的功能、特性、应用以及使用24C芯片进行存储器编程的方法,总计约1000字。

24C芯片具有以下功能和特性:1. 容量:24C系列芯片的容量从1K到512K不等,可以存储不同大小的数据。

2. I2C接口:采用2线串行I2C总线协议进行通信,可以方便地连接到多种微控制器和其他外围设备。

3. 读写速度:24C芯片的读写速度较快,可以在较短的时间内完成存储器的读写操作。

4. 电可擦写:24C芯片采用电可擦写技术,在不需要电源的情况下,可以对存储的数据进行擦写和修改。

5. 高可靠性:24C芯片具有良好的耐久性和可靠性,可以在广泛的工作温度范围内正常工作。

24C芯片的应用非常广泛,常见的应用包括:1. 数字产品:24C芯片可以用于存储数字产品中的配置信息、用户数据等。

2. 工业自动化:在工业自动化领域中,24C芯片可以用于存储设备的配置参数、运行数据等。

3. 汽车电子:汽车电子产品中常常需要存储一些重要的数据,比如行车记录、车辆配置信息等。

24C芯片可以满足这些需求。

4. 仪器仪表:24C芯片可以用于存储仪器仪表中的校准数据、测量结果等。

使用24C芯片进行存储器编程的方法如下:1. 硬件连接:将24C芯片与微控制器或其他主设备连接,连接时需要注意芯片的地址设置。

2. 初始化:通过I2C总线发送初始化命令,将24C芯片设置为写模式。

3. 写数据:发送写数据命令和数据地址,然后发送要写入的数据。

可以逐个字节写入,也可以连续写入多个字节。

4. 擦除数据:可以对整个芯片进行擦除,也可以对指定的数据进行擦除。

5. 读数据:发送读数据命令和数据地址,然后接收芯片返回的数据。

可以逐个字节读取,也可以连续读取多个字节。

需要注意的是,在进行24C芯片的读写操作时,需要注意处理超时、错误检测等异常情况,以保证数据的完整性和正确性。

AT24C01+点阵

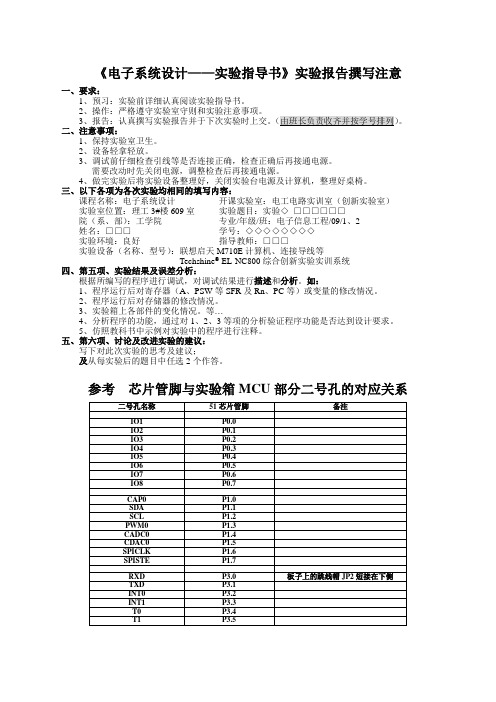

《电子系统设计——实验指导书》实验报告撰写注意一、要求:1、预习:实验前详细认真阅读实验指导书。

2、操作:严格遵守实验室守则和实验注意事项。

3、报告:认真撰写实验报告并于下次实验时上交。

二、注意事项:1、保持实验室卫生。

2、设备轻拿轻放。

3、调试前仔细检查引线等是否连接正确,检查正确后再接通电源。

需要改动时先关闭电源,调整检查后再接通电源。

4、做完实验后将实验设备整理好,关闭实验台电源及计算机,整理好桌椅。

三、以下各项为各次实验均相同的填写内容:课程名称:电子系统设计开课实验室:电工电路实训室(创新实验室)实验室位置:理工3#楼609室实验题目:实验◇□□□□□□院(系、部):工学院专业/年级/班:电子信息工程/09/1、2姓名:□□□学号:◇◇◇◇◇◇◇◇实验环境:良好指导教师:□□□实验设备(名称、型号):联想启天M710E计算机、连接导线等Techshine® EL-NC800综合创新实验实训系统四、第五项、实验结果及误差分析:根据所编写的程序进行调试,对调试结果进行描述和分析。

如:1、程序运行后对寄存器(A、PSW等SFR及Rn、PC等)或变量的修改情况。

2、程序运行后对存储器的修改情况。

3、实验箱上各部件的变化情况。

等…4、分析程序的功能,通过对1、2、3等项的分析验证程序功能是否达到设计要求。

5、仿照教科书中示例对实验中的程序进行注释。

五、第六项、讨论及改进实验的建议:写下对此次实验的思考及建议;及从每实验后的题目中任选2个作答。

参考芯片管脚与实验箱MCU部分二号孔的对应关系参考HD72791、HD7279的主要特点(1)与CPU间采用SPI串行接口方式,仅占用4根口线;(2)内部含有译码器,可直接接收BCD码或16进制码,同时具有两种译码方式,实现LED 数码管位寻址和段寻址,消隐和闪烁属性等多种控制指令,编程灵活;(3)循环左移和循环右移指令;(4)内部含有驱动器,无需外围元件可直接驱动LED;(5)具有级联功能,可方便的实现多于8位显示或多于64键的键盘接口;(6)具有自动消除抖动并识别按键键值的功能。

24c02中文资料

24c02中文资料1. 简介24c02是Microchip公司推出的一种串行电子可擦写可编程读写存储器,属于EEPROM(Electrically Erasable Programmable Read-Only Memory)系列。

它采用2-wire串行总线(I2C)接口,具有体积小、功耗低、可靠性高等特点。

本文档将详细介绍24c02的硬件特性、接口规范、存储容量和使用方法。

2. 硬件特性24c02的主要硬件特性如下:•存储容量:24c02有256个字节,每个字节有8位,总计拥有2Kb的存储空间。

•工作电源:24c02需要使用3.3V到5V的供电电压,支持广泛的电源电压范围。

•通信接口:24c02使用I2C串行总线进行通信,具有两根信号线:串行数据线(SDA)和串行时钟线(SCL)。

•封装类型:24c02有多种封装类型可供选择,如DIP(双列直插式封装)、SOP(小型轻负载封装)等。

3. 接口规范24c02采用I2C串行总线接口,其接口规范如下:•数据传输方式:24c02支持字节读写操作和页写操作。

字节读写操作是指每次读写一个字节的数据;页写操作是指每次可以写入8个连续字节的数据。

•起始信号和停止信号:在I2C总线上进行通信时,需要发送起始信号(Start)和停止信号(Stop)以标识数据传输的开始和结束。

•从器件地址:24c02有多个从器件地址可供选择,通过设置硬件地址引脚,可以实现多个24c02器件的级联。

4. 存储容量24c02的存储容量为2Kb,相当于256个字节。

每个字节有8位,可存储0x00到0xFF的数据。

这些存储空间可以被分为多个页,每页包含8个字节。

5. 使用方法以下是24c02的基本使用方法,供参考:•初始化:将24c02与主控芯片(如单片机)连接,并提供正常的供电电源。

同时,设置24c02的硬件地址引脚,确保能正确寻址。

•写入数据:选择要写入数据的存储地址,发送起始信号和器件地址,然后发送数据字节。

24C01A外部eeprom

DS11183D-page 12© 1996 Microchip Technology Inc.Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. No repre-sentation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip’s products as critical components in life support systems is not autho-rized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights. The Microchip logo and name are registered trademarks of Microchip Technology Inc. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.W ORLDWIDE S ALES & S ERVICEASIA/PACIFICChinaMicrochip TechnologyUnit 406 of Shanghai Golden Bridge Bldg.2077 Yan’an Road West, Hongiao District Shanghai, Peoples Republic of China Tel: 86 21 6275 5700Fax: 011 86 21 6275 5060 Hong KongMicrochip Technology RM 3801B, Tower Two Metroplaza223 Hing Fong RoadKwai Fong, N.T. Hong KongTel: 852 2 401 1200 Fax: 852 2 401 3431IndiaMicrochip TechnologyNo. 6, Legacy, Convent Road Bangalore 560 025 IndiaTel: 91 80 526 3148 Fax: 91 80 559 9840KoreaMicrochip Technology168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku,Seoul, KoreaTel: 82 2 554 7200 Fax: 82 2 558 5934SingaporeMicrochip Technology 200 Middle Road #10-03 Prime Centre Singapore 188980Tel: 65 334 8870 Fax: 65 334 8850Taiwan, R.O.CMicrochip Technology 10F-1C 207Tung Hua North Road Taipei, Taiwan, ROCTel: 886 2 717 7175 Fax: 886 2 545 0139EUROPEUnited KingdomArizona Microchip Technology Ltd.Unit 6, The CourtyardMeadow Bank, Furlong RoadBourne End, Buckinghamshire SL8 5AJ Tel: 44 1628 850303 Fax: 44 1628 850178FranceArizona Microchip Technology SARL Zone Industrielle de la Bonde 2 Rue du Buisson aux Fraises 91300 Massy - FranceTel: 33 1 69 53 63 20 Fax: 33 1 69 30 90 79GermanyArizona Microchip Technology GmbH Gustav-Heinemann-Ring 125D-81739 Muenchen, GermanyTel: 49 89 627 144 0 Fax: 49 89 627 144 44ItalyArizona Microchip Technology SRLCentro Direzionale Colleone Pas Taurus 1Viale Colleoni 120041 Agrate Brianza Milan ItalyTel: 39 39 6899939 Fax: 39 39 689 9883JAPANMicrochip Technology Intl. Inc.Benex S-1 6F3-18-20, Shin Yokohama Kohoku-Ku, Yokohama Kanagawa 222 JapanTel: 81 45 471 6166 Fax: 81 45 471 61229/3/96AMERICASCorporate OfficeMicrochip Technology Inc.2355 West Chandler Blvd.Chandler, AZ 85224-6199Tel: 602 786-7200 Fax: 602 786-7277Technical Support: 602 786-7627Web: AtlantaMicrochip Technology Inc.500 Sugar Mill Road, Suite 200B Atlanta, GA 30350Tel: 770 640-0034 Fax: 770 640-0307BostonMicrochip Technology Inc.5 Mount Royal Avenue Marlborough, MA 01752Tel: 508 480-9990 Fax: 508 480-8575ChicagoMicrochip Technology Inc.333 Pierce Road, Suite 180Itasca, IL 60143Tel: 708 285-0071 Fax: 708 285-0075DallasMicrochip Technology Inc.14651 Dallas Parkway, Suite 816Dallas, TX 75240-8809Tel: 972 991-7177 Fax: 972 991-8588DaytonMicrochip Technology Inc.Suite 150Two Prestige Place Miamisburg, OH 45342Tel: 513 291-1654 Fax: 513 291-9175Los AngelesMicrochip Technology Inc.18201 Von Karman, Suite 1090Irvine, CA 92612Tel: 714 263-1888 Fax: 714 263-1338New YorkMicrochip Technmgy Inc.150 Motor Parkway, Suite 416Hauppauge, NY 11788Tel: 516 273-5305 Fax: 516 273-5335San JoseMicrochip Technology Inc.2107 North First Street, Suite 590San Jose, CA 95131Tel: 408 436-7950 Fax: 408 436-7955TorontoMicrochip Technology Inc.5925 Airport Road, Suite 200Mississauga, Ontario L4V 1W1, Canada Tel: 905 405-6279Fax: 905 405-6253All rights reserved. © 1996, Microchip Technology Incorporated, USA. 9/96Printed on recycled paper.This datasheet has been downloaded from:Free DownloadDaily Updated Database100% Free Datasheet Search Site100% Free IC Replacement Search SiteConvenient Electronic DictionaryFast Search SystemAll Datasheets Cannot Be Modified Without PermissionCopyright © Each Manufacturing Company。

eeprom24C系列芯片中文

分布电容 TA=25 , f =1.0MHz, Vcc =5V 测试项 I/O 电容 SDA 脚 输出电容 A0 A1 A2 SCL WP 最大 8 6 单位 PF PF 条件 VI/O=0V VIN=0V 符号 CI/O CIN 交流特性 Vcc=+1.8V +6.0V 除非特别说明 输出负载能力为 1 个 TTL 门和 100pF 读写周期范围 符号 FSCL TI tAA tBUF tHD: STA tLOW tHIGH tSU: STA tHD: DAT tSUl: DAT tR tF tSU: STO tDH 时钟频率 SCL,SDA 输入的噪声抑制时间 SCL 变低至 SDA 数据输出及应答信号 新的发送开始前总线空闲时间 起始信号保持时间 时钟低电平周期 时钟高电平周期 起始信号建立时间 数据输入保持时间 数据输入建立时间 SDA 及 SCL 上升时间 SDA 及 SCL 下降时间 停止信号建立时间 数据输出保持时间 4 100 4.7 4 4.7 4 4.7 0 50 1 300 0.6 100 参数 1.8 V 最小 2.5 V 最大 100 200 3.5 1.2 0.6 1.2 0.6 0.6 0 50 0.3 300 4.5V 最小 5.5V 最大 400 200 1 单位 KHz ns s s s s s s ns ns s ns s ns

I2C 总线协议

I2C 总线协议定义如下

5

广州周立功单片机发展有限公司 Tel

020

38730976

38730977

Fax 38730925

1 只有在总线空闲时才允许启动数据传送 2 在数据传送过程中 钟线为高电平时 起始信号 时钟线保持高电平期间 数据线电平从高到低的跳变作为 I2C 总线的起始信号 停止信号 时钟线保持高电平期间 数据线电平从低到高的跳变作为 I2C 总线的停止信号 图1 总线时序 当时钟线为高电平时 数据线必须保持稳定状态 不允许有跳变 时 数据线的任何电平变化将被看作总线的起始或停止信号

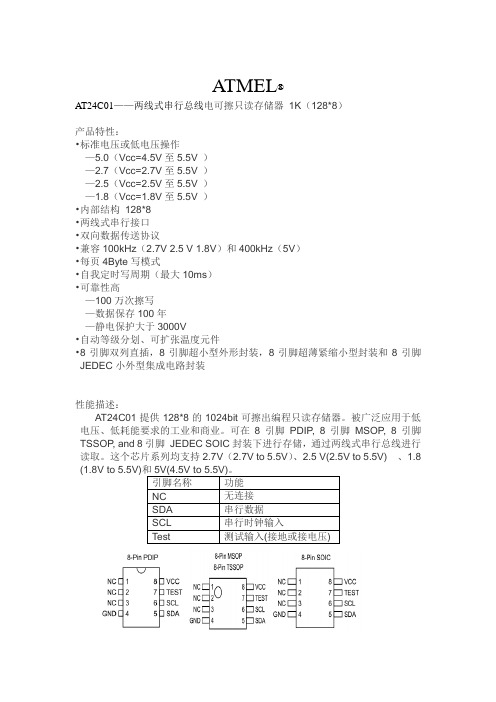

AT24C

1Features•Low-voltage and Standard-voltage Operation –2.7 (V CC = 2.7V to 5.5V)–1.8 (V CC = 1.8V to 5.5V)•Internally Organized 128 x 8 (1K), 256 x 8 (2K), 512 x 8 (4K),1024 x 8 (8K) or 2048 x 8 (16K)•Two-wire Serial Interface•Schmitt Trigger, Filtered Inputs for Noise Suppression •Bidirectional Data Transfer Protocol•100 kHz (1.8V) and 400 kHz (2.7V, 5V) Compatibility •Write Protect Pin for Hardware Data Protection•8-byte Page (1K, 2K), 16-byte Page (4K, 8K, 16K) Write Modes •Partial Page Writes Allowed•Self-timed Write Cycle (5 ms max)•High-reliability–Endurance: 1 Million Write Cycles –Data Retention: 100 Years •Automotive Devices Available•8-lead JEDEC PDIP , 8-lead JEDEC SOIC, 8-lead Ultra Thin Mini-MAP (MLP 2x3), 5-lead SOT23, 8-lead TSSOP and 8-ball dBGA2 Packages•Die Sales: Wafer Form, Waffle Pack and Bumped WafersDescriptionThe AT24C01A/02/04/08A/16A provides 1024/2048/4096/8192/16384 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 128/256/512/1024/2048 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The AT24C01A/02/04/08A/16A is available in space-saving 8-lead PDIP ,8-lead JEDEC SOIC, 8-lead Ultra Thin Mini-MAP (MLP 2x3), 5-lead SOT23(AT24C01A/AT24C02/AT24C04), 8-lead TSSOP, and 8-ball dBGA2 packages and is accessed via a Two-wire serial interface. In addition, the entire family is available in 2.7V (2.7V to 5.5V) and 1.8V (1.8V to 5.5V) versions. Table 1. Pin ConfigurationPin Name Function A0 - A2Address Inputs SDA Serial Data SCL Serial Clock Input WP Write Protect NC No Connect GND Ground VCCPower Supply8-lead SOIC 8-lead PDIP8-lead Ultra Thin Mini-MAP(MLP 2x3)Bottom View 5-lead SOT238-ball dBGA2Bottom View 8-lead TSSOP2AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Figure 1. Block DiagramAbsolute Maximum RatingsOperating Temperature..................................–55°C to +125°C *NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent dam-age to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Storage Temperature.....................................–65°C to +150°C Voltage on Any Pinwith Respect to Ground....................................–1.0V to +7.0V Maximum Operating Voltage..........................................6.25V DC Output Current........................................................5.0 mA3AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Pin DescriptionSERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA): The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.DEVICE/PAGE ADDRESSES (A2, A1, A0): The A2, A1 and A0 pins are device address inputs that are hard wired for the AT24C01A and the AT24C02. As many as eight 1K/2K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section).The AT24C04 uses the A2 and A1 inputs for hard wire addressing and a total of four 4K devices may be addressed on a single bus system. The A0 pin is a no connect and can be connected to ground.The AT24C08A only uses the A2 input for hardwire addressing and a total of two 8K devices may be addressed on a single bus system. The A0 and A1 pins are no connects and can be connected to ground.The AT24C16A does not use the device address pins, which limits the number of devices on a single bus to one. The A0, A1 and A2 pins are no connects and can be connected to ground.WRITE PROTECT (WP): The AT24C01A/02/04/08A/16A has a Write Protect pin that provides hardware data protection. The Write Protect pin allows normal Read/Write operations when connected to ground (GND). When the Write Protect pin is connected to V CC , the write protection feature is enabled and operates as shown in Table 2.Table 2. Write ProtectMemory OrganizationAT24C01A, 1K SERIAL EEPROM: Internally organized with 16 pages of 8 bytes each,the 1K requires a 7-bit data word address for random word addressing.AT24C02, 2K SERIAL EEPROM: Internally organized with 32 pages of 8 bytes each,the 2K requires an 8-bit data word address for random word addressing.AT24C04, 4K SERIAL EEPROM: Internally organized with 32 pages of 16 bytes each,the 4K requires a 9-bit data word address for random word addressing.AT24C08A, 8K SERIAL EEPROM: Internally organized with 64 pages of 16 bytes each, the 8K requires a 10-bit data word address for random word addressing. AT24C16A, 16K SERIAL EEPROM: Internally organized with 128 pages of 16 bytes each, the 16K requires an 11-bit data word address for random word addressing.WP Pin Status Part of the Array Protected24C01A 24C0224C0424C08A 24C16A At V CC Full (1K) ArrayFull (2K) ArrayFull (4K) ArrayFull (8K) ArrayFull (16K) ArrayAt GNDNormal Read/Write Operations4AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Note:1.This parameter is characterized and is not 100% tested.Note:1.V IL min and V IH max are reference only and are not tested.Table 3. Pin Capacitance (1)Applicable over recommended operating range from T A = 25°C, f = 1.0 MHz, V CC = +1.8VSymbol Test ConditionMax Units Conditions C I/O Input/Output Capacitance (SDA)8pF V I/O = 0V C IN Input Capacitance (A 0, A 1, A 2, SCL)6pFV IN = 0VTable 4. DC CharacteristicsApplicable over recommended operating range from: T AI = –40°C to +85°C, V CC = +1.8V to +5.5V, V CC =+1.8V to +5.5V (unless otherwise noted)Symbol Parameter Test ConditionMin TypMax Units V CC1Supply Voltage 1.8 5.5V V CC2Supply Voltage 2.7 5.5V V CC3Supply Voltage4.55.5V I CC Supply Current V CC = 5.0V READ at 100 kHz 0.4 1.0mA I CC Supply Current V CC = 5.0V WRITE at 100 kHz 2.0 3.0mA I SB1Standby Current V CC = 1.8V V IN = V CC or V SS 0.6 3.0µA I SB2Standby Current V CC = 2.5V V IN = V CC or V SS 1.4 4.0µA I SB3Standby Current V CC = 2.7V V IN = V CC or V SS 1.6 4.0µA I SB4Standby Current V CC = 5.0V V IN = V CC or V SS 8.018.0µA I LI Input Leakage Current V IN = V CC or V SS 0.10 3.0µA I LO Output Leakage Current V OUT = V CC or V SS0.05 3.0µA V IL Input Low Level (1)–0.6V CC x 0.3V V IH Input High Level (1)V CC x 0.7V CC + 0.5V V OL2Output Low Level V CC = 3.0V I OL = 2.1 mA 0.4V V OL1Output Low Level V CC = 1.8VI OL = 0.15 mA 0.2V5AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Note:1.This parameter is characterized.Table 5. AC CharacteristicsApplicable over recommended operating range from T AI = –40°C to +85°C, V CC = +1.8V to +5.5V, V CC = +2.7V to +5.5V,CL = 1 TTL Gate and 100pF (unless otherwise noted)Symbol Parameter1.8-volt2.7, 5.0-volt Units MinMax MinMax f SCL Clock Frequency, SCL 100400kHz t LOW Clock Pulse Width Low 4.7 1.2µs t HIGH Clock Pulse Width High 4.00.6µs t I Noise Suppression Time (1)10050ns t AA Clock Low to Data Out Valid 0.1 4.50.10.9µs t BUF Time the bus must be free before a new transmission can start (1) 4.7 1.2µs t HD.STA Start Hold Time 4.00.6µs t SU.STA Start Setup Time 4.70.6µs t HD.DAT Data In Hold Time 00µs t SU.DAT Data In Setup Time 200100ns t R Inputs Rise Time (1) 1.00.3µs t F Inputs Fall Time (1)300300ns t SU.STO Stop Setup Time 4.70.6µs t DH Data Out Hold Time 10050ns t WRWrite Cycle Time 55ms Endurance (1) 5.0V, 25°C, Byte Mode1M 1MWrite Cycles6AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Device OperationCLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an exter-nal device. Data on the SDA pin may change only during SCL low time periods (see Figure 4 on page 7). Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 5 on page 8).STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition.After a read sequence, the stop command will place the EEPROM in a standby power mode (see Figure 5 on page 8).ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it has received each word. This happens during the ninth clock cycle.STANDBY MODE: The AT24C01A/02/04/08A/16A features a low-power standby mode which is enabled: (a) upon power-up and (b) after the receipt of the STOP bit and the completion of any internal operations.MEMORY RESET: After an interruption in protocol, power loss or system reset, any 2-wire part can be reset by following these steps:1.Clock up to 9 cycles.2.Look for SDA high in each cycle while SCL is high.3.Create a start condition.7AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Bus TimingFigure 2. SCL: Serial Clock, SDA: Serial Data I/O ®Write Cycle TimingFigure 3. SCL: Serial Clock, SDA: Serial Data I/ONote:1.The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.Figure 4.Data Validity8AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Figure 5. Start and Stop DefinitionFigure 6.Output Acknowledge9AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Device AddressingThe 1K, 2K, 4K, 8K and 16K EEPROM devices all require an 8-bit device address word following a start condition to enable the chip for a read or write operation (refer to Figure 7).The device address word consists of a mandatory one, zero sequence for the first four most significant bits as shown. This is common to all the EEPROM devices.The next 3 bits are the A2, A1 and A0 device address bits for the 1K/2K EEPROM.These 3 bits must compare to their corresponding hard-wired input pins.The 4K EEPROM only uses the A2 and A1 device address bits with the third bit being a memory page address bit. The two device address bits must compare to their corre-sponding hard-wired input pins. The A0 pin is no connect.The 8K EEPROM only uses the A2 device address bit with the next 2 bits being for memory page addressing. The A2 bit must compare to its corresponding hard-wired input pin. The A1 and A0 pins are no connect.The 16K does not use any device address bits but instead the 3 bits are used for mem-ory page addressing. These page addressing bits on the 4K, 8K and 16K devices should be considered the most significant bits of the data word address which follows.The A0, A1 and A2 pins are no connect.The eighth bit of the device address is the read/write operation select bit. A read opera-tion is initiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address, the EEPROM will output a zero. If a compare is not made, the chip will return to a standby state.Write OperationsBYTE WRITE: A write operation requires an 8-bit data word address following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a zero and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a zero and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condi-tion. At this time the EEPROM enters an internally timed write cycle, t WR , to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 8 on page 11).PAGE WRITE: The 1K/2K EEPROM is capable of an 8-byte page write, and the 4K, 8K and 16K devices are capable of 16-byte page writes.A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to seven (1K/2K) or fifteen (4K, 8K, 16K) more data words. The EEPROM will respond with a zero after each data word received. The microcontroller must terminate the page write sequence with a stop condition (see Figure 9 on page 11).The data word address lower three (1K/2K) or four (4K, 8K, 16K) bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address,internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than eight (1K/2K) or sixteen (4K, 8K, 16K) data words are transmitted to the EEPROM, the data word address will “roll over” and previ-ous data will be overwritten.10AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06ACKNOWLEDGE POLLING: Once the internally timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a zero allowing the read or write sequence to continue.ReadOperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one. There are three read operations:current address read, random address read and sequential read.CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address “roll over” during read is from the last byte of the last memory page to the first byte of the first page.The address “roll over” during write is from the last byte of the current page to the first byte of the same page.Once the device address with the read/write select bit set to one is clocked in and acknowl-edged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input zero but does generate a following stop condi-tion (see Figure 10 on page 12).RANDOM READ: A random read requires a “dummy” byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition.The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a zero but does generate a fol-lowing stop condition (see Figure 11 on page 12).SEQUENTIAL READ: Sequential reads are initiated by either a current address read or a ran-dom address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will “roll over” and the sequential read will con-tinue. The sequential read operation is terminated when the microcontroller does not respond with a zero but does generate a following stop condition (see Figure 12 on page 12).11AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Figure 7. Device AddressFigure 8. Byte WriteFigure 9. Page Write(* = DON’T CARE bit for 1K)12AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Figure 10. Current Address ReadFigure 11. Random Read(* = DON’T CARE bit for 1K)Figure 12.Sequential Read13AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Notes:1.This device is not recommended for new design. Please refer to AT24C01B datasheet. For2.7V devices used in the 4.5V to5.5V range, please refer to performance values in the AC and DC characteristics table.2.“U” designates Green Package + RoHS compliant.3.“H” designates Green Package + RoHS compliant, with NiPdAu Lead Finish.4.Available in waffle pack and wafer form; order as SL788 for inkless wafer form. Bumped die available upon request. Pleasecontact Serial EEPROM Marketing.AT24C01A Ordering Information (1)Ordering CodePackage Operation RangeAT24C01A-10PU-2.7(2)AT24C01A-10PU-1.8(2)AT24C01A-10SU-2.7(2)AT24C01A-10SU-1.8(2)AT24C01A-10TU-2.7(2)AT24C01A-10TU-1.8(2)AT24C01A-10TSU-1.8(2)AT24C01AU3-10UU-1.8(2)AT24C01AY1-10YU-1.8(2) (Not recommended for new design)AT24C01AY6-10YH-1.8(3)8P38P38S18S18A28A25TS18U318Y18Y6Lead-free/Halogen-free/Industrial Temperature (–40°C to 85°C)AT24C01A-W1.8-11(4)Die SaleIndustrial Temperature (–40°C to 85°C)Package Type8P38-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)8Y18-lead, 4.90 mm x 3.00 mm Body, Dual Footprint, Non-leaded, Miniature Array Package (MAP)8Y68-lead, 2.00 x 3.00 mm Body, 0.50 mm Pitch, Ultra Thin Mini-MAP , Dual No Lead Package (DFN), (MLP 2x3 mm)5TS15-lead, 2.90 mm x 1.60 mm Body, Plastic Thin Shrink Small Outline Package (SOT23)8U3-18-ball, die Ball Grid Away Package (dBGA2)Options–2.7Low-voltage (2.7V to 5.5V)–1.8Low-voltage (1.8V to 5.5V)14AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Notes:1.This device is not recommended for new design. Please refer to AT24C02B datasheet. For2.7V devices used in the 4.5V to5.5V range, please refer to performance values in the AC and DC characteristics table.2.“U” designates Green Package + RoHS compliant.3.Available in waffle pack and wafer form; order as SL719 for wafer form. Bumped die available upon request. Please contactSerial EEPROM Marketing.AT24C02 Ordering Information (1)Ordering Code Package Operation RangeAT24C02-10PU-2.7(2)AT24C02-10PU-1.8(2)AT24C02N-10SU-2.7(2)AT24C02N-10SU-1.8(2)AT24C02-10TU-2.7(2)AT24C02-10TU-1.8(2)AT24C02Y1-10YU-1.8(2)AT24C02-10TSU-1.8(2)AT24C02U3-10UU-1.8(2)8P38P38S18S18A28A28Y15TS18U3-1Lead-free/Halogen-free/Industrial Temperature (–40°C to 85°C)AT24C02-W2.7-11(3)Die SaleIndustrial Temperature (–40°C to 85°C)Package Type8P38-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)8Y18-lead, 4.90 mm x 3.00 mm Body, Dual Footprint, Non-leaded, Miniature Array Package (MAP)5TS15-lead, 2.90 mm x 1.60 mm Body, Plastic Thin Shrink Small Outline Package (SOT23)8U3-18-ball, die Ball Grid Away Package (dBGA2)Options–2.7Low-voltage (2.7V to 5.5V)–1.8Low-voltage (1.8V to 5.5V)15AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Notes:1.For2.7V devices used in the 4.5V to 5.5V range, please refer to performance values in the AC and DC characteristics table.2.“U” designates Green Package + RoHS compliant.3.“H” designates Green Package + RoHS compliant, with NiPdAu Lead Finish.4.Available in waffle pack and wafer form; order as SL788 for inkless wafer form. Bumped die available upon request. Please contact Serial EEPROM Marketing.AT24C04 Ordering Information (1)Ordering CodePackage Operation RangeAT24C04-10PU-2.7(2)AT24C04-10PU-1.8(2)AT24C04N-10SU-2.7(2)AT24C04N-10SU-1.8(2)AT24C04-10TU-2.7(2)AT24C04-10TU-1.8(2)AT24C04Y1-10YU-1.8(2) (Not recommended for new design)AT24C04Y6-10YH-1.8(3)AT24C04-10TSU-1.8(2)AT24C04U3-10UU-1.8(2)8P38P38S18S18A28A28Y18Y65TS18U3-1Lead-free/Halogen-free/Industrial Temperature (–40°C to 85°C)AT24C04-W1.8-11(4)Die SaleIndustrial Temperature (–40°C to 85°C)Package Type8P38-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)8Y18-lead, 4.90 mm x 3.00 mm Body, Dual Footprint, Non-leaded, Miniature Array Package (MAP)8Y68-lead, 2.00 x 3.00 mm Body, 0.50 mm Pitch, Ultra Thin Mini-MAP , Dual No Lead Package (DFN), (MLP 2x3 mm)5TS15-lead, 2.90 mm x 1.60 mm Body, Plastic Thin Shrink Small Outline Package (SOT23)8U3-18-ball, die Ball Grid Away Package (dBGA2)Options–2.7Low-voltage (2.7V to 5.5V)–1.8Low-voltage (1.8V to 5.5V)16AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Notes:1.For2.7V devices used in the 4.5V to 5.5V range, please refer to performance values in the AC and DC characteristics table.2.“U” designates Green Package + RoHS compliant.3.“H” designates Green Package + RoHS compliant, with NiPdAu Lead Finish.4.Available in waffle pack and wafer form; order as SL788 for inkless wafer form. Bumped die available upon request. Please contact Serial EEPROM Marketing.AT24C08A Ordering Information (1)Ordering CodePackage Operation RangeAT24C08A-10PU-2.7(2)AT24C08A-10PU-1.8(2)AT24C08AN-10SU-2.7(2)AT24C08AN-10SU-1.8(2)AT24C08A-10TU-2.7(2)AT24C08A-10TU-1.8(2)AT24C08AY1-10YU-1.8(2) (Not recommended for new design)AT24C08AY6-10YH-1.8(3)AT24C08AU2-10UU-1.8(28P38P38S18S18A28A28Y18Y68U2-1Lead-free/Halogen-free/Industrial Temperature (−40°C to 85°C)AT24C08A-W1.8-11(4)Die SaleIndustrial Temperature (–40°C to 85°C)Package Type8P38-pin, 0.300" Wide, Plastic Dual Inline Package (PDIP)8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)8Y18-lead, 4.90 mm x 3.00 mm Body, Dual Footprint, Non-leaded, Miniature Array Package (MAP)8Y68-lead, 2.00 x 3.00 mm Body, 0.50 mm Pitch, Ultra Thin Mini-MAP , Dual No Lead Package (DFN), (MLP 2x3 mm)8U2-18-ball, die Ball Grid Array Package (dBGA2)Options−2.7Low Voltage (2.7V to 5.5V)−1.8Low Voltage (1.8V to 5.5V)17AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Notes:1.This device is not recommended for new design. Please refer to AT24C16B datasheet. For2.7V devices used in the 4.5V to5.5V range, please refer to performance values in the AC and DC characteristics table.2.“U” designates Green Package + RoHS compliant.3.“H” designates Green Package + RoHS compliant, with NiPdAu Lead Finish.4.Available in waffle pack and wafer form; order as SL788 for inkless wafer form. Bumped die available upon request. Pleasecontact Serial EEPROM Marketing.AT24C16A Ordering Information (1)Ordering CodePackage Operation RangeAT24C16A-10PU-2.7(2)AT24C16A-10PU-1.8(2)AT24C16AN-10SU-2.7(2)AT24C16AN-10SU-1.8(2)AT24C16A-10TU-2.7(2)AT24C16A-10TU-1.8(2)AT24C16AY1-10YU-1.8(2) (Not recommended for new design)AT24C16AY6-10YH-1.8(3)AT24C16AU2-10UU-1.8(2)8P38P38S18S18A28A28Y18Y68U2-1Lead-free/Halogen-free/Industrial Temperature (−40°C to 85°C)AT24C16A-W1.8-11(3)Die SaleIndustrial Temperature (−40°C to 85°C)Package Type8P38-pin, 0.300" Wide, Plastic Dual Inline Package (PDIP)8S18-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)8A28-lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)8Y18-lead, 4.90 mm x 3.00 mm Body, Dual Footprint, Non-leaded, Miniature Array Package (MAP)8Y68-lead, 2.00 x 3.00 mm Body, 0.50 mm Pitch, Ultra Thin Mini-MAP , Dual No Lead Package (DFN), (MLP 2x3 mm)8U2-18-ball, die Ball Grid Array Package (dBGA2)Options−2.7Low Voltage (2.7V to 5.5V)−1.8Low Voltage (1.8V to 5.5V)18AT24C01A/02/04/08A/16A0180Z–SEEPR–11/06Packaging Information8P3 – PDIP19AT24C01A/02/04/08A/16A0180Z–SEEPR–11/068S1 – JEDEC SOIC20AT24C01A/02/04/08A/16A0180Z–SEEPR–11/068A2 – TSSOP21AT24C01A/02/04/08A/16A0180Z–SEEPR–11/068Y1 – MAP22AT24C01A/02/04/08A/16A0180Z–SEEPR–11/068Y6 − Mini-MAP (MLP 2x3 mm)23AT24C01A/02/04/08A/16A0180Z–SEEPR–11/065TS1 – SOT2324AT24C01A/02/04/08A/16A0180Z–SEEPR–11/068U2 – dBGA225AT24C01A/02/04/08A/16A0180Z–SEEPR–11/068U3-1 – dBGA20180Z–SEEPR–11/06Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature© 2006 Atmel Corporation. All rights reserved. Atmel ®, logo and combinations thereof, Everywhere You Are ® and others, are registered trade-marks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

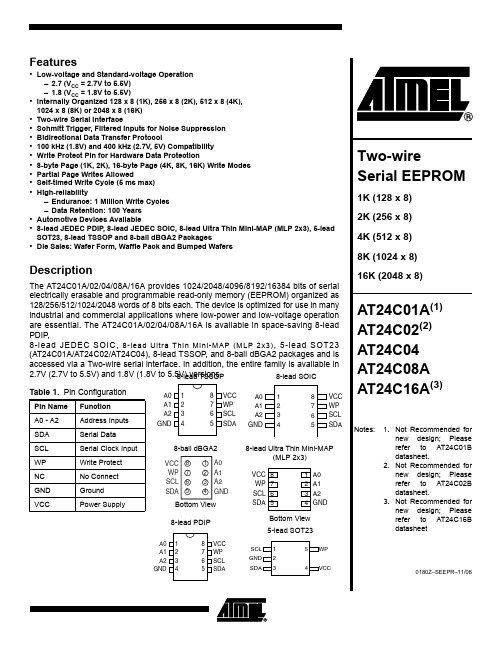

(完整word版)AT24Cxx中文数据手册

AT24C01A/02/04/08A/16A提供1024/2048/4096/8192/16384个连续的可擦除的位,以及由每8位组成一个字节的可编程只读存储器(EEPROM),其分别提供128/256/512/1024/2048个字节.该设备适用在许多低功耗和低电压操作的工业和商业应用中。

1引脚描述1.1串行时钟(SCL)SCL输入用于正向输出边缘时钟信号到每个EEPROM设备,以及每个设备输出的反向边缘时钟数据。

1.2串行数据(SDA)SDA引脚是用于串行数据双向传输。

该引脚为开漏输出,同时可以与其他开漏极或集电极开路器件进行线或.1.3设备/页地址(A2,A1,A0)对于AT24C01A和AT24C02,A2、A1和A0引脚是配置器件的硬件地址输入。

一根总线上可以连接多达八个1K / 2K的设备(器件寻址部分详细讨论了器件寻址).AT24C04使用A2和A1引脚作为硬件地址输入,在一根总线上有4个4K 的设备可用来寻址。

A0引脚没有连接。

AT24C08A只使用A2引脚作为硬件地址输入,在一根总线上有2个8K 的设备可用来寻址.A0和A1引脚没有连接。

AT24C16A不使用设备地址引脚,这限制了一根总线上只能挂一个设备。

A0、A1和A2引脚没有连接。

1.4写保护(WP)AT24C01A / 02 / 04 / 08A/ 16A有一个写保护引脚,提供硬件数据保护。

写保护引脚允许正常读/写操作时连接到GND。

当写保护引脚连接到VCC,写保护功能启用和操作如下表所示.2设备操作2.1时钟和数据转换SDA引脚通常情况下拉高.SDA引脚上的数据只能在SCL低时间段内更改,而启动条件或停止条件在SCL 为高时进行。

2.2启动条件在任何其他指令之前,SDA由高变为低,且SCL为高。

2.3停止条件SDA由低变为高,且SCL为高。

在读取序列之后,执行停止命令后EEPROM进入备用电源模式.2.4应答所有地址和数据字都是从EEPROM串行发送和接收8位字节。

IC卡24C01资料

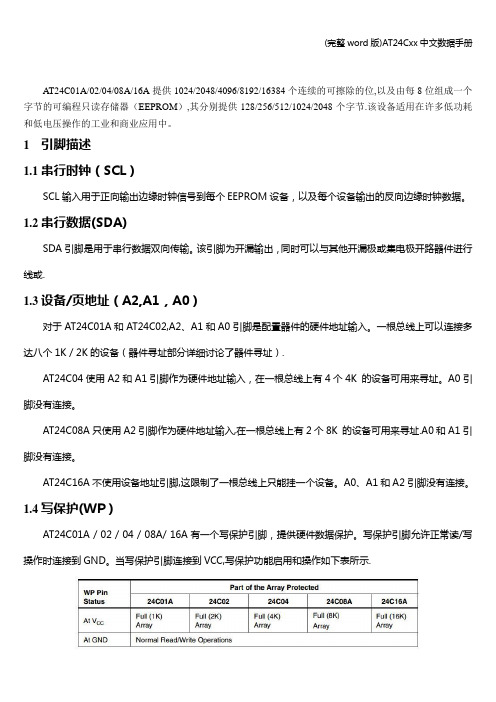

I2C总线器件应用单片机应用系统正向小型化、高可靠性、低功耗等方向发展。

在一些设计功能较多的系统中,常需扩展多个外围接口器件。

若采用传统的并行扩展方式,将占用较多的系统资源,且硬件电路复杂,成本高、功耗大、可靠性差。

为此,Philips公司推出了一种高效、可靠、方便的串行扩展总线—I2C总线。

单片机系统采用I2C总线后将大大简化电路结构,增加硬件的灵活性,缩短产品开发周期,降低成本,提高系统可靠性。

I2C总线(Inter IC BUS)是Philips推出的芯片间串行传输总线。

它以两根连线实现了完善的全双工同步数据传送,可以极方便地构成多机系统和外围器件扩展系统。

I2C总线采用了器件地址的硬件设置方法,通过软件寻址完全避免了器件的片选线寻址方法,从而使硬件系统具有最简单而灵活的扩展方法。

第一节I2C总线器件应用概述一、I2C总线器件目前许多单片机厂商引进了Philips公司的I2C总线技术,推出了许多带有I2C总线接口的单片机。

Philips公司除了生产具有I2C总线接口的单片机外,还推出了许多具备I2C总线的外部接口芯片,如24XX系列的E2PROM 、128字节的静态RAM芯片PCF8571、日历时钟芯片PCF8563、4位LED驱动芯片SAA1064、160段LCD驱动芯片PCF8576等多种类多系列接口芯片。

二、I2C总线工作原理采用I2C总线系统结构如图7-1所示。

图7-1 I2C总线系统结构图其中,SCL是时钟线,SDA是数据线。

总线上的各器件都采用漏极开路结构与总线相连,因此,SCL、SDA均需接上拉电阻,总线在空闭状态下均保持高电平。

I2C总线支持多主和主从两种工作方式,通常为主从工作方式。

在主从工作方式中,系统中只有一个主器件(单片机),总线上其它器件都是具有I2C总线的外围从器件。

在主从工作方式中,主器件启动数据的发送(发出启动信号),产生时钟信号,发出停止信号。

为了实现通信,每个从器件均有唯一一个器件地址,具体地址由I2C总线委员会分配。

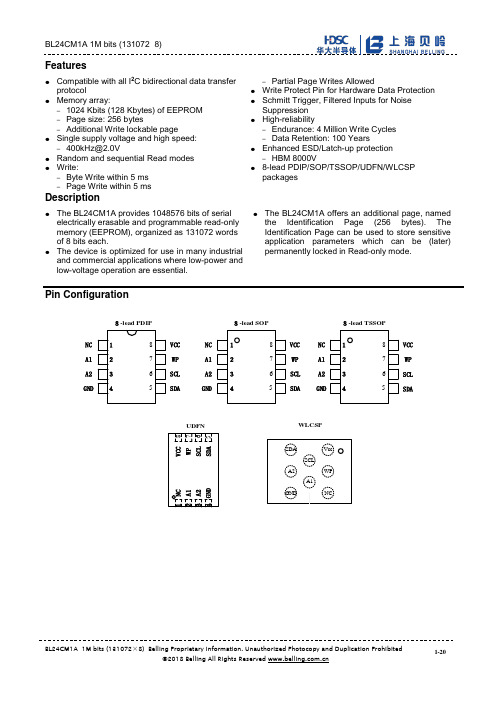

AT24C1024B 1024K EEPROM 产品说明书

Features•Low-voltage Operation–1.8V(V CC=1.8V to3.6V)–2.5V(V CC=2.5V to5.5V)•Internally Organized131,072x8•Two-wire Serial Interface•Schmitt Triggers,Filtered Inputs for Noise Suppression•Bidirectional Data Transfer Protocol•400kHz(1.8V)and1MHz(5V,2.5V)Clock Rate•Write Protect Pin for Hardware and Software Data Protection•256-byte Page Write Mode(Partial Page Writes Allowed)•Random and Sequential Read Modes•Self-timed Write Cycle(5ms Typical)•High Reliability–Endurance:1,000,000Write Cycles/Page–Data Retention:40Years•8-lead PDIP,8-lead JEDEC SOIC,8-lead EIAJ SOIC,8-lead TSSOP,8-lead Ultra Thin Small Array(SAP),and8-ball dBGA2Packages•Die Sales:Wafer Form,Tape and Reel and Bumped DieDescriptionThe AT24C1024B provides1,048,576bits of serial electrically erasable and program-mable read only memory(EEPROM)organized as131,072words of8bits each.The device’s cascadable feature allows up to four devices to share a common two-wire bus.The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential.The devices are available in space-saving8-lead PDIP,8-lead JEDEC SOIC,8-lead EIAJ SOIC,8-lead TSSOP, 8-ball dBGA2and8-lead Ultra Thin SAP packages.In addition,the entire family is available in1.8V(1.8V to3.6V)and2.5V(2.5V to5.5V)versions.8-lead PDIP12348765NCA1A2GNDVCCWPSCLSDA8-lead TSSOP12348765VCCWPSCLSDANCA1A2GND8-lead SOIC12348765NCA1A2GNDVCCWPSCLSDA8-lead Ultra-Thin SAPBottom ViewVCCWPSCLSDANCA1A2GND123487658-lead dBGA2Bottom ViewVCCWPSCLSDANCA1A2GND1234876525194F–SEEPR–1/08AT24C1024B1.Absolute Maximum Ratings**NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings”may cause permanent dam-age to the device.This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied.Exposure to absolute maximum rating conditions for extended periods may affect device reliability.35194F–SEEPR–1/08AT24C1024BFigure 1-1.Block Diagram2.Pin DescriptionSERIAL CLOCK (SCL):The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA):The SDA pin is bi-directional for serial data transfer.This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.DEVICE/ADDRESSES (A1/A2):The A1,A2pin is a device address input that can be hardwired or left not connected for hardware compatibility with other AT24Cxx devices.When the A1,A2pins are hardwired,as many as four 1024K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section).If the A1/A2pins are left floating,the A1/A2pin will be internally pulled down to GND if the capacitive coupling to the circuit board V CC plane is <3pF.If coupling is >3pF,Atmel recommends connecting the A1/A2pin to GND.WRITE PROTECT (WP):The write protect input,when connected to GND,allows normal write operations.When WP is connected high to V CC ,all write operations to the memory are inhibited.If the pin is left floating,the WP pin will be internally pulled down to GND if the capacitive cou-pling to the circuit board V CC plane is <3pF.If coupling is >3pF,Atmel recommends connecting the pin to GND.Switching WP to V CC prior to a write operation creates a software write-protectfunction.VCC GND WP SCL SDAA 2A 1A 045194F–SEEPR–1/08AT24C1024B3.Memory OrganizationAT24C1024B,1024K SERIAL EEPROM:The 1024K is internally organized as 512pages of 256bytes each.Random word addressing requires a 17-bit data word address.IL IH Table 3-1.Pin Capacitance (1)Table 3-2.DC CharacteristicsTable 3-3.AC Characteristics (Industrial Temperature)Applicable over recommended operating range from T AI =-40︒C to +85︒C,V CC =+1.8V to +3.6V,CL =100pF (unless oth-55194F–SEEPR–1/08AT24C1024B2.AC measurement conditions:R L (connects to V CC ):1.3k Ω(2.5V,5V),10k Ω(1.8V)Input pulse voltages:0.3V CC to 0.7V CC Input rise and fall times:≤50nsInput and output timing reference voltages:0.5V CC4.Device OperationCLOCK and DATA TRANSITIONS:The SDA pin is normally pulled high with an external device.Data on the SDA pin may change only during SCL low time periods (see Figure 4-4on page 7).Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION:A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 4-5on page 8).Table 3-3.AC Characteristics (Industrial Temperature)Applicable over recommended operating range from T AI =-40︒C to +85︒C,V CC =+1.8V to +3.6V,CL =100pF (unless oth-65194F–SEEPR–1/08AT24C1024BSTOP CONDITION:A low-to-high transition of SDA with SCL high is a stop condition.After a read sequence,the Stop command will place the EEPROM in a standby power mode (see Fig-ure 4-5on page 8).ACKNOWLEDGE:All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words.The EEPROM sends a zero during the ninth clock cycle to acknowl-edge that it has received each word.STANDBY MODE:The AT24C1024B features a low-power standby mode which is enabled:a)upon power-up and b)after the receipt of the stop bit and the completion of any internal operations.SOFTWARE RESET:After an interruption in protocol,power loss or system reset,any 2-wire part can be protocol reset by following these steps:(a)Create a start bit condition,(b)clock 9cycles,(c)create another start bit followed by stop bit condition as shown below.The device is ready for next communication after above steps have been completed.Figure 4-1.Software ResetFigure 4-2.Bus Timing (SCL:Serial Clock,SDA:Serial Data I/O ®)SCLSDASCLSDA INSDA OUT75194F–SEEPR–1/08AT24C1024BFigure 4-3.Write Cycle Timing (SCL:Serial Clock,SDA:Serial Data I/O)Note:1.The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.Figure 4-4.DataValiditySTOP CONDITIONSTART CONDITIONSCLSDASDASCLDAT A STABLEDAT A STABLEDAT A CHANGE85194F–SEEPR–1/08AT24C1024BFigure 4-5.Start and Stop DefinitionFigure 4-6.Output Acknowledge5.Device AddressingThe 1024K EEPROM requires an 8-bit device address word following a start condition to enable the chip for a read or write operation (see Figure 7-1on page 11).The device address word con-sists of a mandatory one,zero sequence for the first four most significant bits as shown.This is common to all two-wire EEPROM devices.The 1024K uses the two device address bit,A1,A2,to allow up to four devices on the same bus.These A1,A2bits must compare to the corresponding hardwired input pins.The A1,A2pin uses an internal proprietary circuit that biases it to a logic low condition if the pin is allowed to float.The seventh bit (P 0)of the device address is a memory page address bit.This memory page address bit is the most significant bit of the data word address that follows.The eighth bit of the device address is the read/write operation select bit.A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address,the EEPROM will output a zero.If a compare is not made,the device will return to astandby state.SDASCLSTART STOPSCLDAT A INDAT A OUTSTART ACKNOWLEDGE98195194F–SEEPR–1/08AT24C1024BDATA SECURITY:The AT24C1024B has a hardware data protection scheme that allows the user to write-protect the entire memory when the WP pin is at V CC .6.Write OperationsBYTE WRITE:To select a data word in the 1024K memory requires a 17-bit word address.The word address field consists of the P 0bit of the device address,then the most significant word address followed by the least significant word address (see Figure 7-2on page 11)A write operation requires the P 0bit and two 8-bit data word addresses following the device address word and acknowledgment.Upon receipt of this address,the EEPROM will again respond with a zero and then clock in the first 8-bit data word.Following receipt of the 8-bit data word,the EEPROM will output a zero.The addressing device,such as a microcontroller,then must terminate the write sequence with a stop condition.At this time the EEPROM enters an internally timed write cycle,T WR ,to the nonvolatile memory.All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 7-2on page 11).PAGE WRITE:The 1024K EEPROM is capable of 256-byte page writes.A page write is initiated the same way as a byte write,but the microcontroller does not send a stop condition after the first data word is clocked in.Instead,after the EEPROM acknowledges receipt of the first data word,the microcontroller can transmit up to 255more data words.The EEPROM will respond with a zero after each data word received.The microcontroller must ter-minate the page write sequence with a stop condition (see Figure 7-3on page 11).The data word address lower 8bits are internally incremented following the receipt of each data word.The higher data word address bits are not incremented,retaining the memory page row location.When the word address,internally generated,reaches the page boundary,the follow-ing byte is placed at the beginning of the same page.If more than 256data words are transmitted to the EEPROM,the data word address will “roll over”and previous data will be overwritten.The address “rollover”during write is from the last byte of the current page to the first byte of the same page.ACKNOWLEDGE POLLING:Once the internally timed write cycle has started and the EEPROM inputs are disabled,acknowledge polling can be initiated.This involves sending a start condition followed by the device address word.The read/write bit is representative of the operation desired.Only if the internal write cycle has completed will the EEPROM respond with a zero,allowing the read or write sequence to continue.7.Read OperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one.There are three read operations:current address read,random address read and sequential read.CURRENT ADDRESS READ:The internal data word address counter maintains the last address accessed during the last read or write operation,incremented by one.This address stays valid between operations as long as the chip power is maintained.The address “rollover”during read is from the last byte of the last memory page,to the first byte of the first page.105194F–SEEPR–1/08AT24C1024BOnce the device address with the read/write select bit set to one is clocked in and acknowledged by the EEPROM,the current address data word is serially clocked out.The microcontroller does not respond with an input zero but does generate a following stop condition (see Figure 7-4on page 11).RANDOM READ:A random read requires a “dummy”byte write sequence to load in the data word address.Once the device address word and data word address are clocked in and acknowledged by the EEPROM,the microcontroller must generate another start condition.The microcontroller now initiates a current address read by sending a device address with the read/write select bit high.The EEPROM acknowledges the device address and serially clocks out the data word.The microcontroller does not respond with a zero but does generate a follow-ing stop condition (see Figure 7-5on page 12).SEQUENTIAL READ:Sequential reads are initiated by either a current address read or a ran-dom address read.After the microcontroller receives a data word,it responds with an acknowledge.As long as the EEPROM receives an acknowledge,it will continue to increment the data word address and serially clock out sequential data words.When the memory address limit is reached,the data word address will “roll over”and the sequential read will continue.The sequential read operation is terminated when the microcontroller does not respond with a zero,but does generate a following stop condition (see Figure 7-6on page 12).115194F–SEEPR–1/08AT24C1024BFigure 7-1.Device AddressFigure 7-2.Byte WriteFigure 7-3.Page WriteFigure 7-4.Current AddressReadSIGNIFICANTMOSTSIGNIFICANTLEAST125194F–SEEPR–1/08AT24C1024BFigure 7-5.Random ReadFigure 7-6.Sequential Read135194F–SEEPR–1/08AT24C1024BNotes: 1.“-B”denotes bulk2.“-T”denotes tape and reel.SOIC =4K per reel.TSSOP and dBGA2=5K per reel.SAP =3K per reel.EIAJ =2K per reel.3.Available in tape and reel and wafer form;order as SL788for inkless wafer form.Bumped die available upon request.Pleasecontact Serial Interface Marketing.Ordering Information145194F–SEEPR–1/08AT24C1024B8.Part marking scheme8.18-SOIC(1.8V)8.28-SOIC(2.5V)TOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L H Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 152 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L H Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 252 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom Mark155194F–SEEPR–1/08AT24C1024B8.38-TSSOP(1.8V)8.48-TSSOP(2.5V)TOP MARKPin 1 Indicator (Dot)Y = SEAL YEAR WW = SEAL WEEK |6: 2006 0: 2010 02 = Week 2 |---|---|---|---| 7: 2007 1: 2011 04 = Week 4 * H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 1 50 = Week 50 |---|---|---|---|---| 52 = Week 52BOTTOM MARK|---|---|---|---|---|---|---| P H|---|---|---|---|---|---|---| A A A A A A A |---|---|---|---|---|---|---| <- Pin 1 IndicatorTOP MARKPin 1 Indicator (Dot)Y = SEAL YEAR WW = SEAL WEEK |6: 2006 0: 2010 02 = Week 2 |---|---|---|---| 7: 2007 1: 2011 04 = Week 4 * H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 2 50 = Week 50 |---|---|---|---|---| 52 = Week 52BOTTOM MARK|---|---|---|---|---|---|---| P H|---|---|---|---|---|---|---| A A A A A A A |---|---|---|---|---|---|---| <- Pin 1 Indicator165194F–SEEPR–1/08AT24C1024B8.58-PDIP(1.8V)8.68-PDIP(2.5V)8.78-Ultra Thin SAP (1.8V)TOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L U Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 152 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L U Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 252 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal Year| Seal Week Y = SEAL YEARWW = SEAL WEEK | | |6: 2006 0: 2010 02 = Week 2 |---|---|---|---|---|---|---|---| 7: 2007 1: 2011 04 = Week 4 A T M L H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 150 = Week 50 |---|---|---|---|---|---|---|---| 52 = Week 52Lot Number|---|---|---|---|---|---|---|---| * |Pin 1 Indicator (Dot)175194F–SEEPR–1/08AT24C1024B8.88-Ultra Thin SAP (2.5V)8.9dBGA2TOP MARKSeal Year| Seal Week Y = SEAL YEARWW = SEAL WEEK | | |6: 2006 0: 2010 02 = Week 2 |---|---|---|---|---|---|---|---| 7: 2007 1: 2011 04 = Week 4 A T M L H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 250 = Week 50 |---|---|---|---|---|---|---|---| 52 = Week 52Lot Number|---|---|---|---|---|---|---|---| * |Pin 1 Indicator (Dot)TOP MARKLINE 1-------> 2GBU LINE 2-------> PYMTC|<-- Pin 1 This CornerP = COUNTRY OF ORIGINY = ONE DIGIT YEAR CODE 4: 2004 7: 20075: 2005 8: 20086: 2006 9: 2009M = SEAL MONTH (USE ALPHA DESIGNATOR A-L) A = JANUARY B = FEBRUARY " " """"""" J = OCTOBER K = NOVEMBER L = DECEMBERTC = TRACE CODE (ATMEL LOT NUMBERS TO CORRESPONDWITH ATK TRACE CODE LOG BOOK)185194F–SEEPR–1/08AT24C1024B9.Packaging Information 8P3–PDIP195194F–SEEPR–1/08AT24C1024B8S1-JEDEC SOIC205194F–SEEPR–1/08AT24C1024B8S2–EIAJ SOICAT24C1024B 8A2-TSSOP2122AT24C1024B8U4-1-dBGA2AT24C1024B 8Y7–SAP2324AT24C1024B10.Revision HistoryHeadquarters InternationalAtmel Corporation 2325Orchard Parkway San Jose,CA95131 USATel:1(408)441-0311 Fax:1(408)487-2600Atmel AsiaRoom1219Chinachem Golden Plaza77Mody Road TsimshatsuiEast KowloonHong KongTel:(852)2721-9778Fax:(852)2722-1369Atmel EuropeLe Krebs8,Rue Jean-Pierre TimbaudBP30978054Saint-Quentin-en-Yvelines CedexFranceTel:(33)1-30-60-70-00Fax:(33)1-30-60-71-11Atmel Japan9F,Tonetsu Shinkawa Bldg.1-24-8ShinkawaChuo-ku,Tokyo104-0033JapanTel:(81)3-3523-3551Fax:(81)3-3523-7581Product ContactWeb SiteTechnical Support******************Sales Contact/contactsLiterature Requests/literatureDisclaimer:The information in this document is provided in connection with Atmel products.No license,express or implied,by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products.EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE,ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS,IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING,BUT NOT LIMITED TO,THE IMPLIED WARRANTY OF MERCHANTABILITY,FITNESS FOR A PARTICULAR PURPOSE,OR NON-INFRINGEMENT.IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT,INDIRECT,CONSEQUENTIAL,PUNITIVE,SPECIAL OR INCIDEN-TAL DAMAGES(INCLUDING,WITHOUT LIMITATION,DAMAGES FOR LOSS OF PROFITS,BUSINESS INTERRUPTION,OR LOSS OF INFORMATION)ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT,EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice.Atmel does not make any commitment to update the information contained herein.Unless specifically provided otherwise,Atmel products are not suitable for,and shall not be used in,automotive applications.Atmel’s products are not intended,authorized,or warranted for use as components in applications intended to support or sustain life.©2008Atmel Corporation.All rights reserved.Atmel®,logo and combinations thereof,are registered trademarks or trademarks of Atmel Cor-poration or its subsidiaries.Other terms and product names may be trademarks of others.。

AT24C01

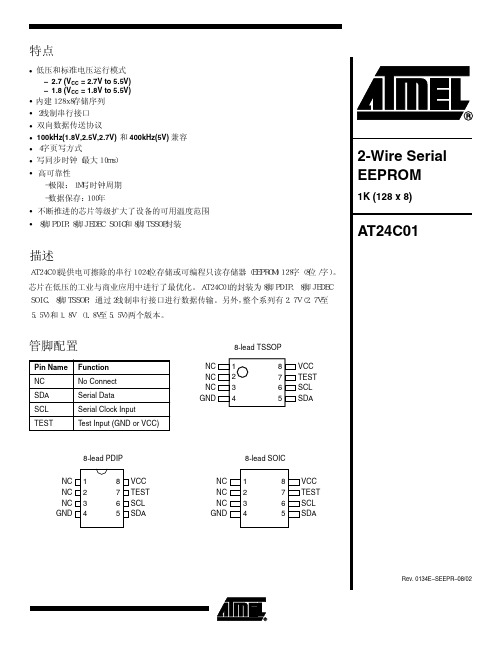

1•–2.7(V CC =2.7V to 5.5V)–1.8(VCC =1.8V to 5.5V)•••••••••8-lead PDIP 8-lead SOIC8-lead TSSOP特点低压和标准电压运行模式内建128x8存储序列2线制串行接口双向数据传送协议100kHz(1.8V,2.5V,2.7V)400kHz(5V)和兼容4字页写方式写同步时钟(最大10ms)高可靠性-极限:1M写时钟周期-数据保存:100年不断推进的芯片等级扩大了设备的可用温度范围8脚PDIP,8脚JEDEC SOIC和8脚TSSOP封装描述AT24C01提供电可擦除的串行1024位存储或可编程只读存储器(EEPROM)128字(8位/字)。

芯片在低压的工业与商业应用中进行了最优化。

AT24C01的封装为8脚PDIP、8脚JEDEC SOIC、8脚TSSOP,通过2线制串行接口进行数据传输。

另外,整个系列有2.7V(2.7V至5.5V)和1.8V (1.8V至5.5V)两个版本。

管脚配置2AT24C010134E –SEEPR –08/02°C to +125°C °C to +150°C?最大额定值运行温度............................-55存储温度............................-65管脚耐压...............................-1.0Vto+7.0V 6.25V 最大工作电压.................................5.0mA直流输出电流................................结构图*注意:超出左边的“最大额定值”表列出的值使用可能会造成芯片永久损坏,这些仅仅是额定值,并不是说芯片必须在此环境下运行或部分超出额定值。

芯片长期在最大额定值下运行可能会影响可靠性。

24CXX

3: VCC <2.5V,频率为 400 kHz。

4: MSOP 型封装 24XX128 和 24XX256 器件的引脚 A0 和 A1 没有连接。

5: P = 8-PDIP,SN = 8-SOIC (150 mil JEDEC),ST = 8-TSSOP,OT = 5 或 6-SOT23,MC = 2x3mm DFN, MS = 8-MSOP, SM = 8-SOIC (200 mil EIAJ),MF = 5x6mm DFN, ST14 = 14-TSSOP。

1.8-5.5V 2.5-5.5V 1.8-5.5V

400 kHz (2)

400 kHz 1 MHz(3)

64 字节

整个阵列

A0, A1, A2(4)

I

P, SN, SM, ST, MS, MF,

I, E ST14

I

256 千位器件

24AA256

1.8-5.5V 400 kHz (2)

24LC256 24FC256

2005 Microchip Technology Inc.

DS21930A_CN 第 3 页

24AAXX/24LCXX/24FCXX

2.0 电气特性

绝对最大额定值 (†)

VCC.............................................................................................................................................................................6.5V 相对于 Vss 的所有输入和输出 ............................................................................................................ -0.6V 到 VCC +1.0V 存储温度 ................................................................................................................................................. -65°C 到 +150°C 环境温度 (使用电源时)........................................................................................................................ -40°C 到 +125°C 所有引脚静电保护 ....................................................................................................................................................................≥ 4 kV

AT24C02中文手册

主要特性

� � � 工作电压:1.8V~5.5V 输入/输出引脚兼容 5V 应用在内部结构: 128x8(1K),256x8(2K),512x8(4K),1024x8(8K),2048x8(16K) � � � � � � 二线串行接口 输入引脚经施密特触发器滤波抑制噪声 双向数据传输协议 兼容 400KHz(1.8V,2.5V,2.7V,3.6V ) 支持硬件写保护 高可靠性:读写次数:1,000,000 次 – 数据保存:100 年

(WP) 引脚: 24C01/02/04/08/16 具有用于硬件数据写保护功能的引脚。当该引脚接 GND 时,允许正常 写保护 写保护(WP) (WP)引脚: 引脚:24C01/02/04/08/16 的读/写操作。当该引脚接 VCC 时,芯片启动写保护功能。

器件操作

时钟及数据传输:SDA 引脚通常被外围器件拉高。SDA 引脚的数据应在 SCL 为低时变化;当数据在 SCL 为高 时变化,将视为下文所述的一个起始或停止命令。 起始命令:当 SCL 为高,SDA 由高到低的变化被视为起始命令,必须以起始命令作为任何一次读/写操作命令 的开始(参见图 5)。 停止命令:当 SCL 为高,SDA 由低到高的变化被视为停止命令,在一个读操作后,停止命令会使 EEPROM 进 入等待态低功耗模式(参见图 5)。 应答:所有的地址和数据字节都是以 8 位为一组串行输入和输出的。每收到一组 8 位的数据后,EEPROM 都 会在第 9 个时钟周期时返回应答信号。每当主控器件接收到一组 8 位的数据后,应当在第 9 个时钟周期向 EEPROM 返回一个应答信号。收到该应答信号后,EEPROM 会继续输出下一组 8 位的数据。若此时没有得到主 控器件的应答信号,EEPROM 会停止读出数据,直到主控器件返回一个停止命令来结束读周期。 24C01/02/04/08/16 特有一个低功耗的等待模式。可以通过以下方法进入该模式:(a)上电 ()收 等待模式: 等待模式:24C01/02/04/08/16 到停止位并且结束所有的内部操作后。 在 器件复位:在协议中断、下电或系统复位后,器件可通过以下步骤复位:(1)连续输入 9 个时钟;(2) 每个时钟周期中确保当 SCL 为高时 SDA 也为高;(3)建立一个起始条件。

24c01程序控制及原理图