计算机组成原理+常用集成芯片型号及引脚图

常用电子器件管脚排列图

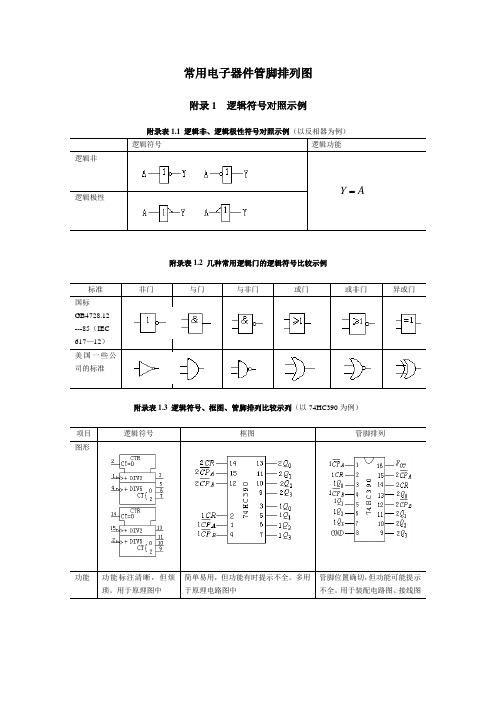

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例)附录2 集成电路1. 集成电路命名方法集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍集成电路IC 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与CMOS 集成电路的注意事项(1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

附录图 2.1双列直插式集成电路的引脚排列②电路的各输入端不能直接与高于V 5.5+和低于V 5.0-的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。

如果将集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到CC V 端。

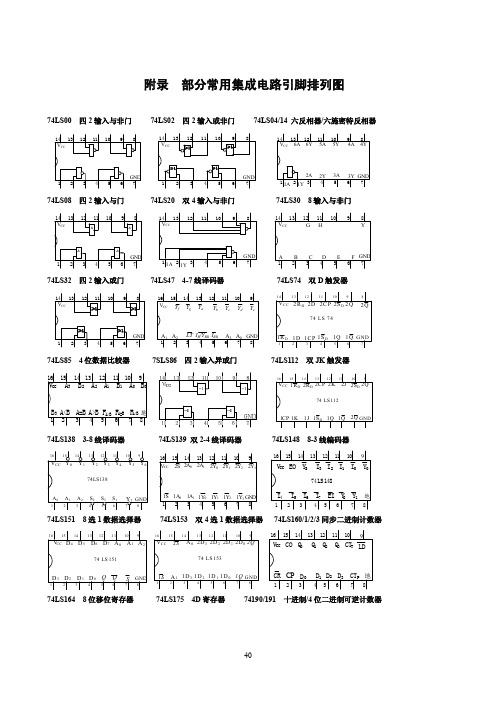

部分常用数字集成电路引脚排列图

部分常用数字集成电路引脚排列图

四2输入与非门六反向器

74LS0074LS04

三3输入与非门双4输入与非门74LS1074LS20

4线至7段译码器/驱动器4路2-3-3-2输入与非门74LS4874LS54

双上升沿D触发器4位D型锁存器

74LS7474LS75

双下降沿JK触发器四2输入异或门

74LS7674LS86

十进制计数器4位二进制计数器

74LS9074LS93

3线—8线译码器双4选1数据选择器74LS13874LS153

十进制同步计数器(异步清除)4位二进制同步计数器(异步清除)74LS16074LS161

4位二进制超前进位全加器

74LS283

四2输入与非门双4输入与非门

CC4011CC4012

四R-S锁存器(3S)六反相器CC4043CC4069

四2输入与门双定时器

CC4081CC7556

定时器

CC7555

注:CMOS电路(CC*)引脚排列图中的VDD和VSS等同于TTL电路(74LS*)引脚排列图中的VCC和GND。

常用芯片引脚图

附录三常用芯片引脚图一、 单片机类1、MCS-51芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。

MCS-51系列单片机共有40条引脚,包括32条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。

引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。

P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。

P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。

P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。

ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号)PSEN :片外程序存储器开发信号引脚(输出信号)EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚RST/VPD :复位/备用电源引脚2、MCS-96芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单片机系列。

它含有比较丰富的软、硬件资源,适用于要求较高的实时控制场合。

它分为48引脚和68引脚两种,以48引脚居多。

引脚说明:RXD/P2.1 TXD/P2.0:串行数据传出分发送和接受引脚,同时也作为P2口的两条口线HS1.0~HS1.3:高速输入器的输入端HS0.0~HS0.5:高速输出器的输出端(有两个和HS1共用)Vcc :主电源引脚(+5V )Vss :数字电路地引脚(0V )Vpd :内部RAM 备用电源引脚(+5V )V REF :A/D 转换器基准电源引脚(+5V )12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7EA/V PP ALE/PROG PSENP2.7/A 15P2.6/A 14P2.5/A 13P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751AGND:A/D转换器参考地引脚XTAL1、XTAL2:内部振荡器反相器输入、输出端,常外接晶振。

系列芯片引脚图及逻辑功能表

系列芯片引脚图及逻辑

功能表

Document serial number【NL89WT-NY98YT-NC8CB-NNUUT-NUT108】

74LS11——3输入端3与门管脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门

74LS54——4-2-3与或非门

74LS08——2输入4与门。

74LS系列IC管脚图大全

74LS390 双十进制计数器

74LS624 压控振荡器

74LS625 压控振荡器

74LS626 压控振荡器

74LS627 压控振荡器

74LS628 压控振荡器

74LS629 压控振荡器

两片74LS283构成的8位加法器

74LS289 64位随机存取存储器

74LS289 64位随机存取存储器

74LS290异步2—5—10进制计数器

74LS290异步2—5—10进制计数器

74LS292 可编程分频器/数字定时器

74LS293 4位二进制计数器

74LS294 16位可编程模块

74LS374 八D触发器(三态同相)

74381

符号

A0 A1 A2 A3

B0 B1 B2 B3

C -1

S0 S1 S2

引脚排列

A 1 1 20 VCC

F0

B1

A2

F1

A0

B2

F2

B0

F3

S0

A3 B3

7 43 81

S1

C -1

S2

P

P

F0

G

G

F1

F3

GND 1 0 1 1 F 2

74LS381算术逻辑单元

74LS181 算术逻辑单元/功能发生器

74LS181 四位算术逻辑运算器

7 4 18 2

G 1 1 16 V cc

P1

P2

G0

G2

P0

C -1

G3

C0

P3

C1

P

G

G ND 8 9 C 2

74LS182先行进位发生器/超前进位产生器

VCC 2Ai 2Bi 2Ci-1 2Ci 2Si VCC2A 2B 2CIn 2COn+1 2F 74LS183 1COn+1 1A 1B 1CIn 1F GND 1Ai 1Bi 1Ci-1 1Ci 1Si 地

常用芯片引脚图

您的数字ID 是:463099您的密码是:1.8667附录三常用芯片引脚图一、 单片机类1、MCS-51芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。

MCS-51系列单片机共有40条引脚,包括32条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。

引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。

P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。

P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。

P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。

ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号)PSEN :片外程序存储器开发信号引脚(输出信号)EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚RST/VPD :复位/备用电源引脚2、MCS-96芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单片机系列。

它含有比较丰富的软、硬件资源,适用于要求较高的实时控制场合。

它分为48引脚和68引脚两种,以48引脚居多。

引脚说明:RXD/P2.1 TXD/P2.0:串行数据传出分发送和接受引脚,同时也作为P2口的两条口线HS1.0~HS1.3:高速输入器的输入端HS0.0~HS0.5:高速输出器的输出端(有两个和HS1共用)Vcc :主电源引脚(+5V )Vss :数字电路地引脚(0V )Vpd :内部RAM 备用电源引脚(+5V )V REF :A/D 转换器基准电源引脚(+5V )AGND :A/D 转换器参考地引脚XTAL1、XTAL2:内部振荡器反相器输12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7EA/V PP ALE/PROG PSENP2.7/A 15P2.6/A 14P2.5/A 13P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751入、输出端,常外接晶振。

常用集成电路管脚和功能表

74LS190的外引线图

74LS190的逻辑符号

31

主菜单 开 始 回 退 前 进 最 后 返 退 回2020作/6/1?5 业 出

74LS190功能表

32

2020/6/15

集成二进制同步可逆计数器74LS191

74LS191的外引线图

33

74LS191的逻辑符号

2020/6/15

74LS191功能 FA>BFA<BFA = B

100 010 100 010 100 010 100 010 100 010 001 001

2020/6/15

集成JK触发器74LS112

集成JK触发器74LS112 (a) 外引脚图 (b) 逻辑符号

15

2020/6/15

34

2020/6/15

双时钟集成十进制同步可逆计数器74LS192

74LS192的外引线图

35

74LS192的逻辑符号

2020/6/15

74LS192功能表

36

2020/6/15

双时钟4位二进制同步可逆计数器74LS193

74LS193的外引线图

37

74LS193的逻辑符号

2020/6/15

74LS193功能表

74LS112的功能表

16

2020/6/15

集成双D触发器74LS74

1. 双D触发器74LS74外引脚图和逻辑符号

图4-27 双D触发器74LS74

(a) 外引脚图 (b)逻辑符号

17

2020/6/15

双D触发器74LS74的功能表

18

2020/6/15

集成数码锁存器74LS373

8D型锁存器74LS373

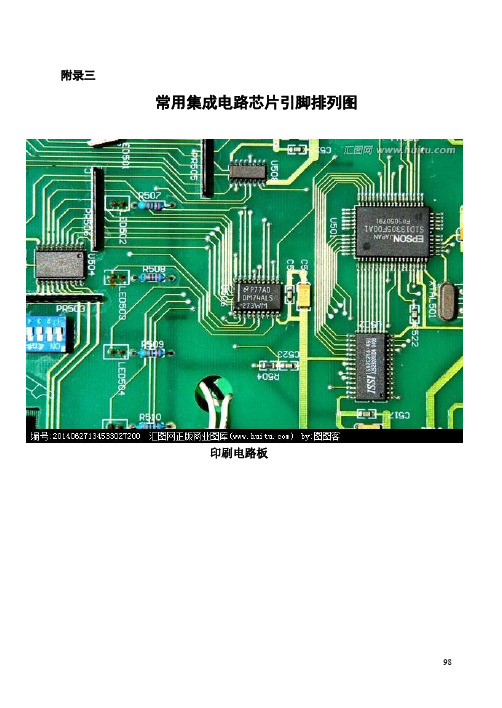

集成电路引脚图

附录三常用集成电路芯片引脚排列图印刷电路板贴片封装芯片双列直插式封装74LS00 74LS03Y=AB四2输入正与非门Y=AB集电极开路输出的四2输入正与非门74LS0474LS08Y=A六反相器Y=AB 四2输入正与门74LS10 74LS11Y=ABC三3输入正与非门Y=ABC 三3输入正与门74LS2074LS21Y=ABCD双4输入正与非门Y=ABCD双4输入正与门74LS32 74LS48测试Y=A+B 四2输入正或门BCD-七段译码器74LS48是具有内部上拉电阻的BCD-七段译码器/驱动器。

输出高电平有效,其中,A、B、C、D是输入端,a、b、c、d、e、f是输出。

74LS51 74LS74Y=CDAB+与或非门双D型正边沿触发器74LS8674LS90CP2Y=A⊕B 四2输入异或门十进制计数器(2、5分频)74LS90是四位十进制计数器。

各有两个置“0”(R01、R02)和置“9”(R91、R92)输入端,有两个计数输入端A和B,Q A-Q D为输出。

若从A端输入计数脉冲,将Q A与B短接,则组成十进制计数器(分频器);若从B端输入计数脉冲,把Q D与A短接,则组成二~五混合进制计数器(或五分频器)74LS112 74LS125双J -K 负边沿触发器(带预置和清除端) Y=A 三态输出的四总线缓冲门 EN 为高时禁止74LS13874LS153输出选择允许输出数据输入选通选择输出3-8线译码器/分配器 双4-1线数据选择器/多路开关 74LS138为3-8线译码器,包含三个允许输入端S 1、2S 、3S ,可对8条线中任意一条进行译码,这取决于三个二进制选择输入端A 0、A 1、A 2和三个允许输入端S 1、2S 、3S 的状态。

74LS160 74LS180数据输入输出4位同步计数器(十进制,直接清除) 9位奇/偶校验器/发生器74LS175 74LS183输入输入输出四D 型触发器(互补输出,共直接清除) 双保留进位全加器74LS183全加器每一位有一个单独的进位输出,它可在多输入保留进位方法中使用,能在不大于两级门的延时内产生真和、真进位输出。

芯片引脚图及引脚描述

芯片引脚图及引脚描述文档编制序号:[KKIDT-LLE0828-LLETD298-POI08]555芯片引脚图及引脚描述555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。

1脚为地。

2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。

当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平;2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。

6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。

3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。

4脚是复位端,当4脚电位小于时,不管2、6脚状态如何,输出端3脚都输出低电平。

5脚是控制端。

7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。

555集成电路管脚,工作原理,特点及典型应用电路介绍.1 555集成电路的框图及工作原理555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。

但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。

此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。

由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图1所示。

常用集成电路引脚排列图

A0 A1 A2 S2 S3 S1

1

2

3

4

56

Y7 GND

78

74LS151 8 选 1 数据选择器

16 15 14 13 12 11 10 9 VCC 2S 2A0 2A1 2Y0 2Y1 2Y2 2Y3

1S 1A0 1A1 1Y0 1Y1 1Y2 1Y3 GND 12345678

74LS153 双 4 选 1 数据选择器

VCC 1RD 2RD 2CP 2K 2J 2SD 2Q 74 LS 112

1CP 1K 1J 1SD 1Q 1Q 2Q GND

74LS138 38 线译码器

74LS139 双 24 线译码器

74LS148 83 线编码器

16 15 14 13 12 11 10 9

VCC Y0 Y1 Y2 Y3 Y4 Y5 Y6

14 13 12 11 10 9 8

VCC 2CP 2 CR 2 Q 0 2 Q1 2Q2 2 Q3

1C P 1 CR 1Q 0 1Q 1 1 Q 2 1 Q 3 地

1234

56

7

14 13 12 11 10 9 8

VDD

≥1

≥1

≥1

≥1

GND

1234567

CC4011 74LS02 四 2 输入与非门 CC4012 双 4 输入与非门 CC4013 双 D 触发器

12 3 45 6 78

A B C D E F GND 1234567

74LS74 双 D 触发器

14

13 12

11

10

9

8

VCC 2RD 2D 2CP 2S D 2Q 2Q

74 LS 74

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

X

X X

L L…. . .L

QA0QBO... QHO

H QAn...QGn

L QAn...QGn

H

L

X X

H

↑

H H

H

↑

L X

H

↑

X L

L QAn...QGn

74LS183双保存全加器功能表

输入

输出

Cn B A

ΣCn+1

L L L

L L

L L H

H L

L H L

H L

L H H

L H

H L L

H L

H L H

L H

H H L

L H

H H H

H H

74LS244 8位缓冲器及线驱动器

2114RAM管脚图功能表

CS

R/W

I/O

工作

模式

A0~A9

地址

1

X

高阻

不选中

CS

片选

0

0

0

写0

R/W

读/写

0

0

1

写1

I/00~I/03

数据

入/出

0

1

Dout

读出

VDD

正电源

VSS

地

74LS181四位算术逻辑运算器

附录2常用集成芯片型号及引脚图

74LS00二输入四与非门74LS04六反向器

74LS08二输入四与门74LS20四输入双与非门

74LS30 8输入与非门74LS32 2输入四或门

74LS51 2-2 3-3输入双与或非门

74LS74双D触发器74LS86二输入四异或门

输入

输出

PR CLR C1 1D

X

X X X X

QA0QB0QC0QD0

↓

L L

X

X X X X

QA0QB0QC0QD0

↓

L H

X

X X X X

QA0QB0QC0QD0

↑

H L

X

X X X X

QA0QB0QC0QD0

↑

H H

X

X X X X

QA0QB0QC0QD0

74LS138 3线-8线译 码器

74LS151 8选1数据选择器功能表

74LS153双四选一数据选择器功能表

输入

选择

数据输入

选通

输入

输出

B A

C0 C1 C2 C3

G1

Y1

X X

X X X X

1

0

0 0

C0 X X X

0

C0

0 1

X C1 X X

0

C1

1 0

X X C2 X

0

C2

1 1

X X X C3

0

C3

7

74LS164 8位移位寄存器

功能表

输入

输出

清零

时钟

A B

QAQB... QHAFra bibliotekB C DQAQBQCQD

H

H X

X

X X X X

QA0QB0QC0QD0

H

↓X

X

a b c d

a b c d

H

↓X

X

QE+QC+QD+d

QBnQCnQDnd

L

LH

X

X X X X

QA0QB0QC0QD0

L

X↓

H

X X X X

H QAnQBnQCn

L

X↓

L

X X X X

L QAnQBAQCn

↑

L L

L H X X

H L X X

L L X X

H H↑H

H H↑L

H H L X

H L

L H

H H

H L

L H

74LS74双D触发器功能表74LS86二输入四异或门功能表

输入

输出

A B

Y

L L

L H

H L

H H

L

H

H

L

74LS95四位移位寄存器74LS95功能表

输入

输出

方式

控制

时钟

2(L)1(R)

串行

并行