EP2C35F672C6sopc实验

vhdl BCD码加法器

实验一BCD码加法器一、实验目的了解BCD 码的构成。

了解BCD 码加法器的原理和设计实现方法。

巩固Quartus II 的使用。

二、实验内容与要求通过键盘输入两组4BIT的二进制数据,按照二进制加法器原理进行加和,求出和合进位,并通过电路静态数码LED显示灯输出显示,完成编译、综合、适配、仿真、实验箱上的硬件测试。

三、实验平台(1)硬件:计算机、GX-SOC/SOPC-DEV-LABCycloneII EP2C35F672C8核心板(2)软件:Quartus II四、实验原理BCD码是二进制编码的十进制码,也就是用4位二进制数来表示十进制中的0~9这十个数。

由于4位二进制数有0000~1111共16种组合,而十进制数只需对应4位二进制数的10种组合,故从4位二进制数的16种组合中取出10种组合来分别表示十进制中的0~9,则有许多不同的取舍方式,于是变形成了不同类型的BCD码。

当BCD码相加的值小于等于9时,结果仍旧是正确的BCD码;当两个码相加的结果大于9时,必须作加6的修正处理,对于大于19的值作加12的修正处理,对于大于29的值作加18的修正处理。

然后根据仿真进行实验及验证。

六、仿真截图七、硬件实现八、程序代码1LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY f_ADDER IsPort (x: In Std_Logic;y: In Std_Logic;cin: In Std_Logic;cout: Out Std_Logic;sum: Out Std_Logic);END f_ADDER;ARCHITECTURE fd1 Of f_ADDER Is Component HADDERPort( a,b: In Std_Logic;co,so: Out Std_Logic);END Component;Component oraPort(a,b: In Std_Logic;c: Out Std_Logic);END Component;Signal d,e,f: Std_Logic;BeginU1: HADDERPort Map(a=>X,b=>Y,Co=>d,so=>e);U2:HADDERPort Map(a=>e,b=>cin,Co=>f,so=>sum);U3:ora Port Map(a=>d,b=>f,c=>cout);END ARCHITECTURE fd1;2LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY HADDER IsPort (a,b: In Bit;Co, So: Out Bit);END HADDER;ARCHITECTURE fh1 Of HADDER Is BEGINSo <= (a Xor b);Co <= (a And b);END fh1;3LIBRARY Ieee;USE Ieee.Std_Logic_1164.all;ENTITY ora IsPort ( a: in Std_Logic;b: in Std_Logic;c: out Std_Logic);END ora;ARCHITECTURE org OF ora ISBEGINc <= a Or b;END org;4Library ieee;Use ieee.std_logic_1164.all;Entity Qadd isPort (a:in std_logic_VECTOR(7 DOWNTO 0);b:in std_logic_VECTOR(7 DOWNTO 0);--cin:in std_logic;s:out std_logic_VECTOR(7 DOWNTO 0));End Qadd;Architecture one of Qadd isSignal c0,c1,c2,c3,c4,c5,c6,c7 : std_logic;Component f_ADDERPort (x: In Std_Logic;y: In Std_Logic;cin: In Std_Logic;cout: Out Std_Logic;sum: Out Std_Logic);END Component;Beginu1 :F_ADDERPort map(sum=>s(0),cout=>c0,X=>a(0),Y=>b(0),cin=>'0'); u2 :F_ADDERPort map(sum=>s(1),cout=>c1,X=>a(1),Y=>b(1),cin=>c0 ); u3 : F_ADDERPort map(sum=>s(2),cout=>c2,X=>a(2),Y=>b(2),cin=>c1 ); u4 : F_ADDERPort map(sum=>s(3),cout=>c3,X=>a(3),Y=>b(3),cin=>c2 ); u5 : F_ADDERPort map(sum=>s(4),cout=>c4,X=>a(4),Y=>b(4),cin=>c3 ); u6 : F_ADDERPort map(sum=>s(5),cout=>c5,X=>a(5),Y=>b(5),cin=>c4 ); u7 :F_ADDERPort map(sum=>s(6),cout=>c6,X=>a(6),Y=>b(6),cin=>c5 ); u8 : F_ADDERPort map(sum=>s(7),cout=>c7,X=>a(7),Y=>b(7),cin=>c6 ); END;九、实验总结。

基于FPGA的洗衣机控制系统设计

基于FPGA的洗衣机控制系统设计郭忠;李涛;李勇;张勇【摘要】To improve the performance of household binocular washing machines control system, timing accuracy and washing effect, a control system for washing machines based on FPGA is designed and timing simulation is carried out in this paper. So, the design is further ideal. Digital control and display of washing machine control system has been available, and the washing performance has been effectively improved.%为提高家用双缸洗衣机控制系统的性能,改善定时精确度和洗涤效果,基于可编程性强的FPGA设计了一种用于洗衣机的控制系统,并进行了时序仿真。

通过实验对设计方案进行了完善,得到了可进行数字化控制和显示的洗衣机控制系统。

有效地提高了洗衣机性能。

【期刊名称】《电子设计工程》【年(卷),期】2012(020)013【总页数】3页(P190-192)【关键词】控制理论与控制工程;FPGA;洗衣机控制系统;Quartus;Ⅱ;NiosⅡ【作者】郭忠;李涛;李勇;张勇【作者单位】泰山医学院,山东泰安271000;空军工程大学工程学院,陕西西安710038;泰山医学院,山东泰安271000;泰山医学院,山东泰安271000【正文语种】中文【中图分类】P242.6随着时代的发展,洗衣机已成为人们日常生活中的必需品。

目前全自动单筒、滚筒洗衣机已日渐盛行,但其结构复杂,日常维修和购买时成本偏高,所以结构简单、价格实惠的双缸洗衣机依然受到普通大众的欢迎。

QuartusII学习总结

QuartusII学习总结目录一、FPGA简介二、SOPC简介三、Quartus9.1安装过程及破解四、文本编辑五、原理图编辑六、混合编辑(方波应用实例)一、FPGA简介1.1 FPGA的定义FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

1.2 FPGA的现状中国每年对于FPGA设计人才的需求缺口巨大,FPGA设计人才的薪水也是行业内最高的。

目前,美国已有FPGA人才40多万,中国台湾地区也有7万多,而中国内地仅有1万左右,可见中国渴望有更多的FPGA人才涌现出来。

FPGA(现场可编程逻辑器件)产品的应用领域已经从原来的通信扩展到消费电子、汽车电子、工业控制、测试测量等广泛的领域。

而应用的变化也使FPGA产品近几年的演进趋势越来越明显:一方面,FPGA供应商致力于采用当前最先进的工艺来提升产品的性能,降低产品的成本;另一方面,越来越多的通用IP(知识产权)或客户定制IP被引入FPGA中,以满足客户产品快速上市的要求。

此外,FPGA 企业都在大力降低产品的功耗,满足业界越来越苛刻的低功耗需求。

1.3 FPGA的发展趋势分析(1)规模越来越大,集成度越来越高。

早期的FPGA规模只有几千门,2006年5月份,Xilinx公司推出世界上第一个65nm FPGA系列——Virtex-5。

基于65nm三极栅氧化层技术、11层铜布线工艺、低K材料、新型镍硅自对准技术、新型ExpressFabric技术和ASMBL架构,可以提供330 000个逻辑单元(可编程逻辑门约660万门)和1 200个用户I/O。

(2)速度不断提高,性能不断提升。

Xilinx 2006年推出的Virtex-5 LX 性能和利用率都很高,同时功耗大幅度降低。

quturs ii操作

Quartus II软件操作基础本章介绍Altera公司的Quartus II6.0版本软件的使用方法作为EDA实训设计的基础。

通过本章的学习读者可初步采用Quartus II 软件的原理图输入法和HDL文本输入法来设计数字电路和系统并掌握用EDA实训仪设计电路进行硬件验证的方法。

uartus II是Altera公司近几年推出的新一代、功能强大的可编程逻辑器件设计环境至今已公布了6.0以上版本。

Quartus II 软件提供了SOPC设计的综合开发环境是SOPC设计的基础。

Quartus II集成环境支持系统级设计、嵌入式系统设计和可编程器件设计的设计输入、编译、综合、布局、布线、时序分析、仿真、编程下载等EDA设计过程。

Quartus II支持多种编辑输入法包括图形编辑输入法VHDL、Verilog HDL和AHDL的文本编辑输入法符号编辑输入法以及内存编辑输入法。

下面以Quartus II6.0版本为例介绍Quartus II软件的基本操作。

2.1 Quartus II软件的安装Quartus II6.0版本设计软件的安装比较简单只要把Quartus II6.0设计软件光盘放入计算机的光驱中安装光盘将自动引导完成Quartus II6.0的安装。

但软件安装结束之后还必须在软件中指定Altera公司的授权文件License.dat才能正常使用Quartus II软件。

在Windows 2000或Windows XP系统下指定授权文件的操作步骤如下① 打开Windows窗口下的“控制面板”用鼠标左键双击控制面板上的“系统”图标或用鼠标右键点击“我的电脑”在弹出的对话框中选择“属性”在弹出的“系统特性”对话框中展开“高级”页面如图2.1所示。

用鼠标左键点击该页面上的“环境变量”按钮弹出如图2.2所示的“环境变量”对话框。

在环境变量对话框中点击“XXX的用户变量”XXX为用户PC机名栏目下的“新建”按钮弹出“新建用户变量”对话框见图2.2中所示。

sopc课程设计

SoPC课程设计(报告)题目:液晶控制显示器学院:电子工程学院系部:微电子学系专业:集成电路设计与集成系统班级: 1002 学生姓名:曹松松指导教师:曾泽沧起止时间: 2013年6月17日——2013年6月28日目录1 课程设计要求 (2)基本要求 (2)2 实验使用平台 (2)3 题目:选题2 (2)4 课程设计总结 (5)5 附件 (5)1课程设计要求基本要求课程设计要求所有题目采用Quartus II 工具提供的图形输入或者VerilogHDL语言输入方式作为电路设计工具,在NiosII上采用C语言实现编程,自定向下正向设计方法,先设计硬件系统,再进行软件编程,能够生成正确的FPGA下载代码和NiosII执行的软件代码。

硬件功能仿真和时序仿真采用第三方工具(建议为:modelsim),综合与布局布线工具为:Quartus II,SOPC Builder建立软件运行环境,具体要求为:1)根据课设题目,进行总体设计方案(10分);2)硬件电路顶层设计、模块划分、引脚定义(10分);3)电路设计及NiosII设计,提交电路设计源代码或电路图(10分);4)综合与布局布线,提交综合与布局布线报告(10分);5)FPGA下载代码和引脚分布(10分);6)软件总体设计及画出流程图(10分);7)程序设计,提交程序代码(10分);8)程序编译下载及仿真调试(10分)。

2实验使用平台实验平台使用Altera的DE2开发板,开发工具使用Altera的Quartus II和Nios II IDE。

3 题目:选题2在字符型液晶显示器上移动显示“XIAN UNIVERSITY POST AND TELECOMMUNICATIONS YOUR NAME 2013-6”,要求FPGA 设计硬件,内嵌NiosII,液晶显示采用软件实现。

1)根据课设题目,进行总体设计方案;(10分)此次sopc课程设计选题2,题目相对比较简单。

EDA技术实训_DE2使用教程

Altera DE2 使用教程电子信息科学与技术系目录DE2开发板资源: (3)FPGA简要介绍 (5)Quaturs使用基础 (7)用HDL写代码 (22)管脚的输入方式 (25)NIOSII 实验 (25)FAQ (36)DE2开发板资源:Table. DE2 Board InformationFPGA•Cyclone II EP2C35F672C6 with EPCS16 16-Mbit serial configuration deviceI/O Devices•Built-in USB-Blaster TM cable for FPGA configuration•10/100 Ethernet•RS232•Video out (VGA 10-bit DAC)•Video in (NTSC/PAL/multi-format)•USB 2.0 (type A and type B)•PS/2 mouse or keyboard port•Line in/out, microphone in (24-bit Audio CODEC)•Expansion headers (76 signal pins)•Infrared portMemory•8-MBytes SDRAM, 512K SRAM, 4-MBytes flash•SD memory card slotDisplays•16 x 2 LCD display•Eight 7-segment displaysSwitches and LEDs•18 toggle switches•18 red LEDs•9 green LEDs•Four debounced push-button switchesClocks•50-MHz crystal for FPGA clock input•27-MHz crystal for video applications•External SMA clock input可以在目前开发板上做的实验包括基本的VHDL以及Verilog HDL实验接口实验高级实验NIOS II CPU 实验开发套件清单1DE2开发板一个2ByteBlasterII 下载电缆1根35v电源一个4光盘一张FPGA简要介绍FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。

实验七 SOPC 基础实验

实验七SOPC 基础实验SOPC即System-On-a-Programmable-Chip(可编程片上系统),本章通过一系列的实验,使学习者对SOPC的应用有较为深刻的认识,并对FPGA的仿真与设计环境有深入的了解,为进一步的工作奠定基础。

7.1 SOPC概述SOPC是PLD和ASIC技术融合的结果,它是一种特殊的嵌入式系统。

首先它是片上系统(SOC),即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

由于FPGA无论在逻辑门密度还是在运行频率等诸多方面都取得了长足进步,基于FPGA的嵌入式系统成为SOPC的热点。

目前已经可以把处理器软核、ASIC硬核、数字信号处理器件以及网络控制等各种数字逻辑控制器以IP核的形式集成到FPGA芯片里,构成嵌入式系统。

7.2 基本硬件设计实验嵌入式开发环境EDK是用于设计嵌入式处理系统的集成软件,是利用嵌入式PowerPC™硬处理器核和/或Xilinx MicroBlaze™软处理器核进行Xilinx平台FPGA设计时所需的全部技术文档和IP。

EDK包括硬件部分和软件部分:1. 硬件部分:Xilinx Platform Studio (XPS)XPS是设计嵌入式处理器系统硬件部分的开发环境和用户图形界面。

可使用底层系统生成器BSB(Base System Builder )创建XPS工程,BSB能够快速和有效地创建工程设计。

Xilinx推荐使用BSB向导来创建任何新的嵌入式设计工程,BSB能够满足你所有设计的需要,并且可以帮助你节省很多时间。

使用BSB创建XPS的过程如下:创建顶层工程文件(*.xmp File)选择板型选择和配置处理器选择和配置多重I/O口添加内部的外围设备设置软件观看系统摘要页2. 软件部分:Software Development Kit (SDK)SDK是综合的开发环境,是对XPS的补充,可用C/C++进行嵌入式软件应用的编写和验证。

数字电路与数字逻辑实验指导书-DE2版本

数字电路与数字逻辑实验指导书目录实验一:Quartus II软件操作 (3)实验二:数据选择器和译码器功能验证 (15)实验三:数据选择器和译码器应用 (18)实验四:触发器的应用 (20)实验五:计数器的功能验证 (22)实验六:计数器的应用 (23)实验七:寄存器的功能验证 (24)附录:................................................................................ 错误!未定义书签。

实验一:Quartus II软件操作实验目的和要求:1、了解并掌握QuartusII软件的使用方法。

2、了解并掌握仿真(功能仿真及时序仿真)方法及验证设计正确性。

3、了解并掌握EDA QuartusII中的原理图设计方法。

实验内容:本实验通过简单的例子介绍FPGA开发软件QuartusII的使用流程,包括图形输入法的设计步骤和仿真验证的使用以及最后的编程下载。

图形编辑输入法也称为原理图输入设计法。

用Quartus II的原理图输入设计法进行数字系统设计时,不需要了解任何硬件描述语言知识,只要掌握数字逻辑电路基本知识,就能使用QuartusII提供的EDA平台设计数字电路或系统。

QuartusII的原理图输入设计法可以与传统的数字电路设计法接轨,即把传统方法得到的设计电路的原理图,用EDA平台完成设计电路的输入、仿真验证和综合,最后编程下载到可编程逻辑器件(FPGA/CPLD)或专用集成电路(ASIC)中。

实验步骤:在QuartusII中通过原理图的方法,使用与门和异或门实现半加器。

第1步:打开QuartusII软件。

第2步:新建一个空项目。

选择菜单File->New Project Wizard,进入新建项目向导。

如下图所示,填入项目的名称“hadder”,默认项目保存路径在Quartus安装下,也可修改为其他地址,视具体情况而定。

王晓阳基于DE2实验板的存储器实验

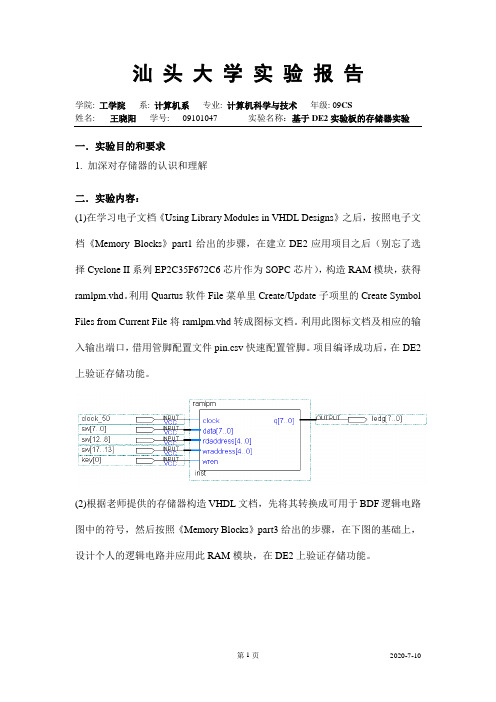

汕头大学实验报告学院: 工学院系: 计算机系专业: 计算机科学与技术年级: 09CS姓名: 王晓阳学号: 09101047 实验名称:基于DE2实验板的存储器实验一.实验目的和要求1. 加深对存储器的认识和理解二.实验内容:(1)在学习电子文档《Using Library Modules in VHDL Designs》之后,按照电子文档《Memory Blocks》part1给出的步骤,在建立DE2应用项目之后(别忘了选择Cyclone II系列EP2C35F672C6芯片作为SOPC芯片),构造RAM模块,获得ramlpm.vhd。

利用Quartus软件File菜单里Create/Update子项里的Create Symbol Files from Current File将ramlpm.vhd转成图标文档。

利用此图标文档及相应的输入输出端口,借用管脚配置文件pin.csv快速配置管脚。

项目编译成功后,在DE2上验证存储功能。

(2)根据老师提供的存储器构造VHDL文档,先将其转换成可用于BDF逻辑电路图中的符号,然后按照《Memory Blocks》part3给出的步骤,在下图的基础上,设计个人的逻辑电路并应用此RAM模块,在DE2上验证存储功能。

(3)根据老师提供的VHDL文档,按照《Memory Blocks》part4给出的步骤,在下图的基础上,通过设计个人的逻辑电路,应用DE2板上的SRAM芯片。

(4) 电子文档《Memory Blocks》给出的其它实验内容(选做部分)三、实验记录及分析(1)Project1a) 实验逻辑电路图experiment2-1实验逻辑电路图b) 实验结果记录将00000010写入地址为11000的内存中从地址为11000的内存中读出数据,结果为00000010c) 实验结果分析SW17~SW13为5位的写入地址,SW12~SW8为5位读数据的内存地址,SW7~SW0为8位的输入数据,KEY0为读入控制,每按一次写入一次。

EDA技术与VHDL实验指导书

EDA技术与VHDL实验指导书电气中心实验室编制2011-9前言《EDA技术与VHDL实验指导书》是与理论课程《EDA技术与VHDL》配套开出的,是电子信息工程等专业的一门专业选修课程,对电子信息工程等专业的学生具有非常重要的作用。

本实验课与理论课同时进行,与理论课有着较密切的联系。

因此学生在做本实验之前必须具备1.一定的C语言基础;2.电路与电子技术的基础知识;3.计算机辅助设计的基本操作能力;4.理论联系实践的自学能力。

学生学习完本实验课后,应具有1.能熟练使用Quartus II等EDA开发工具软件;2.掌握CPLD/FPGA芯片的基本使用方法,能用现代数字系统的设计方法进行基本的数字系统设计;3.掌握图形编辑和VHDL文本编辑两种设计方法,重点是VHDL文本编辑;4.具备基本的开发能力,为后续学习打下坚实的基础等方面能力。

从70 年代第一片可编程逻辑器件PROM的诞生到现在的CPLD/FPGA,数字系统的设计发生了本质的变化。

基于CPLD/FPGA和EDA(电子设计自动化)工具进行数字系统的设计与开发。

它代表了数字电信领域的最高水平,给数字电路的设计带来了革命性的变化。

从传统的对电路板的设计到现在的基于芯片的设计,使得数字系统设计的效率大大提高,产品更新速度大大加快,设计周期大大变短。

所以本科生学习本课程有着非常重要的意义。

本实验不同于其它实验,其实验手段和实验方法都有重大的变化,要求实验前提交预习报告,检查通过后方可实验,设计与综合实验环节。

本实验是在PC 平台上,用原理图或文本进行输入,然后进行编译,通过之后再进行波形仿真,如有缺陷,对源文件进行修改。

利用ISP技术、采用EDA工具、应用PLD 器件,在PC及EDA开发平台上进行。

实验一组合逻辑电路设计实验学时:3学时实验类型:验证实验要求:必做一、实验目的1.熟练掌握QuartusII开发工具软件;2.掌握门电路VHDL语言程序设计方法;3.掌握选择器VHDL语言程序设计方法;4.掌握加法器VHDL语言程序设计方法;5.熟悉VHDL编程的基本方法;二、实验原理1.二输入与门二输入与门是我们数字电路中的一个基础逻辑门电路,是最基本的逻辑门电路之一,也是最简单的逻辑门之一。

基于FPGA的语音录制与回放系统

基于FPGA的语音录制与回放系统曾繁政;王明娟;曲艺;李立礼【摘要】系统用FPGA实现了I2C总线控制器,以Altera公司的NiosⅡ嵌入式软处理器为核心,结合高品质数字信号音频编/解码芯片WM8731成功地实现了语音的录制及回放功能,同时利用Matlab 7.0.4软件对所采集的语音数据进行仿真.系统采用SoPC技术,自行设计采集模块和I2C协议驱动模块,并通过AWALON总线挂载在Nios软核上实时高速采集与回放.实践表明,系统具有集成度高,稳定性好,实时性强的特点.【期刊名称】《现代电子技术》【年(卷),期】2010(033)016【总页数】3页(P66-68)【关键词】SoPC;FPGA;I2C总线;WM8731【作者】曾繁政;王明娟;曲艺;李立礼【作者单位】贺州学院,广西,贺州,542800;钦州学院,广西,钦州,535000;钦州学院,广西,钦州,535000;贺州学院,广西,贺州,542800【正文语种】中文【中图分类】TN495-340 引言随着微电子技术的发展,系统集成向高速、高集成度、低功耗发展已经成为必然,同时SoPC技术也应用而生。

SoPC将软硬件集成于单个可编程逻辑器件平台,使得系统设计更加简洁灵活。

SoPC综合了SoC,PLD和FPGA的优点,集成了硬核和软核CPU、OSP、存储器、外围I/O及可编程逻辑,用户可以利用SoPC平台自行设计高速、高性能的CPU和DSP处理器,使得电子系统设计进入一个崭新的模式[1-10]。

该设计运用SoPC技术实现嵌入式数字化语音录制与回放。

其中,介绍了在FPGA 上构建WM8731的I2C总线,以及数字化语音在SRAM中的存储, 并利用Matlab 7.0.4软件对所采集的语音数据进行仿真。

SoPC是现在电子技术、电子系统设计的汇聚点和发展方向。

充分体现了其高性能、设计灵活和易用等特点。

1 系统整体方案系统以Altera公司的FPGA 芯片(Cyclone Ⅱ系列)EP2C35F672C6NK为平台,结合音频编/解码芯片WM8731实现语音录制与回放。

DE2开发板指导手册

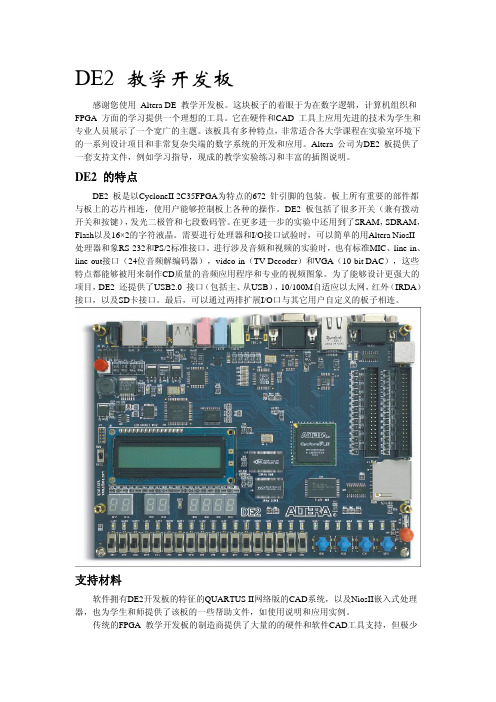

DE2 教学开发板感谢您使用 Altera DE 教学开发板。

这块板子的着眼于为在数字逻辑,计算机组织和FPGA 方面的学习提供一个理想的工具。

它在硬件和CAD 工具上应用先进的技术为学生和专业人员展示了一个宽广的主题。

该板具有多种特点,非常适合各大学课程在实验室环境下的一系列设计项目和非常复杂尖端的数字系统的开发和应用。

Altera 公司为DE2 板提供了一套支持文件,例如学习指导,现成的教学实验练习和丰富的插图说明。

DE2 的特点DE2 板是以CycloneII 2C35FPGA为特点的672 针引脚的包装。

板上所有重要的部件都与板上的芯片相连,使用户能够控制板上各种的操作。

DE2 板包括了很多开关(兼有拨动开关和按键),发光二极管和七段数码管。

在更多进一步的实验中还用到了SRAM,SDRAM,Flash以及16×2的字符液晶。

需要进行处理器和I/O接口试验时,可以简单的用Altera NiosII处理器和象RS-232和PS/2标准接口。

进行涉及音频和视频的实验时,也有标准MIC、line-in、line-out接口(24位音频解编码器),video-in(TV Decoder)和VGA(10-bit DAC),这些特点都能够被用来制作CD质量的音频应用程序和专业的视频图象。

为了能够设计更强大的项目,DE2 还提供了USB2.0 接口(包括主、从USB),10/100M自适应以太网,红外(IRDA)接口,以及SD卡接口。

最后,可以通过两排扩展I/O口与其它用户自定义的板子相连。

支持材料软件拥有DE2开发板的特征的QUARTUS II网络版的CAD系统,以及NiosII嵌入式处理器,也为学生和师提供了该板的一些帮助文件,如使用说明和应用实例。

传统的FPGA 教学开发板的制造商提供了大量的的硬件和软件CAD工具支持,但极少提供直接面向教学目的的帮助文件。

但Altera 公司的DE2 板别树一帜,除了DE2 板的硬件和软件外,Aletra 公司也为一些典型的逻辑设计课程和计算机组织提供了全套的能够在实验室条件下实现的实验练习。

DE2 2.0 Quartus使用实例

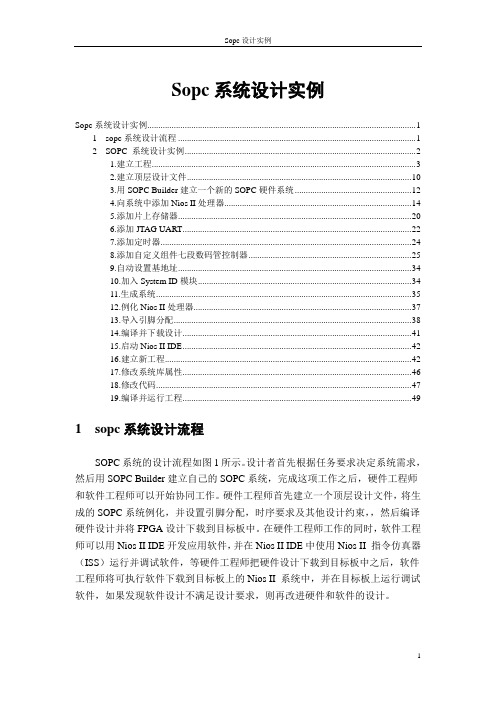

Sopc系统设计实例Sopc系统设计实例 (1)1 sopc系统设计流程 (1)2 SOPC 系统设计实例 (2)1.建立工程 (3)2.建立顶层设计文件 (10)3.用SOPC Builder建立一个新的SOPC硬件系统 (12)4.向系统中添加Nios II处理器 (14)5.添加片上存储器 (20)6.添加JTAG UART (22)7.添加定时器 (24)8.添加自定义组件七段数码管控制器 (25)9.自动设置基地址 (34)10.加入System ID模块 (34)11.生成系统 (35)12.例化Nios II处理器 (37)13.导入引脚分配 (38)14.编译并下载设计 (41)15.启动Nios II IDE (42)16.建立新工程 (42)17.修改系统库属性 (46)18.修改代码 (47)19.编译并运行工程 (49)1 sopc系统设计流程SOPC系统的设计流程如图1所示。

设计者首先根据任务要求决定系统需求,然后用SOPC Builder建立自己的SOPC系统,完成这项工作之后,硬件工程师和软件工程师可以开始协同工作。

硬件工程师首先建立一个顶层设计文件,将生成的SOPC系统例化,并设置引脚分配,时序要求及其他设计约束,,然后编译硬件设计并将FPGA设计下载到目标板中。

在硬件工程师工作的同时,软件工程师可以用Nios II IDE开发应用软件,并在Nios II IDE中使用Nios II 指令仿真器(ISS)运行并调试软件,等硬件工程师把硬件设计下载到目标板中之后,软件工程师将可执行软件下载到目标板上的Nios II 系统中,并在目标板上运行调试软件,如果发现软件设计不满足设计要求,则再改进硬件和软件的设计。

图1 sopc系统设计流程2 SOPC 系统设计实例用SOPC系统在DE2平台上实现一个计数器。

先在DE2平台上建立SOPC 系统的硬件,这个系统包括一个NIos II/s 嵌入式处理器、存储器、一个JTAG UART及一个定时器,一个ID模块。

Qsys范例程序

Qsys范例程序一、跑马灯打开Quartus II,出现如下界面新建一个工程,选择File->New Project Wizard,出现以下界面选择Next > ,出现以下对话框给新工程命名并选择工程目录,本例使用RunningLED作为工程名。

点击两次Next >,出现如下对话框在Family中选择Cyclone II,Available devices中选择EP2C35F672C6,为我们使用的FPGA芯片型号。

然后点击Finish,至此就建立好了新工程。

再点击Quartus II软件右上方工具栏的,打开Qsys程序。

本例将建立一个包含CPU核、8kB片上RAM、一个定时器和8个IO口的最小片上系统以演示跑马灯程序。

Qsys 启动后界面如下:首先在系统中添加片上RAM。

在程序左侧列表中选择Memory and Memory Controllers -> On-Chip -> On-Chip Memory (RAM or ROM),双击添加至系统中。

在弹出的对话框中指定片上RAM的属性。

设置内存大小为8192Byte。

再添加CPU。

双击Embedded Processors-> Nios II Processor,在弹出的对话框中间选择第一个Nios II/e,表示economy,最小的NIOS II核心。

其它的都保留默认设置即可。

点击Finish添加CPU核。

添加定时器。

在列表中选择Peripherals -> Microcontroller Peripherals -> Interval Timer,弹出如下对话框。

定时器在本系统中主要作用是产生一个固定间隔的中断信号,让CPU改变LED灯的状态。

因此在Period中选择500ms,表示灯的状态每500ms改变一次。

在右侧Library中双击Simple periodic interrupt。

FPGA,学习心得体会

篇一:fpga学习心得大报告《fpga技术基础》学习报告--课程内容学习心得姓名:学号:年级专业:指导教师:瞿麟 201010401128 自动化101薛小军摘要从开始学fpga到现在粗略算来的话,已经有3个多月了,就目前而言,我并不确定自己算不算高手们所说的入门了,fpga学习总结。

但是不管现在的水平如何,现在就总结一下自己学习它的感受或一些认识吧。

关键词fpga de2板 quartusii软件 verilog语言引言fpga是什么?fpga现状?怎样学习fpga?fpga是现场可编程门阵列的简称,fpga的应用领域最初为通信领域,但目前,随着信息产业和微电子技术的发展,可编程逻辑嵌入式系统设计技术已经成为信息产业最热门的技术之一,应用范围遍及航空航天、医疗、通讯、网络通讯、安防、广播、汽车电子、工业、消费类市场、测量测试等多个热门领域。

并随着工艺的进步和技术的发展,向更多、更广泛的应用领域扩展。

越来越多的设计也开始以asic转向fpga, fpga正以各种电子产品的形式进入了我们日常生活的各个角落。

正文(1)掌握fpga的编程语言在学习一门技术之前我们往往从它的编程语言开始,如同学习单片机一样,我们从c语言开始入门,当掌握了c语言之后,开发单片机应用程序也就不是什么难事了。

学习fpga也是如此,fpga的编程语言有两种:vhdl和verilog,这两种语言都适合用于fpga的编程。

(2)fpga实验尤为重要除了学习编程语言以外,更重要的是实践,将自己设计的程序能够在真正的fpga里运行起来,这时我们需要选一块板子进行实验,我们选择使用de2板才进行试验。

初识de2开发板de2的资源de2的资源非常丰富,包括1. 核心的fpga芯片-cyclone ii 2c35 f672c6,从名称可以看出,它包含有35千个le,在altera的芯片系列中,不算最多,但也绝对够用。

altera下载控制芯片- epcs16以及usb-blaste对jtag的支持。

干涉合成孔径声纳的信号源系统设计

干涉合成孔径声纳的信号源系统设计洪琳琅;刘海华;袁利;陈军波【摘要】In order to achieve Interference synthetic aperture sonar systemto the special requirements of the signal source, this paper presents a FPGA-based SOPC technology implementations, the signal provided to the transmitter analog signal on the one hand, returned to the echo signal acquisition system clock and sync signal in order to ensure consistency of the signal system time, as well as to the receiver signal to achieve time-varying gain compensation for attenuation of the echo signal; the other hand, also real-time collection and transmission system in the underwater sonar motion attitude, depth, pressure and other information; through lake test and sea trials, the signal source system to complete the analog signal and digital signal indicators test , satisfy the design requirements.%为达到干涉合成孔径声纳系统对信号源的特殊要求,提出了一种基于SOPC技术的FPGA实现方法,该信号源一方面提供给发射机模拟信号,还给回波信号采集系统提供时钟和同步信号以保证信号系统时间一致性,同时还给接收机的时变增益信号实现对回波信号衰减的补偿;另一方面还实时采集并传输声纳系统在水下的运动姿态、深度、压力等信息;经过湖试和海试,该信号源系统完成了模拟信号和数字信号各项指标的测试,满足设计要求.【期刊名称】《计算机测量与控制》【年(卷),期】2012(020)001【总页数】4页(P212-215)【关键词】干涉合成孔径声纳;SOPC;FPGA【作者】洪琳琅;刘海华;袁利;陈军波【作者单位】中南民族大学生物医学工程学院,湖北武汉430074;中南民族大学生物医学工程学院,湖北武汉430074;海军工程大学电子工程学院,湖北武汉430033;中南民族大学生物医学工程学院,湖北武汉430074;中南民族大学生物医学工程学院,湖北武汉430074【正文语种】中文【中图分类】TN790 引言干涉合成孔径声纳系统(InSAS)用于水下目标的探测和识别,由水上控制处理机部分和水下拖体两大部分组成,其中水下拖体包含:信号源、采集卡、接收机、发射机和传感器等。

FPGA开发板

/shop_view.asp?id=50产品浏览红色飓风II代-Altera版开发板品牌:Red Cyclone现在现货订购39次,浏览9000次开发板价格:699元开发板原价:699元不打折E 币支付:不可用开发板编号:RC2-1C6【产品特色】1 支持NIOSII开发;2 提供USB2.0 数据接口,480Mbps传输速度,可以作为算法验证和高速数据采集板;3 提供接口丰富的扩展板,针对音频,视频,网络和无线等应用提供参考设计;4 面向国内外开发型用户,可独立/或用户量身定制扩展板,满足各种特定应用【产品清单】1 RCII-CY1C6开发板 1块2 ByteBlasterII并口下载电缆 1条(如果是笔记本电脑,没有并口,建议购买¥999的USB套件)3 串口连接线 1条4 USB连接线 1条5 5V, 1A电源 1个6 标准的16×2液晶模块 1个7 配套DVD光盘 1张【USB套件-¥999】除了包括以上所有配件之外,另外包括:1. USB下载电缆(原价¥200)1 FPGA芯片: EP1C6Q2405,960LEs,相当于15万门规模。

2 配置芯片:EPCS13 512K Byte 高速,异步SRAM一片256K×16Bit的ASRAM,独立的字节使能信号4 128Mb高速SDARM一片4M×32Bit SDRAM ,最高143MHz读写速度;5 4M Byte 快速FLASH一片 4M×8Bit 或者 2M×16Bit Flash读写速度为90ns;灵活的页面方式,可以用来存储FPGA配置文件或者操作系统镜像文件;4 100M网络扩展板【¥600】采用10M/100M的以太网物理层/介质访问控制(PHY/MAC)芯片,LAN91C111,兼容Altera原厂开发板网络接口和设计实例。

/shop_view.asp?id=48产品浏览SoPC专家平台RED2开发板品牌:Red Cyclone现在现货订购2次,浏览6000次开发板价格:3500元开发板原价:3500元不打折E 币支付:不可用开发板编号:RED2-2C35【RED2的产品清单】1 RED2-2C35开发板 1套2 USB 下载电缆 1条3 串口连接线 1条4 USB连接线 1条5 5V、2A电源 1个6 标准的16×2液晶模块 1个7 配套DVD光盘 1张【红色飓风RED2硬件配置】采用8层板结构,按工业标准精心设计:1 FPGA芯片: EP2C35F6722 配置芯片:EPCS163 32M高速SDARM两片采用独立的两片美光公司高质量MT48LC16M16芯片,可升级为单片32Mbyte容量MT48LC32M16芯片,最高读写速率可高达166MHz,NIOS II和高速双端口SDRAM控制器均支持4 16Mbyte nor型闪存(可升级至32Mbyte)采用Intel公司高质量E28F128J3A芯片,可升级为单片32Mbyte容量E28F256J3A芯片,8位16位可选数据总线,NIOS II和高速多端闪存控制器均支持;5 1M Byte 高速,异步SRAM一片512K×16Bit的SRAM,独立的字节使能信号12 以太网DM9000A接口DM9000A是中国台湾DAVICOM公司推出的一款高速以太网接口芯片,其基本特征是:集成10/100M 物理层接口;内部带有16K字节SRAM用作接收发送的FIFO缓存;支持8/16bit两种主机工作模式;通过HP认证的AUTO-Mdix(支持直接互连自动翻转)功能;支持TCP/IP加速(IPV4 check sum offload)减轻CPU负担,提高整机效能;10ns I/O读写时间。

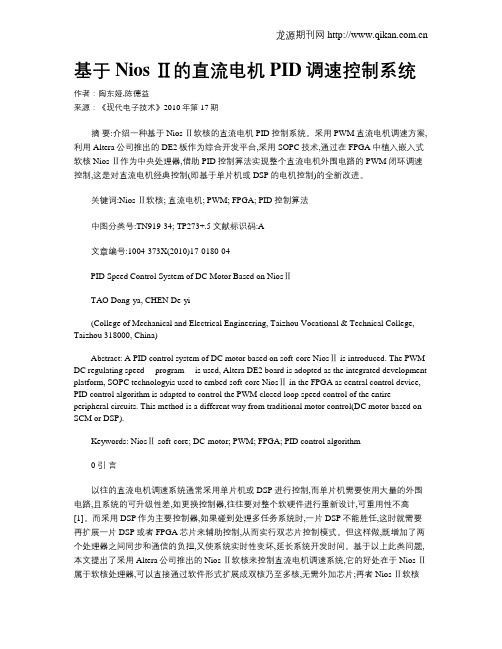

基于Nios Ⅱ的直流电机PID调速控制系统

基于Nios Ⅱ的直流电机PID调速控制系统作者:陶东娅,陈德益来源:《现代电子技术》2010年第17期摘要:介绍一种基于Nios Ⅱ软核的直流电机PID控制系统。

采用PWM直流电机调速方案,利用Altera公司推出的DE2板作为综合开发平台,采用SOPC技术,通过在FPGA中植入嵌入式软核Nios Ⅱ作为中央处理器,借助PID控制算法实现整个直流电机外围电路的PWM闭环调速控制,这是对直流电机经典控制(即基于单片机或DSP的电机控制)的全新改进。

关键词:Nios Ⅱ软核; 直流电机; PWM; FPGA; PID控制算法中图分类号:TN919-34; TP273+.5文献标识码:A文章编号:1004-373X(2010)17-0180-04PID Speed Control System of DC Motor Based on NiosⅡTAO Dong-ya, CHEN De-yi(College of Mechanical and Electrical Engineering, Taizhou Vocational & Technical College, Taizhou 318000, China)Abstract: A PID control system of DC motor based on soft-core NiosⅡ is introduced. The PWMd development platform, SOPC technologyis used to embed soft-core NiosⅡ in the FPGA as central control device, PID control algorithm is adapted to control the PWM closed loop speed control of the entire peripheral circuits. This method is a different way from traditional motor control(DC motor based on SCM or DSP).Keywords: NiosⅡ soft-core; DC-motor; PWM; FPGA; PID control algorithm0 引言以往的直流电机调速系统通常采用单片机或DSP进行控制,而单片机需要使用大量的外围电路,且系统的可升级性差,如更换控制器,往往要对整个软硬件进行重新设计,可重用性不高[1]。

EL-EMCU-I(SOPC)实验指导书

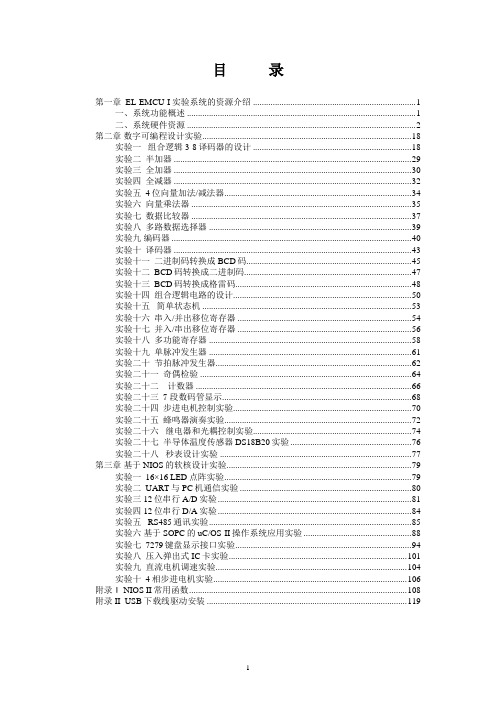

目录第一章 EL-EMCU-I实验系统的资源介绍 (1)一、系统功能概述 (1)二、系统硬件资源 (2)第二章数字可编程设计实验 (18)实验一组合逻辑3-8译码器的设计 (18)实验二半加器 (29)实验三全加器 (30)实验四全减器 (32)实验五 4位向量加法/减法器 (34)实验六向量乘法器 (35)实验七数据比较器 (37)实验八多路数据选择器 (39)实验九编码器 (40)实验十译码器 (43)实验十一二进制码转换成BCD码 (45)实验十二 BCD码转换成二进制码 (47)实验十三 BCD码转换成格雷码 (48)实验十四组合逻辑电路的设计 (50)实验十五简单状态机 (53)实验十六串入/并出移位寄存器 (54)实验十七并入/串出移位寄存器 (56)实验十八多功能寄存器 (58)实验十九单脉冲发生器 (61)实验二十节拍脉冲发生器 (62)实验二十一奇偶检验 (64)实验二十二计数器 (66)实验二十三 7段数码管显示 (68)实验二十四步进电机控制实验 (70)实验二十五蜂鸣器演奏实验 (72)实验二十六继电器和光耦控制实验 (74)实验二十七半导体温度传感器DS18B20实验 (76)实验二十八秒表设计实验 (77)第三章基于NIOS的软核设计实验 (79)实验一 16×16 LED点阵实验 (79)实验二 UART与PC机通信实验 (80)实验三 12位串行A/D实验 (81)实验四 12位串行D/A实验 (84)实验五 RS485通讯实验 (85)实验六基于SOPC的uC/OS-II操作系统应用实验 (88)实验七 7279键盘显示接口实验 (94)实验八压入弹出式IC卡实验 (101)实验九直流电机调速实验 (104)实验十 4相步进电机实验 (106)附录I NIOS II常用函数 (108)附录II USB下载线驱动安装 (119)第一章 EL-EMCU-I实验系统的资源介绍一、系统功能概述EL-EMCU-I型教学实验系统是属于一种综合的教学实验系统,该系统支持8位的8051 / C8051F021等型号、16位的MSP430系列 / AVR系列以及基于Cortex-M3内核的32位群星系列ARM处理器,实现了多模块的应用实验。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3 3.1

SOPC

� (1)掌握 SOPC 基本的开发流程。 (2)熟悉 QuartusII 软件的使用。 (3)熟悉 NiosII IDE 集成开发环境。 � � (1) 在 D:\sopc\works\下建立一个 hello_led 文件夹 (2) 打开 QuartusII, 点击下拉菜单中的 New project Wizard…会弹出如图 3.1.1 对话 框 将 8 位 LED 灯点亮,进行流水灯控制。

图 3.1.2 选定器件 (5) 点击 Tools 下拉菜单下的 SOPC Builder 工具,出现如图 3.1.3 对话框:

图 3.1.3 设定名称 (6) 在系统名称(System Name)中填写为 NiosII32,选择语言为 VHDL 后点击 OK,在 Device Family 中选择使用芯片的系列,这里选 Cyclone II,更改系统 频率为 50MHz,在 Board 中暂时先不选,使用 Unspecified Board,如图 3.1.4 所示;

图 3.1.4 设定芯片及系统时钟 (7) 在左面元件池中选择元件,我们这里需要使用 NiosII 32BIT CPU、调试串口、 led PIO、RAM,首先选择如图 3.1.5 所示的 Nios Processor,双击后会弹出如 图 3.1.6 所示对话框;在 JTAG Debug Module 栏中选择 level 1,点击 Finish 按 钮后返回 SOPC Builder 窗口,将 CPU_0 重新命名为 CPU 如图 3.1.7 所示;

图 3.1.8 JTAG UART 设置 B. C. (9) A. 保持默认选项,点击 Finish,返回 SOPC Builder 窗口。 将 jtag_uart_0 重命名为 jtag_uart. 添加内部 RAM, RAM 为程序运行空间, 该空间越大越有利, 这里使用 4Kbytes; 选择 Memory->On-Chip Memory,双击加入,会出现如图 3.1.9 所示设置向导;

2.2

SOPC

SOPC 系统的开发流程一般分为硬件和软件两大部分, 硬件开发主要是创建以 NiosII 处 理器为核心并包含了相应外设的系统, 作为应用程序运行的平台; 软件开发主要是根据系统 应用的需求,利用 C/C++语言和系统所带的 API 函数编写实现所需功能的程序。这样软件 运行在相应的硬件上,就构成了完整的 SOPC 应用系统。 可以将 NiosII 开发流程简化为以下几个步骤: 1)在 QuartusII 中建立工程 2)在 SOPC Builder 中建立 NiosII 系统模块 3)在 QuartusII 中的图形编辑界面中进行管脚连接、锁定工作 4)编译工程后下载到 FPGA 中 5)在 NiosII IDE 中根据硬件建立软件工程 6)编译后,经过简单设置下载到 FPGA 中进行调试、验证。

2 2.1

SOPC Altera SOPC

本书实验都是针对 Altera 公司的 NiosII 软核处理器设计的。基于 32 位的 NiosII 软核处 理器进行嵌入式系统设计包含了硬件配置、硬件设计、硬件仿真、软件设计以及软件调试等 多个步骤。Altera 提供了 SOPC 系统设计的完整的软件工具,主要有如下几部分: QuartusII 用于完成 Nios 系统的综合、硬件优化、适配、编程下载和硬件系统调试; SOPC Builder Nios 嵌入式处理器软件开发包,用于实现 Nios 系统的配置、生成及 软件调试平台的建立,SOPC Builder 工具集成在 QuartusII 软件中; Megacore IP 集成了 Altera 公司提供的知识产权(IP) 内核 NiosII IDE Nios 嵌入式系统软件开发集成环境,用于软件调试; DSP Builder 和 Matlab 软件协同工作,可用于生成 Nios 系统的硬件加速器,适用于 内嵌 DSP 处理模块的 FPGA 系列; 在进行 SOPC 系统设计前,需要安装 QuartusII 和 NiosII 开发软件,如果需要使用 DSP Builder,则要先安装 MATLAB7.0 以上的版本。 本书以 Windows 环境下 QuartusII6.1 和 NiosII EDS6.1 为例。 � 需安装软件 当你获得正版的 QuartusII 软件包后,需要安装以下几部分内容: (1)QuartusII 6.1 (2)MegaCore IP 6.1 (3)NiosII EDS 6.1 (4)DSP Builder v6.1 除此以外,还可以安装 Modelsim 等第三方仿真软件来配套使用。 � 软件的获得和下载 你可以通过代理购买 QuarutusII 软件包,获得安装 DVD。 除此以外,你可以直接到 Altera 公司的 FTP 网站去下载相应的软件包,下载地址为 ftp:///outgoing/release,你可以选择下载所需版本的 QuartusII 软件包内容,比如 windows 版 QuartusII 6.1 版本的文件为 61_quartus_windows.exe , MegaCore6.1 文件为 61_ip_windows.exe,NiosII EDS6.1 文件为 61_nioseds_windows.exe 等,以此类推。 � 软件使用许可的设置 软件安装完成后,如果你拥有正版的 license 许可文件,则可以按如下步骤设置软件许 可,打开 QuartusII 软件环境,选 Tools 菜单,运行 License Setup,在 License File 输入框中 输入你包含路径的 License 文件名然后确认即可,如果你使用的是网络版的使用许可,则输 入许可服务器的端口号和 IP 地址,如:27000@192.168.1.2 ,其含义表示 license 运行在 IP 地址为 192.168.1.2 的服务器的 27000 端口上。

1.2

DE2

DE2 平台上包含了丰富的硬件接口,组成结构如图所示 27MHz 时钟/50MHz 时钟/外部时钟 USB2.0 主机/设备 10/100M 以太网 SD 卡 IRDA 红外收发器 1MByte 闪存 8MByte SDRAM 512Kbyte SRAM 8 个 7 段数码管 2 个 40 脚扩展口 CycloneII FPGA EP2C35 16bit 音频 CODEC 10bit VGA DAC TV 解码器 8 个绿色 LED 18 个红色 LED 16X2 字符 LCD 模块 PS2/RS232 端口 18 个拨动开关 4 个按钮

图 3.1.1 建立工程 (3) 输入工程存放目录, 或点击工程路径右面的按钮设置工程存放目录, 在第二栏 中输入工程名称,这里输入为 led;点击 finish,此时我们建立好了 LED 工程 文件; (4) 点击 Assignments 菜单中的 Device,选择芯片 EP2C35F672C6 如下图 3.1.2 所 示;

图 3.1.9 RAM 设置 B. 设置后如上图所示,点击 Finish,返回到 SOPC Builder 窗口,命名为 ram; (10) 加入 led_pio,此元件为 IO 口,可以根据需要配置设置选项; A. 选择 Other->PIO,双击加入,出现如图 3.1.10 所示设置向导:

图 3.1.10 添加 led_pio B. 选择 Output ports only,点击 Finish,重新命名为 led_pio; (11) 指定基地址和分配中断号,SOPC Builder 会给用户的 NiosII 系统模块分配默 认的基地址,用户也可以更改这些默认地址。选择执行 System 下拉菜单中的 Auto-Assign Base Address;选择执行 System 下拉菜单中的 Auto-Assign IRQs; (12) 进行系统设置, 选择 More “CPU” Settings, 按照图 3.1.11 所示对系统进行设置;

图 1.1 DE2 开发板布局 DE2 平台提供的主要资源有: (1) Altera CycloneII 系列 FPGA 芯片 EP2C35F672C6(U16) 。 (2) 主动串行配置器件 EPCS16(U30) 。 (3) 编程调试接口 USB Blaster,支持 JTAG 模式和 AS 模式,其中 U25 是实现 USB Blaster 的 USB 接口芯片 FT245B; U26 为 CPLD 芯片 EPM3128, 用以实现 JTAG 模式和 AS 模式配置,可以用 SW19 选择配置模式;USB Blaster 的 USB 口为 J9 。 (4) 512K 字节 SRAM(U18) 。 (5) 8M 字节 SDRAM(U17) 。 (6) 1M 字节闪存(U20) 。 (7) SD 卡接口(U19) 。 (8) 4 个手动按钮(KEY0-KEY3)和 18 个拨动开关(SW0-SW17) 。 (9) 9 个绿色 LED(LEDG0-LEDG8)和 18 个红色 LED(LEDR0-LEDR17) 。 (10) 板上时钟源(50MHz 晶振 Y1 和 27MHz 晶振 Y3) ,外部时钟接口(J5) 。

图 3.1.5 选择 NiosII

图 3.1.6 NiosII 设置

图 3.1.7 重命名 CPU 注意:对模块命名要遵循以下规则: � 名字最前面应该使用英文; � 能使用的字符只有英文字母、数字和下划线“_” ; � 不能连续使用“_”符号,在名字的最后也不能使用“_” 。 (8) 添加 JTAG UART Interface, 通过该接口, 我们可以在 PC 主机和 SOPC Builder 系统之间进行串行字符流更新,主要用来调试、下载数据等,也可以作为标准 输入、输出来使用; A. 选择 Communication->JTAG UART 加入,会出现设置向导如图 3.1.8 所示:

EPCS16 配置器件

USB Blaster

图 1.2 DE2 平台结构

DE2 平台的核心是 Altera 公司的 FPGA 芯片 EP2C35F672, 该芯片是 Altera 公司 CycloneII 系列产品之一。EP2C35F672 采用 Fineline BGA 672 脚的封装,可以提供多达 475 个 I/O 引 脚供使用者使用。