03-第三章 STM32处理器总线结构和存储器

《计算机硬件技术基础(第三版)》第3章 32位微处理器

(1)总线接口部件 总线接口部件与片内Cache外部总线接口实行的是逻辑接口连接。当访问 Cache出现没命中、或需更改系统存储器内容、或需向Cache写入某些信 息时,就要通过总线接口从外部存储器系统中取出一批数据。 (2)预取缓冲部件 预取缓冲部件 取指令是指从高速缓冲存储器Cache内或从内存储器中取出指令代码, 以备译码之用的操作。 (3)指令译码部件 指令译码部件 译码操作, 一是检查一条指令的格式, 二是确定它是哪种类型操作的指令,并给出这条指令所需的操作数。 (4)控制部件 控制部件 Pentium微处理器控制部件的作用是,负责解释来自指令译码部件的 指令字和控制ROM的微代码。控制部件的输出控制着整数流水线部件和 浮点部件。 (5)执行部件 执行部件 是微处理器用于执行指令所规定的具体操作的CPU的核心硬件部分。 这些非常具体的操作是指诸如数值运算、逻辑操作以及分支转移处理等。

为了支持在Pentium内采用的分支转移预测新技术,芯片内装备有两个 预取缓冲存储器,一个是以线性方式来预取代码,另一个则是根据分支转 移目标缓冲器(BTB)预取代码。这样就可以保证在执行之前将所需用的 指令从存储器预取出来。 由于Pentium采用了这项技术,可以在无延迟的情况下正确地预测各 种转移。另外,V流水线中的条件转移指令可以与一条比较类指令成对执 行,当然也可以与U流水线中的置标志指令配合执行。但Pentium作到了 与现有软件是完全兼容,所以不必修改现有软件。

计算机硬件技术基础

3.1 .

CISC和RISC 和

1 复杂指令系统计算机 复杂指令系统计算机—CISC 每一种微处理器的CPU都有属于它自己的指令系统。 CPU正是通过执行一系列的特定的指令来实现应用程序 的某种功能。像Intel x86系列,为了增加新的功能, 就必须增加新的指令;另一方面,为了保持向上兼容, 又必须保留原有的指令。每条指令又有若干个不同的操 作字段,用来说明要操作的数据类型,以及存放的位置。 这就意味着一个较大的指令系统和复杂的寻址技术。以 这样的微处理器为平台的计算机系统就是“复杂指令系 统计算机”(CISC)。 CISC也有许多优点,如指令经编译后生成的指令程 序较小执行起来较快,节省硬件资源。像存取指令的次 数少,占用较少的存储器等。

STM32中文参考手册

9.1 DMA简介

9.2 DMA主要特性

9.3 功能描述

STM32F10xxx参考手册

75

75 75 76 76 77 77 77

78

78 78 79 79 80 80 81 82 82

83

83 83 86 86 87 87

88

89

89

89 89

91

91 92 92 92 94

108

9.4.3 DMA通道x配置寄存器(DMA_CCRx)(x = 1…7)

108

9.4.4 DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7)

110

9.4.5 DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7)

110

9.4.6 DMA通道x存储器地址寄存器(DMA_CPARx)(x = 1…7)

16

1.3 可用的外设

16

2 存储器和总线构架

17

2.1 系统构架

17

2.2 存储器组织

18

2.3 存储器映像

19

2.3.1 嵌入式SRAM

20

2.3.2 位段

20

2.3.3 嵌入式闪存

21

2.4 启动配置

23

3 CRC计算单元(CRC)

25

3.1 CRC简介

25

3.2 CRC主要特性

25

3.3 CRC功能描述

STM32F10xxx参考手册

38

38 39

39

39 39 40 40 42

45

45

45 45 46

46

48 48 49 49 49 50 50 50 50 50

stm32的总线AMBA、AHB、APB

stm32的总线AMBA、AHB、APBAMBAAMBA(Advanced Microprocessor Bus Architecture)是ARM公司提出的一种开放性的SoC 总线标准,现在已经广泛的应用于RISC的内核上了。

AMBA定义了一种多总线系统(mulTIlevel busing system),包括系统总线和等级稍低的外设总线。

AMBA支持32位、64位、128位的数据总线,和32位的地址总线,同时支持byte和half-word设计。

它定义了两种总线:AHB(Advanced High-performance Bus)先进的高性能总线,也叫做ASB (Advanced System Bus)。

APB(Advanced peripheral Bus)先进的外设总线AHB和ASB其实是一个东西,是高速总线,主要负责嵌入式处理器、DMA控制器、Memory等等的接口。

APB是低速总线,主要负责外设接口AHB和APB之间是通过Bridge(桥接器)链接的Bus Bridges总所周知,一个系统中的各个模块之间相互通信是通过总线,总线的作用,就是把数据和地址从设备A搬运到设备B上,如果说设备A和设备B具有一致性(原文是under discussion,这里我不知道怎么翻译比较好,暂且翻译为一致性),那么设备A和设备B可以直接挂在同一个总线上,并直接解读总线上的数据。

但是,如果设备A和设备B不具有一致性,那么设备A和设备B就必须挂在两条不同的总线上,这时候我们就需要一个翻译,把设备A上的总线上的数据和地址转换成设备B可以解析的格式,然后放到设备B的总线上,这个翻译就是Bus Bridge,下面这幅图就形象的说明了Bus Bridge在AHB和APB之间的作用。

AHB链接的设备的数据传输速度是比APB设备传输的速度快很多的,也就是说,这里的这个Bus Beidge所起的作用就是缓冲这里可以看到AHB主要是链接在了系统的内核以及存储管理上面的,APB则主要分布给我外设。

stm32芯片简介

单片机存储器处理器成本STM32背景如果你正为项目的处理器而进行艰难的选择:一方面抱怨16位单片机有限的指令和性能,另一方面又抱怨32位处理器的高成本和高功耗,那么,基于ARM Cortex-M3内核的STM32系列处理器也许能帮你解决这个问题。

使你不必在性能、成本、功耗等因素之间做出取舍和折衷。

即使你还没有看完STM32的产品手册,但对于这样一款融合ARM和ST技术的“新生儿”相信你和我一样不会担心这款针对16位MCU应用领域的32位处理器的性能,但是从工程的角度来讲,除了芯片本身的性能和成本之外,你或许还会考虑到开发工具的成本和广泛度;存储器的种类、规模、性能和容量;以及各软件获得的难易,我相信你看完本专题会得到一个满意的答案。

对于在16位MCU领域用惯专用在线仿真器(ICE)的工程师可能会担心开发工具是否能够很快的上手?开发复杂度和整体成本会不会增加?产品上市时间会不会延长?没错,对于32位嵌入式处理器来说,随着时钟频率越来越高,加上复杂的封装形式,ICE已越来越难胜任开发工具的工作,所以在32位嵌入式系统开发中多是采用JTAG仿真器而不是你熟悉的ICE。

但是STM32采用串行单线调试和JTAG,通过JTAG调试器你可以直接从CPU获取调试信息,从而将使你的产品设计大大简化,而且开发工具的整体价格要低于ICE,何乐而不为?有意思的是STM32系列芯片上印有一个蝴蝶图像,据ST微控制器产品部Daniel COLONNA 先生说,这是代表自由度,意在给工程师一个充分的创意空间。

我则“曲解”为预示着一种蝴蝶效应,这种蝴蝶效应不仅会对方案提供商以及终端产品供应商带来举足轻重的影响,而且会引起竞争对手策略的改变……翅膀已煽动,让我们一起静观其变!STM32市面上流通的型号截至2010年7月1日,市面流通的型号有:基本型:STM32F101R6 STM32F101C8 STM32F101R8 STM32F101V8 STM32F101RBSTM32F101VB增强型:STM32F103C8 STM32F103R8 STM32F103V8 STM32F103RBSTM32F103VB STM32F103VE STM32F103ZESTM32系列的作用简介ARM公司的高性能”Cortex-M3”内核1.25DMips/MHz,而ARM7TDMI只有0.95DMips/MHz一流的外设1μs的双12位ADC,4兆位/秒的UART,18兆位/秒的SPI,18MHz的I/O翻转速度低功耗在72MHz时消耗36mA(所有外设处于工作状态),待机时下降到2μA最大的集成度复位电路、低电压检测、调压器、精确的RC振荡器等简单的结构和易用的工具 STM32F10x重要参数2V-3.6V供电容忍5V的I/O管脚优异的安全时钟模式带唤醒功能的低功耗模式内部RC振荡器内嵌复位电路工作温度范围:-40°C至+85°C或105°C STM32F101性能特点36MHz CPU 多达16K字节SRAM 1x12位ADC温度传感器 STM32F103性能特点72MHz CPU多达20K字节SRAM 2x12位ADC 温度传感 PWM定时器 CAN USBSTM32互联型系列简介:全新STM32互连型(Connectivity)系列微控制器增加一个全速USB(OTG)接口,使终端产品在连接另一个USB设备时既可以充当USB主机又可充当USB 从机;还增加一个硬件支持IEEE1588精确时间协议(PTP)的以太网接口,用硬件实现这个协议可降低CPU开销,提高实时应用和联网设备同步通信的响应速度。

stm32单片机的工作原理

stm32单片机的工作原理STM32单片机是一款广泛应用于嵌入式系统的微控制器,具有高性能、低功耗和丰富的外设资源等特点。

本文将详细介绍STM32单片机的工作原理,并对其各个部分进行解析。

一、概述STM32单片机是由意法半导体(STMicroelectronics)公司开发的一款32位微控制器。

它采用了先进的ARM Cortex-M内核,非常适用于嵌入式控制应用。

STM32单片机具有丰富的外设资源,如通用IO口、定时器、通信接口(如USART、SPI、I2C)等,可以满足不同应用的需求。

二、内核结构STM32单片机的内核结构采用了Harvard体系结构,主要由处理器核、存储器和总线组成。

处理器核负责指令执行和数据处理,存储器用于存储程序代码和数据,总线则用于连接处理器核和存储器。

1. 处理器核STM32单片机的处理器核采用了ARM Cortex-M系列的核心。

它具有强大的计算能力和高效的指令执行速度,支持多种指令集和调试接口,能够满足不同应用的需求。

处理器核负责执行存储在存储器中的程序代码,控制外设的操作,并根据指令完成相应的数据处理。

2. 存储器STM32单片机的存储器分为Flash存储器和RAM存储器两部分。

Flash存储器用于存储程序代码和常量数据,可在电源关闭后保持数据的不变性。

RAM存储器用于存储临时的变量和数据,速度较快但断电后数据会消失。

3. 总线STM32单片机的总线用于连接处理器核和存储器,同时也用于连接外设。

总线分为数据总线、地址总线和控制总线三部分。

数据总线用于传输数据,地址总线用于指定存储器或外设的地址,控制总线用于传递读写和控制信号。

三、外设资源STM32单片机具有丰富的外设资源,可以满足各种嵌入式控制应用的需求。

这些外设包括通用IO口、定时器、通信接口等。

1. 通用IO口通用IO口是STM32单片机最常用的外设之一,它可以配置为输入或输出,用于连接外部设备或传感器。

通用IO口的数量和类型取决于具体型号,一般都有多个引脚可供使用。

stm32的组成

stm32的组成STM32是一款由STMicroelectronics公司生产的32位微控制器系列,广泛应用于嵌入式系统领域。

STM32微控制器由核心处理器、存储器、外设和引脚等组成,其丰富的特性和强大的性能使其成为嵌入式系统设计的首选。

1. 核心处理器:STM32微控制器使用ARM Cortex-M系列核心处理器,如Cortex-M0、Cortex-M3、Cortex-M4等。

这些处理器具有低功耗、高性能和丰富的指令集,适用于嵌入式应用。

它们提供了高效的计算能力、良好的实时性能和出色的能源管理。

2. 存储器:STM32微控制器具有不同容量和类型的存储器,包括闪存存储器、RAM和EEPROM。

闪存存储器用于存储程序代码和数据,RAM用于临时存储数据,EEPROM用于非易失性存储。

存储器的大小和类型可以根据具体应用的需求进行选择。

3. 外设:STM32微控制器提供了丰富的外设,包括通用输入/输出口(GPIO)、通用串行总线(USART、SPI、I2C)、通用定时器和计数器(TIM)、模拟至数字转换器(ADC)、数字至模拟转换器(DAC)、通用同步/异步收发器(USART、USB、CAN)等。

这些外设可以满足不同嵌入式系统的需求,实现各种功能。

4. 引脚:STM32微控制器的引脚用于连接外部器件,如传感器、执行器、显示屏和通信设备等。

引脚的数量和类型根据具体微控制器型号的不同而有所差异,可满足不同应用的连接需求。

微控制器的引脚也具有多种功能,如GPIO、模拟输入、定时器输入捕获等。

5. 电源管理:STM32微控制器提供了多种电源管理功能,包括低功耗模式、供电电压检测、时钟管理等。

低功耗模式可以使微控制器在待机或睡眠状态下降低功耗,延长电池寿命。

供电电压检测用于监测供电电压的稳定性,保证微控制器正常工作。

时钟管理用于控制微控制器的时钟频率和源。

6. 开发工具:STM32微控制器配套了一系列的开发工具,如集成开发环境(IDE)、调试器和编译器等。

STM32内部结构

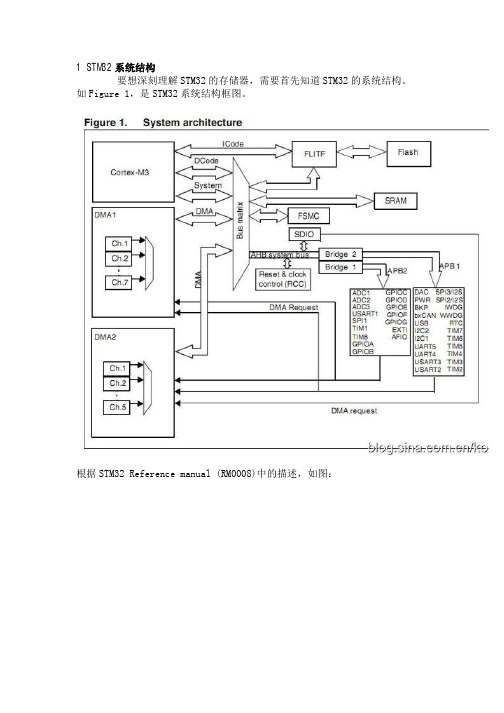

1 STM32系统结构要想深刻理解STM32的存储器,需要首先知道STM32的系统结构。

如Figure 1,是STM32系统结构框图。

根据STM32 Reference manual (RM0008)中的描述,如图:可以得知STM32系统结构的组成,每一个模块更为详细的内容,请参考相关文档。

RM0008文档中可以看出,STM32采用的是Cortex-M3内核,因此,有必要了解Cortex-M3的存储器结构。

图中还可以看出,Cortex-M3是通过各个总线和Flash、SROM相连接的。

2 STM32内核(Cortex-M3)的结构以下是Cortex-M3模块框图:该Cortex-M3内核通过I-Code、D-Code、System总线与STM32内部的Flash、SROM相连接的,该种连接情况直接关系到STM32存储器的结构组织;也就是说,Cortex-M3的存储器结构决定了STM32的存储器结构。

这里可能说的比较笼统,可以这样理解:Cortex-M3是一个内核,自身定义了一个存储器结构,ST公司按照Cortex-M3的这个存储器定义,设计出了自己的存储器结构;但是ST公司的STM32的存储器结构必须按照Cortex-M3这个定义的存储器结构来进行设计。

举个例子:我买了一个做饭的调料盒子,有三块区域(假设存储器分为3块),上面分别标有盐(Flash)、糖(SROM)、味精(Peripheral);此时,该调料盒子并没有任何意义(对应Cortex-M3内核);我按照标签放入特定品牌、特定分量的盐(Flash)、糖(SROM)、味精(Peripheral),产生一个有实际意义的调料盒(各类Cortex-M3内核的芯片,如STM32)。

期间,调料位置不能放错,但可以不放。

由上面的例子可以看出,空的调料盒子决定了有意义的调料盒子存放调料的结构。

因此,只要了解空盒子的存储结构,就可以很清楚的明白当有调料时的用法了。

cortex-m3第三章

STM32F10x

框 图

多种封装形式

Cortex-M3系列微处理器的主要特点如下:

处理模式和线程模式。 ISR 的低延迟进入和退出。 可中断-可继续的LDM/STM,PUSH/POP。 ARMv6类型BE8/LE支持。 ARMv6 非对齐访问。

STM32的主要优势

1、具业界领先架构的Cortex-M3内核

系统结构图:

互联型产品的系统结构

AHB/APB桥(APB)

两个桥在AHB和APB总线间提供同步连接。 APB1操作速度限于36MHz,APB2操作于全速(最高 72MHz)。 在每一次复位以后,所有除SRAM和FLITF以外的外设都 被关闭,在使用一个外设之前,必须设置寄存器 RCC_AHBENR来打开该外设的时钟。

等待周期体现了系统时钟(SYSCLK)频率与闪存访 问时间的关系:

0等待周期,当 0 < SYSCLK < 24MHz 1等待周期,当 24MHz < SYSCLK ≤ 48MHz 2等待周期,当 48MHz < SYSCLK ≤ 72MHz

半周期配置不能与使用了预分频器的AHB一起使用, 时钟系统应该等于HCLK时钟。该特性只能用在时 钟频率为8MHz或低于8MHz时,可以直接使用的 内部RC振荡器(HSI),或者是主振荡器(HSE),但 不能用PLL。

USB开发工具集 USB开发工具集提供了完整的,经过验证的固件包, 使得用户可以顺利地开发各个类的USB固件,其中包 括: 用于普通的设备管理任务的控制传输 中断传输,附带人机界面类(HID)鼠标/游戏杆例 程 批量传输,附带大规模存储(mass storage)例程 同步传输,附带扬声器/麦克风例程

STM32单片机的知识点总结

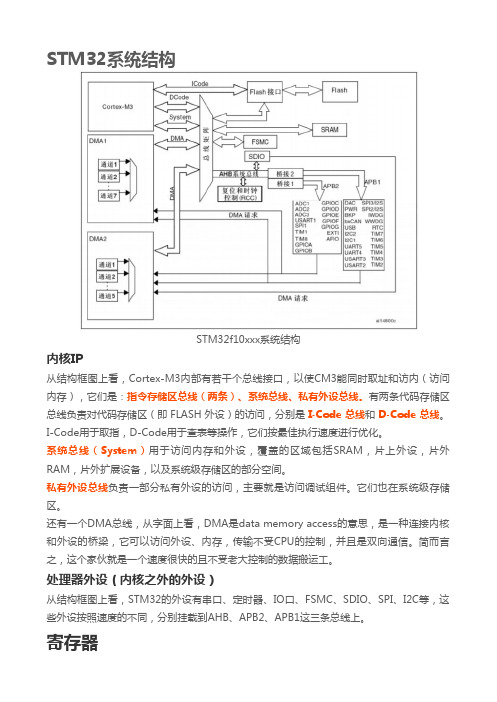

STM32系统结构STM32f10xxx系统结构内核IP从结构框图上看,Cortex-M3内部有若干个总线接口,以使CM3能同时取址和访内(访问内存),它们是:指令存储区总线(两条)、系统总线、私有外设总线。

有两条代码存储区总线负责对代码存储区(即 FLASH 外设)的访问,分别是 I-Code 总线和 D-Code 总线。

I-Code用于取指,D-Code用于查表等操作,它们按最佳执行速度进行优化。

系统总线(System)用于访问内存和外设,覆盖的区域包括SRAM,片上外设,片外RAM,片外扩展设备,以及系统级存储区的部分空间。

私有外设总线负责一部分私有外设的访问,主要就是访问调试组件。

它们也在系统级存储区。

还有一个DMA总线,从字面上看,DMA是data memory access的意思,是一种连接内核和外设的桥梁,它可以访问外设、内存,传输不受CPU的控制,并且是双向通信。

简而言之,这个家伙就是一个速度很快的且不受老大控制的数据搬运工。

处理器外设(内核之外的外设)从结构框图上看,STM32的外设有串口、定时器、IO口、FSMC、SDIO、SPI、I2C等,这些外设按照速度的不同,分别挂载到AHB、APB2、APB1这三条总线上。

寄存器什么是寄存器?寄存器是内置于各个IP外设中,是一种用于配置外设功能的存储器,并且有想对应的地址。

一切库的封装始于映射。

是不是看的眼都花了,如果进行寄存器开发,就需要怼地址以及对寄存器进行字节赋值,不仅效率低而且容易出错。

库的存在就是为了解决这类问题,将代码语义化。

语义化思想不仅仅是嵌入式有的,前端代码也在追求语义特性。

从点灯开始学习STM32内核库文件分析cor_cm3.h这个头文件实现了:1、内核结构体寄存器定义。

2、内核寄存器内存映射。

3、内存寄存器位定义。

跟处理器相关的头文件stm32f10x.h实现的功能一样,一个是针对内核的寄存器,一个是针对内核之外,即处理器的寄存器。

RT-Thread STM32 说明

; void rt_hw_interrupt_enable(rt_base_t level); ; 恢复中断 rt_hw_interrupt_enable PROC EXPORT rt_hw_interrupt_enable MSR PRIMASK, r0 ; 恢复R0寄存器的值到PRIMASK中

RT-Thread 网站:

Cortex M3 微处理器是 ARM 公司于 2004 年推出的基于 ARMv7 架构的新一代微处理器,它 的速度比目前广泛使用的 ARM7 快三分之一,功耗则低四分之三,并且能实现更小芯片面 积,利于将更多功能整合在更小的芯片尺寸中。 Cortex-M3 微处理器包含了一个 ARM core,内置了嵌套向量中断控制器、存储器保护等系 统外设。ARM core 内核基于哈佛架构,3 级流水线,指令和数据分别使用一条总线,由于 指令和数据可以从存储器中同时读取,所以 Cortex-M3 处理器对多个操作并行执行,加快 了应用程序的执行速度。

swtich_to_thread LDR r1, =rt_interrupt_to_thread LDR r1, [r1] LDR r1, [r1] ; 载入切换到线程的栈指针到R1寄存器 LDMFD MSR ORR BX ENDP r1!, {r4 - r11} psp, r1 lr, lr, #0x04 lr ; 恢复R4 – R11寄存器 ; 更新程序栈指针寄存器 ; 构造LR以返回到Thread模式 ; 从PendSV异常中返回

Handler 模式 R4 ... R11 图 D - 1 正常模式下的线程上下文切换 当要进行切换时 (假设从 Thread [from] 切换到 Thread [to]) , 通过 rt_hw_context_switch 函数触发一个 PenSV 异常。异常产生时,Cortex M3 会把 PSR,PC,LR,R0 – R3,R12 压入当前线程的栈中,然后切换到 PenSV 异常。到 PenSV 异常后,Cortex M3 工作模式 切换到 Handler 模式,由函数 rt_hw_pend_sv 进行处理。rt_hw_pend_sv 函数会载 入切换出线程和切换到线程的栈指针,如果切换出线程的栈指针是 0 那么表示这是第一次 线程上下文切换,不需要对切换出线程做压栈动作。如果切换出线程栈指针非零,则把剩余 未压栈的 R4 – R11 寄存器依次压栈;然后从切换到线程栈中恢复 R4 – R11 寄存器。当 从 PendSV 异常返回时,PSR,PC,LR,R0 – R3,R12 等寄存器由 Cortex M3 自动恢 复。 因为中断而导致的线程切换可用图 D - 2 中断中线程上下文切换表示。 R4 ... R11

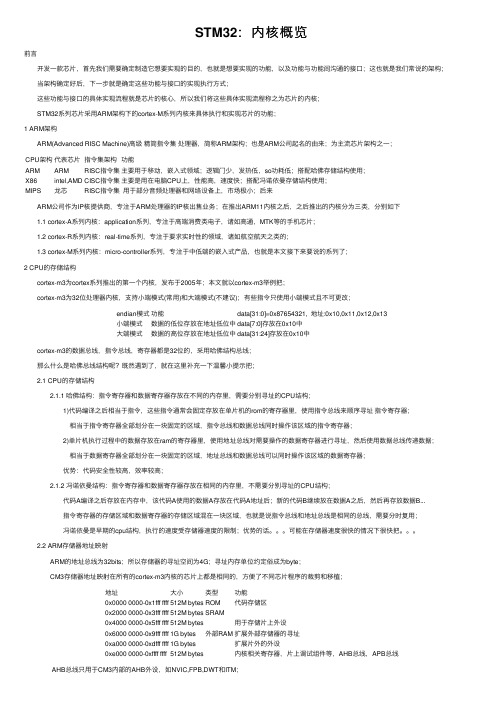

STM32:内核概览

STM32:内核概览前⾔ 开发⼀款芯⽚,⾸先我们需要确定制造它想要实现的⽬的,也就是想要实现的功能,以及功能与功能间沟通的接⼝;这也就是我们常说的架构; 当架构确定好后,下⼀步就是确定这些功能与接⼝的实现执⾏⽅式; 这些功能与接⼝的具体实现流程就是芯⽚的核⼼,所以我们将这些具体实现流程称之为芯⽚的内核; STM32系列芯⽚采⽤ARM架构下的cortex-M系列内核来具体执⾏和实现芯⽚的功能;1 ARM架构 ARM(Advanced RISC Machine)⾼级精简指令集处理器,简称ARM架构;也是ARM公司起名的由来;为主流芯⽚架构之⼀;CPU架构代表芯⽚指令集架构功能ARM ARM RISC指令集主要⽤于移动,嵌⼊式领域;逻辑门少,发热低,so功耗低;搭配哈佛存储结构使⽤;X86intel,AMD CISC指令集主要是⽤在电脑CPU上,性能⾼,速度快;搭配冯诺依曼存储结构使⽤;MIPS龙芯RISC指令集⽤于部分⾳频处理器和⽹络设备上,市场极⼩;后来 ARM公司作为IP核提供商,专注于ARM处理器的IP核出售业务;在推出ARM11内核之后,之后推出的内核分为三类,分别如下 1.1 cortex-A系列内核:application系列,专注于⾼端消费类电⼦,诸如⾼通,MTK等的⼿机芯⽚; 1.2 cortex-R系列内核:real-time系列,专注于要求实时性的领域,诸如航空航天之类的; 1.3 cortex-M系列内核:micro-controller系列,专注于中低端的嵌⼊式产品,也就是本⽂接下来要说的系列了;2 CPU的存储结构 cortex-m3为cortex系列推出的第⼀个内核,发布于2005年;本⽂就以cortex-m3举例把; cortex-m3为32位处理器内核,⽀持⼩端模式(常⽤)和⼤端模式(不建议);有些指令只使⽤⼩端模式且不可更改;endian模式功能data[31:0]=0x87654321, 地址:0x10,0x11,0x12,0x13⼩端模式数据的低位存放在地址低位中data[7:0]存放在0x10中⼤端模式数据的⾼位存放在地址低位中data[31:24]存放在0x10中 cortex-m3的数据总线,指令总线,寄存器都是32位的,采⽤哈佛结构总线; 那么什么是哈佛总线结构呢?既然遇到了,就在这⾥补充⼀下温馨⼩提⽰把; 2.1 CPU的存储结构 2.1.1 哈佛结构:指令寄存器和数据寄存器存放在不同的内存⾥,需要分别寻址的CPU结构; 1)代码编译之后相当于指令,这些指令通常会固定存放在单⽚机的rom的寄存器⾥,使⽤指令总线来顺序寻址指令寄存器; 相当于指令寄存器全部划分在⼀块固定的区域,指令总线和数据总线同时操作该区域的指令寄存器; 2)单⽚机执⾏过程中的数据存放在ram的寄存器⾥,使⽤地址总线对需要操作的数据寄存器进⾏寻址,然后使⽤数据总线传递数据; 相当于数据寄存器全部划分在⼀块固定的区域,地址总线和数据总线可以同时操作该区域的数据寄存器; 优势:代码安全性较⾼,效率较⾼; 2.1.2 冯诺依曼结构:指令寄存器和数据寄存器存放在相同的内存⾥,不需要分别寻址的CPU结构; 代码A编译之后存放在内存中,该代码A使⽤的数据A存放在代码A地址后;新的代码B继续放在数据A之后,然后再存放数据B... 指令寄存器的存储区域和数据寄存器的存储区域混在⼀块区域,也就是说指令总线和地址总线是相同的总线,需要分时复⽤; 冯诺依曼是早期的cpu结构,执⾏的速度受存储器速度的限制;优势的话。

stm32单片机的组成

stm32单片机的组成STM32单片机是一款基于ARM Cortex-M内核的微控制器。

它由多个功能单元组成,包括中央处理器(CPU)、存储器、时钟和控制单元、外设接口等。

本文将对STM32单片机的组成进行详细介绍。

一、中央处理器(CPU)STM32单片机采用ARM Cortex-M系列的处理器核心作为CPU。

这种处理器核心具有高性能和低功耗的特点,能够满足嵌入式系统的需求。

根据不同型号和系列,STM32单片机可以搭载不同频率和功能的ARM Cortex-M处理器。

二、存储器STM32单片机的存储器由闪存(Flash)和随机存取存储器(SRAM)两部分组成。

闪存用于存储程序代码和只读数据,而SRAM用于存储数据和变量。

闪存的容量和速度因不同型号和系列而异,可以满足不同应用场景的需求。

三、时钟和控制单元STM32单片机的时钟和控制单元负责提供系统时钟和外设控制。

它包括时钟发生器、复位电路、电源管理单元等组件。

时钟发生器用于产生各种时钟信号,包括系统时钟、外设时钟等,以保证整个系统的运行稳定。

复位电路用于初始化系统状态,电源管理单元则负责控制供电和功耗管理。

四、外设接口STM32单片机具有丰富的外设接口,包括通用输入输出(GPIO)、通用串行总线(SPI/I2C)、通用异步收发器(UART)、定时器、模数转换器(ADC/DAC)等。

这些外设接口可以与外部器件进行数据交互和控制。

不同型号和系列的STM32单片机在外设接口的数量和功能上可能有所差异,可以根据具体应用需求进行选择。

五、调试和编程接口STM32单片机支持多种调试和编程接口,包括串行线调试接口(SWD)、JTAG接口等。

这些接口可以用于单片机的调试、仿真和编程。

通过调试和编程接口,开发者可以实时监测和调试单片机的运行状态,并实现固件的烧录和更新。

六、其他组成部分除了上述提到的主要组成部分外,STM32单片机还包括其他一些辅助组件。

例如,晶体振荡器用于提供系统时钟的时基,电源管理单元使得单片机可以在低功耗模式下工作,外部中断和DMA控制器可实现外设的中断和直接内存访问。

stm32单片机的基本组成和工作原理

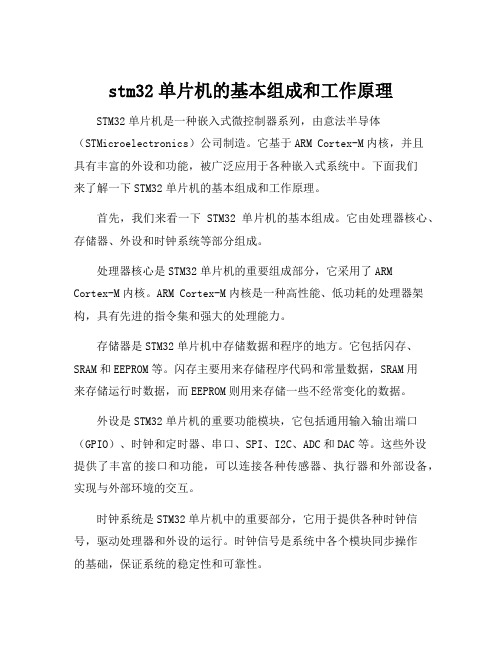

stm32单片机的基本组成和工作原理STM32单片机是一种嵌入式微控制器系列,由意法半导体(STMicroelectronics)公司制造。

它基于ARM Cortex-M内核,并且具有丰富的外设和功能,被广泛应用于各种嵌入式系统中。

下面我们来了解一下STM32单片机的基本组成和工作原理。

首先,我们来看一下STM32单片机的基本组成。

它由处理器核心、存储器、外设和时钟系统等部分组成。

处理器核心是STM32单片机的重要组成部分,它采用了ARMCortex-M内核。

ARM Cortex-M内核是一种高性能、低功耗的处理器架构,具有先进的指令集和强大的处理能力。

存储器是STM32单片机中存储数据和程序的地方。

它包括闪存、SRAM和EEPROM等。

闪存主要用来存储程序代码和常量数据,SRAM用来存储运行时数据,而EEPROM则用来存储一些不经常变化的数据。

外设是STM32单片机的重要功能模块,它包括通用输入输出端口(GPIO)、时钟和定时器、串口、SPI、I2C、ADC和DAC等。

这些外设提供了丰富的接口和功能,可以连接各种传感器、执行器和外部设备,实现与外部环境的交互。

时钟系统是STM32单片机中的重要部分,它用于提供各种时钟信号,驱动处理器和外设的运行。

时钟信号是系统中各个模块同步操作的基础,保证系统的稳定性和可靠性。

接下来,我们来了解一下STM32单片机的工作原理。

首先在上电或复位后,处理器核心从存储器中读取程序代码,并按照指令序列执行相应的操作。

处理器还可以通过外设来执行特定的功能,比如读取传感器数据、控制执行器等。

处理器通过总线和存储器、外设进行数据交换和通信。

数据可以从存储器中读取到处理器中进行运算,也可以从处理器中写入存储器进行存储。

外设可以向处理器发送数据,也可以接收处理器发送的数据。

这样,就实现了处理器与存储器和外设之间的数据交换和通信。

时钟系统为处理器和外设提供了时钟信号,使它们能够按照同步的方式工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.4 启动配置

系 统 启 动之 后, CPU 从 位 于 0x0000 0000 地 址 处 的 启 动区开始执行代码。 对 于STM32F10x 系列处理器,可以通过配置 BOOT[1:0]引脚选择三种不同启动模式。

启动模式配置

3.4 启动配置

通过设置 BOOT[1:0]引脚,各种不同启动模式 对应的存储器物理地址将被映像到第 0 块(启 动区)。 系统复位后,在 SYSCLK 引脚的第4 个上升 沿,BOOT 引脚的值将被锁存。

3.3 位段

Cortex-M3 存储器空间中包括两个位段区: SRAM 区的最低 1MB空间和外设存储区的最 低 1MB 空间。 这两个位段区分别与两个 32M 的位段别名区 对应,位段区中的每一位映射到位段别名区中 的一个字。 通过对别名区中某个字的读写操作可以实现对 位段区中某一位的读写操作。

位段别名区中的字与位段区的位映射公式

bit_word_addr = bit_band_base + (byte_offset x 32) + bit_number × 4 例如:SRAM 位段区中地址为 0x20000300 的字节中的位 2 被映射到别名区中的地址为: 0x22006008(= 0x22000000 + (0x300*32) + (2*4))的字。

rtex-M3 处理器的存储系统采用统一编址方 式;程序存储器、数据存储器、寄存器以及输 入输出端口被组织在同一个 4GB 的线性地址 空间内;

小端方式存放。

3.2.2 STM32 处理器存储器映射

STM32 系列处理器将可访问的存储器空间被 分成 8 个主块,每个块为 512MB。 处理器内部存储器、片上外围设备的地址映射 以及分配给片上各个外围设备的地址空间请参 照书籍。

STM32F10x 处理器总线结构

总线结构中各单元的功能

ICode 总线:将 Flash 存储器指令接口与 Cortex-M3 内核的指令总线相连接,用于指 令预取; DCode 总线:将 Flash 存储器的数据接口与 Cortex-M3 内核的 DCode 总线相连接,用于 常量加载和调试访问; System 总线:将Cortex-M3 内核的 System 总线(外设总线)连接到总线矩阵;

总线结构中各单元的功能

DMA 总线:将DMA 的 AHB 主控接口与总线 矩阵相连; 总线矩阵:用于连接三个主动单元部件和三个 被动单元,负责协调和仲裁Cortex-M3 内核和 DMA 对 SRAM 的访问,仲裁采用轮换算法。 AHB/APB 桥:两个 AHB/APB 桥在 AHB 和 2 个 APB 总线之间提供完全同步连接。

3.3 位段

对别名区中某个字进行写操作,该字的第 0 位 将影响位段区中对应的位。 对别名区中某个字进行读操作,若位段区中对 应的位为 0 则读的结果为 0x00,若位段区中 对应的位为 1 则读的结果为0x01。 对别名区的读写可以实现对位段区中每一位的 原子操作,而且仅只需要一条指令即可实现。

第三章 STM32 处理器总线结构和存储器

3.1 系统总线构架 3.2 存储器的组织与映射 3.3 位段 3.4 启动配置

3.1 系统总线构架

四个主动单元:Cortex-M3 内核的 ICode 总 线(I-bus)、DCode 总线(D-bus)、 System 总线(S-bus)和通用 DMA(GPDMA)。 三个被动单元:内部SRAM、内部Flash 存储 器、AHB 到 APB 的桥(AHB2APBx,连接 所有的 APB 设备)。