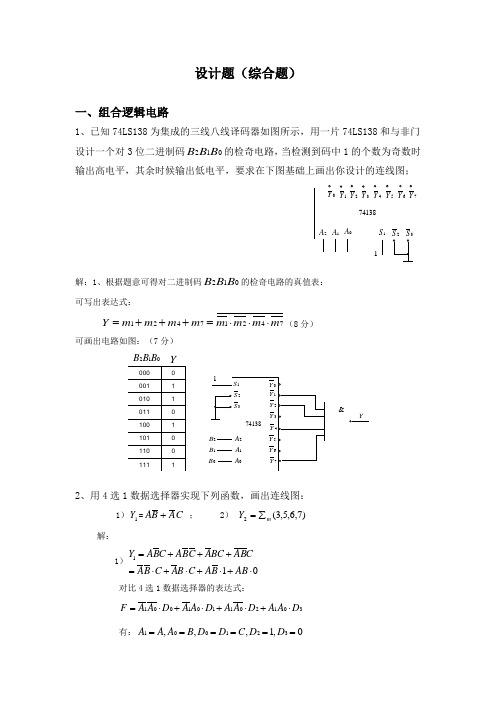

用74LS138和门电路设计1位二进制全减器

(完整版)基于QuartusII的数字电路仿真实验报告手册

数字电路仿真实验报告班级通信二班姓名:孔晓悦学号:10082207 作业完成后,以班级为单位,班长或课代表收集齐电子版实验报告,统一提交.文件命名规则如“通1_王五_学号”一、实验目的1. 熟悉译码器、数据选择器、计数器等中规模数字集成电路(MSI)的逻辑功能及其使用方法。

2. 掌握用中规模继承电路构成逻辑电路的设计方法。

3. 了解EDA软件平台Quartus II的使用方法及主要功能。

二、预习要求1. 复习数据选择器、译码器、计数器等数字集成器件的工作原理。

2. 熟悉所有器件74LS153、74LS138、74LS161的功能及外引线排列。

3.完成本实验规定的逻辑电路设计项目,并画出接线图,列出有关的真值表。

三、实验基本原理1.译码器译码器的逻辑功能是将每个输入的二进制代码译成对应的高、低电平信号。

译码器按功能可分为两大类,即通用译码器和显示译码器。

通用译码器又包括变量译码器和代码变换译码器。

变量译码器是一种完全译码器,它将一系列输入代码转换成预知一一对应的有效信号。

这种译码器可称为唯一地址译码器。

如3线—8线、4线—16线译码器等。

显示译码器用来将数字或文字、符号的代码译成相应的数字、文字、符号的电路。

如BCD-七段显示译码器等。

2.数据选择器数据选择器也陈伟多路选择器或多路开关,其基本功能是:在选择输入(又称地址输入)信号的控制下,从多路输入数据中选择某一路数据作为输出。

因此,数据选择器实现的是时分多路输入电路中发送端电子开关的功能,故又称为复用器。

一般数据选择器有n 个地址输入端,2n错误!未找到引用源。

个数据输入端,一个数据输出端或反码数据输出端,同时还有选通端。

目前常用的数据选择器有2选1、4选1、8选1、16选1等多种类型。

3.计数器计数器是一个庸医实现技术功能的时序部件,它不仅可以用来对脉冲计数,还常用作数字系统的定时、分频、执行数字运算以及其他一些特定的逻辑功能。

74LS161是4位同步二进制计数器,它除了具有二进制加法计数功能外,还具有预置数、保质和异步置零等附加功能。

数电组合逻辑电路习题含答案)

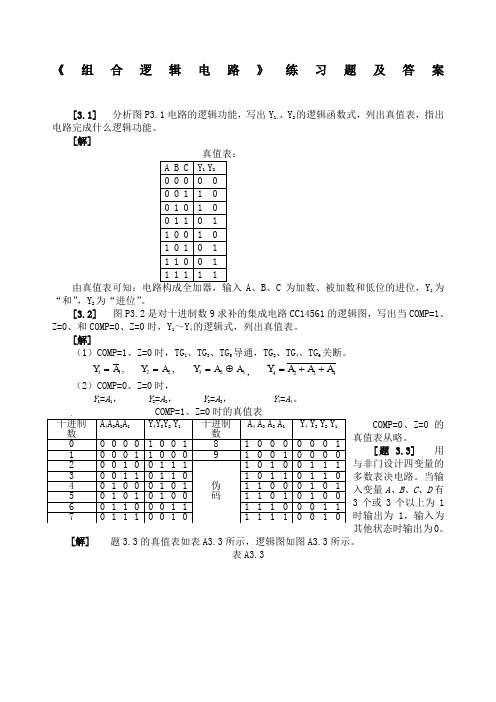

《组合逻辑电路》练习题及答案[3.1] 分析图P3.1电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]A 、B 、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

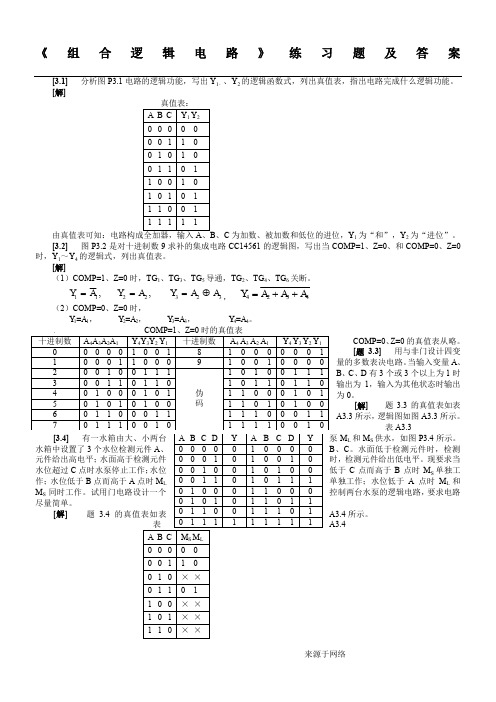

[3.2] 图P3.2是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

[解](1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。

3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++= (2)COMP=0、Z=0时,Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。

COMP=1、Z=0时的真值表 COMP=0、Z=0的真值表从略。

[题 3.3] 用与非门设计四变量的多数表决电路。

当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题3.3的真值表如表A3.3所示,逻辑图如图A3.3所示。

表A3.3[3.4] 有一水箱由大、小两台泵M L 和M S 供水,如图P3.4所示。

水箱中设置了3个水位检测元件A 、B 、C 。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

[解] 题3.4的真值表如表A3.4所示。

真值表中的C B A 、C B A 、C B A 、C AB 为约束项,利用卡诺图图A3.4(a)化简后得到: C B A M S +=, B M L =(M S、M L的1状态表示工作,0状态表示停止)。

【数电】组合逻辑电路习题(含答案)

《组合逻辑电路》练习题及答案[3.1]分析图P3.1电路的逻辑功能,写出Y1、、Y2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]、Z=0A、1时A3.3所示。

P3.4所示。

M S单独工点时M L和要求电路真值表中的C A 、C B A 、C B A 、C AB 为约束项,利用卡诺图图A3.4(a)化简后得到:C B A M S +=, B M L =(M S 、M L的1状态表示工作,0状态表示停止)。

逻辑图如图A3.4(b)。

[3.5] 设计一个代码转换电路,输入为4位二进制代码,输出为4位循环码。

可以采用各种逻辑功能的门电路来实现。

[解] 题3.5的真值表如表A3.5所示。

D 4、D 3与足上述控制要求的逻辑电路,给出控制四个指示灯状态的高、低电平信号。

74LS148的逻辑图如图P3.7所示,其功能表如表P3.7所示。

表 P3.7 74LS148的功能表A 、B 、C 、L 1、0为0000~2)工作,P3.10输 入21O 123用外加与非门实现之,如图A3.10所示。

[3.11] 画出用4线-16线译码器74LS154(参见题3.9)和门电路产生如下多输出逻辑函数的逻辑图。

[解]电路图如图A3.11所示。

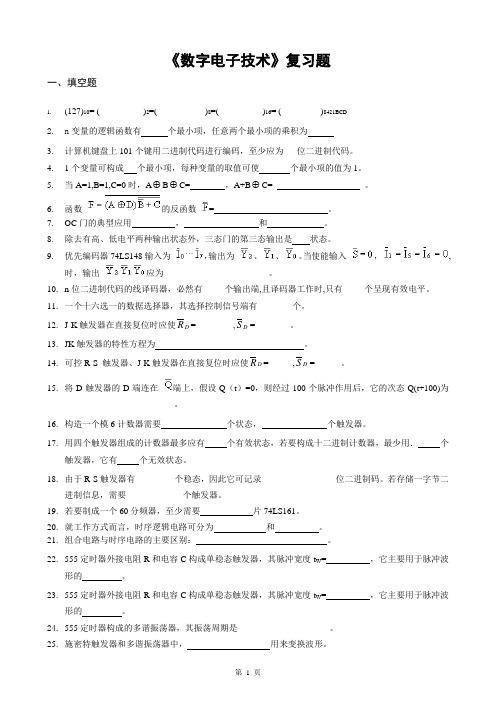

[3.12] 用3线-8线译码器74LS138和门电路设计1位二进制全减器电路。

输入为被减数、减数和来自低位的借位;输出为两数之差及向高位的借位信号。

[解] 设a i 为被减数,b i 为减数,c i-1为来自低位的借位,首先列出全减器真值表,然后将Di ,Ci 表达式写成非-与非形式。

最后外加与非门[3.13] 74LS153[解] [3.14]如表P3.14 [解][3.15][解] [3.16] [解] 与4选1[3.17][解] 则 D =41507632 如图A3.17所示。

[3.18] 用8选1数据选择器CC4512(参见题3.14)产生逻辑函数[解] 将Y 变换成最小项之和形式。

【数电】组合逻辑电路习题(含答案)

《组合逻辑电路》练习题及答案[3.1] 分析图P3.1电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]BCAC AB Y BC AC AB C B A ABC Y ++=+++++=21)(B 、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[3.2] 图P3.2是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

[解](1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。

3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++=(2)COMP=0、Z=0时,Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。

COMP =0、Z=0的真值表从略。

[题3.3] 用与非门设计四变量的多数表决电路。

当输入变量A 、B 、C 、D 有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题3.3的真值表如表A3.3所示,逻辑图如图A3.3所示。

ABCD D ABC D C AB CD B A BCD A Y ++++=BCD ACD ABC ABC +++=B C D A C D A B D A B C ⋅⋅⋅=[3.4] 有一水箱由大、小两台泵M L 和M S 供水,如图P3.4所示。

水箱中设置了3个水位检测元件A 、B 、C 。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

[解] 题3.4的真值表如表A3.4所示。

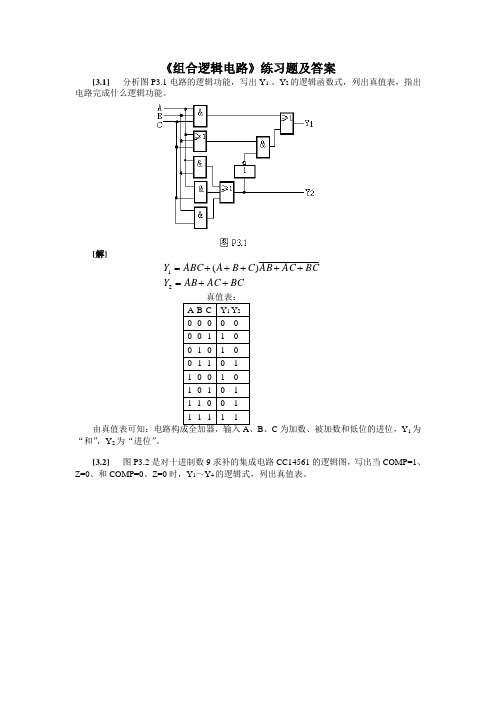

复习题(数电)

《数字电子技术》复习题一、填空题1.(127)10= ( )2=( )8=( )16= ( )8421BCD2. n 变量的逻辑函数有 个最小项,任意两个最小项的乘积为3. 计算机键盘上101个键用二进制代码进行编码,至少应为___位二进制代码。

4. 1个变量可构成 个最小项,每种变量的取值可使 个最小项的值为1。

5. 当A=1,B=1,C=0时,A ⊕B ⊕C= ,A+B ⊕C= 。

6. 函数 的反函数 = 。

7. OC 门的典型应用 , 和 。

8. 除去有高、低电平两种输出状态外,三态门的第三态输出是____状态。

9. 优先编码器74LS148输入为```,输出为、、。

当使能输入,,时,输出应为________________________。

10. n 位二进制代码的线译码器,必然有_____个输出端,且译码器工作时,只有_____个呈现有效电平。

11. 一个十六选一的数据选择器,其选择控制信号端有________个。

12. J-K 触发器在直接复位时应使D R =________ ,D S =________。

13. JK 触发器的特性方程为 。

14. 可控R-S 触发器、J-K 触发器在直接复位时应使D R =_____ ,D S =______。

15. 将D 触发器的D 端连在 端上,假设Q (t )=0,则经过100个脉冲作用后,它的次态Q(t+100)为_________________________。

16. 构造一个模6计数器需要 个状态, 个触发器。

17. 用四个触发器组成的计数器最多应有 个有效状态,若要构成十二进制计数器,最少用. 个触发器,它有 个无效状态。

18. 由于R-S 触发器有_________个稳态,因此它可记录_________________位二进制码。

若存储一字节二进制信息,需要_____________个触发器。

19. 若要制成一个60分频器,至少需要 片74LS161。

[题38]写出图p38中z1、z2、z3的逻辑函数式,并化简为最

![[题38]写出图p38中z1、z2、z3的逻辑函数式,并化简为最](https://img.taocdn.com/s3/m/1c0ac2b40129bd64783e0912a216147917117ebf.png)

[题3.8] 写出图P3.8中Z 1、Z 2、Z 3的逻辑函数式,并化简为最简的与或表达式。

译码器74LS42的逻辑图见图3.3.10。

图P3.8 [解]⎪⎪⎩⎪⎪⎨⎧++=⋅⋅=++=⋅⋅=++=⋅⋅=Q P N M Q NP M PQ N M Y Y Y Z Q P N M Q P N M Q P N M Y Y Y Z NPQM Q P N M Q P N M Y Y Y Z 963385227411 利用伪码(视为约束项)化简后得到⎪⎪⎩⎪⎪⎨⎧++=++=++=PQN Q NP MQ Z QP N Q P N Q M Z NPQ Q P N Q P N M Z 321[题3.10] 试画出用3线-8线译码器74LS138(见图3.3.8)和门电路产生如下输出函数的逻辑图。

⎪⎩⎪⎨⎧+=++==CAB C B Y BC C B A C B A Y AC Y 321 [解]640374312751Y Y Y C AB C B A C B A C AB C B Y Y Y Y Y ABC C B A BC A C B A BC C B A C B A Y Y Y ABC C B A AC Y =++=+==+++=++==+==M N PQ312图A3.10[题3.11] 画出用4线-16线译码器74LS154(参见题3.9)和门电路产生如下多输出逻辑函数的逻辑图。

⎪⎪⎩⎪⎪⎨⎧=+++=+++=BA Y D ABC D C AB CD B A BCD A Y DC B AD C B A D C B A D C B A Y 321[解]⎪⎪⎩⎪⎪⎨⎧===465431413117284211Y Y Y Y Y Y Y Y Y Y YY Y Y Y图A3.11B C 1132B D 213A[题3.12] 用3线-8线译码器和门电路设计1位二进制全减器电路。

输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

数字电路复习题(含答案)

一、填空题:1.在计算机内部,只处理二进制数;二制数的数码为1 、0两个;写出从(000)2依次加1的所有3位二进制数:000、001、010、011、100、101、110、111 。

2.13=(1101)2;(5A)16=(1011010)2;(10001100)2=(8C)16。

完成二进制加法(1011)2+1=(1100)23.写出下列公式:= 1 ;= B ;= A+B ;=BA 。

4.含用触发器的数字电路属于时序逻辑电路(组合逻辑电路、时序逻辑电路)。

TTL、CMOS电路中,工作电压为5V的是TTL ;要特别注意防静电的是CMOS 。

5.要对256个存贮单元进行编址,则所需的地址线是8 条。

6.输出端一定连接上拉电阻的是OC 门;三态门的输出状态有1 、0 、高阻态三种状态。

7.施密特触发器有 2 个稳定状态.,多谐振荡器有0 个稳定状态。

8.下图是由触发器构成的时序逻辑电路。

试问此电路的功能是移位寄存器,是同步时序电路(填同步还是异步),当R D=1时,Q0Q1Q2Q3= 0000 ,当R D=0,D I=1,当第二个CP脉冲到来后,Q0Q1Q2Q3= 0100 。

(图一)1.和二进制数(111100111.001)等值的十六进制数是( B )A.(747.2)16B.(1E7.2)16C.(3D7.1)16D.(F31.2)161D C1FF01DC1FF01DC1FF01DC1FF0R D R D R D R D Q3Q2Q1Q0D IRCP2.和逻辑式B A C B AC ++相等的式子是( A )A .AC+BB . BCC .BD .BC A +3.32位输入的二进制编码器,其输出端有( D )位。

A. 256B. 128C. 4D. 5 4.n 位触发器构成的扭环形计数器,其无关状态数为个( B )A .2n -nB .2n -2nC .2nD .2n -15.4个边沿JK 触发器,可以存储( A )位二进制数A . 4B .8C .166.三极管作为开关时工作区域是( D )A .饱和区+放大区B .击穿区+截止区C .放大区+击穿区D .饱和区+截止区7.下列各种电路结构的触发器中哪种能构成移位寄存器( C ) A .基本RS 触发器B .同步RS 触发器C .主从结构触发器8.施密特触发器常用于对脉冲波形的( C )A .定时B .计数C .整形1.八进制数 (34.2 ) 8 的等值二进制数为 11100.01 ;十进制数 98 的 8421BCD 码为 10011000 。

组合逻辑电路 课后答案

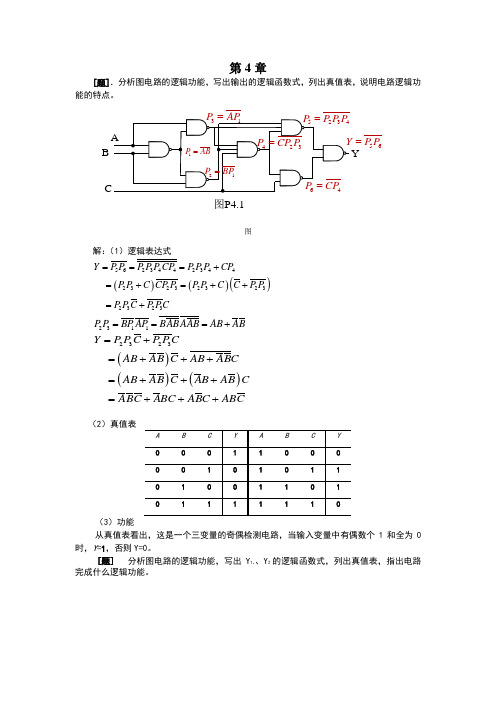

第4章[题].分析图电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题] 分析图电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())由真值表可知:、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题] 图是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG1、TG3、TG5导通,TG2、TG4、TG6关断。

,(2)COMP=0、Z=0时,Y1=A1,Y2=A2,Y3=A3,Y4=A4。

、COMP=1、Z=0时的真值表、Z=0的真值表从略。

[题] 用与非门设计四变量的多数表决电路。

当输入变量A、B、C、D有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题的真值表如表所示,逻辑图如图(b)所示。

长沙理工大学数字电子技术基础试卷数电试卷题库(01-10)

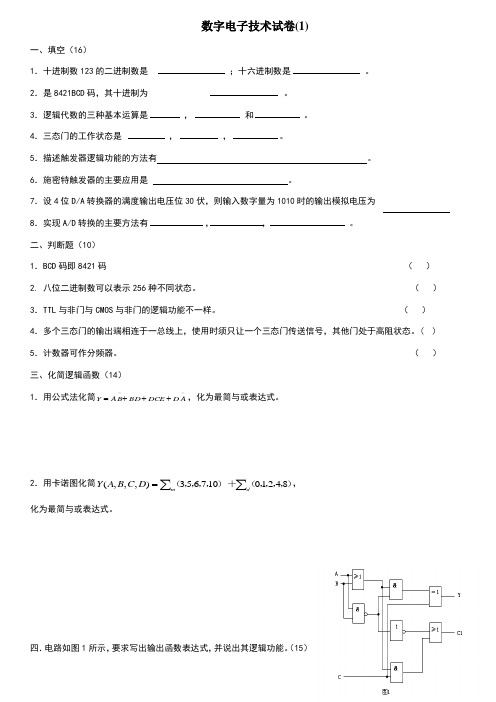

数字电子技术试卷(1)一、填空(16)1.十进制数123的二进制数是 ;十六进制数是 。

2.是8421BCD 码,其十进制为。

3.逻辑代数的三种基本运算是 , 和。

4.三态门的工作状态是 ,,。

5.描述触发器逻辑功能的方法有。

6.施密特触发器的主要应用是 。

7.设4位D/A 转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为 8.实现A/D 转换的主要方法有 , , 。

二、判断题(10)1.BCD 码即8421码 ( ) 2. 八位二进制数可以表示256种不同状态。

( ) 3.TTL 与非门与CMOS 与非门的逻辑功能不一样。

( )4.多个三态门的输出端相连于一总线上,使用时须只让一个三态门传送信号,其他门处于高阻状态。

( ) 5.计数器可作分频器。

( ) 三、化简逻辑函数(14) 1.用公式法化简--+++=A D DCE BD B A Y ,化为最简与或表达式。

2.用卡诺图化简∑∑=m d D C B A Y ),,,,()+,,,,(84210107653),,,(, 化为最简与或表达式。

五.触发器电路如图2(a),(b)所示,⑴写出触发器的次态方程;⑵对应给定波形画出Q端波形(设初态Q=0)(15)六.试用触发器和门电路设计一个同步的五进制计数器。

(15)七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O,V C的工作波形,并求出振荡频率。

(15)数字电子技术试卷(2)一.填空(16)1.十进制数的二进制数是 ;十六进制数是 。

2.逻辑代数中逻辑变量得取值为 。

3.组合逻辑电路的输出状态只与 有关而与电路 。

4.三态门的输出有 ,三种状态,当多个三态门的输出端连在一根总线上使用时,应注意。

5.触发器的基本性质有。

6.单稳态触发器的主要应用是 。

7.设6位D/A 转换器的满度输出电压位伏,则输入数字量为110111,输出模拟电压为8.一个8K 字节的EPROM 芯片,它的地址输入端的个数是 。

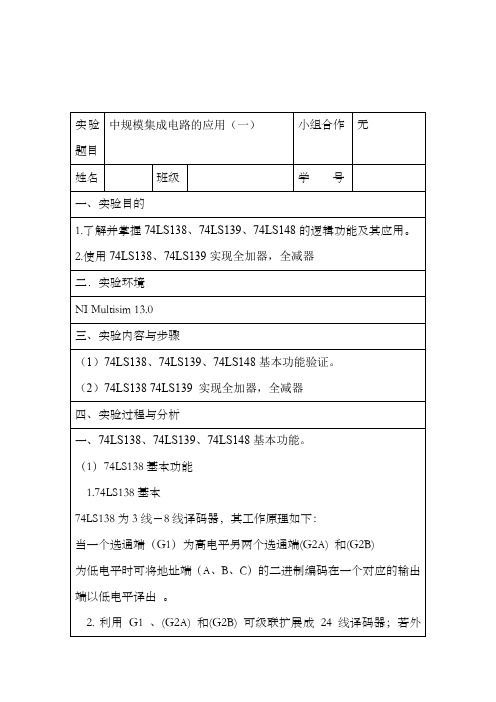

电子技术基础B中规模集成电路的应用(一)实验报告

接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138 还可作数据分配器3.3 线-8 线译码器74LS138的逻辑图与功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7 个输出引脚全为高电平1。

如果出现两个输出引脚同时为0 的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出(2)74LS139基本功能当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一个对应的输出端以低电平译出。

若将选通端(G1)作为数据输入端时,139 还可作数据分配器。

管脚图内部逻辑引脚功能引出端符号:A、B:译码地址输入端G1、G2 :选通端(低电平有效)Y0~Y3:译码输出端(低电平有效)真值表(3)74LS148基本功能74LS148是8 线-3 线优先编码器,共有54/74148 和54/74LS148两种线路结构型式,将8 条数据线(0-7)进行3 线(4-2-1)二进制(八进制)优先编码,即对最高位数据线进行译码。

利用选通端(EI)和输出选通端(EO)可进行八进制扩展。

管脚图管脚介绍0-7 编码输入端(低电平有效)EI 选通输入端(低电平有效)A0、A1、A2 三位二进制编码输出信号即编码输出端(低电平有效)GS 片优先编码输出端即宽展端(低电平有效)EO 选通输出端,即使能输出端逻辑图真值表由74ls148真值表可列输出逻辑方程为:A2 = (I4+I5+I6+I7)IEA1 = (I2I4I5+I3I4I5+I6+7)·IEA0 = (I1I2I4I6+I3I4I6+I5I6+I7)·IE工作原理该编码器有8个信号输入端,3个二进制码输出端。

此外,电路还设置了输入使能端EI,输出使能端EO和优先编码工作状态标志GS。

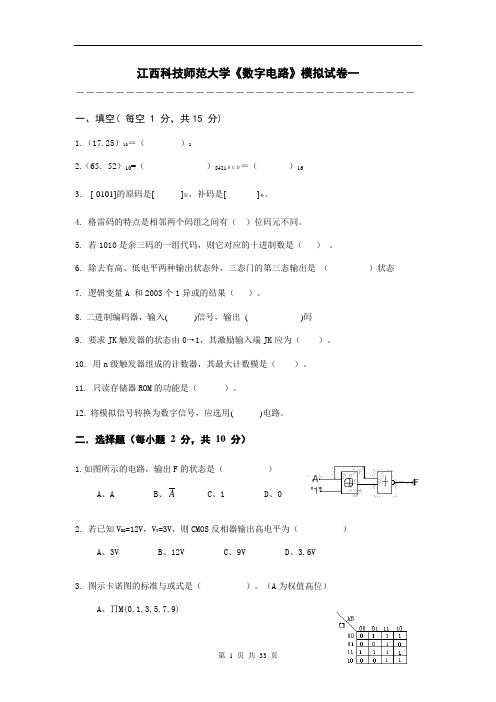

数电模拟试卷

江西科技师范大学《数字电路》模拟试卷一――――――――――――――――――――――――――――――――――一、填空( 每空 1 分,共15 分)1.(17.25)10=()22.(65.52)10=()8421BCD=()163. [-0101]的原码是[ ]原,补码是[ ]补。

4. 格雷码的特点是相邻两个码组之间有()位码元不同。

5. 若1010是余三码的一组代码,则它对应的十进制数是()。

6. 除去有高、低电平两种输出状态外,三态门的第三态输出是()状态7. 逻辑变量A 和2003个1异或的结果()。

8. 二进制编码器,输入( )信号,输出( )码9. 要求JK触发器的状态由0→1,其激励输入端JK应为()。

10. 用n级触发器组成的计数器,其最大计数模是()。

11. 只读存储器ROM的功能是()。

12. 将模拟信号转换为数字信号,应选用()电路。

二.选择题(每小题 2 分,共10 分)1.如图所示的电路,输出F的状态是()A、AB、AC、1D、02. 若已知V DD=12V,V T=3V,则CMOS反相器输出高电平为()A、3VB、12VC、9VD、3.6V3. 图示卡诺图的标准与或式是()。

(A为权值高位)A、∏M(0,1,3,5,7,9)B 、∏M(0,1,2,5,6,9)C 、∑M(2,4,6,8,10,11,12,13,14,15)D 、∑M(3,4,7,8,10,11,12,13,14,15)4. 设某函数的表达式F=A+B ,若用4选1多路选择器(数据选择器)来设计,则数据端D 0D 1D 2D 3的状态是( )。

(设A 为权值高位)A 、0001B 、0111C 、0101D 、10105. 三极管作为开关时工作区域是( )。

A. 饱和区+放大区B. 击穿区+截止区C. 放大区+击穿区D. 饱和区+截止区三.化简下列逻辑函数,并表示为最简与或式( 每小题5分,共10 分)1.F(A,B,C,D)=∑m (1,3,4,5,10,11,12,13,14,15) 2. F(A,B,C,D)=∑m (3,4,5,10,11,12) +∑d (1,2,13)四 判断下列函数是否存在险象,若有则消除。

用74LS138和门电路设计1位二进制全减器

1、用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号(74LS138的逻辑框图如图1.1所示)。

CO-—-向高位的借位; Y ———两位数之差;C I —-—来自低位的借位;

Y=m 1+m 2+m 4+m 7;CO=m 3+m 5+m 6+m 7;

其逻辑图如下:

1

2、试用8选1数据选择器74LS152和必要的门电路设计一个路灯控制电路,要求在四个不同的地方都能独立地开灯和关灯,画出逻辑电路图(74LS152的逻辑框图如图2.1所示)。

7

D1D0

A0

A1

A2S 152 m m

3,210代表亮,或是开关闭合;0代表灯灭;Y=A3(m1+m2+m4+m0)

对照着所给的逻辑表达式可得:

D0=D1=D2=D4=A3

D3=D5=D6=D7=0; A2=A2;A1=A1;A0=A0;

故逻辑图如下所示:

A。

数字电子技术基础简明教程(第三版)余孟尝第三章-完成ok

第三章 组合逻辑电路【】 分析图P3.1电路的逻辑功能,写出Y 1、Y 2的逻辑函数式,列出真值表,指出电路完成了什么逻辑功能.Y 1【解】1()Y ABC A B C AB AC BC ABC ABC ABC ABC=+++•++=+++2Y AB BC AC =++由真值表可见,这是一个全加器电路。

A 、B 、C 为加数、被加数和来自低位的进位,Y 1是和,Y 2是进位输出。

【】 图3.2是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1;Z=0和COMP=0,Z=0时Y 1,Y 2,Y 3,Y 4的逻辑式,列出真值表。

Y 1Y 2Y 3Y 4A 1A 2A 3A 4Z【解】(1)COMP=1、Z=0时输出的逻辑式为11223234234Y A Y A Y A A Y A A A⎧=⎪=⎪⎨=⊕⎪⎪=++⎩ 〔2〕COMP=0、Z=0时输出的逻辑式为11223344Y A Y A Y A Y A =⎧⎪=⎪⎨=⎪⎪=⎩〔即不变换,真值表从略〕3个或3个以上为1时输出1,输入为其他状态时输出0。

【解】Y ABCD ABCD ABCD ABCD ABCD ABC ABD ACD BCD ABC ABD ACD BCD=++++=+++=•••B D Y【】 有一水箱由大、小两台水泵M L 、M S 供水,如图P3.4所示.水箱中设置了3个水位检测元件A、B 、C 。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C 点时水泵停止工作;水位低于C 点高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 、M S 同时工作。

试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。

【解】图P3.4M L真值表中的ABC 、ABC 、ABC 、ABC 为约束项,利用卡诺图【图A3.4(a)】化简后得到S L M A BCM B⎧=+⎪⎨=⎪⎩ 〔M S 、M L 的1状态表示工作,0状态表示停止〕 逻辑图如图A3.4(b).S M A BC =+L M B =〔a 〕(b)A B CM SM L【】。

数字综合题

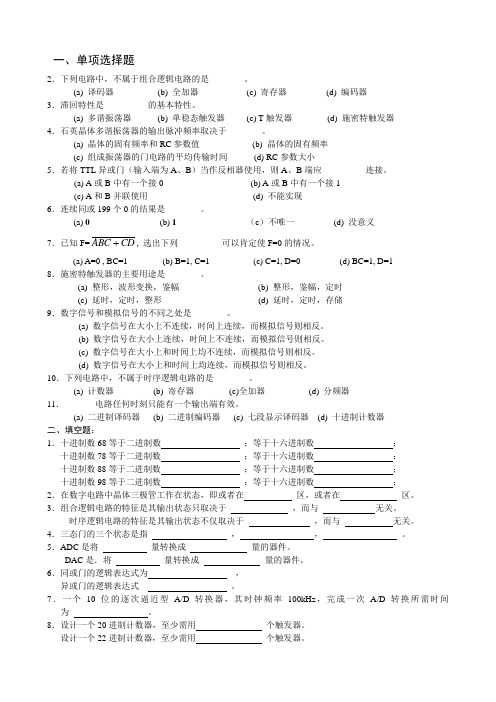

一、单项选择题2.下列电路中,不属于组合逻辑电路的是________。

(a) 译码器(b) 全加器(c) 寄存器(d) 编码器3.滞回特性是________ 的基本特性。

(a) 多谐振荡器(b) 单稳态触发器(c) T触发器(d) 施密特触发器4.石英晶体多谐振荡器的输出脉冲频率取决于________。

(a) 晶体的固有频率和RC参数值(b) 晶体的固有频率(c) 组成振荡器的门电路的平均传输时间(d) RC参数大小5.若将TTL异或门(输入端为A、B)当作反相器使用,则A、B端应________ 连接。

(a) A或B中有一个接0 (b) A或B中有一个接1(c) A和B并联使用(d) 不能实现6.连续同或199个0的结果是________。

(a) 0(b) 1 (c)不唯一(d) 没意义ABC , 选出下列________ 可以肯定使F=0的情况。

7.已知F=CD(a) A=0 , BC=1 (b) B=1, C=1 (c) C=1, D=0 (d) BC=1, D=18.施密特触发器的主要用途是________。

(a) 整形,波形变换,鉴幅(b) 整形,鉴幅,定时(c) 延时,定时,整形(d) 延时,定时,存储9.数字信号和模拟信号的不同之处是________。

(a) 数字信号在大小上不连续,时间上连续,而模拟信号则相反。

(b) 数字信号在大小上连续,时间上不连续,而模拟信号则相反。

(c) 数字信号在大小上和时间上均不连续,而模拟信号则相反。

(d) 数字信号在大小上和时间上均连续,而模拟信号则相反。

10.下列电路中,不属于时序逻辑电路的是_______ 。

(a) 计数器(b) 寄存器(c)全加器(d) 分频器11.______ 电路任何时刻只能有一个输出端有效。

(a) 二进制译码器(b) 二进制编码器(c) 七段显示译码器(d) 十进制计数器二、填空题:1.十进制数68等于二进制数;等于十六进制数;十进制数78等于二进制数;等于十六进制数;十进制数88等于二进制数;等于十六进制数;十进制数98等于二进制数;等于十六进制数;2.在数字电路中晶体三极管工作在状态,即或者在区,或者在区。

《数字电子技术基础》课后习题及参考答案

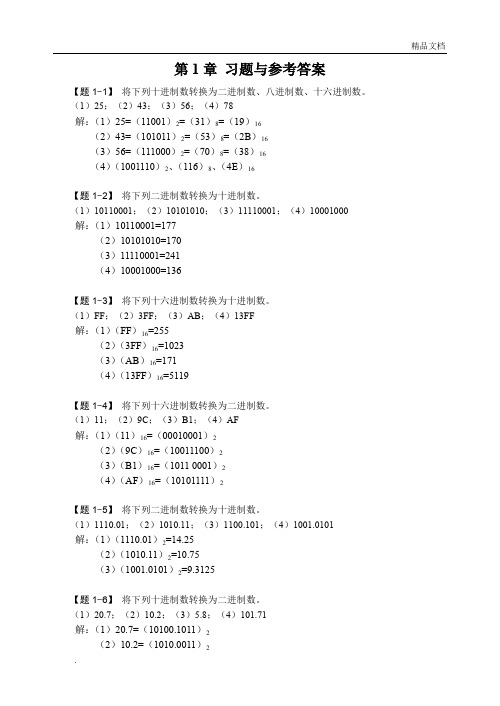

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

山东科技大学考研专业课真题_电子技术2014

+5V R1 D

3

VCC vOD 7

TH

RD 8 4

V0

R2 R3 C

6 2

NE555

3

vo

TR

7

5 VCO 0.01μ F 图5

1

GND

输

入

输

出 RD0 1 11 1VI12 VCC 3 2 VCC 3 2 VCC 3 2 VCC 3

+15V R1 Ui D1 D2 R2

图 10

+ UO R L =8Ω

-

-15V

十、计算题(本题 15 分)

电路如图 11 所示,已知D z 的电压U Z = 4V,三级管T饱和时,U CES =2V,R 1 =330, R 2 =100,R 3 =100,R Ww =300,C 1 足够大。 1.求稳压电路输出U 0 的调节范围是多少? 2.估算输入电压有效值U 2 ,电容两端的直流电压U I 各约是多少?

七、分析题(本题 15 分)

1.试分析图 8 电路,说明电路是什么类型的反馈电路? 2.假设集成运算放大 器为理想运放,请写出 电路的电压放大倍数A uf R3 的表达式 。 R1 + - Ui R2 +V CC R4 + Uo -

八、分析计算题(本题 15)

-V EE 电路如图 9 所示,A 1 、A 2 、 图8 A 3 均为理想运放、电源电 压为±15V。问: 1. A 1 ~A 3 分别组成何种基本运算电路。 2. A 1 ~A 3 输入端那些是虚地、虚短、即不虚地也不虚短。 3. 已知Ui 1 =0.5V,Ui 2 =1V,Ui 3 = - 4V,Ui 4 = 2V,求U O1 ,U O2 和U O3 。 30KΩ 20KΩ 2KΩ K=2

设计题2

四个地方的开关分别用A、B、C、D表示,灯用Z表示。按4位循环顺序排序列A、B、C、D取值,列真值表

真值表:

选用8选1数据选择器74151,其输出信号表达式为

令 、 、 ,比较 , 的表达式,可得

、 、 、 、 、 、 、

路灯控制电路:

3.19

16、电话室需要对四种电话进行编码控制,优先级别最高的是火警电话,其次是急救电话,第三是工作电话,第四是生活电话,试用与非门或者或非门设计该控制电路。

对照图5(a)和(b)可确定D0~D7,其方法是:

图(b)中Di对应于图(a)中的方格内全为1,则此Di= 1;反之,若方格内全为0,则Di= 0。

图(b)中Di对应于图(a)中的方格内有0也有1,则Di应为1格对应的输入变量的积之和(此积之和式中只能含余下变量D)。

由此得Di为

D0=0 D1=1 D2=1 D3=0 D4=1 D5=1 D6=0 D7=1

3.7

9、分别设计能够实现下列要求的组合电路,输入是4位二进制正整数 。

1)能被2整除时输出为1,否则为0。

2)能被5整除时输出为1,否则为0。

解:

真值表如表:

由真值表可直接得 , 的卡诺图:

的卡诺图

可得

逻辑图:

10、分别设计能够实现下列要求的组合电路,输入是4位二进制正整数 。

1)大于或等于5时输出为1,否则为0。

2)

用一片就可以实现,逻辑图见图;

2、用两片集成译码器74LS138和与非门,实现下列函数:

解:

画出Y的卡诺图:

得到Y的函数最简式:

可以看出利用约束条件后,变量A已经没有了,所以Y可以看成变量B、C、D的函数,其卡诺图可重新画成:

电子技术基础第9-13章的学习参考习题解答

解:去耦电容的作用是消除芯片动作对电源电流的影响,或是消除电源电压波动对芯片的影响,因此越接近芯片的电源引脚越好。

【题

解:一个是输出瞬变时间,门电路的输出从一个状态向另外一个状态转换需要的过渡时间。

另外一个是传输延迟时间,是输入信号变化到输出信号变化之间需要的时间。

【题

图题3-16

解:(a)导通;(b)截止;(c)导通;(d)截止

【题

解:1%=1/100>1/2n,有2n>100

可知n应该大于等于7,因此D/A转换器的位数至少7位。

【题

解:偏移误差是D/A转换器输入数字为0时,输出电压不为0,输出电压的大小就是偏移误差,偏移误差可以用在输出电压上叠加电压的方法消除。

【题

解:引起增益误差。

【题

解:

【题

解:并联A/D转换速度最快,Δ-Σ位数最多。

解:

D

C

B

A

A1

A0

GS

EO

0

0

0

0

0

0

0

1

0

0

0

1

0

0

1

0

0

0

1

X

0

1

1

0

0

1

X

X

1

0

1

0

1

X

X

X

1

1

1

0

得到:

逻辑电路如下图所示。

【题4-10】用3线-8线译码器74LS138和与非门实现如下多输出函数。

解: =

=

【题4-11】试用3线-8线译码器74LS138和门电路实现一位二进制全减器(输入为被减数、减数与来自低位的借位;输出为差和向高位的借位)。要求用按键输入减数、被减数和进位,发光二极管显示减法结果。

数字电子技术实验报告(学生版)

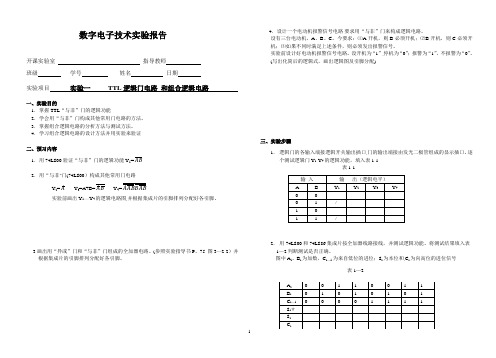

数字电子技术实验报告开课实验室 指导教师 班级 学号 姓名 日期实验项目 实验一 TTL 逻辑门电路 和组合逻辑电路一、实验目的1.掌握TTL “与非”门的逻辑功能.2.学会用“与非”门构成其他常用门电路的方法。

3.掌握组合逻辑电路的分析方法与测试方法。

4.学习组合逻辑电路的设计方法并用实验来验证.二、预习内容1.用74LS00验证“与非”门的逻辑功能Y 1=AB 2.用“与非"门(74LS00)构成其他常用门电路Y 2=A Y 3=A+B=B A Y 4=AB B AB A实验前画出Y 1——Y 4的逻辑电路图,并根据集成片的引脚排列分配好各引脚。

3.画出用“异或”门和“与非”门组成的全加器电路。

(参照实验指导书P 。

75 图3—2-2)并根据集成片的引脚排列分配好各引脚。

4.设计一个电动机报警信号电路.要求用“与非”门来构成逻辑电路。

设有三台电动机,A 、B 、C 。

今要求:⑴A 开机,则B 必须开机;⑵B 开机,则C 必须开机;⑶如果不同时满足上述条件,则必须发出报警信号。

实验前设计好电动机报警信号电路。

设开机为“1”,停机为“0”;报警为“1”,不报警为“0”。

(写出化简后的逻辑式,画出逻辑图及引脚分配)三、实验步骤1. 逻辑门的各输入端接逻辑开关输出插口,门的输出端接由发光二极管组成的显示插口。

逐个测试逻辑门Y 1-Y 4的逻辑功能,填入表1-1表1-12. 用74LS00和74LS86集成片按全加器线路接线,并测试逻辑功能。

将测试结果填入表 1—2.判断测试是否正确。

图中A i 、B i 为加数,C i —1为来自低位的进位;S i 为本位和,C i 为向高位的进位信号.表1—23.根据设计好的电动机报警信号电路用74LS00集成片按图接线,并经实验验证.将测试结果填入表1—3。

表1-3四、简答题1.Y4具有何种逻辑功能?2.在实际应用中若用74LS20来实现Y=AB时,多余的输入端应接高电平还是低电平? 3.在全加器电路中,当A i=0,S i*=1,C i=1时C i—1=?数字电子技术实验报告开课实验室 指导教师 班级 学号 姓名 日期 实验项目 实验二 组合逻辑电路的设计一、实验目的1.掌握用3线- 8线译码器74LS138设计组合逻辑电路。

胡全连版数字逻辑第3章习题解答

f 习题三3.1写出如图判p3.1中各逻辑图的逻辑表达式,并化简成最简与或表达式。

BCBC(a) (b)AA C(c)(d)图p3.1题3.1逻辑图解:(a )C B C B A C B C B A F +=•=(b) 1=)+(+)+(+)+(=+•+•+=C B B A C A C B B A C A F(c)CA BC AB C B A AB C B A AB F++=)⊕(+=)⊕(+=1 ABC C B A C B A C B A C B A F +++=⊕⊕=2(d)F=A⊙B⊙C= ABC C B A C B A C B A C AB B A C AB B A +++=•)+(+•+3.2、3.2、化简下列逻辑函数,并用与非门和或非门实现。

解:(1)∑)7,3,2,0(=),,(m C B A F与非门实现:BC B A BC B A F •=+=或非门实现:C B C A F +=,C B C A C B C A F F +++=)+)(+(== (2) C A C B AB C B A F ++=),,( 解:与非门实现:AB C AB C F •=+=或非门实现:C B C A F +=,C B C A C B C A F F +++=)+)(+(== ┏ (^ω^)=☞(3) ABD D C B C A B A D C B A F +++=),,,( 解:与非门实现:BCD AC AB BCD AC AB F ••=++= 或非门实现:C B D A C A B A F +++=,C BD A C A B A C B D A C A B A F F +++++++=)+)(+)(+)(+(==(4) ∑)15,14,10,8,2,0(=),,,(m D C B A F解:与非门实现:ABC BD ABC BD F •=+= 或非门实现:C B D B D A B A F +++=,C BD B D A B A C B D B D A B A F F +++++++=)+)(+)(+)(+(==(图略)3.3、分析如图p3.2所示组合逻辑电路,写出输出函数表达式,列出真值表,说明电路的逻辑功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

同的地方都能独立地开灯和关灯,画出逻辑电路图(74LS152 的逻辑框图如图所示)。

m

m

A2 A1 A0

74L S152

D0

D1

D2

Y

D3

D4

D5

D6

D7

7

Y D0 A2 A1 A0 D7 A2 A1A0 Dimi i0

m

m

A3

A2

A1 图 7A40LS152 的逻Y辑框图

0

0

0

0

0

0

0

1、用 3 线—8 线译码器 74LS138 和门电路设计 1 位二进制全减器,输入为被减数、减数和 来自低位的借位;输出为两数之差和向高位的借位信号(74LS138 的逻辑框图如图所示)。

CO---向高位的借位; 真值表如下:其中 A2=A0;A1=A1;A0=CI

Y---两位数之差;CI---来自低位的借位;

D0=D1=D2=D4=A3 D3=D5=D6=D7=0; A2=A2;A1=A1;A0=A0;

故逻辑图如下所示:

A2 A1 A0 A3

1

A2 A1 A0

D0

D1 74LS152

D2

Y

D3

D4

D5

D6

D7

\1

Y

Байду номын сангаас

A2

A1

A0

Y

CO

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

故:

Y=m1+m2+m4+m7;CO=m3+m5+m6+m7;

其逻辑图如下:

Y7

A0

A2

Y6

A1

A1

Y5

CI

A0

Y4

Y3

S1

Y2

S2 S0

Y1

1

Y0

&

CO

&

Y

2、试用 8 选 1 数据选择器 74LS152 和必要的门电路设计一个路灯控制电路,要求在四个不

0

1

1

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

0

0

1

1

×

0

1

0

1

×

0

1

1

0

×

0

1

1

1

×

1

0

0

1

×

1

0

1

0

×

1

1

0

0

×

1

1

0

1

×

1

0

1

1

×

1

1

1

0

×

1

1

1

1

×

其中 A3,A2,A1,A0 分别代表四个不同的地方;Y 代表灯;1 代表亮,或是开关闭合;0 代表灯灭;

Y=A3(m1+m2+m4+m0)

对照着所给的逻辑表达式可得: