中频数字接收机的设计

一种高性能数字中频接收机的设计及实现

样 中的直 流分 量 , 影响 了数 字 中频 的低端 性 能 时 同

根 据 式 1 AD 的 采 样 率 和 中频 频 率 之 间 为 等 式 , , 限

制 了 中频 频 率和 AD 采样 率 的 选择 , 对 中频 频 率 而

较 高 的 系 统 , 可 能 无 法 找 到 合 适 的 AD 采 样 率 ; 很 同 时这类 方 案只适 用于全 相参 雷达 系统而 无法 用于 中 频 相 参 雷 达 。 用 NC 采 O+ L F的 数 字 中 频 目 前 在 通 P 信 系 统 中 应 用 较 多 , 由 于 目前 雷 达 系 统 中 频 综 一 但

信 号 的 频 谱 分 布 并 不 充 满 整 个 频 带 , 以 可 欠 采 样 所 而 保 证 信 号 的 有 用 频 谱 不 产 生 混 迭 , 而 得 到 正 确 从

2 2 联 合 相干中频 处理 .

的 幅 相 误 差 较 大 , IQ 的 幅 相 误 差 会 严 重 影 响 雷 而 / 达 的 整 机 性 能 行复杂 的校 正处 理。。 字中频利 用 中频直 接采 样 , 数 通 过 数 字 信 号 处 理 获 得 视 频 IQ 信 号 , 有 IQ 镜 / 具 / 频 抑 制 比 高 、 性 动 态 范 围 大 、 积 小 、 量 轻 、 致 线 体 重 一 性 好等 优点 , 现 代高 性 能雷达 的发展 方 向。 是

维普资讯

Hale Waihona Puke 现 代 雷 达 第 1期

一

种 高 性 能数 字 中频接 收机 的设 计及 实现

王金础 杨 正 远

( 流 信 息技 术 有 限 公 司 成 都 6 0 2 ) 潮 10 1

【 要 】 采 用 中频 回赦 和 中 颤相 参 信 号 联 合 相 干 处 理 , 场 采 样 - 场 处 理 - 程 传 话 的体 系 结 构 实 现 了 高性 摘 现 现 远 能 数 字 中频 雷 达 接 收 机 . 性能 可 以满 足 现 代 高性 能 雷 达 系 统 的需 要 。 其 【 键词 】 敷 字 中频 . I 滤渡 , 性 动 态 范 围 . 频 抑 制 比 美 FR 线 镜

600Mbit/s高速数传数字中频接收机DFT结构设计

CHEN Da—u ZHANG — a g f Ery n

( o eeo lc oi SineadE gneig Naoa nvri f ees eh o g ,C agh ,H n rv c 10 3 C l g f et nc c c n nier , t nl iesyo fneT cn l y h sa u a Poi e4 0 7 ) l E r e n i U t D o n n n

fr (D T rhtc r o ra bn ii F rci rwt P A ipe n t n o r rmm beci r o m I F )aci t e fabod a ddg a I ee e i F G m l eu t l v h met i napo a al hp f ao g o 6 0 i s i . t dt a s si n f c v nbn P K moua o ddmoua o T eaci c r a 0 Mb / s r e a t nmi o ade et ei—adQ S dlt na e d l in h ht t ef — t h h a ar sn i i n t r eu e

字 中频接 收机 D T并行 结构 , 突 出特 点是在频 率域 上 实现平 方根升 余 弦特 性 的 匹配 滤波 和符号 同步 的定 时 F 其

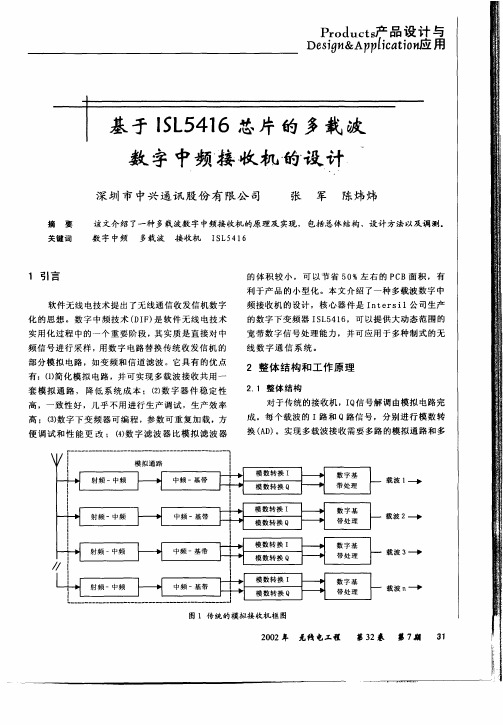

基于ISL5416芯片的多载波数字中频接收机的设计

基 于 IL 4 片 的 多载 波 S5 1 6芯

数 字 中颊 接 收 机的’ 计 设

^

深圳 市 中兴 通 讯 股份 有 限公 司

摘 要 关键词

张 军 陈炜 炜

载 波 1— ◆ 1

20 0 2年 无线电工程 第 3 2鲞 摹 7 啊 3 J 1

D s M A pi t n ej & p / ai l c o  ̄用

个模 数 转换 器 ( D ) A C 。 在数字 中频接收 机 中,下变频 和 I 解调 的功 能 Q 由数字 电路 完成 ,模 拟 电路只 是信 号 的通道 ,信 号 经 过模拟 通 路没 有发 生性 质变 化 ,只 是信 号频 谱从 射 频搬 移到 中频 。A C输 出 的数字信 号仍然 属 于多 D 载 波 的中频 信 号 。因此 ,数字 接 收机 可 以共 用 一个 模 拟 通 道 , 并 Ⅱ 这 一模 拟 通 道 在 结 构 上 也 更 为 简 化 ,通常 只 需 作 一次 下变 频 。在 带 来益 处 的 同时 , 另一方 面 ,数字 中频接 收机 对模拟 通 道和 A C的 要 D 求也相 应 增加 ,主 要表现 在 带 宽和动 态范 围上 。 实

际 应 用 中 共 用 的 载 波 数 目一 般 不 大 于 3 。

P 0 u t产 品 设 计 与 r d cs

弦信 号与 数字 中频信 号分别 混频得 到 I Q基带 信号 ; 三是信 道滤 波 , 将基 带信 号 以外的其它 频率滤 除 , 同 时 , 可 以实现数 字信 号的成形 滤波 。 还 N 0是 数 控 本 振 ,本 振 的 频 率值 可 以通 过 设 C 置 寄 存 器 设 定 。 频 器 用 乘 法 器 实 现 。 C 和 乘 法 混 NO 器 的采 样 频 率 都 和 A C的采 样 频 率 相 同 , 为 A C D D 的采 样 频率 。 由于 较 高 的 A D采 样 频 率 可 以获 得一些处理增益, 此 , 因 其值 往 往 选 为数 倍 或 十 几 倍 的 2 信 号带 宽 。 样 的 采 样 频率 , 于 后 续 的 倍 这 对 信 道 滤 波 器 以及 基 带 处 理 部分 , 没 有什 么 益 处 , 却 并且会增加硬件开销, 此, 因 在混 频和 信 道 滤 波 之 问 有 抽 取 模 块 实 现 降 采样功能。

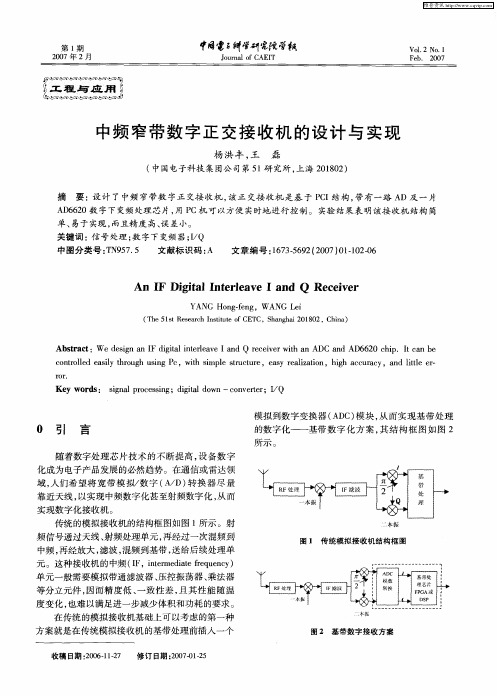

中频窄带数字正交接收机的设计与实现

维普资讯

20 07年第 1期

杨洪丰 等 : 中频窄带数 字正交接收机 的设计与实现

13 0

该 方案 采用 与传 统模 拟 接 收机一 样 的方 式经 过 两 次混频 将 射频 信 号 转 换 成 基 带 模 拟 信 号 , 后 再 然 利 用 A D转换 器将 该模 拟 信号 转 换 成 数据 流 , 给 / 传 后 续 的数字 信号 处理 器件 。该方 案 的优 点是 容 易实 现, 这是 由于要处 理 的模 拟信 号 已经 是基 带信 号 , 所 以它对 A D转 换 器 的频 率 要 求 不 高 。但 由 于 它 采 /

r or .

K yw rs s n l rcsi ; i t o n—c n e e ; e o d : i a poes g dg a d w g n i l o vr r VQ t

模 拟 到数 字变 换器 ( D ) 块 , 而实 现 基 带处 理 A C模 从

0 引 言

元 。这种接 收机 的中频 (F, nem d t eu n y I it e i e ̄ q e c ) r a

的数 字化— — 基带 数 字 化 方 案 , 结 构 框 图 如 图 2 其

所示 。

基

带

处

理

举

图 1 传 统 模 拟 接 收 机 结 构 框 图

单 元一 般需 要模 拟带 通滤 波器 、 压控 振荡 器 、 法器 乘

c n r l d e sl h o g s g P o t l a i t r u h u i c,w t i l tu tr o e y n i smp e s cu e,e s e l a in,h g c u a y n i l r h r a y r ai t z o ih a c r c ,a d l t e — te

数字中频接收机结构

2dB 衰减步进:提高动态范围优化

DR

2 dB Step Attenuator

3rd Order DANL Worst case DR due to insufficient Atten step size

Potential DR Given Up Optimum DR

Mixer Level

Dynamic Range Vs. Distortion and Noise

Log

ADC

频谱

参考电平

接近参考电平处 取得最佳准确度

对数 放大 范围

离参考电平越远 准确度越差

参考电平

对数放大范围

柱状图

2012 第12届国际电磁兼容暨微波展览会

7

数字中频改善幅度精度 (4)

数字中频对数放大 – 大大提高了对数显示精度,不需要 把信号调整到参考电平处

频谱

参考电平

ADC 提高的 对数精度

DIGITAL FILTER

RES BW 100 Hz

SPAN 3 kHz

形状因子决定了RBW 在大信号存在的情况下分辨小信号的能力

12

2012 第12届国际电磁兼容暨微波展览会

数字滤波器具有更快的扫描速度

达到同样的选择性,数字滤波器可以用更宽的RBW, 可以达到数倍的速度改善

30 kHz Digital Filter

不需要调整参考电平,意味着更高的测量吞吐率

11

2012 第12届国际电磁兼容暨微波展览会

数字中频滤波器:更好的选择性和更快的扫描速度 选择性典型值 Analog 12:1 Digital ≤5:1

ANALOG

FILTER

数字滤波器扫描速度改善:

RBW 100 Hz 30 Hz 10 Hz 3 Hz 1 Hz 速度提高(倍数) 3.10 14.40 52.40 118.00 84.00

探讨中频数字接收机的设计与实现

甜技凰探讨中频数字接收机的设计与实现陈春霞(91982部队13分队,海南三亚572000)c}商要】中频数字接收杌是随着数字信号处理技术不断成熟的。

笔者研究了中频数字接牧机的设计方案,并进一步探计了数据采集、数字成形滤波以及控制器的实现,很好地实现了在节约成本基础上的性能完善。

p翱】中频数字接牧机;软件无线电;数据采集;成形滤波软件无线电作为未来无线通信的发展方向,世界各国都在进行深入的研究。

基本结构主要有三种:射频低通采样数字化结构、射频带通采样数字化结构和宽带中频采样数字化结构。

其中宽带中频数字化结构既降低了中频之前模拟滤波放大处理的难度,也使其较之传统的中频数字化缕收机具有更好的波形适应性,信号带宽灵活性及可扩展性。

1中频数字接收机的设计方案随着数字信号处理技术的发展,接收机设计经历了从模拟到数字的演变过程,并且因A D C器件水平的提高,数字化程度越来越来高。

如伺j哿模拟信号变换为数字信号变成了实聊超越以往接收机系统的关键之一圈l中颏数字化方案示意图经过下变频,将射频信号变换为中频l F信号,在宽带A D C前可用~个中心频率固定的高性能抗混叠滤波器滤除带外无用信号并可在中放级实现自动增益控制,获得最大信号增益,减轻带内信号过载的可能性。

同时,A D C后用数字滤波代替了模拟滤波,提高了系统的灵活性和滤波器的选錾i性。

而且,就系统的可编程性而言,宽带中频数字化接收机与射频数字化方案相当。

2中频数字接收机的实现2.1数据采集的实现为了能采样10M H z的中频信号,高速数据采集部分采样时钟选定为f s=40M H zo此外,带通采样有可能避开带外的谐波,杂散混叠到带内来,在设计过程中只要精心选择采样频率和l F频率就能避免,因此在系统设计时I F和F s的选取是关键。

本文选用了A N LO G D E—V I C E公司的A D6640021.1模拟输入电路一般A D变换器之前要用运算放大器来驱动。

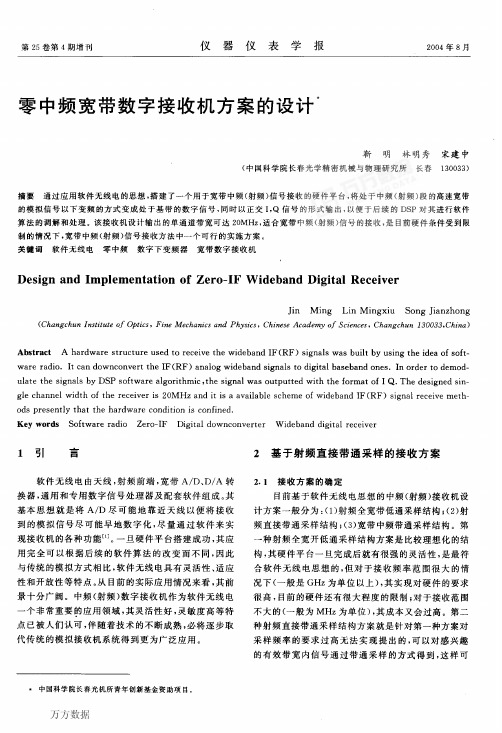

零中频宽带数字接收机方案的设计

第25卷第4期增刊仪器仪表学报2004年8月零中频宽带数字接收机方案的设计+靳明林明秀宋建中(中国科学院长春光学精密机械与物理研究所长春130033)摘要通过应用软件无线电的思想,搭建了一个用于宽带中频(射频)信号接收的硬件平台,将处于中频(射频)段的高速宽带的模拟信号以下变频的方式变成处于基带的数字信号,同时以正交I,Q信号的形式输出,以便于后续的DSP对其进行软件算法的调解和处理。

该接收机设计输出的单通道带宽可达20MHz,适合宽带中频(射频)信号的接收,是目前硬件条件受到限制的情况下,宽带中频(射频)信号接收方法中一个可行的实施方案。

关键词软件无线电零中频数字下变频器宽带数字接收机DesignandImplementationofZero—IFWidebandDigitalReceiverJinMingLinMingxiuSongJianzhong(ChangchunInstituteofOptics,FineMechanicsandPhysics,ChineseAcademyofSciences,Changchun130033,China)AbstractAhardwarestructureusedtOreceivethewidebandIF(RF)signalswasbuiltbyusingtheideaofsoft—wareradio.ItcandownconverttheIF(RF)analogwidebandsignalstodigitalbasebandones.Inordertodemod—u|atethesignalsbyDSPsoftwarealgorithmic,thesignalwasoutputtedwiththeformatofIQ.Thedesignedsin—glechannelwidthofthereceiveris20MHzanditisaavailableschemeofwidebandIF(RF)signalreceivemeth—odspresentlythatthehardwareconditionisconfined.KeywordsSoftwareradioZero—IFDigitaldownconverterWidebanddigitalreceiver1引言软件无线电由天线,射频前端,宽带A/D、D/A转换器,通用和专用数字信号处理器及配套软件组成。

主被动导引头数字中频接收机设计与实现

【 e od 】 I r e e; / ; S K yw rs F e irA D DP cv

O 引 言 …

在 现代 战争 中 , 随着 战场环境 的 日益复 杂化 , 单一 制导方 式 已经不 能很好 地满 足在 复杂 战场环 境下 具有 良好 的战术性 能 的要求 。单 纯采 用 主动或 单纯采 用被 动制导 都存 在 一定 的 缺 陷 , 已经 不 适 应 现 实 的需 求 。 主动跟 踪适 用范 围广 、 信息 量大 , 一旦受 到复 杂 电子 但

定律 , 要求 采样 速率 至 少 是 2× 0=10MH , 用 现 6 2 z使 有 的处理技 术 , 是很 难 达 到 这样 的采 样 速率 的 。解 决 问题 的一个 好 办法 就 是带 通 采 样 定理 , 通 采 样 定理 带 的意义 在于 , 对于载 波 频 率几 十兆 甚 至 上百 兆 的中频

o he Ac ie ft tv /Pa sv o i da s i e H m ng Ra r

L i , a g p n ,BICha — i IHu 。 LIXin — i g o hu ,L — un。 IYa k

( .D p r n f lc o i E g er gadIfr t no A I Y n i 6 0 1 C ia 1 e a met et nc ni ei n no i f E , t oE r n n ma o N a t 4 0 , hn ) a2 ( .G a u t Su e t ea m n f ati nvr t, Y na 2 0 0, hn ) 2 rd a tdn p r et na U ie i a t 6 0 C i e D t oY sy i4 带 A D和 带通采 样技 术 . /

中频数字化技术在接收机中的应用

收机进 行数 字化 改造 具有一 定 的现实 意义 。

软件无线 电的最终 目的是将模数转换器件紧

接在天线后, 直接在射频进行采样 , D A C变换后的

所有处理都用数字信号处理芯片,依靠软件编程来

实 现 。但 是 ,随着现 代 电子技 术 的飞速 发展 ,各种 电子 战 设 备 的工 作 频 率 已经包 含 在 整 个 无 线 电频

线 电领 域 的又一 次革命 。因此 ,在这 种情 况下 ,接

1概 述

当前伴随着 数字信号处理技 术和大规模集 成 电路的迅猛发展 ,无线通信技术正朝着数字化方 向

发展 ,软件 无线 电就 是最突 出一 例 。软 件无 线 电是 将 模 块化 、标 准化 的硬 件构 成基 本平 台 ,通 过软 件 加载 来实现 尽可 能 多的无 线 电功能 ,这 样 的无线 电 系统 具有很 强 的通用 性 ;同时 ,我 们知 道信 号失 真

Ap l ai n o gtl e h oo y i c i e p i t f F Di i c n l g Re ev r c o I aT n

BA1Y n o g a h n

Ab t a t A e i f Fd g a c ie a e n s f a e a i te r rsne . ii l igteI g a o MHz s r c : d s no ii l e ev r s do t r do h oy i p e e td D gt i n s l f 0 g I t r b ow r s az h F i 7 n

・2 3 2・

现代导航

本 文 提 出 了一 种 基 于 软件 无 线 电 理 论 的 中 频

进 行 限幅 、预选 、放 大和 下变频 ,产生 7MHz的 0 中频信 号 ,并将 7MHz中频 信 号进行 A/ 转换 , 0 D

中频数字接收机的设计

( cOl f nO a。 n 、T n a。 nier g Hab nier gUnv i , ri 5 0 1C ia S h0 。 fm1inad( lmu i t nE gnei , ri E g ei i t Hab 10 0 , hn) I t 0】 ci n n n n y n

p o e sn p e ft i s s e wih h g n e r t n,g o e i i t n lx b l y r c s i g s e d o h s y tm t ih i t g a i o o d r l b l y a d f i i t .S ttx e s s r f r n e a i e i o i x s se ee e c s v l e i a iu p l a i n . a u v r sa p i t s n o c o Ke wo d : i i lr c i e ; fwa e r d o i e n e e it r q e c y r s d g t e ev r s t r a i ;f d i t r d a e fe u n y a o x m

a d meh d ae ito u e n c nu cin wi h h o y a d meh fs fwae rdo n t o r n r c d i o j n t t t e te r n t o o o t r a i.Th o cee i l— d o h d e c n rt mpe

于 固定 中频数 字下变频 的中频数 字化接 收机 , 最 并且 终能够用硬件 实 现其 基本 功能 . 本设 计 首先 , 出一 提 种对 固定 中频进 行数字下变频 的实现方法 , 通过 简要

一种TD-SCDMA中频数字接收机设计

=

在其中的一个频带( +))n=0 ,…) 枷 1 ( ,2 上 l

存 在信号 , 而不允许 在不 同的频 带上同时存在 信 号 , 则将 会 引起信 号混 叠 。 否 1 2软 件无 线 电框 架 . 软件无 线电采 用一个通 用硬件平 台 , 对 无 线 电信号 进 行 接 收 、 采样 、 波 和 下变 滤 频 , 完成 后 续 的解 调 、 道均 衡 、 并 信 自动 增益 控 制 、 扩 、 道 解 码 、 源 解码 等信 号处 解 信 信 理 工作 。 因此 , 件 无线 电框 架 可以 用 图l 软 所 示框架表示 。 图 1 示 的 软 件 无 线 电框 架 由射 频 处 所 理 、 带A/ D A 换 以 及D P 理 i e e Tech ogy nnov i n r d nd nol I at o He al

多通道雷达中频数字接收机的工程实现方法研究

I l me tto ft e mu t c a n lI i i lr c i e o a a s mp e n a in o h li h n e F d gt e e v rf r r d r — a

x A u.ig. A G S iu l o X e n W N h- n y j

维普资讯

雷达 与对抗

20 0 7年

第 1期

多通 道 雷达 中频 数字 接 收机 的工 程 实现 方 法研 究

肖学颖 , 王世 军

( 南京长江电子信 息产业集 团有 限公 司研究所 , 江苏 南京 2 0 3 ) 10 7

摘

要 : 据 中频 直接 采样 与数 字下 变频 的基 本原 理 , 根 实现 多通 道数 字 中频 接 收 , 出了 工程 实 给

接收机中频数字化处理设计

根据 N y q u i s t 带通采样定理 , 采样 速率在满足大于信号带宽 ( B = ) 两倍 的情况下 , 选取远远低于信号最 高频率 的两倍 速率就能正确 地 反映带通 信号 的特性 日 . 与低 通采样相 比 . 带通 采样降低 了采样 速 率. 极大地减小 了后续数字信号处理负担。 由带通采样定理可知 .带通采样率 f s 满足下式 即可实 现无混叠 采样 : / ( n + 1 ) ≤ ≤ / n , 1 -n < -l <  ̄ I f , / B ] ( 1 ) [ ・ ] 表示取不 大于括号内数值的整数 。不难看 出, 式( 1 ) 将采样 频率划分成若干个区间 , 并且 由 n 值确定 。 n 值越小 . 频率区间范 围越 大, 也就是说对输入信号频 率或采样频率偏差 的要求越小。 并且随着 1 1 值 的下降 , 采样频率会越高 , 量化信 号的频谱重复 间距越 大 , 对抗 混叠 滤波器带外能量抑制特性要求降低 : 在设计 时应 当根据系统 电路结构 和应用场合折衷确定 n 的取值 2 . 2 数字下变频 ( D DC 、 由于数字信号处理 的速度有 限 . 往往难 以对 A D C采样得到 的高 速率数字中频信号直接 进行各种类别 的实时处理 为 了解 决这个 问 题. 需要采用数字下 变频技术 . 将采样 得到的高速率数 字中频信号 变 成低 速率基带信号 , 以便进行下一步的信号处理 。 数 字下变频功能包 括数 字正交混频 、 低通滤波和数字重采样 , 如图 4 所示 。

软件无线电接收机的基本思想 是数据采 集环 节尽可能靠近天线 。 中频和射频级的接收信号直接数字化 . 将 由模 拟器件实现部分信号前 端处理 ( 例如信道切换 、 下变频 、 滤波 、 解调等) 转换为 由可编程数字处 理芯片实现 . 通过将不 同的数字处理模块下载到芯片 即可灵活切换信 道接人方式 , 接收来 自不 同发射系统的信号【 1 ] 。 目前软件无线 电接收机 的实现集中在数字化 的基 础上 。 本文 运用软件无线 电理论 . 结合 目前 可实现 的中频软件无线 电接收机 . 给 出了一种可行 的接 收机 中频 数字 化处理结 构 . 并系统 阐述 了相关 的数字信号处理技术 。

基于DSP和FPGA的中频数字接收机的设计

式中:

为采 样 频 率 ; 0为 带 通 信 号 的 中心 频 f

l 引 言

传统 的接 收 机 采 用 超 外差 方 式 混 频 到 基 带

率 ; 取大 于 1的整数 。 上式选 定 采样频 率 , M 用 可

以保 证信 号 的有用频 谱 不产生 混 叠 , 从而 得 到正

确 的 IQ信号 。 / 经过 A/ D变换 后形 成 的数字信 号 X( , NC 数 控 振 荡 器 )产 生 的 正 交 信 号 ) 与 O(

A b ta t T hs pa ri r sr c : i pe ntodu e he t or d de i e ho i ia i e m e a e f e ue y r c i r a d a e c s t he y an sgn m t d ofd g t l nt r dit r q nc e eve . n b s d on hi p e gh s e d DSP nd FPGA sa i h h r w a e pr e s pltor . T h ys e ’ c e i ofwar nd p i st a r a e tbls a d r oc s a f m e s tm S or s s t e a a ple O a r da

一

.

()o ( o+ () , tcsW t ) 当以时 间间隔 一 1 采样 / 后, 一 (M一 17 2 一般 M 取为 1 2 )/ , r 或者 2若 ,

取 M 一 1则 : ,

( r )一 J 7 c s, / ]一 Q( s [ 2 , ( )o [ r2 2  ̄ )i , ]一 n  ̄/

c sபைடு நூலகம்。 )和 s ( 。 到 数 字 混 频 器 。 混 频 后 o( 7 2 i W ) n 经

中频数字化接收机系统设计与实现的开题报告

中频数字化接收机系统设计与实现的开题报告一、研究背景随着现代通信技术的飞速发展,无线通信系统的需求不断增加,数字化接收机成为了这些系统中的关键性组件之一。

数字化接收机替换了传统的模拟接收机,具有系统性能稳定,现场调试方便等优势。

现有的数字化接收机已经具有较高的精度和可靠性,但是随着技术的不断进步,数字化接收机的性能还有很大的提升空间,尤其是在中频数字化接收机领域。

因此,本文将对中频数字化接收机系统进行研究,设计一种新型的中频数字化接收机系统,以提升其性能和稳定性。

二、研究目的本文的研究目的如下:1.深入研究中频数字化接收机系统的基本原理和架构,掌握其工作流程和关键技术。

2.设计出一种能够满足实际需求的中频数字化接收机,包括对信号进行处理和数字化的模块,对数字信号进行解调和滤波的模块,数据传输和存储模块等。

3.测试和验证设计的中频数字化接收机系统的性能和稳定性,考察其现场应用效果。

三、研究方法本文将采用如下研究方法:1.文献资料研究法:对数字化接收机技术、中频数字化接收机系统等方面的文献资料进行归纳整理,并结合国内外相关研究成果进行分析。

2.理论分析法:以中频数字化接收机系统的基本原理和架构为基础,分析其工作流程和关键技术,并结合实际应用场景进行分析和探讨。

3.系统设计法:根据理论分析结果,设计出一种能够满足实际需求的中频数字化接收机,并进行系统集成和调试。

4.实验验证法:对设计的中频数字化接收机系统进行实验验证,测试和评估其性能和稳定性,考察其现场应用效果。

四、预期研究结果1.深入研究中频数字化接收机系统的基本原理和关键技术,了解数字化接收机技术发展的趋势,提高数字化接收机的水平。

2.设计出一种能够满足实际需求的中频数字化接收机系统,包括对信号进行处理和数字化的模块,对数字信号进行解调和滤波的模块,数据传输和存储模块等,提升数字化接收机系统的性能和稳定性。

3.测试和验证设计的中频数字化接收机系统的性能和稳定性,考察其现场应用效果,为以后数字化接收机系统的设计和研发提供参考。

中频数字接收机中的数字滤波器设计分析

K e n n e d y 两位 学者在1 9 9 5 年 研究 自然 界生物群聚行 为, 所发 展 出以生物群体为背景 的计算技 术, 借助模拟单一个体所 组成的

3 . 3改良型粒子群最优化演算法流程

自己与同伴 的经验来选择 , 最后通 过迭代次数寻求最优解 。 二是粒子群最 优化演算法 ( P a r t i c 1 e S w a r m

O p t i m i Z a t i o n , P S O ) , 这 是 由R u s S e l 1 E b e r h a r t * I J a m e S

下, 本文重点从改 良型粒子群最优化演算法着手, 对于数字滤波器的设计进行了 分析。 关键词: 中频数字接收机; 数字滤波器; 设计; 粒子群最优化演算法

1 中频数字接收机的数字滤波器应用及特征

优化演算 法在信息的交换并更新 向量之 间, 除了考虑原有的粒

新增 的区域最优解 可以使演算法 滤 波器可以用相 当简单 的手法 改变 信号的本质 , 设计者可 子最 优解与全域最优解之外 , 进而缩 以自由选 择所需的频段, 并滤除其 他不需要 的部分。 例 如, 当输 在求 解最优化 问题时更有效率的搜寻到最优 解的位置, 入_信号通过低通滤 波器后, 便 可以让低频部 分的信号通过并 短求解最优化问题所需的时间。 在粒子群优 演算法 中, 每 一个个体 被称为粒子, 每一个 粒 能消除高频 部分 的信号; 反之 , 高通滤波器 也可让 高频 部分 的

比滤波器 要考虑 电子元件、 电路、 温 度, 经 过时间长短而改变 , 在 数字滤波器上却没有此 问题。 w e i g h t m e t h o d ) 、 最大 速度法 ( M a x m e t h o d ) 和收缩系数 法

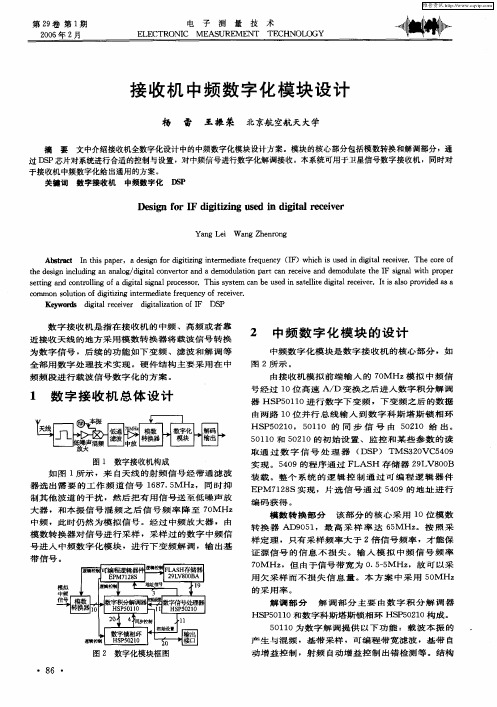

接收机中频数字化模块设计

的采 用率 。

模 主 I 叫 t i丝二■ 拟 I J 生 3 i L. 皇 i 童 中顿

取通 过 数 字 信 号 处 理 器 ( P) TM s 2 VC5 0 DS 3O 49

图 1 数字接收机构成 如 图 1所 示 ,来 自天 线 的 射 频 信 号 经 带 通 滤 波

器 选 出 需 要 的 工 作 频 道 信 号 1 8 . M Hz 同 时 抑 6 75 ,

实 现 。5 0 4 9的程序 通 过 F AS 存储 器 2 L 0 B L H 9 V8 0

器 HS 0 P5 1 0进 行 数 字 下 变 频 ,下 变 频 之 后 的 数 据 1

1 数 字 接 收 机 总体 设 计

由两路 1 O位 并 行 总 线 输 入 到 数 字 科 斯 塔 斯 锁 相 环

HS 5 2 0 5 1 0 的 同 步 信 号 由 5 2 0 给 出 。 P 01, 01 01 5 1 0和 5 2 0的初始 设 置 、监 控 和某 些 参数 的读 01 01

s ti d c n rlig o ii l in lpo e s r et a o tol f dg t g a r c so .Thss se c n b s di ael edgtl e ev r I i as rvd da g n n n a as i y tm a eu e s tlt iia c ie. t s lop o ie sa n i r c mmo ou in o ii zn itr e it rq e c fr c ie. o n s l t fdgt i n e o i g m da efe u n y o eev r

一种数字化中频接收机的与实现

软件无线电(Software Radio )的概念自上世纪末提出以来,最近几年取得了引人注目的进展。

数字化中频接收机是软件无线电的重要部分。

软件无线电的主要原理是将数字化推向前端,即是把模数/数模转换器(ADC/DAC )尽量放在射频端,这是数字化接收机的发展方向,也是软件无线电的理想实现方法。

早期的数字化接收机受ADC 发展水平的限制,采用正交双通道零中频的实现方案,即将射频通过变频变换到零中频(基带),正交解调得到模拟的正交信号之后再进行数字化。

该方案的频率变换主要都在模拟部分实现,数字化较少,不是真正意义上的数字化接收机。

而且,此方案实现起来设备量较大,方案中的正交混频器是模拟器件,得到的正交I ,Q 信号也难以保证幅相正交的精度[1]。

目前比较成熟的数字化接收机理论和实现方案是中频数字化接收机,即将射频信号经一次或二次下变频后,在中频(或高中频)直接采样,再数字下变频到基带,得到正交I ,Q 信号。

软件无线电技术的迅猛发展,使其在航天测控领域的应用成为了可能。

在我国当前的C 频段微波统一测控系统中,中频接收机主要由模拟电路构成,这种结构已经逐渐不能达到测控系统的精度要求。

数字化已经成为中频接收机的必然发展趋势,关于这方面的研究,已经开展了很多[2-6]。

文中设计了一种数字化中频接收机,该方案采用软件无线电思想,并给出了采用FPGA 和DSP 实现该接收机的方法。

1系统工作原理软件无线电的目标和思路是在标准化、完全可编程的硬件平台上,用不同的软件适应通信、测控等业务的各种体制,并实现尽可能多的无线功能,其原理框图如图1所示。

在理想的软件无线电中,系统的所有功能都在一个通用的处理器上用软件实现,原则上允许同一硬件平台支持任何物理层和更高的协议层。

文中所设计的数字化中频接收机的应用了软件无线电的设计思路,在中频70MHz 上进行带通采样。

输入的信号有和路和差路,其中和路信号包含有测距、遥测等信息,而差路信号则含有角误差信息。

基于PID干扰抑制算法的中频接收机设计

基于PID干扰抑制算法的中频接收机设计

丁杨

【期刊名称】《科技通报》

【年(卷),期】2014(30)8

【摘要】为设计抗干扰能力强的中频接收机,提高中频接收机的抗干扰调制解调性能,提出一种基于可变论域模糊PID控制的中频接收机干扰抑制算法。

改进算法采用在载波频率变换成中频频率时引入可变论域理论,在混频管中进行可变论域非线性分区,对PID抗干扰抑制算法进行改进,用LT5575实现解调功能,采用LT6600-20芯片实现基带信号的滤波和中频放大功能,实现中频接收机的硬件设计。

测试结果表明,采用该抗干扰抑制算法设计中频接收机,对中频干扰和镜像干扰具有很好的抑制效果,接收机性能较好。

【总页数】3页(P137-139)

【关键词】PID控制;中频接收机;抗干扰;可变论域

【作者】丁杨

【作者单位】西南交通大学计算机与通讯工程系;四川建筑职业技术学院信息工程系

【正文语种】中文

【中图分类】TN713.5

【相关文献】

1.北斗和GPS双模接收机干扰抑制算法的设计与实现 [J], 张建立;杨祖芳;潘伟;郑建生

2.基于变换域方法抑制线性调频干扰的GPS接收机设计 [J], 谭文群;芦莉;侯友国

3.一种零中频数字接收机镜像抑制新算法 [J], 区洋;刘重军;邓单

4.卫星导航接收机中频域抗窄带干扰算法指标评估 [J], 王彦朋;李玉莹;王星

因版权原因,仅展示原文概要,查看原文内容请购买。

基于GC4016的SDR数字中频接收机滤波器的设计与实现

同时 , 对射频信号接收要满足邻信道抑制 : 8 ≥1

d @偏移 10k z t6 B B 3 H ; 0 d @偏 移 4 0k z 阻塞 干 > 0 H ;

在 S R( 件定 义无线 电 , D 软 简称 软件 无 线 电 ) 设

2 S DR接 收 信 道 指标 要 求

G 4 1 片是可 编程 的 , C 0 6芯 因此可 以满足 多种应 用需 求 。在 S R某频 段应用 中 , 射 频和基 带 的指 D 从 标要 求 , 多速率处 理主 要满足 以下几 个方 面 : 输入采 样率 :14 z 6 .4 MH ;

关 系出发 , 结合 G ae i 司生产 的 多通 道数 字 下 变频 器 G 4 1 ryhp公 C 0 6芯 片 , 出 了 中频 数 字滤 波 器 的 给 设计 方法 , 理论 上进行 了分析和仿 真 , 从 并在 实际 工程 中进 行 了 实验验 证 , 到 了预 期 的结果 。 得 关键 词 : 件无 线 电 ; 字下变频 器 ; 软 数 中频接 收 机 ; 滤波 器设 计

中图分类号 :N 1 T 73 文献标 识码 : A

De i n a d Re lz to f t e Fi e o DR g t l sg n a i a i n o h l r f r S t Di ia I t r e i t e u n y Re e v r Ba e n GC4 n e m d a e Fr q e c c i e s d o 01 6

adI . h na a s a ea ds l o e o e .Fn l , i me o ai t rjc a d n T e nl i im d n i a nip r r d iay t s t di vl ae i po t n F y ss mu t s fm i l h h s d dn e

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

文章编号:1009-671X (2006)04-0007-03中频数字接收机的设计于 搏,赵忠凯,王 丹(哈尔滨工程大学信息与通信工程学院,黑龙江哈尔滨150001)摘 要:介绍了中频数字接收机的总体设计方案,提出了固定中频数字接收机的设计思想与方法,结合软件无线电的有关理论与方法,阐述中频数字接收机的具体实现.主要采用高速的A/D 转换器和高端现场可编程逻辑阵列的结构,使得总体系统的处理速度大为提高,而且集成度高,可靠性好,使用灵活,具有很强的应用参考价值.关键词:数字接收机;软件无线电;固定中频中图分类号:TN85211 文献标识码:A收稿日期:2005-05-10.作者简介:于 搏(1980-),男,硕士研究生,主要研究方向:通信与信息系统,E -mail :yubohrb @.Design of intermediate frequency digital receiverYU Bo ,ZHAO Zhong-kai ,WAN G Dan(School of Information and Communication Engineering ,Harbin Engineering University ,Harbin 150001,China )Abstract :The general design of digital receiver in intermediate frequency is presented.The design conception and method are introduced in conjunction with the theory and method of software radio.The concrete imple 2mentation procedure is demonstrated thoroughly.The application of A/D and FP G A highly increases the final processing speed of this system with high integration ,good reliability and flexibility.So it possesses reference value in various applications.K eyw ords :digital receiver ;software radio ;fixed intermediate frequency 随着信息时代和信息社会的到来,信息技术和电子对抗技术业已成为现代战争的主要手段,作为电子战实施的一个关键环节,中频数字接收机[1]的研究与探索越来越受到人们的强烈关注.本研究的重点是结合软件无线电的方法研制基于固定中频数字下变频的中频数字化接收机,并且最终能够用硬件实现其基本功能.本设计首先,提出一种对固定中频进行数字下变频的实现方法,通过简要分析论证了其正确性和可靠性;其次,整个硬件系统仅采用一片FPG A 来处理,并采用3片双通道A/D 芯片同时同步采样的运行模式.这片FPG A为主控芯片,通过FPG A 对整个系统进行通信和控制,大大提高了系统的运行速度.1 硬件设计中频数字接收机的每路信号的总体硬件结构流程图如图1所示.111 模拟带通滤波器中频信号有各种干扰存在,最好在接收中频信图1 总体硬件结构流程图号前先对它进行模拟滤波,将所选频率范围取出.本设计选用的是VANLON G 公司生产的BP60110型模拟带通滤波器,其中心频率为70MHz ,中频带宽为20MHz ,矩形系数为2,故信号通频带带宽为10MHz.但是,BP 60110的插入损耗最大值为第33卷第4期 应 用 科 技 Vol.33,№.42006年4月 Applied Science and Technology Apr.20062710dB ,常规数值为2318dB ,对应的电压最大衰减值是输入的2214倍,常规衰减量是输入的1515倍.因此,BP60110模拟带通滤波器衰减比较严重,输出幅度太小,为了提高它的输出幅度,加了一个运算放大器.112 运算放大器放大是整个模拟前端电路中的重要环节.由于接收的信号通频带宽较宽,还会存有部分杂波,所以使用运算放大器时,采用了单端输入(输入副端接地)双端输出信号的传输方式.提供给下级电路的有用信号为差模信号,而噪声为共模信号,这样可以有效地抑制噪声和温度漂移.本设计采用AD 公司的运算放大器AD8138,其工作原理如图2所示.图2 AD8138运算放大器电路原理图考虑到运算放大器要和前端的滤波器进行阻抗匹配,需要计算运算放大器输入阻抗,经计算得R IN ,dm =R G ×11-R F2(R G +R F ). 当AD8138在通带为0~-3dB 带宽下,选择R G =499Ω,R F =2149kΩ时,70MHz 中频信号放大了315倍,AD8138的输出通过变压器耦合后,可以满足AD9238采样时需要的电压幅度而又不会使其溢出.AD8138放大性能指标如图3所示.图3 AD8138对数幅频特性曲线113 A/D 变换器A/D 变换器选用AD 公司的高端产品AD9238,工作频率是65MHz ,可以配以几十兆采样速度,单次采样时间是ns 数量级.AD9238有2个完全相同的输入通道,除了共用内部电压参考源,这2个通道是完全独立的.采样输出数据高达12bit ,精度很高.对输入信号来说,每个通道均可设为双端输入,更适合对差模信号进行采样量化.由于器件工作在中频范围内,要适用于固定中频带通采样的应用,采样不可以按照低通纳奎斯特采样原则,应该满足带通欠采样定理:一个频带限制在(f L ,f H )的信号,如果其采样速率f S 满足f S =2(f L +f H )/(2m +1);f 0=(f L +f H )/2,故f S =4f 0/(2m +1);m 取满足f S ≥2(f H -f L )的最大正整数.114 FP G A运用FP G A 设计时序逻辑电路,具有速度快,精度高,设计灵活,集成度高以及性能稳定可靠等优点[2].本设计选用了AL TERA 公司的Stratix 系列器件EP1S40F780I6,还选用了高性能的EPC16对FP G A 配置.EP1S40拥有逻辑单元41250个,锁相环PLL12个,DSP 块14个,嵌入式乘法器112个.2 软件设计软件编程采用AL TERA 公司提供的嵌入式系统开发环境Quartus II 软件.本设计采用了V HDL 语言编写时序逻辑程序模块,再把各个模块衔接起来.软件设计方面的工作全部在FP G A 内部完成,软件的设计流程原理图[3]如图4所示.图4 软件设计流程原理图S (n )=a (n )cos [ω0n +<(n )],(1)用正交分量来表示,式(1)可改写成S (n )=I (n )cos (ω0n )-Q (n )sin (ω0n ).(2)式中:I (n )=a (n )cos <(n ),Q (n )=a (n )×sin <(n ),ω0=2πf 0,n =N /f S ,其中N 是采样点个数;根据欠采样定理,f S =4f 0/(2m +1);m 取3.・8・应 用 科 技 第33卷cos(ω0n)=cos(N(2m+1)π/2)=cos(3Nπ/2), sin(ω0n)=sin(N(2m+1)π/2)=sin(3Nπ/2).故,cos(ω0n)是1,0,-1,0周期循环数字序列;sin(ω0n)是0,-1,0,1周期循环数字序列.2.1 数字下变频数字下变频是利用FP G A内部提供的硬件乘法器,对输入的数据进行数字正交混频,输出结果中既含有2倍频分量,又含有零中频的同相分量I或正交分量Q,再经过后面的低通滤波提取出I或Q.其中ω0表示数字本振,要求数字本振是初相为0的,并且和输入信号是同频率的[3].在接收多路信号时,要保证各路信号的同步性,可以利用FP G A 中的PLL模块同时触发各路信号使得时钟同步.本设计所选Stratix系列FP G A内部带有12个PLL 模块.在QuartusⅡ软件开发环境中调用1个PLL 模块,输入时钟设置为由外挂的晶振提供给FP G A,将PLL模块设置为多路时钟从FP G A输出、每路输出时钟相对输入时钟的倍频因子设置为1,置为0,相移设置为0.这样,每路的输出时钟就和输入时钟完全一样,即可使各路输出时钟严格同步.用这样的同步时钟触发各路A/D变换器进行采样,就可以保证对各路信号采样的同步性.2.2 数字低通滤波低通滤波的实现是采用了AL TERA公司的IP 核进行设计.所谓IP核是一种含有自动布局布线信息的软件模块,这种软件IP模块不仅包含可综合寄存器级硬件描述语言模型,还提供带有布局布线信息的网表.在QuartusⅡ软件开发环境中可直接生成并调用出IP核模块,IP核采用分布式算法,利用其可视化的操作界面设置参数,可自动生成数字滤波器的各个系数,再设置量化因子将系数量化,进行抽取FIR低通滤波器的设计[1].2.3 MA TLAB仿真结果QuartusⅡ软件只有仿真数据,不能形象直观地说明问题,而IP核也可以结合在MA TLAB环境下使用.因此,下面给出在MA TLAB中仿真经数字滤波后同相分量I(正交分量Q也类似)的结果.将70MHz正弦数字信号(见图5(a))进行脉冲调制,脉冲(见图5(b))宽度为3μs,占空比50%,在IP核的可视化界面中将滤波参数设置如下:FIR低通滤波,窗函数为汉明窗,通带截止频率为1125MHz,阻带起始频率为215MHz,阶数为40,采样频率为40MHz,抽取率因子为2,采用完全并行结构,流水线延迟Pipeline=1,单通道输入,输入数据为12bit,滤波器系数按12bit自动量化,则同相分量I输出结果如图5(c)所示.图5 使用IP核进行数字滤波的仿真结果由图5看出:从脉冲前沿到FIR输出平稳值需要一定时间的延时,这是由于FIR的滤波特性决定的;由于阶数为40,当进入滤波器模块的数据超过40个后,才能确保输出的数值是稳定.从脉冲前沿到输出稳定的数值,所需时间为40×25ns=1μs.由于脉冲宽度是3μs,采样频率为40MHz,这样可以取得120个数据,稳定数值的个数为80个,2抽1后输出的稳定数值有40个.2.4 FIFO存储器FIFO作为数据的缓冲器,当后续电路忙时暂存在FIFO中,等待后续电路空闲时再来读取,避免了个别信息的丢失.其特点是容量大,存取速度快,可以同时运行读和写2种操作.考虑到接收到的雷达信号参数有的是匹配的,有的是要剔除的,故设计了2级FIFO级联的形式.第1级FIFO将滤波后接收到的信号全部存入,并存入相应的雷达信号参数作为标识,这就要求第1级FIFO的容量要很大;根据雷达信号参数,把匹配的雷达信号数据写入第2级FIFO中,等待后续电路的读取.3 结束语本设计能够较好实现中频数字接收机的总体指标,准确可靠地完成接收前端目标信号的任务并做出相应的一系列处理;系统性能稳定,实时处理性强,运行速度快,抗干扰性强,电磁兼容性好,达到了设计要求.参考文献:[1]杨小牛,陆安南,金 飚.宽带数字接收机[M].北京:电子工业出版社,2002.[2]褚振勇,翁木云.FPG A设计及应用[M].西安:西安电子科技大学出版社,2002.[3]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.[责任编辑:李玲珠]・9・第4期 于 搏,等:中频数字接收机的设计。