实时信号处理系统设计与实现

基于DSP+FPGA的实时信号采集系统设计与实现

基于DSP+FPGA的实时信号采集系统设计与实现周新淳【摘要】为了提高对实时信号采集的准确性和无偏性,提出一种基于DSP+FPGA 的实时信号采集系统设计方案.系统采用4个换能器基阵并联组成信号采集阵列单元,对采集的原始信号通过模拟信号预处理机进行放大滤波处理,采用TMS32010DSP芯片作为信号处理器核心芯片实现实时信号采集和处理,包括信号频谱分析和目标信息模拟,由DSP控制D/A转换器进行数/模转换,通过FPGA实现数据存储,在PC机上实时显示采样数据和DSP处理结果;通过仿真实验进行性能测试,结果表明,该信号采集系统能有效实现实时信号采集和处理,抗干扰能力较强.%In order to improve the accuracy and bias of real-time signal acquisition,a real-time signal acquisition system based on DSP +-FPGA is proposed.The system adopts 4 transducer array to build parallel array signal acquisition unit,the original signal acquisition amplification filtering through analog signal pretreatment,using TMS32010DSP chip as the core of signal processor chip to realize real-time signal acquisition andprocessing,including the signal spectrum analysis and target information simulation,controlled by DSP D/A converter DAC,through the realization of FPGA data storage,real-time display on the PC and DSP sampling data processing results.The performance of the system is tested by simulation.The results show that the signal acquisition system can effectively realize the real-time signal acquisition and processing,the anti-interference ability is strong.【期刊名称】《计算机测量与控制》【年(卷),期】2017(025)008【总页数】4页(P210-213)【关键词】DSP;FPGA;信号采集;系统设计【作者】周新淳【作者单位】宝鸡文理学院物理与光电技术学院,陕西宝鸡721016【正文语种】中文【中图分类】TN911实时信号采集是实现信号处理和数据分析的第一步,通过对信号发生源的实时信号采集,在军事和民用方面都具有广泛的用途。

单片机系统中的信号处理技术原理与实时性要求分析

单片机系统中的信号处理技术原理与实时性要求分析在单片机系统中,信号处理技术是一个关键的部分。

它涉及到将传感器采集到的信号转化为数字形式,以便单片机进行处理和分析。

信号处理技术的准确性和实时性是确保系统性能和稳定性的重要因素。

本文将介绍单片机系统中的信号处理技术原理,并分析实现实时性要求的方法。

首先,我们需要了解信号处理技术的原理。

在单片机系统中,信号处理主要分为模拟信号处理和数字信号处理两个阶段。

模拟信号处理涉及到将传感器采集的模拟信号进行放大、滤波和调整电平等操作,以便适应单片机输入的电平要求。

数字信号处理则将模拟信号转化为数字形式,以便单片机进行数学运算和逻辑判断。

在模拟信号处理阶段,放大电路负责将传感器采集的微弱信号放大到适合单片机输入的电平范围。

滤波电路则通过滤波器对信号进行滤波,去除高频噪声和干扰,使得信号质量更好。

另外,电平调整电路还可以将信号调整为单片机所需要的电平范围,以确保单片机能够稳定地接收信号。

而在数字信号处理阶段,模数转换器(ADC)负责将模拟信号转换为数字形式。

ADC使用采样和量化技术,将连续的模拟信号按照一定的时间间隔进行采样,并将每个采样点的幅值量化为一组数字数据。

此外,为了保证信号的准确性,在信号转换前应对信号进行抗混叠滤波和抗混叠插值处理,以消除混叠失真。

在实时性要求分析方面,单片机系统需要在规定的时间内准确地处理实时的信号。

实时性是指系统对外部事件和内部任务能够及时做出反应,并在特定时间范围内完成所需的处理。

对于信号处理技术来说,实时性要求主要体现在信号采集的频率和处理的速度上。

首先,信号采集的频率决定了系统对信号变化的响应能力。

如果信号变化很快,系统需要以较高的采样频率来获取准确的信号。

然而,采样频率过高会增加系统的计算负担,导致实时性下降。

因此,需要根据具体应用的要求和信号特征选择合适的采样频率。

其次,处理速度决定了系统对信号处理的能力。

单片机通过程序来处理信号,因此程序的执行速度极大地影响了系统的实时性。

一种雷达信号处理模块的设计和实现

一种雷达信号处理模块的设计和实现一种雷达信号处理模块的设计和实现现代雷达特别是机载雷达数字信号处理机的特点是输入数据多,工作模式复杂,信息处理量大。

因此,在一个实时信号处理系统中,雷达信号处理系统要同时进行高速数据分配、处理和大量的数据交换.而传统的雷达信号处理系统的设计思想是基于任务,设计者针对应用背景确定算法流程,确定相应的系统结构,再将结构划分为模块进行电路设计。

这种方法存在一定的局限性。

首先,硬件平台的确定会使算法的升级受到制约,由此带来运算量加大、数据存储量增加甚至控制流程变化等问题。

此外,雷达信号处理系统的任务往往不是单一的,目前很多原来由模拟电路完成的功能转由数字器件来处理。

系统在不同工作阶段的处理任务不同,需要兼顾多种功能。

这些问题都对通用性提出了进一步要求[2].随着大规模集成电路技术、高速串行处理及各种先进算法的飞速发展,利用高速DSP和FPGA相结合的系统结构是解决上述问题的有效途径。

1雷达信号处理机方案设计1.1雷达信号处理的目的现代机载雷达信号处理的任务繁重,主要功能是在空空方式下将AD 数据录取后进行数字脉压处理、数据格式转换和重排、加权降低频谱副瓣电平,然后进行匹配滤波或相参积累(FFT或DFT)、根据重复频率的方式进行一维或二维CFAR处理、跟踪时测角等运算后提取出点迹目标送给数据处理机。

空地方式下还要进行地图(如RBM和SAR)等相关图像成像处理,最后坐标转换成显示数据送给显控处理机。

上述任务需要基于百万门级可编程逻辑器件FPGA与高性能DSP芯片作为信号处理模块,以充分满足系统的实时性要求,同时为了缩短机载雷达系统的研制周期和减少开发经费,设计的基本指导思想是通用化的信号处理模块,可以根据不同要求,通过软件自由修改参数,方便用户使用。

1.2系统模块化设计方案的功能模块,除了信号处理所必需的脉冲压缩模块、为MTD模块作准备的数据重排模块、FIR滤波器组模块、求模模块、恒虚警处理模块和显示数据存储模块外,还包括雷达同步信号和内部处理同步产生模块、自检数据产生模块以及不同测试点测试数据采样存储模块。

一种距离高分辨力雷达实时信号处理机的设计与实现

De in a d I pe sg n m lme t t n o g n e Re ou i n Ra a n a i fa Hih Ra g — s lt d r o o

Re l i g a o e s r a — me Si n l t Pr c s o

Z A G Y n -e F N Xa -o WA G Jn L h oh n H N ogj A iob i - N u I a -o g S -

( col f l t ncadIf mao nier g B iagU ie i ) Sh o o e r i n n r t nE gne n ,e n n r t E co o i i h v sy

p r llsgn — o e sn yse w t a a e i a prc s ig s tm h mulil g — ef r n e DS o e td w t g s e d d t e wo k. s se c n g ain i l l i tp ehih p ro ma c Psc nn ce h hih—p e a an t r A y tm o f ur t s i i o

表1系统中主要操作的计算鲑存储景和传输量增益脉冲压缩多酋勒滤波跟踪搜索恒虚警检测跟踪搜索肌控制15ufl42ub10us42ua15us945ms420mi5ins运算时间6711857up1365nm9惦ms传输量dma154kb256kb80120mb3280mb存储量896kb640kb64mb32ib允许最大耗时150us脉冲周期150us脉冲周期looms帧周期looms帧周期考虑到系统性能的裕量以及算法的可扩展性对系统的主要操作在硬件平台上进行以下分配

基于FPGA+DSP的实时图像处理系统设计与实现

万方数据万方数据·110·微处理机2010年(DPRAM)。

虽然C6416片内集成了高达8M位的片内高速缓存,但考虑到图像处理算法必涉及到对前后几帧图像进行处理,为保证系统运行时存储容量不会成为整个系统的性能瓶颈(chokepoint),在DSP模块中额外扩展存储空间。

由于EMIFA口的数据宽度更大,因此系统在EMIFA的CEl空间内扩展了两片总共128M位的同步存储器。

C6416的引导方式有三种,分别是:不加载,CPU直接开始执行地址0处的存储器中的指令;ROM加载,位于EMIFBCEl空间的ROM中的程序首选通过EDMA被搬人地址O处,ROM加载只支持8位的ROM加载;主机加载,外部主机通过主机接口初始化CPU的存储空间,包括片内配置寄存器。

本系统采用的是ROM加载方式。

C6416片内有三个多通道缓冲串口,经DSP处理的最终结果将通过DSP的多通道缓冲串口传送至FPGA。

3.4图像输出模块该模块的功能是将DSP处理后的图像数据进行数模转换,并与字符信号合成后形成VGA格式的视频信号。

这里选用的数模转换芯片为ADV7125。

这是ADI公司生产的一款三通道(每通道8位)视频数模转换器,其最大数据吞吐率330MSPS,输出信图2原始图像图3FPGA图像增强结果5结论实时图像处理系统以DSP和FPGA为基本结构,并在此结构的基础上进行了优化,增加了视频输入通路。

同时所有的数据交换都通过了FPGA,后期的调试过程证明这样做使得调试非常方便,既可以监视数据的交换又方便修正前期设计的错误。

整个系统结构简单,各个模块功能清晰明了。

经后期大量的系统仿真验证:系统稳定性高,处理速度快,能满足设计要求。

号兼容RS一343A/RS一170。

由FPGA产生的数字视频信号分别进入到ADV7125的三个数据通道,经数模转换后输出模拟视频信号并与原来的同步信号、消隐信号叠加后便可以在显示器上显示处理的结果了。

基于MATLAB的DSP系统设计与实现

基于MATLAB的DSP系统设计与实现数字信号处理(DSP)技术在现代通信技术中的应用越来越广泛,其中MATLAB是一种广泛使用的开发工具。

在本文中,我们将探讨基于MATLAB的DSP系统设计与实现。

1. DSP的基本概念数字信号处理是将连续时间的模拟信号转换成数字信号,并在数字域中对信号进行处理的一种技术。

DSP技术在音频、视频、图像等领域都有广泛的应用。

2. DSP系统的基本架构一个典型的DSP系统由数据输入/输出部分、数字信号处理器、存储器和控制器等组成。

其中,DSP芯片是实现数字信号处理的核心部分。

DSP芯片一般采用定点运算方式,其运算速度较快,且电路比较简单,易于实现。

另外,DSP还需要使用各种算法来实现数字信号处理功能。

这些算法包括滤波、变换、傅里叶分析等等。

3. MATLAB在DSP系统中的应用MATLAB是一种广泛使用的数学软件,其在数字信号处理领域中也有广泛的应用。

使用MATLAB,可以快速地开发和调试各种DSP算法。

MATLAB提供了丰富的函数库和工具箱,包括数字信号处理工具箱(DSP Toolbox)、信号处理工具箱(Signal Processing Toolbox)等。

这些工具箱提供了各种滤波、变换等数字信号处理算法的实现。

另外,MATLAB也提供了各种绘图和分析工具,方便用户对数字信号进行分析和可视化。

4. DSP系统的设计与实现在基于MATLAB的DSP系统设计与实现过程中,一般需要遵循以下步骤:(1)定义问题:明确数字信号处理系统的输入、输出、处理方式和性能要求等。

(2)算法设计:根据问题的要求,选择合适的数字信号处理算法,并进行算法设计。

(3)算法实现:将算法实现成MATLAB程序,并进行调试和优化。

(4)系统集成:将算法和DSP硬件进行集成并进行测试。

5. 结语基于MATLAB的DSP系统设计与实现可以大大提高数字信号处理的效率和准确性。

在实际应用中,需要对系统进行合理设计和优化,才能达到更好的效果。

基于FPGA+CPU的信号处理系统的设计与实现

• 174•基于FPGA+CPU的信号处理系统的设计与实现上海广电通信技术有限公司 李红霞【摘要】文章简要介绍了雷达信号处理的发展现状,为了解决现有的雷达信号处理系统信号处理能力弱、数据传输速率低的问题,设计开发了基于FPGA+CPU 的船用导航雷达信号处理系统。

该系统充分利用FPGA 的流水性能以及通用 CPU 的并行处理能力,将算法合理分配至不同的处理器中,实现大数据量的实时传输和高性能的实时信号处理。

文章从系统设计入手介绍了船用导航雷达信号处理系统的工作原理,简要介绍了船用导航雷达信号处理系统的硬件设计,并从信号预处理、信号处理、目标跟踪三个方面阐述了船用导航雷达信号处理系统的信号处理流程和算法设计。

【关键词】雷达信号处理系统;信号预处理;信号处理;目标跟踪0 引言船舶驾驶员在驾驶船舶过程中,需要做到瞭望、定位、导航和避碰,这就要通过船用导航雷达来保证。

船用导航雷达是船舶正常航行所必备的电子设备之一,在过弯道、船舶靠港和离开以及海上作业等方面起到了重要的作用[1]。

雷达系统的不断升级相应的要求大幅提升信号处理系统的计算速度、数据带宽和传输速率[2]。

而现有的雷达信号处理系统的运算能力较低,传送数据的速率不高,无法满足现代信号处理的需求。

因此增强雷达系统的运算能力,提高传送数据的速度是如今雷达信号处理亟待解决的问题。

本文所采用的方案,可以很好地完成实时、可靠的雷达信号处理。

本文中的信号处理系统采用ADC+FPGA+CPU 的系统架构,集高密度计算与高速数据传输于一体,实现强大的信号处理及数据交换能力[1],同时提高了系统的集成度。

1 系统设计船用导航雷达信号处理的数据量大,对实时性和数据传输速率都要求较高,本文中针对以上特点,并结合 FPGA 的流水性能以及通用 CPU 的并行处理能力,将算法合理分配至不同的处理器中,提升了信号处理能力和数据传输能力,降低成本的同时提高了系统的集成度。

船用导航雷达信号处理系统通过ADC 对视频信号进行采样,将模拟视频信号转换为数字化的视频数据。

DSP系统中PDT的设计与实现

总第172期2008年第10期舰船电子工程Ship Electronic Enginee ring Vol.28No.10101 DSP 系统中PDT 的设计与实现3亢 琰 徐火生 王 珩(武汉数字工程研究所 武汉 430074)摘 要 在实时信号处理系统中,DSP +F P G A 的系统架构具有较高的数据处理速度和较好的接口设计灵活性。

提出一个DSP +FP GA 架构的实时信号处理系统,分析该系统的存储器构成及工作原理,设计了该系统的PDT (peripher al de 2vice transfe r )传输方式,实现了DSP 的EM IF 口对高速数据的读写控制。

关键词 DSP ;FP GA ;PDT 中图分类号 TN911.72Design a nd Realizat ion of PD T i n a S ystem wit h DS PKa ng Yan X u Huoshe ng W ang He ng(Wuha n Digital Engineering Institute ,Wuhan 430074)Abs tra ct A Real 2time signal proce ssing syste m with the st ruc ture of DSP +FP GA ,specialize s in high 2speed da ta pro 2cessing and has flexibility in it s interfaces de signing.In this paper ,the author designed a Real 2time signal processing system wit h t he str ucture of DSP +FP G A ,analyzed conformation of sto rage of the syste m and its principle of f unctio n ,designed the PDT tr ansfer ring mode of the system ,and r ealized high 2speed data πs read 2write with EMIF upon the DSP.Ke y w ords DSP ,F P G A ,PDT Class N umber TN911.721 引言数字信号处理器(DSP)和现场可编程门阵列器件(F P G A),为高速、实时数字信号处理提供了很好的解决方案。

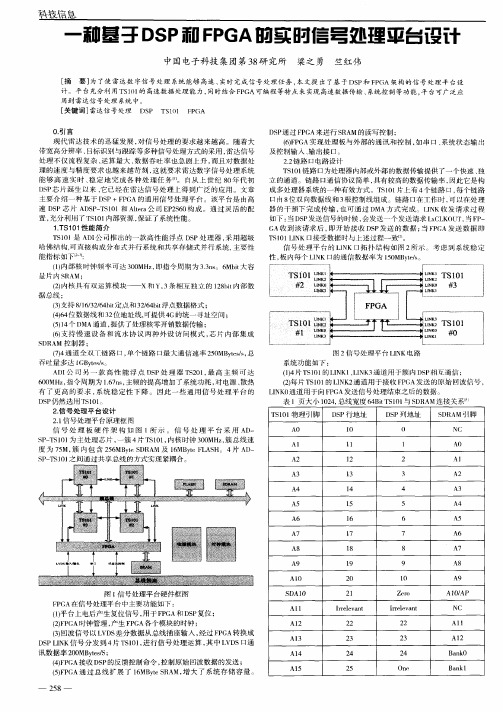

一种基于DSP和FPGA的实时信号处理平台设计

T 1 1是 A I 司推 出的一款 高性能浮点 D P处理器 . s0 D公 S 采用超级 哈佛结构 , 可直接构成 分布式并行 系统 和共享存储式并 行系统, 主要性 能 指 标 如 21 F1 : - 3 () 1内部核时钟频 率可达 30 z 即指令周 期为 33 s 内核 具有 双运算模 块——x和 Y, 条相互 独立 的 18 i内部数 3 2 bt 据 总线 ; () 3支持 81/26 bt /63/4 i 定点和 3 /4 i 26 bt 浮点数据格式 ; ()4 46 位数据线 和 3 位 地址线, 2 可提供4 G的统一寻址空 问; ()4 DMA通道 , 51 个 提供 了处理 核零开销数据传输 ; () 6支持 慢速 设 备和 流水 协议 两种 外设 访 问模式 , 芯片 内部 集成 SR D AM 控 制 器 ; ()通 道全双T链路 V , 74 I单个链路 V最大通信速率 20 ye/, I 5 MB ts 总 s

用到 雷 达 信 号 处 理 系统 中。

[ 关键词 ] 雷达信 号处理

O 引 言 .

DS T 11 F G P S 0 P A D P通过 F G S P A来进行 S M的读写控制 ; RA ()P 6F GA实现 处理板与外 部的通讯 和控制 , 如串 口 、 系统 状态输 出 及 控 制 输 入 、 出接 口 。 输 22 路 口 电路 设 计 .链

T 1 1物 理 引 脚 D P行 地 址 S0 S

A0

A1

21 .信号处理平 台原理框 图 信 号 处 理 板 硬 件 架 构 如 图 1 示 。信 号 处 理 平 台 采 用 A 所 D— s — s 0 为 主 处 理 芯 片 , 簇 4片 T 1 1 内 核 时 钟 3 0 P T l1 一 S0 , 0 MHz簇 总 线 速 , 度 为 7 M, 内包 含 2 6 yeS AM及 1MB t F A H。4片 A 5 簇 5 MB t DR 6 ye L S D— S — SIl P T 之间通过共享总线 的方式实现 紧耦合 。 O

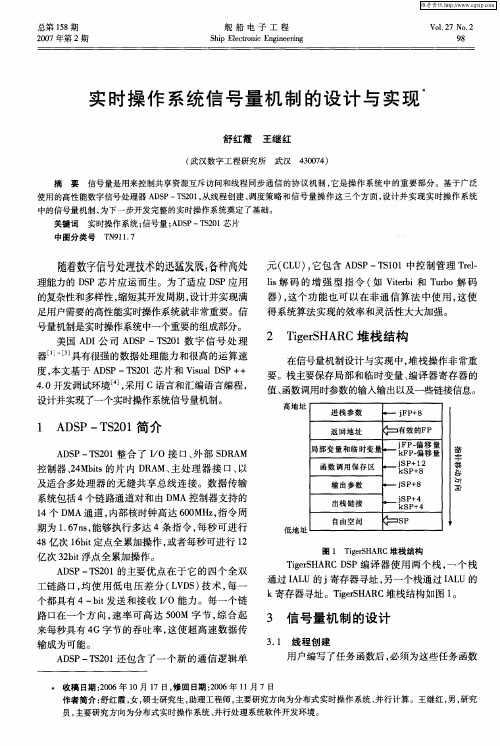

实时操作系统信号量机制的设计与实现

3 信 号 量 机 制 的 设 计

3 1 线程 创 建 .

来每秒具有 4 G字节的吞 吐率 , 这使超高速数据传

输 成为 可能 。

A S T21 D P— S0 还包含 了一 个新 的通信逻辑单

收稿 日期 :06年 1 20 0月 1 7日, 回 日期 : 0 修 2 6年 1 月 7日 0 1

20 0 7年第 2 期

舰 船 电 子 工 程

9 9

创 建线 程 。每个 线程拥 有 自己 的栈空 间 , 有 自己 并

3 3 信 号量 .

的优先级 。为用户任务 函数创建的线程 , 其优先级 由用 户定 义 。定义 空 闲任 务 (de 的优 先 级 为 25 il) 5 ( 最低 )线程优先级最 高为 0 其 中优 先级处于 0 , , 到l 5之间的线程属于高优先级线程 , 其余 的线程

l 解 码 的增 强 型 指令 ( Vt b 和 T r i s 如 iri e u o解 码 b 器) 这个功能也可 以在非通 信算法 中使用 , , 这使 得系统算法实现的效率和灵活性大大加强 。

2 TgrH R i S A C堆栈结构 e

在信号量机制设计与实现中, 堆栈操作非常重

的复杂性和多样性 , 缩短其开发周期, 设计并实现满 足用户需要的高性能实时操作系统就非常重要。信 号量机制是实时操作系统中一个重要的组成部分。 美国 A I 司 A S T 2 1 字信 号 处理 D公 D P— S0 数 器¨ 具有很强的数据处理能力和很高的运算速 卜3

度, 本文基于 A S T 21 D P— S0 芯片和 Vsa D P+ i lS + u 40开发调试环境 , . J采用 c语言和汇编语言编程 ,

ISAR实时成像处理实验系统的设计与实现

ISAR实时成像处理实验系统的设计与实现ISAR(Inverse Synthetic Aperture Radar)技术是一种通过倒时域合成孔径雷达图像的方法,可以获取被测目标的高分辨率、全景、全方位的雷达图像。

ISAR实时成像处理实验系统是一种用于实时处理ISAR数据并实时显示成像结果的系统。

本文将对ISAR实时成像处理实验系统的设计与实现进行详细介绍。

一、系统设计ISAR实时成像处理实验系统的主要功能是实时处理ISAR数据,包括数据预处理、信号处理、成像处理和结果显示等。

系统硬件主要包括雷达天线、采集设备和计算机等部分。

系统软件主要包括ISAR数据处理算法和图像显示算法。

1.雷达天线:选择合适的雷达天线是系统设计的重要环节。

雷达天线的选择应具备较宽的角度覆盖范围、较高的增益和较低的杂散波,以保证对被测目标的较好信号接收能力。

2.采集设备:采集设备主要用于采集雷达接收到的信号并对其进行初步处理。

采集设备应具备高速、高精度的数据采集能力,以满足实时处理的需求。

3.计算机:计算机是整个系统的核心部分,负责对采集到的数据进行实时处理和成像处理。

计算机应具备较高的计算性能和较大的存储容量,以满足实时处理和存储大量数据的需求。

4.系统软件:系统软件主要包括ISAR数据处理算法和图像显示算法。

ISAR数据处理算法用于对采集到的数据进行预处理、信号处理和成像处理等。

图像显示算法用于将处理后的数据以图像的形式显示出来,以便用户进行观察和分析。

二、系统实现1.硬件搭建首先需要根据系统设计的要求选择合适的硬件设备,包括雷达天线、采集设备和计算机等。

根据设备的技术规格和接口要求进行连接和设置,以确保硬件设备正常工作。

其中,雷达天线需要安装在适当的位置,并调整好姿态和方向,以保证对目标的信号接收能力。

2.软件开发首先需要编写数据采集和预处理的软件模块,用于采集和处理雷达接收到的信号。

数据采集模块应具备高速、高精度的数据采集能力,预处理模块应包括滤波、去除杂散波等处理步骤。

实时视频信号采集与处理系统设计与实现

( eat etfE 加, ad I om t nTcn u ,I ,ab 50 1 C i D p r n o c l n fr ai eh i eH TH ri 10 0 , hn m n o q n a)

20 07拄

3 硬 件 设 计

整个 电路 由三 个 部分 组 成 : 频 信 号 的采 集 和 视 恢 复 , 于数字 视频 信 号 的控 制 和使 用 大 型 可 编程 对 逻辑 器件 F G P A进行 数据处 理 。

3 1 视频信 号 的采集 .

高 的重用性 。 3 3 使用 F G . P A进行 复杂 的 图像处 理

摘 要 : 绍采 用视 频编 解 码器 实现视 频信号 的采 集 , 用 At a公 司 的 E L 介 使 lr e P D和 S A 实现 RM

视频图像 的存储和 回放功能, 最后介绍使用 F G P A和 S A R M完成 系统扩展 , 搭建 了一套完整的图像 采 集和处 理平 台。 关键词 : 视频编解码 ; 微处理机 ; 现场可编程门阵列(P A FG ) 中图分 类号 :P 30 2 文献标 识码 : T S6 . 1 B 文章编 号 :02—27 (07 0 09 10 29 20 )3— 05—0 4

维普资讯

第 3期 20 0 7年 6月

微

Байду номын сангаас

处

理

机

No 3 .

MI CROP ROCES OR S S

Jn 2 0 u .,0 7

实 时视 频 信 号 采集 与处 理 系 统 设 计 与 实 现

李一鹏 , 张晓峰 , 张 晔

数字信号处理实时动态实验演示系统设计与实现

关键词 :数字信号处理 ;动态演示 ;M t b a a l

中图分类号 : P 9 T 31 文献标 识码 : B 文章 编号:10 -9 6 2 0 ) 8 0 5 — 3 0 24 5 ( 06 0 — o 0 0

De n tai n s se d sg n e l a i n f rd g tlsg a r c s i g c u s mo sr t y tm e i n a d r a i t o i i in lp o e sn o re o z o a

(n nt i us rsos,简 称 I 、FR ( nt if i mpl epne i e e I R) I f i i e ipl epne m us rsos,简称 FR) 数 字滤 波器 的设 计 与 e I

学习质量都受到一定影响 ,因此 ,对这门课程的教

和学 的难 度 系数都 很大 。 本 文介绍 了 “ 数字 信号 处理 ”实 时动 态实验 演 示 系统 的设 计 与 实 现 方 法 ,利 用 Ma ̄ 的 图形 界 t l

域和频域 的离散对应关系、频谱特性以及它们在实

际中的应用。第 5章 主要讲解 模拟 滤波器 和 I I R

Ke od : i t i a poes g ya cdmosai ;M t b yw r s dga s l r si ;dnmi e nt t n al il g c n n ro a

数字信号处理是 2 O世纪 6 0年代 以来 ,随着大 规模 集成 电路 和计 算机 技术 的发 展而迅 速发 展起来 的一门新兴学科。它以精度高、灵活性大、可靠性 强 、易于大规模集成等优点在通信 、雷达 、地震 、 声纳 、遥感和生物医学等领域得到了越来越广泛的

su e t i ls , te a n e tn h o re moe e i .T a hn f c sa e i r v d ef in l . t d n s n ca s h y c n u d r a d t e c u s r a l s s y e c i g e e t r mp o e f c e t i y

基于声卡的双通道实时信号采集处理系统设计

基于声卡的双通道实时信号采集处理系统设计韩红帮1,解永刚2,张恒云3,杨亚彪1,李海雁1(1.昆明学院现代教育技术中心,云南昆明650214;2.昆明学院资产管理与设备处,云南昆明650214;3.昆明学院化学科学与技术系,云南昆明650214)摘要:采用声卡代替商用数据采集卡,利用Visual C++软件编程技术,设计了基于声卡的双通道实时信号采集处理系统,该系统能够实现25kHz 范围内双路信号的实时采集、实时分析,所采集数据的存储和网络发送等功能,系统实用性较强,可广泛应用于各高校实验室及实时语音信号处理等领域。

关键词:声卡;信号采集;信号处理;系统设计中图分类号:TP274.2文献标识码:A文章编号:1674-6236(2013)02-0001-03Design of double -channel real -time signal collecting and disposal systembased on sound cardHAN Hong -bang 1,XIE Yong -gang 2,ZHANG Heng -yun 3,YANG Ya -biao 1,LI Hai -yan 1(1.The Center of Modern Education Technology ,Kunming University ,Kunming 650214,China ;2.Office of Asset and Equipment Management ,Kunming University ,Kunming 650214,China ;3.The Department of Chemistry ,Kunming University ,Kunming 650214,China )Abstract:This article aims at the design of double -channel real -time signal collecting and disposal system based on sound card by means of replacing commercial data collecting card with sound card ,with the application of Visual C++software programming technology.This system is capable of the real -time collecting ,analysis ,storage and online transmitting of the double -channel signals within the range of 25kHz.And the author believes that this system is of high practical applicability which ensures its full use in university laboratories and other certain fields like real -time voice signal deposal.Key words:sound card ;signal collecting ;signal disposal ;system design收稿日期:2012-09-22稿件编号:201209163基金项目:云南省教育厅科学研究基金项目(2011Y238)作者简介:韩红帮(1977—),男,云南曲靖人,硕士,实验师。

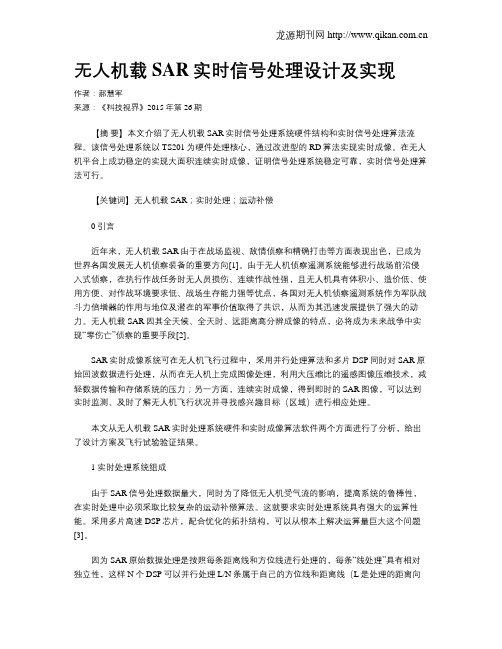

无人机载SAR实时信号处理设计及实现

无人机载SAR实时信号处理设计及实现作者:郝慧军来源:《科技视界》2015年第26期【摘要】本文介绍了无人机载SAR实时信号处理系统硬件结构和实时信号处理算法流程。

该信号处理系统以TS201为硬件处理核心,通过改进型的RD算法实现实时成像。

在无人机平台上成功稳定的实现大面积连续实时成像,证明信号处理系统稳定可靠,实时信号处理算法可行。

【关键词】无人机载SAR;实时处理;运动补偿0 引言近年来,无人机载SAR由于在战场监视、敌情侦察和精确打击等方面表现出色,已成为世界各国发展无人机侦察装备的重要方向[1]。

由于无人机侦察遥测系统能够进行战场前沿侵入式侦察,在执行作战任务时无人员损伤、连续作战性强,且无人机具有体积小、造价低、使用方便、对作战环境要求低、战场生存能力强等优点,各国对无人机侦察遥测系统作为军队战斗力倍增器的作用与地位及潜在的军事价值取得了共识,从而为其迅速发展提供了强大的动力。

无人机载SAR因其全天候、全天时、远距离高分辨成像的特点,必将成为未来战争中实现“零伤亡”侦察的重要手段[2]。

SAR实时成像系统可在无人机飞行过程中,采用并行处理算法和多片DSP同时对SAR原始回波数据进行处理,从而在无人机上完成图像处理,利用大压缩比的遥感图像压缩技术,减轻数据传输和存储系统的压力;另一方面,连续实时成像,得到即时的SAR图像,可以达到实时监测、及时了解无人机飞行状况并寻找感兴趣目标(区域)进行相应处理。

本文从无人机载SAR实时处理系统硬件和实时成像算法软件两个方面进行了分析,给出了设计方案及飞行试验验证结果。

1 实时处理系统组成由于SAR信号处理数据量大,同时为了降低无人机受气流的影响,提高系统的鲁棒性,在实时处理中必须采取比较复杂的运动补偿算法。

这就要求实时处理系统具有强大的运算性能。

采用多片高速DSP芯片,配合优化的拓扑结构,可以从根本上解决运算量巨大这个问题[3]。

因为SAR原始数据处理是按照每条距离线和方位线进行处理的,每条“线处理”具有相对独立性,这样N个DSP可以并行处理L/N条属于自己的方位线和距离线(L是处理的距离向或方位向长度)[4]。

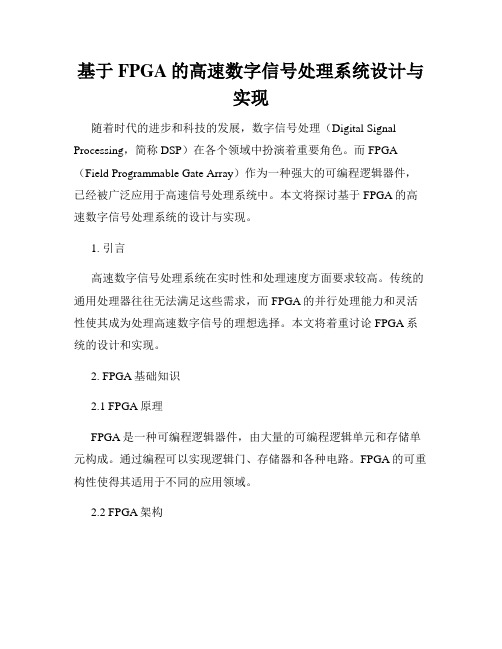

基于FPGA的高速数字信号处理系统设计与实现

基于FPGA的高速数字信号处理系统设计与实现随着时代的进步和科技的发展,数字信号处理(Digital Signal Processing,简称DSP)在各个领域中扮演着重要角色。

而FPGA (Field Programmable Gate Array)作为一种强大的可编程逻辑器件,已经被广泛应用于高速信号处理系统中。

本文将探讨基于FPGA的高速数字信号处理系统的设计与实现。

1. 引言高速数字信号处理系统在实时性和处理速度方面要求较高。

传统的通用处理器往往无法满足这些需求,而FPGA的并行处理能力和灵活性使其成为处理高速数字信号的理想选择。

本文将着重讨论FPGA系统的设计和实现。

2. FPGA基础知识2.1 FPGA原理FPGA是一种可编程逻辑器件,由大量的可编程逻辑单元和存储单元构成。

通过编程可以实现逻辑门、存储器和各种电路。

FPGA的可重构性使得其适用于不同的应用领域。

2.2 FPGA架构常见的FPGA架构包括查找表(Look-up Table,简称LUT)、寄存器和可编程互连网络。

LUT提供逻辑功能,寄存器用于数据存储,而可编程互连网络则实现不同逻辑单元之间的连接。

3. 高速数字信号处理系统设计3.1 系统需求分析在设计高速数字信号处理系统之前,需要明确系统的需求和目标。

这可能包括处理速度、资源利用率、功耗等方面的要求。

3.2 系统架构设计基于FPGA的高速数字信号处理系统的架构设计是关键步骤之一。

需要根据系统需求和目标来选择合适的算法和硬件结构。

可以采用流水线结构、并行处理结构等以提高处理速度。

3.3 硬件设计硬件设计包括选择FPGA器件、选择合适的外设、设计适配电路等。

通过合理的硬件设计可以实现信号处理系统的高速和稳定运行。

4. 实现与验证4.1 FPGA编程使用HDL(Hardware Description Language)进行FPGA编程。

常用的HDL语言包括VHDL和Verilog。

嵌入式系统中的实时信号处理与滤波器设计方法

嵌入式系统中的实时信号处理与滤波器设计方法近年来,随着科技的不断发展,嵌入式系统在各个领域中得到了广泛的应用。

从智能手机到汽车电子,从医疗设备到工业自动化,嵌入式系统的应用范围越来越广泛。

而实时信号处理和滤波器设计方法则是嵌入式系统中不可或缺的一部分。

本文将探讨嵌入式系统中的实时信号处理和滤波器设计方法,并介绍一些常用的技术和算法。

在嵌入式系统中,实时信号处理是指对输入信号进行实时处理和分析的过程。

这些输入信号可以是来自传感器、音频设备、视频设备等等。

实时信号处理的目标是提取有用的信息,滤除噪声和干扰,并根据需要进行信号增强或变换。

为了实现实时信号处理,嵌入式系统需要具备高性能的处理器和适当的算法。

在嵌入式系统中,滤波器是实现实时信号处理的重要工具。

滤波器可以根据信号的频率特性对信号进行增强或抑制。

常见的滤波器类型包括低通滤波器、高通滤波器、带通滤波器和带阻滤波器。

滤波器的设计方法可以根据不同的需求选择,包括传统的模拟滤波器设计方法和数字滤波器设计方法。

传统的模拟滤波器设计方法主要包括基于电容、电感和电阻的滤波器设计。

这些滤波器设计方法通常适用于频率较低的信号处理应用。

例如,用于音频信号处理的滤波器设计。

这些滤波器设计方法需要考虑电路的稳定性、频率响应和相位响应等因素,需要进行精确的电路设计和参数调整。

数字滤波器设计方法则更适用于嵌入式系统中的实时信号处理。

数字滤波器可以通过数字信号处理器(DSP)或嵌入式微处理器来实现。

数字滤波器的设计方法主要包括有限冲激响应(FIR)滤波器和无限冲激响应(IIR)滤波器。

FIR滤波器是一种线性相位滤波器,具有稳定性和易于设计的特点。

IIR滤波器则具有更高的滤波器阶数和更小的存储器需求,但设计和实现相对复杂一些。

在数字滤波器设计中,滤波器的性能评估是一个重要的环节。

常用的性能评估指标包括频率响应、幅频特性、相频特性和群延迟等。

这些指标可以通过滤波器设计软件进行仿真和优化,以达到设计要求。

卫星定位信号实时处理实验平台的设计与实现

卫星定位信号实时处理实验平台的设计与实现

龚国辉;李思昆

【期刊名称】《计算机工程与科学》

【年(卷),期】2006(028)006

【摘要】本文设计了卫星定位信号实时处理实验平台.该平台接收卫星定位信号,经射频电路变换为数字中频信号后分为两路输出:一路与FPGA开发板相接,用于数字卫星定位接收机的研制;另一路通过并行口EPP协议送至主机,用于软件卫星定位接收机的开发.该平台提供了卫星信号处理基础算法库和基础软核库,可有效支持卫星定位接收机的软硬件开发.目前已经基于该实验平台完成了数字GPS接收机原型的设计和软件GPS接收机原型的开发.平台的兼容性很好,只需更换射频电路,即可用于新一代卫星定位接收机的研究开发.应用效果表明,使用该平台可显著提高开发效率和质量.

【总页数】5页(P126-130)

【作者】龚国辉;李思昆

【作者单位】国防科技大学计算机学院,湖南,长沙,410073;国防科技大学计算机学院,湖南,长沙,410073

【正文语种】中文

【中图分类】TP391

【相关文献】

1.云南省广播电视村村通直播卫星接收信号监测平台系统设计与实现 [J], 韩正强;施旭东;

2.基于高性能机群的环境一号C卫星SAR图像全分辨率快视实时处理系统设计与实现 [J], 李景山;温双燕;王建;仲利华;张问一

3.云南省广播电视村村通直播卫星接收信号监测平台系统设计与实现 [J], 韩正强;施旭东

4.KSA高速卫星基带数据实时处理架构设计与实现 [J], 钟瑜;刘红伟

5.广播电视直播卫星接收信号监测平台系统的设计与实现分析 [J], 魏亚峰

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Xilinx CLB

Configurable logic block (CLB) Slice CLB CLB Logic cell Logic cell Slice Logic cell Logic cell

Slice CLB CLB Logic cell Logic cell

Slice Logic cell Logic cell

系统实时性(1)

将数字信号处理系统的功能定义为一个变换Tj,对输 入信号xi(n)进行处理,得到输出信号yj(m)。

y j m Tj x n

x n

T xn , n 0,1,

y m

L 1

T xn , n L, L 1,

2 L 1

»三维优化 (面积,速度,功耗) »实现预期的速度—面积—功率折衷 »功耗

P C V f

2

»延迟减低技术→通过低电压操作提高速度和降 低功耗; »由于乘法运算在信号处理中占主导地位,减少 乘法的操作次数至关重要(通过强度缩减实现 )。

并行处理机制

采用并行处理加快处理速度(性能)

» 模块颗粒度 – 工作(job),任务(Task),过程(Process),变量( Variable),位(Bit) » 并发控制

– 中央控制(编程) – 数据驱动

数据流, 需求驱动

» 通信过程

– 专业网络结构 – 共享存储器

» 问题规模

– 模块数 – 内存大小

鸿沟解决方案

更高…高性能的通用处理器

» 实质上为一种软件计算系统—利用软件和硬件辅助逻辑 实现信号处理计算。

性能更高的定制VLSI电路

» 灵活性(易变性)差,价格竞争力弱。

实时信号处理-信号处理系统的设计与实现,J.G.Ackenhusen著 ,李玉柏 等译,电子工业出版社,2002 VLSI数字信号处理-设计与实现,张欣 著,科学出版社,2003 无线通信FPGA设计,田耘 等编, 电子工业出版社,2008

讲授内容安排

1.绪论

» 数字信号处理与FPGA,数字信号处理的技术要求、设计 与实现

Tc

Ty

系统实时性(2)

Tc < LTx时输入和相应输出的定时关系

» Tc小于帧持续时间,输出总能跟上输入

x n

y m

Tc

y 0

y 1

Tc Tc

y 2

Tc

y 3

系统实时性(3)

Tc > LTx时输入和相应输出的定时关系

» Tc 小于帧持续时间,前一帧的计算要在下一帧的最后一 个样本到达之后才能完成,输出会越来越落后于输入

FPGA非常适合弥补复杂算法和处理器之间存在的 性能鸿沟

» » » » » » » 能实现并行处理,具有极高性能的信号处理能力; 体系结构灵活,实现风险较低; 允许设计移植,以处理不断变化的设计需求; 开发人员可创建一个定制的、与众不同的解决方案 ; 价格下降空间较大; 从功能实现角度计算,功耗较低。 可用设计资源:IP核

FPGA和CPLD结构

FPGA

CPLD

现场可编程逻辑阵列 FPGA(1)

可配置逻辑资源

»可配置逻辑块(Configurable logic Blocks, CLBs)

– 基本功能单元 — 一般以整列形成遍布整个芯片

FPGA(2)

»I/O 块(I/O Blocks,IOBs)

– 内部逻辑和外部封装引脚的接口电路.

» 目标:通过数字电路结构完成算法的运算结构 » 结构设计完全以算法结构为核心,以数字电路为目标。 » 区别于通用结构器件:计算系统固定,以组织指令实现 算法软件结构为目标。

核心实现技术

算法分析

»针对系统设计目标,寻找适合用简单数字逻辑电 路实现的计算方法。 »计算结构分析——寻找计算过程的优化方法,降 低计算复杂度 »算子机构分析——寻找算子合并或分解的可能性 ,找出最简单的算子模块电路 »注意:必须以数字电路为基本出发点,才能得到 正确的分析结果!

Xilinx Logic Cell

16-bit SR 16x1 RAM

a b c d e clock clock enable set/reset

4-input LUT

y mux flip-flop q

Xilinx Virtex-II Pro FPGA 体系结构

Configurable logic block (CLB) Slice CLB CLB Logic cell Logic cell Slice Logic cell Logic cell

x n

y m

Tc LTx

y 0

y 1

y 2

Tc LTx

Tc

LTx

系统实时性(4)

实时概念

» 如果在使用变换Tj计算每个输出样本yj(m)的时候,完成 计算所需时间不超过对输出yj(m)有影响的所有xi(n)的 持续时间,则称该系统是实时的。 » 核心意义:实时系统的基本要求就是对xi(n)进行的计算 Tj必须在特定时间内完成,这个时间就是样本集xi(n)的 持续时间。

实时信号处理系统设计与实现

王明全 wmingquan@ 2014

课程目标

了解

»实时信号处理的概念、技术和发展趋势

掌握

»算法从通用计算环境移植到VLSI结构的方法

重点

»基于FPGA的数字信号处理系统的设计和实现技 术

学时:40(第1~10周)

相关课程

基础课程

»数字电路设计,信号与系统 »数字信号处理理论 »可编程逻辑器件与EDA技术 »硬件描述语言(VHDL或Verilog)

专用结构 (全定制VLSI电路)

» 实现速度、结构和功耗的整体优化; » 功能针对算法专门设计; » 并行计算结构,系统处理速度提高; » 灵活性(通用性)差,价格竞争优势弱; » 一般用作协处理器。

数字信号处理系统性能衡量标准

所需的硬件电路资源或软件空间 由数据吞吐量和时钟频率决定的运行速度 实现既定任务I Digital Signal Processing Systems – Design and Implementation, keshab K. Parhi, Wiley, 1999 中译本:VLSI数字信号处理系统设计与实现,陈弘 毅 等译,机械工业出版社,2004

参考书目(2)

典型DSP系统设计流程

规范 / 标准 描述系统功能的文档

浮点系统模型

C, Matlab, Simulink等代码 浮点代码被转化为定点的C, Matlab, Simulink代码, 然后对照浮点模型做误差分析和性能比对。 用VHDL或Verilog实现的定点系统模型,该模型可由EDA 工具(高层次综合工具、Xilinx System Generator等) 或手工实现。

标准电路

定制电路

固定连线

模拟电路 标准逻辑

定制可编程

半定制

手工制版图

存储器 可编程

RAM 微处理器 可编程DSP

连线 可编程

PROM EPROM ROM

可编程 逻辑

FPL 门海 CPLD FPGA SPLD

门阵列

标准 单元

全定制

基于单 元定制

ULA Megacell MasterSlice Composite cells NAND阵列

y n a x n b x n 1 c x n 2 end

nT 3T 2T T 0

……

信号

算法

输出

数字信号处理应用

典型数字信号处理算法

卷积,相关和数字滤波器 随机梯度和最小均方差自适应滤波器 快匹配算法和离散余弦变换 (DCT)——运动 估计 矢量量化——图像处理和压缩 Viterbi算法——动态规划 抽取和插值——多速率信号处理 小波和滤波器组

后续课程

» VLSI数字信号处理系统设计 » 嵌入式实时信号处理技术及应用实践

– 信号与信息处理和电子与通信工程专业研究生学位课

教材

Digital Signal Processing with FPGA (3rd Edition), Uwe Meyer-Baese, Springer, 2007 第2版中译本:数字信号处理的FPGA实现,刘凌 译,清华大学出版社,2006

»互联资源 — 布线通道

– CLB 和 IOB 之间的布线通道 – 包括各种长度的连线和可编程连接开关,将各个可编 程逻辑块或I/O块连接起来,构成特定功能的电路

FPGA(3)

主要生产厂商

»Xilinx, Altera — 市场领导者和长期竞争对手 »其他厂商

– Lattice Semiconductor (基于flash, 基于SRAM) – Actel (反熔丝, 基于flash, 混合信号产品) – SiliconBlue Technologies (低功耗) – Achronix (SPEEDSTER SD60 – RAM based, 1.5 GHz fabric speed) – QuickLogic (主打重点客户特定标准产品, 非通用 FPGAs)

»由量化和四舍五入造成

CMOS工艺进展

性能鸿沟!(1)

随着应用需求的不断提升,以及算法复杂度 的不断增高,对更高性能的信号处理器的需 求不断增加,传统的固定架构的DSP处理器 无法应对; 在处理复杂度不断提升的算法的高性能模块 时,需要采用DSP协处理器。

性能鸿沟!(2)

面积—速度—功耗的折衷考虑