TI TMS320C6655和TMS320C6657开发板开发板硬件说明书

1-2-TI TMS320C6655创龙开发板硬件说明书2

TMS320C6655(TL665x-EasyEVM)创龙开发板硬件说明书2 TMS320C6655(TL665x-EasyEVM)是创龙基于SOM-TL665x核心板研发的一款TI C66 x多核定点/浮点高性能DSP创龙开发板,采用核心板+底板方式,底板尺寸为200mm*1 06.65mm,采用4*50pin和1*80pin B2B工业级连接器,稳定、可靠、便捷,可以帮助客户快速评估核心板性能。

TMS320C6655(TL665x-EasyEVM)创龙开发板底板采用4层无铅沉金电路板设计,为了方便用户学习开发参考使用,上面引出了各种常见的接口。

共有2个系统复位按键(SW7:FULL RESET,SW5:WARM RESET),2个用户测试用按键(SW3:NMI,SW4:USER0),硬件及引脚定义如下创龙开发板图:9 TMS320C6655按键创龙开发板图19 FULL RESET创龙开发板图20 SW7创龙开发板图21 WARM RESET创龙开发板图22 SW5创龙开发板图23 USER创龙开发板图2410 TMS320C6655启动拨码开关SW2设有5位启动拨码开关,ON为1,硬件及引脚定义如下创龙开发板图:创龙开发板图25创龙开发板图2611 TMS320C6655 JTAG仿真器接口创龙开发板引出1个TI Rev B JTAG接口(CON4),间距为2.54mm,DC3-14P简易牛角座,硬件及引脚定义如下创龙开发板图:创龙开发板图27创龙开发板图2812 TMS320C6655 串口创龙开发板上共引出了2个串口,分别是CON1(UART1)、CON3(UART0)。

UART1通过MAX3232EUE串口电平转换芯片转换为RS232串口,使用DB9公座接口。

UART0则是使用CH340转成Micro USB接口,创龙开发板默认使用UART0进行调试。

硬件及引脚定义如下创龙开发板图:创龙开发板图29 UART1创龙开发板图30 创龙开发板CON1创龙开发板图31 创龙开发板UART0创龙开发板图32 创龙开发板CON3 13 TMS320C6655 千兆以太网口创龙开发板引出1个千兆意外网口(CON5),采用了Marvell Alaska 88E1112网络芯片,可自适应10/100/1000M网络,RJ45连接头内部已经包含了耦合线圈,因此不必另接网络变压器,使用普通的直连网线即可连接本创龙开发板至路由器或者交换机,若是PC和创龙开发板直接相连需要使用交叉网线。

TMS320C6655 57产品预览信息说明书

TMS320C6655/57Fixed and Floating-Point Digital Signal Processor Data ManualPRODUCT PREVIEW information applies to products in theformative or design phase of development. Characteristic dataand other specifications are design goals. Texas Instrumentsreserves the right to change or discontinue these productswithout notice.Literature Number:SPRS814March 2012SPRS814—March 2012Data Manual TMS320C6655/57Release HistoryFor detailed revision information, see ‘‘Revision History’’ on page A-226.RevisionDate Description/Comments SPRS841 March 2012Initial releaseFixed and Floating-Point Digital Signal ProcessorSPRS814—March 2012TMS320C6655/ Contents1Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131.1KeyStone Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141.2Device Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141.3Functional Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162Device Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172.1Device Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172.2DSP Core Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182.3Memory Map Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .212.4Boot Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .252.5Boot Modes Supported and PLL Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .252.5.1Boot Device Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .262.5.2Device Configuration Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .262.5.3PLL Boot Configuration Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332.6Second-Level Bootloaders . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332.7Terminals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .342.7.1Package Terminals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .342.7.2Pin Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .342.8Terminal Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .392.9Development and Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .632.9.1Development Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .632.9.2Device Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .632.10Related Documentation from Texas Instruments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .653Device Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .663.1Device Configuration at Device Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .663.2Peripheral Selection After Device Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .673.3Device State Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .673.3.1Device Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .703.3.2Device Configuration Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .713.3.3JTAG ID (JTAGID) Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .723.3.4Kicker Mechanism (KICK0 and KICK1) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .723.3.5LRESETNMI PIN Status (LRSTNMIPINSTAT) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .723.3.6LRESETNMI PIN Status Clear (LRSTNMIPINSTAT_CLR) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .733.3.7Reset Status (RESET_STAT) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .743.3.8Reset Status Clear (RESET_STAT_CLR) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .753.3.9Boot Complete (BOOTCOMPLETE) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .753.3.10Power State Control (PWRSTATECTL) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .763.3.11NMI Event Generation to CorePac (NMIGRx) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .763.3.12IPC Generation (IPCGRx) Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .773.3.13IPC Acknowledgement (IPCARx) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .783.3.14IPC Generation Host (IPCGRH) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .783.3.15IPC Acknowledgement Host (IPCARH) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .793.3.16Timer Input Selection Register (TINPSEL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .803.3.17Timer Output Selection Register (TOUTPSEL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .823.3.18Reset Mux (RSTMUXx) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .833.3.19Device Speed (DEVSPEED) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .843.3.20Pin Control 0 (PIN_CONTROL_0) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .843.3.21Pin Control 1 (PIN_CONTROL_1) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .863.3.22UPP Clock Source (UPP_CLOCK) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .863.4Pullup/Pulldown Resistors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .874System Interconnect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .884.1Internal Buses and Switch Fabrics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .884.2Switch Fabric Connections Matrix. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .894.3TeraNet Switch Fabric Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .914.4Bus Priorities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .954.4.1Packet DMA Priority Allocation (PKTDMA_PRI_ALLOC) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .954.4.2EMAC / UPP Priority Allocation (EMAC_UPP_PRI_ALLOC) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95SPRS814—March 2012Fixed and Floating-Point Digital Signal Processor TMS320C6655/57 5C66x CorePac . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .975.1Memory Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .985.1.1L1P Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .985.1.2L1D Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .995.1.3L2 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .995.1.4MSM SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1015.1.5L3 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1015.2Memory Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1015.3Bandwidth Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1025.4Power-Down Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1025.5C66x CorePac Revision. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1035.6C66x CorePac Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1036Device Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1046.1Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1046.2Recommended Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1056.3Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1066.4Power Supply to Peripheral I/O Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1077Peripheral Information and Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1087.1Recommended Clock and Control Signal Transition Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1087.2Power Supplies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1087.2.1Power-Supply Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1097.2.2Power-Down Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1147.2.3Power Supply Decoupling and Bulk Capacitors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1147.2.4SmartReflex. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1147.3Power Sleep Controller (PSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1167.3.1Power Domains. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1167.3.2Clock Domains. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1177.3.3PSC Register Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1187.4Reset Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1207.4.1Power-on Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1217.4.2Hard Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1227.4.3Soft Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1237.4.4Local Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1247.4.5Reset Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1247.4.6Reset Controller Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1257.4.7Reset Electrical Data / Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1257.5Main PLL and PLL Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1277.5.1Main PLL Controller Device-Specific Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1287.5.2PLL Controller Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1307.5.3Main PLL Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1367.5.4Main PLL and PLL Controller Initialization Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1377.5.5Main PLL Controller/SRIO/HyperLink/PCIe Clock Input Electrical Data/Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1377.6DD3 PLL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1407.6.1DDR3 PLL Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1407.6.2DDR3 PLL Device-Specific Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1417.6.3DDR3 PLL Initialization Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1417.6.4DDR3 PLL Input Clock Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1427.7Enhanced Direct Memory Access (EDMA3) Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1437.7.1EDMA3 Device-Specific Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1447.7.2EDMA3 Channel Controller Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1447.7.3EDMA3 Transfer Controller Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1447.7.4EDMA3 Channel Synchronization Events. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1457.8Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1477.8.1Interrupt Sources and Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1477.8.2CIC Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1627.8.3Inter-Processor Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1687.8.4NMI and LRESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1697.8.5External Interrupts Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169Fixed and Floating-Point Digital Signal ProcessorSPRS814—March 2012TMS320C6655/57 7.9Memory Protection Unit (MPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1717.9.1MPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1747.9.2MPU Programmable Range Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1817.10DDR3 Memory Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1867.10.1DDR3 Memory Controller Device-Specific Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1867.10.2DDR3 Memory Controller Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1877.11I 2C Peripheral . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1877.11.1I 2C Device-Specific Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1877.11.2I 2C Peripheral Register Description(s). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1887.11.3I 2C Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1897.12SPI Peripheral . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1927.12.1SPI Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1927.13HyperLink Peripheral. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1957.13.1HyperLink Device-Specific Interrupt Event. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1957.13.2HyperLink Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1977.14UART Peripheral. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1997.15PCIe Peripheral. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2007.16EMIF16 Peripheral. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2017.16.1EMIF16 Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2017.17Ethernet Media Access Controller (EMAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2047.17.1EMAC Device-Specific Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2047.17.2EMAC Peripheral Register Description(s). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2057.17.3EMAC Electrical Data/Timing (SGMII) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2097.18Management Data Input/Output (MDIO). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2097.18.1MDIO Peripheral Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2107.18.2MDIO Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2107.19Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2127.19.1Timers Device-Specific Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2127.19.2Timers Electrical Data/Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2127.20Serial RapidIO (SRIO) Port. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2137.21General-Purpose Input/Output (GPIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2147.21.1GPIO Device-Specific Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2147.21.2GPIO Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2147.22Semaphore2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2147.23Emulation Features and Capability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2157.23.1Advanced Event Triggering (AET) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2157.23.2Trace. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2157.23.3IEEE 1149.1 JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2167.24Enhanced Viterbi-Decoder Coprocessor (VCP2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2177.25Turbo Decoder Coprocessor (TCP3d). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2177.26Multichannel Buffered Serial Port (McBSP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2187.26.1McBSP Peripheral Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2187.26.2McBSP Electrical Data/Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2197.27Universal Parallel Port (UPP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2227.27.1UPP Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222A Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226B Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227B.1Thermal Data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227B.2Packaging Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227。

TI TMS320C6678开发板使用之软件安装说明书

TI TMS320C6678开发板使用之软件安装说明书RevisionHistoryDraftDate Revision No. Description2016/04/21 V1.1 1.排版修改。

目录1 SecureCRT调试终端软件安装 (3)1.1软件安装 (3)1.2串口连接设置 (8)1.3SSH连接设置 (9)2 Windows版本CCS5.5安装 (11)3 TI v7.4.14编译工具安装 (17)4 SYS/BIOS组件安装 (21)4.1安装SYS/BIOS 6.37.3.35 (21)4.2安装XDCTools 3.25.06.96 (24)5 TMS320C66x BIOS-MCSDK软件安装 (29)1SecureCRT调试终端软件安装SecureCRT是一个调试终端软件,支持SSH,同时支持Telnet和rlogin协议,是一款用于连接运行包括Windows、UNIX和VMS的理想工具。

通过使用内含的VCP命令行程序可以进行加密文件的传输。

有流行CRTTelnet客户机的所有特点,包括:自动注册、对不同主机保持不同的特性、打印功能、颜色设置、可变屏幕尺寸、用户定义的键位图和优良的VT100、VT102、VT220和ANSI竞争,能从命令行中运行或从浏览器中运行,其它特点包括文本手稿、易于使用的工具条、用户的键位图编辑器、可定制的ANSI颜色等。

SecureCRT的SSH协议支持DES、3DES和RC4密码和密码与RSA鉴别。

1.1软件安装(1)解压光盘资料tools路径下的VanDyke.SecureCRT.zip文件。

64位计算机请双击"VanDyke.SecureCRT\x64\scrt725-x64_.exe"安装程序,32位计算机请双击""VanDyke.SecureCRT\x86\scrt725-x86_.exe"安装程序。

TL665x-EasyEVM开发板规格书

1开发板简介基于TI KeyStone C66x多核定点/浮点DSP TMS320C665x,单核TMS320C6655和双核TMS320C6657管脚pin to pin兼容,同等频率下具有四倍于C64x+器件的乘累加能力; 主频1.0/1.25GHz,单核可高达40GMACS和20GFLOPS,包含2个Viterbi协处理器和1个Turbo协处理解码器,每核心32KByte L1P、32KByte L1D、1MByte L2,1MByte多核共享内存,8192个多用途硬件队列,支持DMA传输;可免装风扇,以最低的功率级别和成本提供最高的性能;支持PCIe、SRIO、HyperLink、uPP、EMIF16、千兆网口等多种高速接口,同时支持I2C、SPI、UART、McBSP等常见接口;连接稳定可靠,80mm*58mm,体积极小的C66x核心板,采用工业级高速B2B连接器,关键大数据接口使用高速连接器,保证信号完整性;提供丰富的开发例程,入门简单,支持裸机和SYS/BIOS操作系统。

图 1 开发板正面图图 2 开发板侧面图1图 3 开发板侧面图2图 4 开发板侧面图3图 5 开发板侧面图4TL665x-EasyEVM是一款基于广州创龙TI KeyStone C66x多核定点/浮点TMS320C665x 核心板SOM-TL665x设计的高端DSP开发板,底板采用沉金无铅工艺的4层板设计,它为用户提供了SOM-TL665x核心板的测试平台,用于快速评估SOM-TL665x核心板的整体性能。

SOM-TL665x引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。

不仅提供丰富的Demo程序,还提供DSP核间通信开发教程,全面的技术支持,协助客户进行底板设计和调试以及多核软件开发。

2典型运用领域✓数据采集处理显示系统Telecom Tower:远端射频单元(RRU)✓X 射线:行李扫描仪✓专业音频混合器✓军用和航空电子成像✓军用:军需品和目标应用✓军用:雷达/声纳✓军用:雷达/电子战✓打印机✓无线通信测试仪✓机器视觉:帧捕捉器✓机器视觉:摄像机✓条码扫描仪✓点钞机✓电信基带单元✓视频分析服务器✓软件无线电(SDR)✓高速数据采集和生成3软硬件参数硬件框图图 6 开发板硬件框图图7 开发板硬件资源图解1图8 开发板硬件资源图解24、硬件参数CPU单核TMS320C6655/双核TMS320C6657,主频1.0/1.25GHz ROM128/256MByte NAND FLASHRAM512M/1GByte DDR3EEPROM1MbitSENSOR 1x TMP102AIDRLT,核心板温度传感器,I2C接口B2B Connector 2x 50pin公座B2B,2x 50pin母座B2B,间距0.8mm,合高5.0mm;1x 80pin高速B2B连接器,间距0.5mm,合高5.0mm,共280pin,信号速率最高可达10GBaudLED2x供电指示灯(核心板1个,底板1个)5x用户指示灯(核心板2个,底板3个)KEY 2x复位按键,包含1个系统复位和1个软复位1x NMI按键1x用户按键SRIO1x SRIO,四端口四通道,每通道最高通信速率5GBaudPCIe1x PCIe Gen2,单端口双通道,每通道最高通信速率5GBaudHyperLink1x HyperLink,最高通信速率40GBaud,KeyStone处理器间互连的理想接口IO2x 25pin IDC3简易牛角座,间距2.54mm,含uPP、EMIF16拓展信号2x 25pin IDC3简易牛角座,间距2.54mm,含McBSP、SPI、TIMER、GPIO等拓展信号UART1x UART0,Micro USB接口,提供4针TTL电平测试端口1x UART1,DB9接口,提供6针TTL电平测试端口Ethernet 1x SGMII,RJ45接口,10/100/1000M自适应JTAG 1x 14pin TI Rev B JTAG接口,间距2.54mmFAN 1x FAN,12V供电,间距2.54mmBOOT SET 1x 5bit拨码开关SWITCH 1x电源开关POWER 1x 12V 2A直流输入DC417电源接口,外径4.4mm,内径1.65mm 备注:广州创龙SOM-TL6655、SOM-TL6657核心板在硬件上pin to pin兼容。

TI KeyStone C66x多核定点浮点DSP TMS320C665x工业核心板,单核TMS320C6655和双核TMS320C6657

Revision HistoryDraft Date Revision No. Description 2016/02/04 V1.1 1. 排版修改。

2014/07/30 V1.0 1. 初始版本。

目录1 核心板简介 (4)2 典型运用领域 (5)3 软硬件参数 (6)4 开发资料 (8)5 电气特性 (9)6 机械尺寸图 (9)7 产品订购型号 (10)8 技术支持 (11)9 增值服务 (11)更多帮助 (12)附录A 开发例程 (13)1核心板简介处理器架构先进:基于TI KeyStone C66x多核定点/浮点DSP TMS320C665x,单核TMS320C6655和双核TMS320C6657管脚pin to pin兼容,同等频率下具有四倍于C64x+器件的乘累加能力;运算能力强:主频1.0G/1.25GHz,单核可高达40GMACS和20GFLOPS,包含2个Viterbi 协处理器和1个Turbo协处理解码器,每核心32KB L1P、32KB L1D、1MB L2,1MB 多核共享内存,8192个多用途硬件队列,支持DMA传输;性价比高:可免装风扇,以最低的功率级别和成本提供最高的性能;拓展资源丰富:支持PCIe、SRIO、HyperLink、uPP、EMIF、千兆网口等多种高速接口,同时支持I2C、SPI、UART、McBSP等常见接口;连接稳定可靠:80mm*58mm,体积极小的C66x核心板,采用工业级高速B2B连接器;开发资料齐全:提供丰富的开发例程,入门简单,支持裸机和SYS/BIOS操作系统。

图 1 SOM-TL665x正面图 2 SOM-TL665x背面由广州创龙自主研发的SOM-TL665x是一款基于TI KeyStone系列多核架构的定点/浮点TMS320C665x 高端DSP核心板,采用沉金无铅工艺的八层板设计,专业的PCB Layout 保证信号完整性的同时,经过严格的质量控制,满足多种环境应用。

2 创龙基于TMS320C665x CCS工程新建、编译和导入开发例程使用手册

在"EmptyProjects"下方选择"EmptyProject(withmain.c)"。

点击"Advancedsettings",在弹出的界面中的"Linkercommandfile:"选项后面选择cmd文件。cmd文件C665x.cmd可在光盘目录"Images"路径下找到,选择前请先将cmd文件拷到非中文路径。

2.2.2

(1)点击"File->New->Project",在弹出的界面中点开"Code Composer Studio",双击"CCS Project",如下图所示:

图75

图76

(2)在弹出的界面中输入工程名字,选择CPU平台和型号、仿真器型号、SYS/BIOS工程模板,如下图所示:

图77

(3)点击Next,弹出如下界面:

2.2.1

(1)点击"File->New->Project",在弹出的对话框中选择"RTSC->NewRTSCPlatform",如下图所示:

图66

图67

(2)点击Next,在弹出的对话框中设置平台包名字、路径,如下图所示:

图68

备注:平台包文件存放路径PlatformPackageRepository不能含有非ASCII字符,请记住此路径,在下面SYS/BIOS工程新建步骤将用到。

图91

打开CCS,点击CCS菜单栏下"Window->Preferences",如下图所示:

图49

TMS320C6657:1.25GHz DSP开发方案

TMS320C6657:1.25GHz DSP开发方案

佚名

【期刊名称】《世界电子元器件》

【年(卷),期】2014(000)002

【摘要】TI公司的TMS320C6655/57是定点/浮点数字信号处理器(DSP),基于KeyStone多核架构,内核速度高达1.25GHz,集成了各种包括C66x内核、存储器子系统、外设和加速器在内的各种子系统,适用于高性能低功耗可编程应用,如任务关键型、测试与自动化、医疗影像以及基础设施设备等。

TI公司的

TMS320C6655/57 DSP最高可以提供2.5GHz的累积DSP,使得该平台具有高能效,并易于使用。

此外,它与所有现有的C6000系列、定点和浮点DSP完全向后兼容。

【总页数】3页(P12-14)

【正文语种】中文

【相关文献】

1.DSP开发方案的设计与选择 [J], 董永宏

2.ADSP-BF609:嵌入视频开发方案 [J],

3.ADSP-21489:SHARC处理器开发方案 [J],

4.基于TMS320C6657的嵌入式Web视频服务器设计 [J], 闫渠成;李勇

5.基于TMS320C6657的千兆以太网接口设计 [J], 吴向旭;冯晓东;王贵冬;陈晶晶因版权原因,仅展示原文概要,查看原文内容请购买。

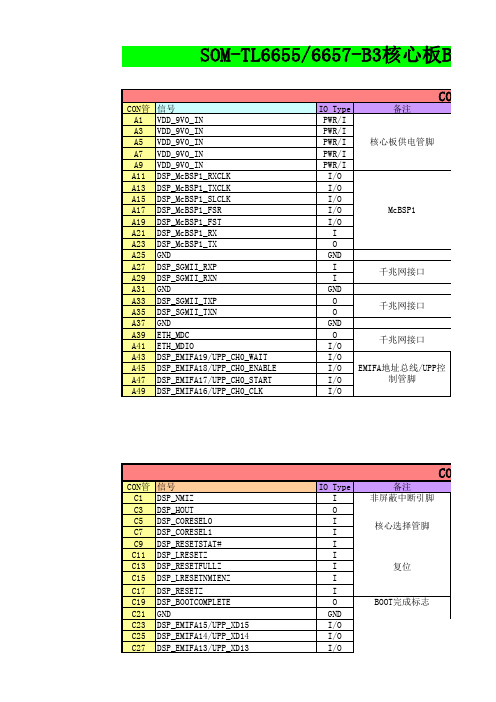

107133-创龙C66x平台资料-SOM-TL665x核心板引脚说明_20171011

CON管脚 E2 E4 E6 E8 E10 E12 E14 E16 E18 E20 E22 E24 E26 E28 E30 E32 E34 E36 E38 E40 E42 E44 E46 E48 E50 E52 E54 E56 E58 E60 E62 E64 E66 E68

PCIe发送通道2

O PCIe_TX2P O PCIe_TX2N

4.利用核心板进行设计底板时,请认真核对自己底板的核心板B2B连接器的信号引脚线序是否正确,连接 确,请务必参考我司提供的底板PCB图进行核对。核心板同样的B2B物料,可以联系我司采购。

5.有关信号详细功能,请查看芯片datasheet。

6.强烈 建议使 用我司 默认使 用的 UART0串 口作为 软件调 7、VDD_1V8_REF及VDD_3V3_REF仅做电平转换的参考电压;底板其他电路不得使用。

CON1C

备注

出厂调试接口;悬空 不用

IO Type 信号 I/O DSP_EMIFWAIT1/UPP_2XTXCLK CPLD_TCK CPLD_TCK CPLD_TDI CPLD_TDO GND GND I/O DSP_EMIFD15/UPP_D15

I/O DSP_EMIFD14/UPP_D14

I

I O GND I/O I/O I/O

CON1C

备注 非屏蔽中断引脚

核心选择管脚

复位

BOOT完成标志

EMIFA地址总线/UPP扩

C29 DSP_EMIFA12/UPP_XD12 C31 DSP_EMIFA11/UPP_XD11 C33 DSP_EMIFA10/UPP_XD10 C35 DSP_EMIFA9/UPP_XD9 C37 DSP_EMIFA8/UPP_XD8 C39 DSP_EMIFA7/UPP_XD7 C41 DSP_EMIFA6/UPP_XD6 C43 DSP_EMIFA5/UPP_XD5 C45 DSP_EMIFA4/UPP_XD4 C47 DSP_EMIFA3/UPP_XD3 C49 VDD_1V8_REF

7 创龙TMS320C665x基于广州创龙编写的RTSC组件的例程使用手册

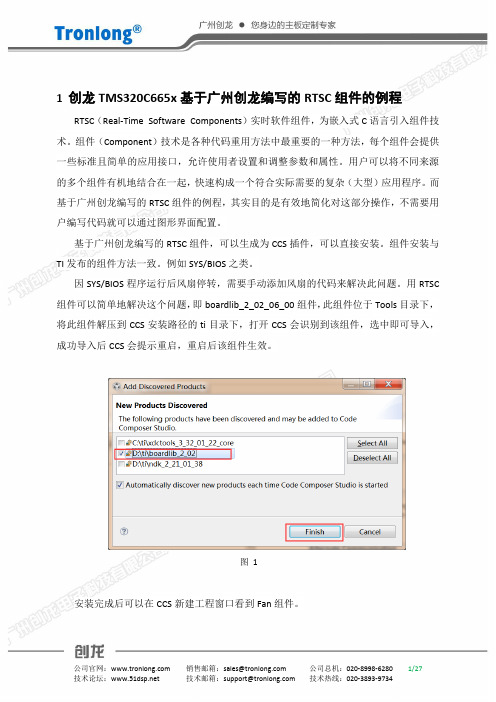

1 创龙TMS320C665x基于广州创龙编写的RTSC组件的例程RTSC(Real-Time Software Components)实时软件组件,为嵌入式C语言引入组件技术。

组件(Component)技术是各种代码重用方法中最重要的一种方法,每个组件会提供一些标准且简单的应用接口,允许使用者设置和调整参数和属性。

用户可以将不同来源的多个组件有机地结合在一起,快速构成一个符合实际需要的复杂(大型)应用程序。

而基于广州创龙编写的RTSC组件的例程,其实目的是有效地简化对这部分操作,不需要用户编写代码就可以通过图形界面配置。

基于广州创龙编写的RTSC组件,可以生成为CCS插件,可以直接安装。

组件安装与TI发布的组件方法一致。

例如SYS/BIOS之类。

因SYS/BIOS程序运行后风扇停转,需要手动添加风扇的代码来解决此问题。

用RTSC 组件可以简单地解决这个问题,即boardlib_2_02_06_00组件,此组件位于Tools目录下,将此组件解压到CCS安装路径的ti目录下,打开CCS会识别到该组件,选中即可导入,成功导入后CCS会提示重启,重启后该组件生效。

图 1安装完成后可以在CCS新建工程窗口看到Fan组件。

图 2此处以SYS/BIOS例程中NDK_UDP为例进行操作。

右键选中NDK_UDP工程,在弹出的窗口点击属性项。

图 3图 4 打开CFG文件。

图 5图 6当组件添加到工程的时候,重新编译并运行这个程序时,风扇就会启动,转速可调。

7.1RTSC_Fan——对散热风扇转速进行控制基于广州创龙编写的RTSC组件的例程路径在光盘的"Demo/RTSC_C665x"文件夹下。

该程序实现的功能是通过定时器调整风扇定时器,控制频率来达到控制转速目的。

将开发板的串口和PC机连接,打开串口调试终端,按照工程导入步骤加载NonOS_Fan.out文件,然后点击程序运行按钮,串口打印信息如下:图7演示现象风扇转速在运行程序后降低。

基于TMS320C6655的多处理器电路设计

基于 TMS320C6655的多处理器电路设计摘要:为了满足对高速数据传输的要求,设计了一种DSP(TMS320C6655含有高速SRIO口和485通讯口)+FPGA+光模块电路架构,利用FPGA的内部资源,作为DSP与外部陀螺和加表交互的桥梁,在DSP与加表、陀螺中开辟相应的数据池,实现多处理器间的异步数据通信。

该方法工程实现简单,达到了实际工程应用状态,在多处理器架构方面,提升了电路资源、处理能力及可靠性。

通过系统试验,验证了系统软硬件设计的正确性高的应用推广价值。

关键词:FPGA;DSP;SRIO;4851、前言在目前电子系统设计中,信息处理电路多采用DSP+FPGA架构。

其中DSP作为电路的核心单元,负责数据处理和算法实现,FPGA作为外围数字电路接口,如RS422串口通信控制、SPI通信控制等。

DSP的缺点是并行处理能力差,FPGA的缺点是信息处理、逻辑分析、决策判断等智能方面存在不足。

因此,在电路设计过程中,根据设计需求灵活选择不同的电路架构。

本文以某捷联惯导中导航计算机电路设计为背景,电路架构由DSP+FPGA升级为DSP+FPGA+光模块架构。

其中DSP为TI公司的C6655[1],FPGA为ACTEL公司的A3P1000[2],光模块为贵州航天电器有限公司的JM032L-2M8103500-T5YCL150 [3]。

2、某捷联惯导原理样机阶段DSP+FPGA架构设计导航计算机电路采用了DSP+FPGA架构,如图1所示。

DSP主要功能为导航算法计算,FPGA主要功能为外围电路接口,与外部的通讯仅仅为422接口,不满足对高速数据传输的要求。

图1 导航计算机电路原理框图为了解决高速数据传输的问题,采用TMS320C6655(含有高速SRIO通讯口)+FPGA+光模块的设计方案,与总体接口实现方式保持一致。

该方法可以解决上述问题,但是,由于引入了含有高速SRIO通讯口的TMS320C6655和光模块,需要研究多处理器电路设计,实现DSP、FPGA、光模块协调、稳定、可靠的工作。

多媒体TITMS320DM6437开发板硬件资源详解

多媒体TITMS320DM6437开发板硬件资源详解多媒体TI TMS320DM6437开发板硬件资源详解目录1 开发板简介 (2)2 典型运用领域 (3)3 软硬件参数 (4)4 开发资料 (6)5 电气特性 (6)6 机械尺寸图 (7)7 核心板型号 (8)8 技术支持 (9)1开发板简介基于TI TMS320DM6437的32位定点多媒体DSP处理器,适合高性能、低成本视频应用开发,最高主频为700MHz;支持8个8bit或4个16bit并行MAC运算,峰值处理能力高达5600MIPS,可实时处理8路CIF或3路D1格式的H.264编码算法;2级Cache体系结构:32KB可配置L1P、80KB可配置L1D和128KB可配置L2;64通道增强型DMA控制器EDMA3,支持复杂的数据类型的传输,利于图像数据高效传输和格式变换;视频处理子系统(VPSS):具有1个VPFE视频输入接口,支持BT.656输入,1个VPBE 视频输出接口,支持NTSC/PAL,S-Video,RGB,YPbPr输出;集成McASP、McBSP、I2C、UART、PCI、HPI、EMIFA等常见接口;核心板大小仅63.5mm*38mm;采用精密工业级B2B连接器,占用空间小,稳定性强,易插拔,防反插。

图1 TL6437-EVM正面图2 TL6437-EVM侧视图1图3 TL6437-EVM侧视图2图4 TL6437-EVM侧视图3图5 TL6437-EVM 侧视图4广州创龙自主研发的TL6437-EVM开发板是基于TMS320DM6437定点DSP核心板,大小仅63.5mm*38mm,功耗小、成本低、性价比高。

采用沉金无铅工艺的二层板设计,专业的PCB Layout保证信号完整性的同时,经过严格的质量控制,满足工业环境应用。

TL6437-EVM引出CPU全部资源信号引脚,二次开发极其容易,用户只需要专上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。

TMS320C6748开发板使用手册2014

三核主板方案领导TMS320C6748开发板使用手册Revision History目录1开发板准备 (4)1.1测试开发板硬件 (4)1.2查看仿真器驱动是否正常安装 (4)2程序烧写 (5)2.1设置工程配置文件信息 (5)2.2测试仿真器是否正常连接 (9)2.3加载GEL文件 (10)2.4CCS连接开发板CPU (11)2.5运行GEL文件来初始化开发板 (12)2.6加载和运行烧写程序C6478_NandWrite.out (13)2.7擦除和烧写Nand Flash (14)2.8镜像格式转换方法 (14)3CCS工程新建和编译 (16)3.1新建工程 (18)3.2编写程序 (21)3.3编译和运行DSP程序 (22)4CCS工程导入和编译步骤 (24)5Demo例程演示 (29)5.1LED (29)5.2KEY (29)5.3UART (29)5.4FFT (30)6附录 (35)6.1Boot Mode Selection (35)前言在进行以下操作之前,请先安装CCS,推荐使用我司验证过的CCS5.5.0版本。

安装包CCS5.5.0.00077_win32.zip可以在TMS320C6748产品资料光盘的tools目录下找到,也可以在TI官网下载,可以下载各种版本的CCS。

下载前需要注册一个TI账号,注册后才能用账号去下载CCS和其他文件,然后再去网上找一个破解文件,安装后按照破解文件指定步骤操作即可正常使用CCS5了。

TI官网下载链接:/index.php/Download_CCS#Code_Composer_Studio_Versio n_5_Downloads1 开发板准备1.1测试开发板硬件将开发板的拨码开关1~5号对应拨到00101(说明见附录,1代表ON,0代表OFF,X代表任意,即可以是0也可以是1),这是UART2档位。

RS232串口线通过USB转串口接到PC机的USB口,DB9母头(带孔)接底板UART2口,设置PC机调试终端COM口,波特率为115200,8N1,无检验位。

TMS320C6748开发板硬件说明书

TMS320C6748开发板硬件说明书Revision History目录前言 (3)1 TMS320C6748开发板简介 (4)2 开发板硬件资源说明 (5)2.1CPU (6)2.2FLASH (7)2.3RAM (8)2.4电源接口和拨码开关 (8)2.5JTAG仿真器接口 (9)2.6LED指示灯 (10)2.7按键 (11)2.8串口 (13)2.9I2C EEPROM (15)2.10SPI FLASH (16)2.11LCD触摸屏接口 (16)2.12BOOTSET启动选择开关 (18)2.13SD卡扩展卡槽 (18)2.14拓展IO信号 (19)2.15核心板B2B连接器 (21)2.16RTC座 (23)2.17SATA硬盘接口 (24)2.18RJ45以太网口 (25)2.19USB OTG和USB HOST接口 (26)2.20音频输出输入接口 (28)2.21VGA视频输出接口 (30)前言广州创龙TMS320C6748开发板是一款以TMS320C6748作为主处理器的浮点DSPC6748开发板,CPU内部集成了强大的多媒体处理单元,拥有SATA、UPP、OTG等接口,同时支持视频输入和VGA输出。

广州创龙TMS320C6748开发板采用TMS320C6748核心板+EVM底板的设计方式,尺寸为18cm x 13cm,它主要帮助开发者快速评估TMS320C6748的性能。

TMS320C6748核心板采用高密度6层板沉金无铅设计工艺,尺寸为55mm x 33mm,它集成了128MB/256MB DDR2,64MB/128MB/256M/512MB NAND Flash存储器,采用5V供电,板载3路转换率很高的DC-DC核心电压转换电源芯片,实现了系统的低功耗指标,精密、原装进口的B2B连接器引出全部接口资源,以便开发者进行快捷的二次开发使用。

1 TMS320C6748开发板简介TMS320C6748开发板底板布局及接口资源如下图所示,它是一个四层无铅沉金电路板,为了方便用户学习开发参考使用,上面引出了常见的各种接口。

TMS320C665x+Artix-7开发板硬件说明书2

TMS320C665x+Artix-7创龙硬件说明书前言广州创龙结合TI KeyStone系列多核架构TMS320C665x及Xilinx Artix-7系列FPGA设计的TL665xF-EasyEVM创龙是一款DSP+FPGA高速大数据采集处理平台,其底板采用沉金无铅工艺的6层板设计,适用于高端图像处理、软件无线电、雷达声纳、高端数控系统、机器视觉等高速数据处理领域。

核心板在内部通过uPP、EMIF16、SRIO通信接口将DSP 与FPGA结合在一起,组成DSP+FPGA架构,实现了需求独特、灵活、功能强大的DSP+F PGA高速数据采集处理系统。

TL665xF-EasyEVM创龙引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。

创龙不仅提供丰富的Demo程序,还提供DSP核间通信、DSP与FPGA间通讯开发教程以及全面的技术支持,协助客户进行底板设计和调试以及多核软件开发。

图 1 开发板正面图图 2 开发板斜视图TMS320C665x+Artix-7处理器主要特点:基于TI KeyStone C66x多核定点/浮点DSP TMS320C665x + Xilinx Artix-7 FPGA处理器;TMS320C665x主频为1.0/1.25GHz,每核运算能力高达40GMACS和20GFLOPS,每核心32KByte L1P、32KByte L1D、1MByte L2,1MByte多核共享内存,8192个多用途硬件队列,支持DMA传输;FPGA芯片型号为XC7A100T-2FGG484I,逻辑单元101K个,DSP Slice 240个;TMS320C665x与FPGA内部通过uPP、EMIF16、SRIO连接;双SFP接口,传输速率可高达5Gbit/s,可接SFP光口模块或SFP电口模块;千兆以太网口,可接工业网络摄像机;工业级FMC连接器,支持高速ADC、DAC和视频输入输出等FMC-LPC标准模块; PCI Express 2.0高速数据传输接口,双通道,每通道通信速率可高达5GBaud;Serial Rapid I/O高速数据传输接口,双通道,每通道通信速率可高达5GBaud;可通过DSP配置及烧写FPGA程序,DSP和FPGA可以独立开发,互不干扰;支持uPP、EMIF16、SPI、McBSP、TIMER、GPIO等常见接口;连接稳定可靠,开发板采用工业级精密B2B高速连接器,关键大数据接口使用高速连接器,保证信号完整性;提供丰富的开发例程,入门简单,支持裸机和SYS/BIOS操作系统。

1-2 详解基于创龙TI DSP TMS320C6678 + Xilinx FPGA Kintex-7开发板的硬件说明书2

封面(根据需求选用封面,美工设计模板)TL6678F-EasyEVM开发板硬件说明书前言TL6678F-EasyEVM是广州创龙基于SOM-TL6678F核心板而研发的一款多核高性能DS P+FPGA开发板。

开发板采用核心板+底板方式,底板采用沉金无铅工艺的8层板设计,尺寸为247.33mm*139.8mm,它为用户提供了SOM-TL6678F核心板的测试平台。

为了方便用户开发和参考使用,上面引出了各种常见的接口,可以帮助用户快速评估SOM-TL66 78F核心板的整体性能。

广州创龙SOM-TL6678F核心板基于TI KeyStone C66x多核定点/浮点TMS3206678 + Xilinx Kintex-7 FPGA设计的高性能DSP+FPGA高速大数据采集处理器,采用沉金无铅工艺的14层板设计,尺寸为112mm*75mm,经过专业的PCB Layout保证信号的完整性,和经过严格的质量管控,满足多种环境应用。

详解基于创龙TI DSP TMS320C6678 + Xilinx FPGA Kintex-7的开发板特点: 基于TI KeyStone C66x多核定点/浮点DSP TMS320C6678 + Xilinx Kintex-7 FPGA的高性能信号处理器;TI TMS320C6678集成8核C66x,每核主频1.0/1.25GHz,每核运算能力高达40GMACS 和20GFLOPS,每核心32KByte L1P、32KByte L1D、512KByte L2,4MByte多核共享内存,8192个多用途硬件队列,支持DMA传输;FPGA芯片型号为XC7K325T-2FFG676I,逻辑单元326K个,DSP Slice 840个,8对速率为12.5Gb/s高速串行收发器,兼容XC7K160T/410T-2FFG676I;TMS320C6678与FPGA内部通过I2C、EMIF16、SRIO连接,其中SRIO每通道传输速度最高可达到5GBaud;外设接口丰富,集成PCIe、EMIF16、双千兆网口等多种高速接口,同时支持SPI、GPI O、TIMER等常见接口;FPGA扩展接口,可连多通道AD、DA等模块,拓展能力强;XADC接口,模拟到数字转换,可灵活配置逻辑输入,片内或片外参考电压可选;2个SFP+接口,传输速率可高达10Gbit/s,可接SFP+光口模块或SFP+电口模块;2个工业级FMC连接器,支持高速ADC、DAC和视频输入输出等FMC-LPC标准模块;可通过DSP配置及烧写FPGA程序,DSP和FPGA可以独立开发且互不干扰;工业级精密B2B连接器,0.5mm间距,稳定,易插拔,防反插,所有数据接口使用高速连接器,保证信号完整性。

1-1-TMS320C6655创龙开发板硬件说明书1

TMS320C6655(TL665x-EasyEVM)创龙开发板硬件说明书1TMS320C6655(TL665x-EasyEVM)是创龙基于SOM-TL665x核心板研发的一款TI C66 x多核定点/浮点高性能DSP创龙开发板,采用核心板+底板方式,底板尺寸为200mm*1 06.65mm,采用4*50pin和1*80pin B2B工业级连接器,稳定、可靠、便捷,可以帮助客户快速评估核心板性能。

SOM-TL665x核心板采用高密度沉金无铅工艺8层板设计,尺寸为80mm*58mm,采用TI KeyStone C66x多核定点/浮点DSP TMS320C665x高性能工业DSP处理器。

采用耐高温、体积小、精度高的B2B连接器,引出了核心板的全部接口资源,帮助开发者快速进行二次开发。

TMS320C6655(TL665x-EasyEVM)创龙开发板底板采用4层无铅沉金电路板设计,为了方便用户学习开发参考使用,上面引出了各种常见的接口。

1 TMS320C6655处理器TI TMS320C665x是一款高性能定点/浮点DSP处理器,主频高达1.0/1.25GHz,处理能力强,单核TMS320C6655和双核TMS320C6657管脚pin to pin兼容,拥有多种工业接口资源,以下是TMS320C665x CPU功能框创龙开发板图:创龙开发板图1创龙开发板图22 TMS320C6655 FLASH核心板上采用工业级NAND FLASH(128/256MByte),硬件如下创龙开发板图:创龙开发板图3核心板上采用工业级SPI NOR FLASH(64Mbit),硬件如下创龙开发板图:创龙开发板图43 TMS320C6655 RAMRAM采用工业级低功耗DDR3L,512M/1GByte可选,硬件如下创龙开发板图:创龙开发板图54 TMS320C6655温度传感器核心板上采用I2C接口的TMP102温度传感器,实现了系统温度的实时监测,测量误差≤2℃,测试温度为-40℃至125℃,硬件如下创龙开发板图:创龙开发板图65 TMS320C6655 EEPROM核心板上采用I2C接口1Mbit大小的工业级EEPROM,硬件如下创龙开发板图:创龙开发板图76 TMS320C6655 底板B2B连接器创龙开发板使用底板+核心板设计模式,底板共有5个B2B连接器。

TMS320C6748开发板规格书

Revision HistoryDraft Date Revision No. Description 2018/07/31 V1.3 1.文档优化。

2017/12/18 V1.2 1.更新为A4版,修改封面、产品图、硬件框图、硬件资源图解。

1.修改硬件参数命名。

2.替换开发板机械尺寸图。

3.更新附录A开发例程。

4.修改产品订购型号及替换产品参数解释图。

2016/01/30 V1.1 1.排版修改。

2014/07/30 V1.0 1.初始版本。

目录1 开发板简介 (4)2 典型运用领域 (7)3 软硬件参数 (7)4 开发资料 (10)5 电气特性 (11)6 机械尺寸图 (11)7 产品认证 (13)8 产品订购型号 (14)9 开发板套件清单 (15)10 技术支持 (15)11 增值服务 (16)更多帮助....................................................................................................... 错误!未定义书签。

附录A 开发例程.. (17)1TI TMS320C6748开发板简介基于TI TMS320C6748定点/浮点DSP C674x处理器,主频456MHz;集成uPP、EMIFA、SATA、USB 2.0 OTG等大数据接口,可与FPGA/CPLD配套使用; 55mm*33mm,C6000系列DSP核心板,仅硬币大小;采用精密工业级B2B连接器,占用空间小,稳定性强,易插拔,防反插;通过高低温、振动测试认证,满足工业环境需求,发热量小;支持裸机、SYS/BIOS操作系统。

图 1 开发板正面图1图 2 开发板正面图2图 3 开发板斜视图图 4 开发板测视图1图 5 开发板测视图2图 6 开发板测视图3图7 开发板测视图4TL6748-EVM是一款基于广州创龙TMS320C6748核心板SOM-TL6748设计的DSP开发板,它为用户提供了SOM-TL6748核心板的测试平台,用于快速评估SOM-TL6748核心板的整体性能。

dsp6657的串口学习

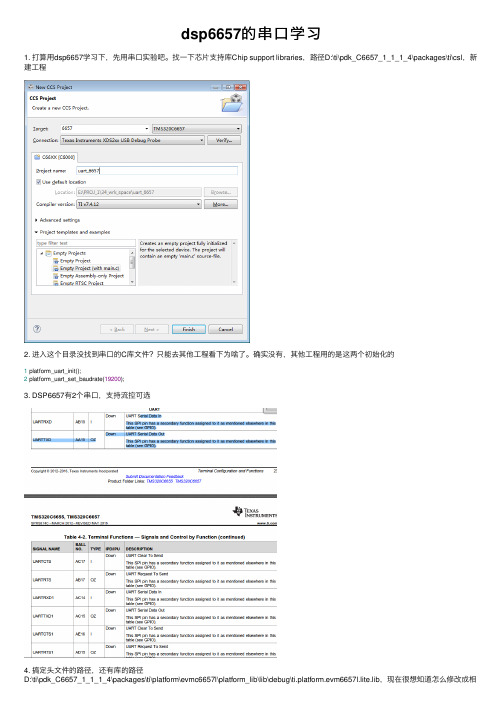

dsp6657的串⼝学习1. 打算⽤dsp6657学习下,先⽤串⼝实验吧。

找⼀下芯⽚⽀持库Chip support libraries,路径D:\ti\pdk_C6657_1_1_1_4\packages\ti\csl,新建⼯程2. 进⼊这个⽬录没找到串⼝的C库⽂件?只能去其他⼯程看下为啥了。

确实没有,其他⼯程⽤的是这两个初始化的1 platform_uart_init();2 platform_uart_set_baudrate(19200);3. DSP6657有2个串⼝,⽀持流控可选4. 搞定头⽂件的路径,还有库的路径D:\ti\pdk_C6657_1_1_1_4\packages\ti\platform\evmc6657l\platform_lib\lib\debug\ti.platform.evm6657l.lite.lib,现在很想知道怎么修改成相对路径,写了⼀个简单的程序,先测试⼀下1 #include "cslr_uart.h"2//估计导⼊包之后就可以直接使⽤包含的路径了3 #include "ti/platform/platform.h"45//#define PLATFORM_WRITE_IN 16void delay(int j)7 {8int i = 50000;9while(j--)10 {11int i = 50000;12while(i--);13 }14 }15void main()16 {17int i;18 platform_init_flags sFlags;19 platform_init_config sConfig;20/* Status of the call to initialize the platform */21 Int32 pform_status;22/* Platform Information - we will read it form the Platform Library */23 platform_info sPlatformInfo;2425/*26 * You can choose what to initialize on the platform by setting the following27 * flags. We will initialize everything.28*/29 memset( (void *) &sFlags, 0, sizeof(platform_init_flags));30 memset( (void *) &sConfig, 0, sizeof(platform_init_config));3132 sFlags.pll = 0;33 sFlags.ddr = 0;34 sFlags.tcsl = 0; /* Time stamp counter */35 sFlags.phy = 0; /* Ethernet */36 sFlags.ecc = 0;3738 sConfig.pllm = 0;3940 pform_status = platform_init(&sFlags, &sConfig);41if (pform_status == Platform_EOK) {42/* Get information about the platform so we can use it in various places */43 memset( (void *) &sPlatformInfo, 0, sizeof(platform_info));44 (void) platform_get_info(&sPlatformInfo);45 }4647 platform_uart_init();48 platform_uart_set_baudrate(19200);49//串⼝初始化50//打印⼀段51while(1)52 {5354 platform_uart_write(0x55);55 (void) platform_led(1, PLATFORM_LED_ON, (LED_CLASS_E) PLATFORM_USER_LED_CLASS);56 delay(50);57 (void) platform_led(1, PLATFORM_LED_OFF, (LED_CLASS_E) PLATFORM_USER_LED_CLASS);58 delay(50);59 }60 }5. 估计是没有cmd⽂件,所以load下载程序的时候失败了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

公司官网:

技术论坛:

销售邮箱:sales@ 技术邮箱:support@

公司总机:020-8998-6280

公司官网:

技术论坛: 2/28

技术论坛: 4/28

1 处理器

TI TMS320C665x 是一款高性能定点/浮点 DSP 处理器。主频高达 1.25GHz,处理能 力强。拥有多种工业接口资源,以下是 TMS320C665x CPU 功能框图:

图1

销售邮箱:sales@ 技术邮箱:support@

公司总机:020-8998-6280

公司官网:

技术论坛: 6/28

RAM 采用工业级低功耗 DDR3L(2*256MByte/2*512MByte),硬件如下图:

图4

4 温度传感器

核心板上采用 TMP102 温度传感器,测量误差≤2°,测试温度为-40°~125°,硬件 如下图:

公司总机:020-8998-6280

公司官网:

技术论坛: 5/28

图 2 TMS320C665x 芯8MByte/256GByte),硬件如下图:

图3

3 RAM

销售邮箱:sales@ 技术邮箱:support@

广州创龙,您身边的主板定制专家!

产品保修

广州创龙所有产品保修期为一年,保修期内由于产品质量原因引起的,经鉴定是非

人为因素造成的产品损坏问题,由广州创龙免费维修或者更换。

更多帮助

销售邮箱:sales@ 技术邮箱:support@

公司总机:020-8998-6280

3 RAM.......................................................................................................................................... 6 4 温度传感器 .............................................................................................................................. 7 5 EEPROM................................................................................................................................... 8 6 电源接口和拨码开关 .............................................................................................................. 8 7 LED 指示灯 .............................................................................................................................. 9 8 按键 ........................................................................................................................................ 11 9 BOOT SET 启动选择开关..................................................................................................... 13 10 JTAG 仿真器接口 ................................................................................................................ 15 11 串口 ...................................................................................................................................... 16 12 RJ45 以太网口...................................................................................................................... 18 13 散热风扇接口 ...................................................................................................................... 19 14 拓展 IO 信号........................................................................................................................ 19 15 底板 B2B 连接器................................................................................................................. 21 16 SRIO...................................................................................................................................... 24 17 Hyperlink 接口...................................................................................................................... 25 18 PCIe 4x 接口......................................................................................................................... 26 19 更多帮助 .............................................................................................................................. 28

公司简介

广州创龙电子科技有限公司(简称“广州创龙”或"Tronlong"),是中国领先的嵌入

式方案商,专业提供嵌入式开发套件、教学设备和主板定制服务,专注于 TI DSP 以及

DSP+ARM 平台方案开发,是 TI 大学计划最重要的第三方合作伙伴,和国内诸多著名企

业、研究所、高等院校合作密切。

广州创龙拥有 TI C2000/C5000/C6000/DaVinci/KeyStone/Sitara、Xilinx Spartan/Virtex、

SOM-TL665x 核心板采用高密度沉金无铅工艺 8 层板设计,尺寸为 80mm*58mm,采 用原装进口美国德州仪器最新 KeyStone C66x 多核定点/浮点 DSP TMS320C665x,高性能 工业 DSP 处理器。采用耐高温、体积小、精度高的 B2B 连接器,引出了核心板的全部接 口资源,帮助开发者快速进行二次开发。

销售邮箱:sales@ 技术邮箱:support@

公司总机:020-8998-6280

公司官网:

技术论坛: 3/28

前言

TL665x-EasyEVM 是广州创龙基于 SOM-TL665x 核心板研发的一款 TI C66x 多核定 点/浮点高性能 DSP 开发板,采用核心板+底板方式,底板尺寸为 200mm*106.65mm,采 用 4*50pin + 1*80pin B2B 工业级连接器,稳定、可靠、便捷,可以帮助客户快速评估核 心板性能。

目

录

前 言 ...................................................................................................................................... 4 1 处理器 ...................................................................................................................................... 5 2 FLASH ...................................................................................................................................... 6

TL665x-EasyEVM 开发板硬件说明书

Revision History

Revision No. V1.0

1.初始版本

Description

Draft Date 2015/6/11

销售邮箱:sales@ 公司总机:020-8998-6280

技术邮箱:support@ 公司官网:

Altera Cyclone/Stratix 等系列产品线,推出基于 DSP+ARM+FPGA 三核架构的数据采集处